JP3615979B2 - 半導体装置及びその製造方法 - Google Patents

半導体装置及びその製造方法 Download PDFInfo

- Publication number

- JP3615979B2 JP3615979B2 JP2000013895A JP2000013895A JP3615979B2 JP 3615979 B2 JP3615979 B2 JP 3615979B2 JP 2000013895 A JP2000013895 A JP 2000013895A JP 2000013895 A JP2000013895 A JP 2000013895A JP 3615979 B2 JP3615979 B2 JP 3615979B2

- Authority

- JP

- Japan

- Prior art keywords

- film

- insulating film

- silicon

- atoms

- oxygen

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P14/00—Formation of materials, e.g. in the shape of layers or pillars

- H10P14/60—Formation of materials, e.g. in the shape of layers or pillars of insulating materials

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W20/00—Interconnections in chips, wafers or substrates

- H10W20/01—Manufacture or treatment

- H10W20/071—Manufacture or treatment of dielectric parts thereof

- H10W20/081—Manufacture or treatment of dielectric parts thereof by forming openings in the dielectric parts

- H10W20/084—Manufacture or treatment of dielectric parts thereof by forming openings in the dielectric parts for dual-damascene structures

- H10W20/085—Manufacture or treatment of dielectric parts thereof by forming openings in the dielectric parts for dual-damascene structures involving intermediate temporary filling with material

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P14/00—Formation of materials, e.g. in the shape of layers or pillars

- H10P14/60—Formation of materials, e.g. in the shape of layers or pillars of insulating materials

- H10P14/65—Formation of materials, e.g. in the shape of layers or pillars of insulating materials characterised by treatments performed before or after the formation of the materials

- H10P14/6516—Formation of materials, e.g. in the shape of layers or pillars of insulating materials characterised by treatments performed before or after the formation of the materials of treatments performed after formation of the materials

- H10P14/6529—Formation of materials, e.g. in the shape of layers or pillars of insulating materials characterised by treatments performed before or after the formation of the materials of treatments performed after formation of the materials by exposure to a gas or vapour

- H10P14/6532—Formation of materials, e.g. in the shape of layers or pillars of insulating materials characterised by treatments performed before or after the formation of the materials of treatments performed after formation of the materials by exposure to a gas or vapour by exposure to a plasma

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W20/00—Interconnections in chips, wafers or substrates

- H10W20/01—Manufacture or treatment

- H10W20/071—Manufacture or treatment of dielectric parts thereof

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W20/00—Interconnections in chips, wafers or substrates

- H10W20/01—Manufacture or treatment

- H10W20/071—Manufacture or treatment of dielectric parts thereof

- H10W20/081—Manufacture or treatment of dielectric parts thereof by forming openings in the dielectric parts

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W20/00—Interconnections in chips, wafers or substrates

- H10W20/01—Manufacture or treatment

- H10W20/071—Manufacture or treatment of dielectric parts thereof

- H10W20/081—Manufacture or treatment of dielectric parts thereof by forming openings in the dielectric parts

- H10W20/084—Manufacture or treatment of dielectric parts thereof by forming openings in the dielectric parts for dual-damascene structures

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W20/00—Interconnections in chips, wafers or substrates

- H10W20/40—Interconnections external to wafers or substrates, e.g. back-end-of-line [BEOL] metallisations or vias connecting to gate electrodes

- H10W20/45—Interconnections external to wafers or substrates, e.g. back-end-of-line [BEOL] metallisations or vias connecting to gate electrodes characterised by their insulating parts

- H10W20/48—Insulating materials thereof

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W20/00—Interconnections in chips, wafers or substrates

- H10W20/40—Interconnections external to wafers or substrates, e.g. back-end-of-line [BEOL] metallisations or vias connecting to gate electrodes

- H10W20/495—Capacitive arrangements or effects of, or between wiring layers

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P14/00—Formation of materials, e.g. in the shape of layers or pillars

- H10P14/60—Formation of materials, e.g. in the shape of layers or pillars of insulating materials

- H10P14/63—Formation of materials, e.g. in the shape of layers or pillars of insulating materials characterised by the formation processes

- H10P14/6326—Deposition processes

- H10P14/6328—Deposition from the gas or vapour phase

- H10P14/6334—Deposition from the gas or vapour phase using decomposition or reaction of gaseous or vapour phase compounds, i.e. chemical vapour deposition

- H10P14/6336—Deposition from the gas or vapour phase using decomposition or reaction of gaseous or vapour phase compounds, i.e. chemical vapour deposition in the presence of a plasma [PECVD]

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P14/00—Formation of materials, e.g. in the shape of layers or pillars

- H10P14/60—Formation of materials, e.g. in the shape of layers or pillars of insulating materials

- H10P14/66—Formation of materials, e.g. in the shape of layers or pillars of insulating materials characterised by the type of materials

- H10P14/668—Formation of materials, e.g. in the shape of layers or pillars of insulating materials characterised by the type of materials the materials being characterised by the deposition precursor materials

- H10P14/6681—Formation of materials, e.g. in the shape of layers or pillars of insulating materials characterised by the type of materials the materials being characterised by the deposition precursor materials the precursor containing a compound comprising Si

- H10P14/6682—Formation of materials, e.g. in the shape of layers or pillars of insulating materials characterised by the type of materials the materials being characterised by the deposition precursor materials the precursor containing a compound comprising Si the compound being a silane, e.g. disilane, methylsilane or chlorosilane

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P14/00—Formation of materials, e.g. in the shape of layers or pillars

- H10P14/60—Formation of materials, e.g. in the shape of layers or pillars of insulating materials

- H10P14/66—Formation of materials, e.g. in the shape of layers or pillars of insulating materials characterised by the type of materials

- H10P14/668—Formation of materials, e.g. in the shape of layers or pillars of insulating materials characterised by the type of materials the materials being characterised by the deposition precursor materials

- H10P14/6681—Formation of materials, e.g. in the shape of layers or pillars of insulating materials characterised by the type of materials the materials being characterised by the deposition precursor materials the precursor containing a compound comprising Si

- H10P14/6684—Formation of materials, e.g. in the shape of layers or pillars of insulating materials characterised by the type of materials the materials being characterised by the deposition precursor materials the precursor containing a compound comprising Si the compound comprising silicon and oxygen

- H10P14/6686—Formation of materials, e.g. in the shape of layers or pillars of insulating materials characterised by the type of materials the materials being characterised by the deposition precursor materials the precursor containing a compound comprising Si the compound comprising silicon and oxygen the compound being a molecule comprising at least one silicon-oxygen bond and the compound having hydrogen or an organic group attached to the silicon or oxygen, e.g. a siloxane

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P14/00—Formation of materials, e.g. in the shape of layers or pillars

- H10P14/60—Formation of materials, e.g. in the shape of layers or pillars of insulating materials

- H10P14/69—Inorganic materials

- H10P14/692—Inorganic materials composed of oxides, glassy oxides or oxide-based glasses

- H10P14/6921—Inorganic materials composed of oxides, glassy oxides or oxide-based glasses containing silicon

- H10P14/6922—Inorganic materials composed of oxides, glassy oxides or oxide-based glasses containing silicon the material containing Si, O and at least one of H, N, C, F or other non-metal elements, e.g. SiOC, SiOC:H or SiONC

Landscapes

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

- Formation Of Insulating Films (AREA)

Description

【発明の属する技術分野】

本発明は、半導体装置及びその製造方法に関し、特に、高速動作・低消費電力化に好適な半導体装置及びその製造方法に関する。

【0002】

【従来の技術】

半導体素子の微細化により、多層配線の寄生容量がトランジスタ自体の入出力容量と同等の大きさになり、素子動作の律速要因となっている。そこで、従来の酸化珪素(比誘電率〜4)より比誘電率が低い絶縁膜(以下、本発明において低誘電率膜と呼ぶ)を導入する検討が盛んに行われている。

【0003】

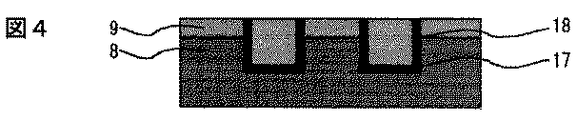

図1から図4は、従来検討されてきた低誘電率膜の使い方を示す断面図で、ある。本図では例としてダマシン法で埋め込み配線を形成する工程を示してある。まず、低誘電率膜8の上に保護膜として酸化珪素膜9を100nm程度以上形成した積層膜に、溝パタン16を形成する(図1)。ついで、レジスト6を除去した後(図2)、バリヤメタル17として窒化チタン,窒化タンタル等を薄く形成し、さらに銅18を形成する(図3)。ついで、化学機械研磨法(CMP)により、溝パタン内にのみ金属を残して配線・層間接続等の導電部とする(図4)。

【0004】

低誘電率膜8としては、フッ素化シロキサン系絶縁膜(比誘電率〜3.5),有機ポリマ系絶縁膜(比誘電率〜3),有機シロキサン系絶縁膜(比誘電率〜3)の3種が主に検討されている。

【0005】

このうち、フッ素化シロキサン系絶縁膜は、Si−F結合を側鎖にもち、主骨格がSi−O−Si結合の膜である(プロシ−ディングス・オブ・ブイエルエスアイ・マルチレベル・インタ−コネクション・コンファレンス、p.199、1997年)。膜中のフッ素が窒化チタン,窒化タンタル等のバリヤメタル17と反応し、剥離するのを防ぐために、酸化珪素保護膜9を用いる。

【0006】

有機ポリマ系絶縁膜は、主骨格が炭素の膜であり、ベンゾシクロブテン系や芳香族樹脂系等のものが主に検討されている。有機ポリマ膜とレジスト6は両者とも有機膜なので、エッチングやレジスト除去の際の両者の選択比は低い。そこで、形状・制御性のよい実用的なパタン加工条件を得るために、ハ−ドマスクとして酸化珪素保護膜9を用いる(プロシ−ディングス・オブ・インタ−ナショナル・インタ−コネクト・テクノロジ−・コンファレンス、p.59、1999年)。

【0007】

有機シロキサン系絶縁膜は、Si−R結合(Rは有機基)を側鎖にもち、主骨格がSi−O−Si結合の膜である。Rとしては、耐熱性に優れたCH3を用いるのが一般的である。その他の成分としてSi−Hを含む場合もある。有機シロキサン系絶縁膜は窒化チタン,窒化タンタル等の金属との接着性が弱い。そこで、CMP中に金属が剥離するのを防ぐ接着層として、酸化珪素保護膜9を用いるのが望ましい(セミコンダクター・インターナショナル、p.62、1999年)。

【0008】

上記有機シロキサン系絶縁膜の形成法としては、メチルアルコキシシラン・オリゴマ−のアルコ−ル溶液(有機塗布ガラス液)を回転塗布・焼成する方法の他に、種種の化学気相成長法(CVD)が検討されている。

【0009】

有機シロキサン系絶縁膜のCVD法の代表例は、有機シランと酸化ガスを用いるものである。たとえば、プロシ−ディングス・オブ・インタ−ナショナル・ソサイアティ・フォ−・オプティカル・エンジニアリング(SPIE)、Vol.3881,p.11、1999年には、RnSiH4−nと酸化ガスによるプラズマCVD法が、エレクトロケミカル・ソサイアティ・プロシ−ディングス、 Vol.98−6、p.146、1998年には、(CH3)3SiHとN2OとHeによるプラズマCVD法が公開されている。

【0010】

その他にも、(CH3)2Si(OCH3)2と不活性ガスを用いるプラズマCVD法が、第60回応用物理学会学術講演会予稿集1p−ZN−9、p.712、1999年に公開されている。ガス流量を通常の1/10程度に絞り、反応室内でのガスの滞在時間を長くすることが必要とされている。

【0011】

【発明が解決しようとする課題】

上記のように、従来検討されてきた低誘電率層間絶縁膜では、上面に保護膜として酸化珪素膜が必要である。実用的なプロセスマ−ジンを考えると、その膜厚は最低100nm程度が必要となる。この厚さは、微細配線の配線の厚さ(たとえばゲ−ト幅0.18umのデバイスでは300nm程度)の約1/3である。したがって、隣接配線間の実効誘電率は、酸化珪素保護膜の誘電率(〜4)に大きく影響され、低誘電率膜自体の誘電率より高くなってしまう。

【0012】

前記の低誘電率膜のうち、フッ素化シロキサン系絶縁膜と有機ポリマ系絶縁膜では、保護膜の使用は不可避である。フッ素化シロキサン系絶縁膜のフッ素の量を低減すれば膜の低誘電率特性が失われる。有機ポリマ系絶縁膜の対レジストエッチング選択比は本質的に高くできない。これに対して、有機シロキサン系絶縁膜は、フッ素のように金属と反応する成分は含まない。対レジストエッチング選択比は高くできる。したがって、上記剥離の問題を解決できれば、酸化珪素保護膜なしで用いることが可能である。

【0013】

ただし、従来技術に記した(CH3)3SiHとN2OとHeによるプラズマCVD法で成膜した場合のように膜中炭素が極端に多い場合は、対レジストエッチング選択比は高くできない。また、炭素含有量を減らせば、接着性が向上するのは明白であるが、同時に比誘電率も増大する。

【0014】

本発明の目的は、低誘電率で、対レジストエッチング選択比が高く、かつ酸化珪素保護膜なしでも剥離の問題を生じないような有機シロキサン系絶縁膜を層間絶縁膜に用いた半導体装置とその製造方法を提供することにある。

【0015】

【課題を解決するための手段】

上記課題は、酸化された場合の体積変化(収縮率)が小さい有機シロキサン系絶縁膜を用いることで解決できる。

【0016】

有機シロキサン系絶縁膜上に金属を成膜しただけの場合、剥離力が加わると単に金属が絶縁膜表面から剥離する。絶縁膜中の有機分(メチル基)が接着を阻害するためである。

【0017】

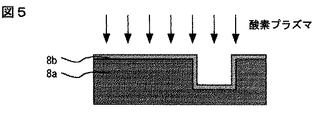

しかし、実際のプロセスでは、剥離のメカニズムは多少異なる。溝パタンを形成した有機シロキサン系絶縁膜8aの表面には、薄い酸化層8bが生じる(図5)。レジスト除去のための酸素プラズマ処理で酸化するからである。酸化層の膜厚は、主に酸素プラズマ処理の圧力で決まり、50mTorr以下の圧力であれば、10nm程度以下にすることができる。この酸化層と、窒化チタン,窒化タンタル等の金属との接着性は十分強い。しかし、酸化層8bとその下の酸化されていない有機シロキサン系絶縁膜層8aの間に力学的なひずみがあると、その界面が化学機械研磨の際に擦られて剥離する(図6)。酸化時の収縮率が大きいほど、この力学的ひずみは大きい。

【0018】

表面層の収縮率を直接測定するのは困難である。そこで、本発明では、膜の内部まで十分に酸化したとき、言い換えれば、膜中の有機分を十分に分解したときの収縮率を定義に用いる。膜の内部まで十分に酸化させるためには、例えば、1Torr以上の高圧力の酸素プラズマ処理してやればよい。測定に用いる膜厚は100−300nm程度が好ましい。薄すぎると測定が不正確で、厚すぎると膜内部まで酸化するのが困難になる。

【0019】

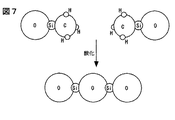

この方法で、従来の有機シロキサン系絶縁膜(比誘電率〜3)を酸化したときの収縮率は20%以上である。Si− CH3で終端されて離れていたSiどうしがシロキサン結合(Si−O−Si)を形成するからである(図7)。膜にSi−Hが含まれる場合も、同様に膜の収縮に寄与する。

【0020】

上記のような、酸化による収縮を起こさない有機成分として、Si−C−Si結合がある。酸化によりこの結合がシロキサン結合に置き換わっても、体積は大きく変化しない(図8)。むしろわずかに増大する。したがって、Si−C−Si結合でSi− CH3結合の一部を置き換えることで、有機シロキサン系絶縁膜の収縮量を14%以下、望ましくは10%以下にすれば、剥離の問題は生じず、本発明の課題は達成される。

【0021】

また、本発明の有機シロキサン系絶縁膜は、酸素原子数が珪素原子数の1.5倍以上、および炭素原子数が珪素原子数の1倍以上2倍以下であることが望ましい。炭素が少なければ、膜を低誘電率(比誘電率<3.5)にできない。膜中の酸素が少なすぎる、または炭素が多すぎても、レジストとのエッチング選択比を高くできない。

【0022】

本発明のSi−C−Si結合を含む有機シロキサン系絶縁膜は、一般式RnSi(OR’)2−0.5n(ただしRはCH3、R’はCH3またはC2H5)であらわされるメチルアルコキシシランの蒸気と非酸化性ガスの混合ガスを用いるプラズマCVD法により、実現できる。Si−OR’どおしが結合してSi−O−Siが形成され、Si−CH3が一部分解したものどおしが結合しSi−C−Siができる。非酸化性ガスを用いるのは、酸素等の酸化性ガスを用いると、膜に必要なSi−CH3やSi−C−Siが分解してしまうからである。ただし、膜の結合に寄与しない不要な有機成分(R’)は、可能な限り膜中から取り除くことが望ましい。したがって、非酸化性ガスとしては、単なる不活性ガスよりも、窒素、水素、アンモニア、あるいはこれらの混合物のような、還元性成分を含み、有機成分をHCNのような形で取り除けるほうが望ましい。ただし水素やアンモニアを用いると除外装置等の安全対策が必要となり、装置が複雑になる。この点では窒素と不活性ガスを用いるほうがさらに望ましい。また、不要な有機成分を低減するには、成膜中は基板を350℃〜400℃程度に加熱するほうが望ましい。

【0023】

上記のCVD法でSi−C−Siを形成するには、反応ガスの反応室内の滞在時間が短いほうが望ましい。滞在時間が長いと、反応室内の雰囲気中に反応生成物の炭素成分が多くなる。その結果、Si−CH3が分解する反応が抑制され、Si−C−Siの生成量が少なくなる。また、膜の結合に寄与しない不要な有機成分(R’)の量も多くなる。滞在時間に比例する量として、(圧力)・(ガス総流量)/(反応室容積)がある。Si−C−Siを形成して膜の収縮を抑制するには、この量は250(Torr・秒)以下が望ましく、150(Torr・秒)以下だとさらに望ましい。

【0024】

また、膜中の炭素量,酸素量を適切にするには、原料に用いるメチルアルコキシシランのnは0.75以上1.5以下であることが望ましい。この範囲に入っていれば、たとえばn=1の蒸気単体であっても、n=0〜2のアルコキシシラン蒸気の混合蒸気であってもかまわない。ただし、蒸気単体を用いるほうが、装置構造を単純にできるため、より望ましい。また、R’はCH3でもC2H5でも大きく違わないが、C2H5の方が蒸気圧が適切で取り扱いやすいため、さらに望ましい。

【0025】

【発明の実施の形態】

以下、実施の形態において本発明を具体的に説明する。

【0026】

<実施の形態1>

図9に示すような平行平板型チャンバをもつプラズマCVD装置で、Si基板上に厚さ200nmの有機シロキサン系膜を形成した。形成条件は以下のとおりである。液体ソ−ス:モノメチルトリエトキシシラン(CH3Si(OC2H5)3)、バブラ温度:37℃、キャリヤHe流量:200sccm、N2流量:200sccm、圧力:5Torr、基板温度375℃、RFパワ−:500W、電極間隔:180mils。

【0027】

形成した膜の比誘電率は3.2、絶縁耐圧は5MV/cmであった。フ−リエ変換法赤外吸収分光光度測定(FTIR)を用いて、膜中の結合を測定したところ、Si−O−Si,Si−CH3のほかにSi−CH3が分解してできたSi−C−Si,Si−Hが観察された(図10)。オ−ジェ分析を用いて膜中の原子数比を測定した。原子数比C/Siは1.6、O/Siは1.8であった。反応ガスに用いた窒素もN/Siで0.1程度、膜中に含まれていた。

【0028】

上記の膜にバレル形アッシャ装置で酸素プラズマ処理を加えた。処理条件は、酸素流量:200sccm、圧力:1Torr、RFパワ−:300W、時間:15分である。膜中の有機分は分解し、膜は酸化したが、エリプソメトリで測定した膜厚変化は5%未満であった。

【0029】

前記の膜を別途形成し、反応性イオンエッチング装置を用いて酸素プラズマ処理を施した。有機シロキサン系膜からのレジスト除去に用いる低圧条件を用いた。処理条件は、酸素流量:50sccm、圧力:10mTorr、RFパワ−:700W、時間:1分である。膜中の有機分はほとんど分解せず、表面の10nm程度が酸化した。この膜上に窒化チタンを50nm、ついで銅を500nm形成した。その後、ダイヤモンド針で格子状に傷をつけ、スコッチテ−プによる引き剥がし試験を行った。窒化チタンおよび銅の剥離は観察されなかった。

【0030】

窒素の代わりに不活性ガスのヘリウムを用いても、上記の剥離試験の結果は変わらなかったが、膜中の炭素含有量が多かった。膜の結合に寄与しない不要な炭素成分が多いためである。また、窒素の代わりに酸素を用いると、Si−CH3、Si−C−Si、Si−Hが少なくなった。この時の膜の誘電率は4以上で低誘電率特性は得られなかった。不要な炭素成分を低減し、かつ上記の特性を得るには、窒素、水素、アンモニア、あるいはこれらの混合ガス、等の還元性ガスが最適であった。また、液体ソ−スをモノメチルトリメトキシシラン(CH3Si(OCH3)3)にしても、バブラ温度を下げて上記と同等の蒸気圧が得られるようにすれば、同等の結果が得られた。

【0031】

<実施の形態2>

圧力を変えて成膜を行い、膜質の依存性を調べた。圧力以外の形成条件はすべて<実施の形態1>と同じである。ガス総流量が一定なので、圧力は滞在時間に比例する。

【0032】

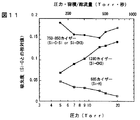

図11にFTIRスペクトルの圧力依存性を示す。縦軸は、波数1030カイザ−のSi−O−Si結合のピ−ク値で規格化してある。図中には、1270カイザ−のSi−CH3結合、885カイザ−のSi−H結合を示してある。Si−C−Si結合のある790カイザ−付近は、大きさが同等な複数のピ−クが近接して重なり、個々を分離できないので、便宜的に750〜850カイザ−の間でピ−クが最大になる波数と、その最大のピ−ク値を示してある。黒丸がSi−C−Si結合のある790カイザ−が最大の場合を示し、白丸がSi−CH3結合のある770カイザ−が最大の場合を示す。

【0033】

圧力が高いと、Si−CH3が多く、Si−Hは少ない。750〜850カイザ−の間でピ−クが最大になる波数は770カイザ−である。これは、Si−CH3が分解してSi−C−SiやSi−Hが生成する反応があまり起こらず、膜中にSi−CH3が多数残存することを示す。圧力が低くなるほど、Si−CH3は減少し、Si−Hは増大する。750〜850カイザ−の間でピ−クが最大になる波数は790カイザ−になり、これはSi−C−Si結合に相当する。圧力が低くなるほど、このSi−C−Si結合のピ−クも増大する。以上より、Si−CH3を分解してSi−C−Siを生成するには、滞在時間を短くすればよいことがわかった。

【0034】

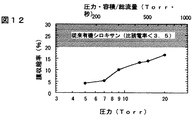

図12に、バレル型アッシャによる膜厚減少率を示す。バレル型アッシャの条件は<実施の形態1>と同じである。圧力が低く、滞在時間が長いほど、膜厚減少率が小さいことがわかった。

【0035】

また、剥離試験を行うために、Si基板上に厚さ200nmの絶縁膜を形成した後に、低圧酸素プラズマ処理を施し、窒化チタンと銅を形成した。これらの条件は<実施の形態1>と同じである。ついで、実際にCMPを行い、剥離の有無を観察した。圧力9Torr以下ではまったく剥離は観察されなかった。圧力13,15Torrでは、0.1mm径以下の微小な剥離が数箇所観察された。それ以上の圧力ではさらに大きな剥離が観察された。これより、良好な接着性を得るには、酸化したときの膜厚減少率を5%以下、さらに望ましくは3%以下にすればいいことがわかった。上記の方法でこのような膜を形成するには、(反応室内の圧力)・(反応室の容積)/(ガス総流量)を500(Torr・秒)以下、さらに望ましくは、280(Torr・秒)以下にすればよい。

【0036】

<実施の形態3>

液体ソ−ス材料を変えて成膜を行い、膜質の材料存性を調べた。2つの液体ソ−スを用いる場合、それぞれのバブラの温度とキャリヤHe流量を独立に制御できる2つのバブラを用いた。これにより、キャリヤHe総流量が200sccm、キャリヤ中の液体ソ−ス蒸気量が実施の形態1と同等になるように調節した。上記以外の形成条件はすべて実施の形態1と同じである。

【0037】

キャリヤガス200sccm中の液体ソ−ス蒸気の量を以下に示す(<実施の形態1>の蒸気量を1とする相対値)。(a)Si(OC2H5)4が1、(b)Si(OC2H5)4が0.25でCH3Si(OC2H5)3が0.75、(c)CH3Si(OC2H5)3が1、(d)CH3Si(OC2H5)3が0.5で(CH3)2Si(OC2H5)2が0.5、(e)(CH3)2Si(OC2H5)2が1。一般式(CH3)nSi(OC2H5)4−nであらわすと、(a)はn=0、(b)はn=0.5、(c)はn=1、(d)はn=1.5、(e)はn=2に相当する。

【0038】

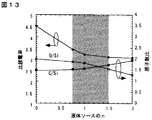

図13に比誘電率、膜中のO/Si比、C/Si比とnの関係を示す。これより、比誘電率3.5以下、O/Si比1.5以上、C/Si比1以上2以下を実現するには、nは0.5以上1.5以下であればよいことがわかった。

【0039】

また、上記の膜にバレル形アッシャ装置で酸素プラズマ処理を加えた。処理条件は、<実施の形態1>と同じである。エリプソメトリで測定した膜厚変化はいずれも10%未満であった。

【0040】

<実施の形態4>

<実施の形態1>の膜を用いて、半導体装置の多層配線を作成した。シングルダマシン法により、銅配線を形成する方法を用いた。

【0041】

まず、トランジスタ1,コンタクト2の形成された半導体基板0上に、<実施の形態1>の膜4を300nm形成し、第一の配線層に相当する溝パタン16を形成した(図14)。圧力10mTorrの低圧酸素反応性イオンエッチングを用いてレジスト6を除去した後、スパッタ法で窒化チタン17を50nm、銅18を100nm形成し、さらに電解メッキを用いて銅でパタン内を埋め込んだ(図15)。ついで、CMPによりパタン外の銅と窒化チタンを除去して第1層配線とした(図16)。

【0042】

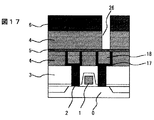

ついで、窒化珪素膜9を50nm、実施の形態1の膜4を400nm形成し、層間接続に相当する孔パタン26を形成した(図17)。この際、銅が露出しないようにエッチングは窒化珪素上で止めた。圧力10mTorrの低圧酸素反応性イオンエッチングを用いてレジストを除去した後、孔底に残存する窒化珪素をエッチングして、銅を露出させた。ついで、スパッタ法で窒化チタン17を50nm、銅18を100nm形成したのち、電解メッキを用いて銅でパタン内を埋め込んだ(図18)。さらに、CMPによりパタン外の銅と窒化チタンを除去して層間接続とした(図19)。

【0043】

さらに、窒化珪素膜9を50nm、<実施の形態1>の膜4を250nm形成し、第2層配線に相当する溝パタン36を形成した(図20)。この際のエッチングは上記と同様である。圧力10mTorrの低圧酸素反応性イオンエッチングを用いてレジストを除去した後、溝底に残存する窒化珪素をエッチングして、銅を露出させた。ついで、スパッタ法で窒化チタン17を50nm、銅18を100nm形成したのち、電解メッキを用いて銅でパタン内を埋め込んだ(図21)。さらに、CMPによりパタン外の銅と窒化チタンを除去して第2層配線とした(図22)。

【0044】

この後さらに、図17から図22と同様の処理を繰り返し、第3層配線を形成した(図23)。

【0045】

上記の工程のすべてで、剥離による問題は生じなかった。

【0046】

比較のために、厚さ100nmの酸化珪素保護膜を用いた試料も作成した。ただし、<実施の形態1>の膜の厚さはすべて100nm減らして、配線高さ、層間接続高さをそろえた。第2層配線間の実効誘電率および上下層配線間の実効誘電率を測定したところ、酸化珪素保護膜がないほうが、約1割実効誘電率が低かった。

【0047】

<実施の形態5>

<実施の形態1>の膜と有機ポリマ膜(ダウケミカル製、商品名SiLK、比誘電率2.7)を用いて、半導体装置の多層配線を作成した。シングルダマシン法により、銅配線を形成する方法を用いた。

【0048】

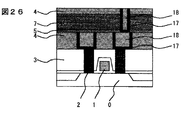

図16の後、窒化珪素膜9を50nm、有機ポリマ膜7を300nm、<実施の形態1>の膜4を100nm形成し、層間接続に相当する孔パタン26を形成した(図24)。この際、まず<実施の形態1>の膜をエッチしておき、ついでこれをハ−ドマスクにして有機ポリマ膜の同時エッチを行った。同時エッチには、酸素・窒素混合ガスによる低圧反応性イオンエッチングを用いた。次に、孔底に残存する窒化珪素をエッチングして、銅を露出させた。ついで、スパッタ法で窒化チタン17を50nm、銅18を100nm形成したのち、電解メッキを用いて銅でパタン内を埋め込んだ(図25)。さらに、CMPによりパタン外の銅と窒化チタンを除去して層間接続とした(図26)。この際、剥離の問題は生じなかった。

【0049】

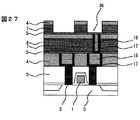

さらに、窒化珪素膜9を50nm、有機ポリマ膜7を150nm、<実施の形態1>の膜4を100nm形成し、第2層配線に相当する溝パタン36を形成した(図27)。この際のエッチングは上記と同様である。次に、溝底に残存する窒化珪素をエッチングして、銅を露出させた。ついで、スパッタ法で窒化チタン17を50nm、銅18を100nm形成したのち、電解メッキを用いて銅でパタン内を埋め込んだ(図28)。さらに、CMPによりパタン外の銅と窒化チタンを除去して第2層配線とした(図29)。

【0050】

この後さらに、図24から図29と同様の処理を繰り返し、第3層配線を形成した(図30)。

【0051】

上記の工程のすべてで、剥離による問題は生じなかった。

【0052】

比較のために、上記の<実施の形態1>の膜をすべて酸化珪素保護膜に代えた試料も作成した。第2層配線間の実効誘電率、および上下層配線間の実効誘電率を測定したところ、実施の形態1の膜を保護膜に用いたほうが、約1割実効誘電率が低かった。

【0053】

<実施の形態6>

<実施の形態1>の膜を用いて、半導体装置の多層配線を作成した。シングルダマシン法に比べて工程数の少ないデュアルダマシン法を用いて、銅配線を形成する方法を用いた。

【0054】

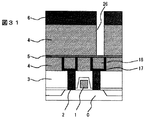

図16の後、窒化珪素膜9を50nm、実施の形態1の膜4を700nm形成し、層間接続に相当する孔パタン26を形成した(図31)。この際、銅が露出しないようにエッチングは窒化珪素上で止めた。圧力10mTorrの低圧酸素反応性イオンエッチングを用いてレジストを除去した後、第2層配線に相当する溝パタン36を形成した(図32)。圧力10mTorrの低圧酸素反応性イオンエッチングを用いてレジスト6を除去した後、孔底に残存する窒化珪素をエッチングして、銅を露出させた。ついで、スパッタ法で窒化チタン17を50nm、銅18を100nm形成したのち、電解メッキを用いて銅でパタン内を埋め込んだ(図33)。さらに、CMPによりパタン外の銅と窒化チタンを除去して層間接続と第2層配線を形成した(図34)。

【0055】

この後さらに、図31から図34と同様の処理を繰り返し、第3層配線を形成した(図35)。

【0056】

上記の工程のすべてで、剥離による問題は生じなかった。

【0057】

<実施の形態7>

<実施の形態1>の膜を用いて、半導体装置の多層配線を作成した。ドライエッチング法により、アルミニウム合金配線を形成する方法を用いた。

【0058】

まず、トランジスタ1,コンタクト2の形成された半導体基板0上に、窒化チタン17,アルミニウム合金19,窒化チタン17をそれぞれ50nm,300nm,50nm形成した。ついで、ホトリソグラフィ−,ドライエッチによって第1層配線を形成し、レジストを除去した(図36)。

【0059】

<実施の形態1>の膜を50nm形成した後、厚さ250nmの有機塗布ガラス(日立化成製、商品名HSG−R7)で溝を埋め込んだ後、<実施の形態1>の膜を厚さ1000nm形成した。ついで、化学機械研磨により表面を平坦化した後、層間接続に相当する孔パタンを形成した(図37)。圧力10mTorrの低圧酸素反応性イオンエッチングを用いてレジスト6を除去した後、スパッタ法で窒化チタン17を50nm、CVD法でタングステン20を300nm形成し、孔内を埋め込んだ(図38)。さらに、CMPによりパタン外のタングステンと窒化チタンを除去して層間接続を形成した(図39)。さらに、窒化チタン,アルミニウム合金,窒化チタンをそれぞれ50nm,300nm,50nm形成した。ついでホトリソグラフィ−,ドライエッチによって第2層配線を形成し、レジストを除去した(図40)。この際のレジスト除去にも、圧力10mTorrの低圧酸素反応性イオンエッチングを用いた。

【0060】

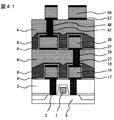

この後さらに、図37から図40と同様の処理を繰り返し、第3層配線を形成した(図41)。

【0061】

上記の工程のすべてで、剥離による問題は生じなかった。

【0062】

比較のために、<実施の形態1>の膜の代わりに酸化珪素保護膜を用いた試料も作成した。第2層配線間の実効誘電率および上下層配線間の実効誘電率を測定したところ、酸化珪素膜を用いたものに比べて、隣接配線間は1割、上下層間は2割、実効誘電率が低かった。

【0063】

【発明の効果】

本発明の低誘電率絶縁膜に孔あるいは溝パタンを形成したものに、直接金属膜を形成して研磨しても、金属膜は剥離しない。これは、パタンを形成後のレジスト除去による絶縁膜表面の収縮が小さいためである。

【0064】

したがって、従来の低誘電率膜と酸化珪素保護膜の積層膜を本発明の低誘電率膜で置き換えれば、工程が削減されると共に、酸化珪素膜による実効誘電率増加を防ぐことできる。また、本発明の低誘電率膜を、さらに低誘電率の絶縁膜の保護膜として用いても、酸化珪素膜による実効誘電率増加を削減できる。

【図面の簡単な説明】

【図1】従来の低誘電率層間絶縁膜を用いた半導体装置の製造方法の一例。

【図2】従来の低誘電率層間絶縁膜を用いた半導体装置の製造方法の一例。

【図3】従来の低誘電率層間絶縁膜を用いた半導体装置の製造方法の一例。

【図4】従来の低誘電率層間絶縁膜を用いた半導体装置の製造方法の一例。

【図5】従来の有機シロキサン系層間絶縁膜の問題点の説明図。

【図6】従来の有機シロキサン系層間絶縁膜の問題点の説明図。

【図7】Si−CH3の酸化による体積変化の説明図。

【図8】Si−C−Siが酸化による体積変化の説明図。

【図9】本発明の実施例1で用いるプラズマCVD装置。

【図10】本発明の実施例1のFTIRスペクトル。

【図11】本発明の実施例2のFTIRスペクトルの圧力依存性。

【図12】本発明の実施例2の膜厚減少率の圧力依存性。

【図13】本発明の実施例3の比誘電率と原子数比のn依存性。

【図14】本発明の実施例4の工程説明図。

【図15】本発明の実施例4の工程説明図。

【図16】本発明の実施例4の工程説明図。

【図17】本発明の実施例4の工程説明図。

【図18】本発明の実施例4の工程説明図。

【図19】本発明の実施例4の工程説明図。

【図20】本発明の実施例4の工程説明図。

【図21】本発明の実施例4の工程説明図。

【図22】本発明の実施例4の工程説明図。

【図23】本発明の実施例4の工程説明図。

【図24】本発明の実施例5の工程説明図。

【図25】本発明の実施例5の工程説明図。

【図26】本発明の実施例5の工程説明図。

【図27】本発明の実施例5の工程説明図。

【図28】本発明の実施例5の工程説明図。

【図29】本発明の実施例5の工程説明図。

【図30】本発明の実施例5の工程説明図。

【図31】本発明の実施例6の工程説明図。

【図32】本発明の実施例6の工程説明図。

【図33】本発明の実施例6の工程説明図。

【図34】本発明の実施例6の工程説明図。

【図35】本発明の実施例6の工程説明図。

【図36】本発明の実施例7の工程説明図。

【図37】本発明の実施例7の工程説明図。

【図38】本発明の実施例7の工程説明図。

【図39】本発明の実施例7の工程説明図。

【図40】本発明の実施例7の工程説明図。

【図41】本発明の実施例7の工程説明図。

【符号の説明】

0・・・半導体基板、1・・・トランジスタのゲ−ト電極、2・・・コンタクト電極、3・・・層間絶縁膜、4・・・本発明の層間絶縁膜、5・・・窒化珪素膜、6・・・レジスト、7・・・有機ポリマ系膜、8・・・従来の低誘電率層間絶縁膜、8a・・・従来の有機シロキサン系膜、8b・・・有機シロキサン系膜の酸化層、9・・・酸化珪素膜、10・・・剥離部、16・・・第一層配線用の溝パタン、17・・・バリヤメタル、18・・・銅、19・・・アルミニウム合金、20・・・タングステン、26・・・層間接続用の孔パタン、36・・・第二層配線用の溝パタン。

Claims (21)

- 少なくとも珪素,酸素,炭素のすべてを含み、酸素原子数が珪素原子数の1.5倍以上であり、かつ炭素原子数が珪素原子の1倍以上2倍以下であり、かつ膜の内部まで十分に酸化した時の膜厚の収縮率が14%以下である層間絶縁膜を有することを特徴とする半導体装置。

- 少なくとも珪素,酸素,炭素のすべてを含み、酸素原子数が珪素原子数の1.5倍以上であり、かつ炭素原子数が珪素原子の1倍以上2倍以下であり、かつ膜の内部まで十分に酸化した時の膜厚の収縮率が10%以下である層間絶縁膜を有することを特徴とする半導体装置。

- 前記層間絶縁膜の比誘電率が、3.5以下であることを特徴とする請求項1又は請求項2に記載の半導体装置。

- 前記層間絶縁膜が、少なくともSi−CH3結合,Si−O−Si結合,Si−C−Si結合のすべてを含むことを特徴とする請求項1乃至請求項3に記載の半導体装置。

- RSi(OR')3(但し、RはCH3,R'はC2H5)であらわされるモノメチルトリエトキシシランの蒸気と非酸化性ガスの混合ガスを用いてプラズマ化学気相成長法により層間絶縁膜を形成する工程と、前記層間絶縁膜に埋め込み配線を形成する工程とを有することを特徴とする半導体装置の製造方法。

- 一般式RnSi(OR')4−n(但し、RはCH3,R'はC2H5,n=0〜2)であらわされるメチルエトキシシランの蒸気を珪素1に対してRが0.75以上1.5以下になるように混合したものと、非酸化性ガスの混合ガスを用いてプラズマ化学気相成長法により層間絶縁膜を形成する工程と、前記層間絶縁膜に埋め込み配線を形成する工程と配線を形成する工程とを有することを特徴とする半導体装置の製造方法。

- RSi(OR')3(但し、RとR'はCH3)であらわされるモノメチルトリメトキシシランの蒸気、或いは、一般式RnSi(OR')4 −n(但し、n=0〜2)であらわされるメチルメトキシシシランの蒸気を珪素1に対してRが0.5以上1.5以下になるように混合したもの、のいずれかと、非酸化性ガスの混合ガスを用いてプラズマ化学気相成長法により層間絶縁膜を形成する工程と、前記層間絶縁膜に埋め込み配線を形成する工程とを有することを特徴とする半導体装置の製造方法。

- 前記非酸化性ガスが、窒素,水素,アンモニア,ヘリウム,アルゴン或いはこれらの混合物を含むことを特徴とする、請求項5乃至請求項7の何れかに記載の半導体装置の製造方法。

- 前記非酸化性ガスが、窒素と不活性ガスの混合物であることを特徴とする請求項5乃至請求項7の何れかに記載の半導体装置の製造方法。

- 前記層間絶縁膜の形成工程は、(反応室内の圧力)・(反応室の容積)/(ガス総流量)が500(Torr・秒)以下の条件で行うことを特徴とする請求項5乃至請求項9の何れかに記載の半導体装置の製造方法。

- 前記層間絶縁膜の形成工程は、(反応室内の圧力)・(反応室の容積)/(ガス総流量)が280(Torr・秒)以下の条件で行うことを特徴とする請求項5乃至請求項9の何れかに記載の半導体装置の製造方法。

- 少なくとも珪素,酸素,炭素のすべてを含み、酸素原子数が珪素原子数の1.5倍以上であり、かつ炭素原子数が珪素原子の1倍以上2倍以下であり、かつ膜の内部まで十分に酸化した時の膜厚の収縮率が14%以下である層間絶縁膜を形成する工程と、前記層間絶縁膜に溝或いは孔を形成する工程と、前記溝或いは孔が埋め込まれるように金属膜を堆積する工程と、前記溝内部或いは孔内部以外の前記金属膜を化学機械研磨法で除去する工程とを有することを特徴とする半導体装置の製造方法。

- 少なくとも珪素,酸素,炭素のすべてを含み、酸素原子数が珪素原子数の1.5倍以上であり、かつ炭素原子数が珪素原子の1倍以上2倍以下であり、かつ膜の内部まで十分に酸化した時の膜厚の収縮率が10%以下である層間絶縁膜を形成する工程と、前記層間絶縁膜に溝或いは孔を形成する工程と、前記溝或いは孔が埋め込まれるように金属膜を堆積する工程と、前記溝内部或いは孔内部以外の前記金属膜を化学機械研磨法で除去する工程とを有することを特徴とする半導体装置の製造方法。

- 前記溝の形成工程は、前記層間絶縁膜を少なくとも50mTorr以下の圧力で酸素を含むプラズマにさらす工程を含むことを特徴とする請求項12又は請求項13に記載の半導体装置の製造方法。

- 金属膜をドライエッチングして第1の配線を形成する工程と、少なくとも珪素,酸素,炭素のすべてを含み、酸素原子数が珪素原子数の1.5倍以上であり、かつ炭素原子数が珪素原子の1倍以上2倍以下であり、かつ膜の内部まで十分に酸化した時の膜厚の収縮率が14%以下である第1の絶縁膜を前記配線上に形成する工程と、塗布絶縁膜を形成する工程と、少なくとも珪素,酸素,炭素のすべてを含み、酸素原子数が珪素原子数の1.5倍以上であり、かつ炭素原子数が珪素原子の1倍以上2倍以下であり、かつ膜の内部まで十分に酸化した時の膜厚の収縮率が14%以下である第2の絶縁膜を形成する工程と、前記第1の絶縁膜,前記塗布絶縁膜及び第2の絶縁膜からなる積層膜に前記第1の配線の表面が露出する孔を開口する工程と、前記孔に金属膜を埋め込む工程と、前記孔内部に前記金属膜を残すように前記第2絶縁膜上の金属膜を研磨により除去する工程とを有することを特徴とする半導体装置の製造方法。

- 金属膜をドライエッチングして第1の配線を形成する工程と、少なくとも珪素,酸素,炭素のすべてを含み、酸素原子数が珪素原子数の1.5倍以上であり、かつ炭素原子数が珪素原子の1倍以上2倍以下であり、かつ膜の内部まで十分に酸化した時の膜厚の収縮率が10%以下である第1の絶縁膜を前記配線上に形成する工程と、塗布絶縁膜を形成する工程と、少なくとも珪素,酸素,炭素のすべてを含み、酸素原子数が珪素原子数の1.5倍以上であり、かつ炭素原子数が珪素原子の1倍以上2倍以下であり、かつ膜の内部まで十分に酸化した時の膜厚の収縮率が10%以下である第2の絶縁膜を形成する工程と、前記第1の絶縁膜,前記塗布絶縁膜及び第2の絶縁膜からなる積層膜に前記第1の配線の表面が露出する孔を開口する工程と、前記孔に金属膜を埋め込む工程と、前記内部に前記金属膜を残すように前記第2絶縁膜上の金属膜を研磨により除去する工程とを有することを特徴とする半導体装置の製造方法。

- 前記孔開口工程と前記金属膜埋込み工程の間に、50mTorr以下の圧力の少なくとも酸素を含むプラズマ処理により、前記孔開口工程で用いたレジストを除去する工程を有することを特徴とする請求項15又は請求項16に記載の半導体装置の製造方法。

- 同一絶縁膜内に形成された複数の埋め込み配線と、前記各埋め込み配線間に形成された、前記絶縁膜は酸化珪素膜よりも誘電率が低い低誘電率膜の単層膜であって、前記低誘電率膜は、少なくとも珪素,酸素,炭素のすべてを含み、酸素原子数が珪素原子数の1.5倍以上であり、かつ炭素原子数が珪素原子の1倍以上2倍以下であり、かつ膜の内部まで十分に酸化した時の膜厚の収縮率が14%以下であることを特徴とする半導体装置。

- 絶縁膜内に形成された複数の埋め込み配線と、前記各埋め込み配線間に形成された、前記絶縁膜は、複数の絶縁膜の積層膜からなり、最上層の絶縁膜が酸化珪素膜よりも誘電率が低い低誘電率膜であって、前記低誘電率膜は、少なくとも珪素,酸素,炭素のすべてを含み、酸素原子数が珪素原子数の1.5倍以上であり、かつ炭素原子数が珪素原子の1倍以上2倍以下であり、かつ膜の内部まで十分に酸化した時の膜厚の収縮率が14%以下であることを特徴とする半導体装置。

- 同一絶縁膜内に形成された複数の埋め込み配線と、前記各埋め込み配線間に形成された、前記絶縁膜は酸化珪素膜よりも誘電率が低い低誘電率膜の単層膜であって、前記低誘電率膜は、少なくとも珪素,酸素,炭素のすべてを含み、酸素原子数が珪素原子数の1.5倍以上であり、かつ炭素原子数が珪素原子の1倍以上2倍以下であり、かつ膜の内部まで十分に酸化した時の膜厚の収縮率が10%以下であることを特徴とする半導体装置。

- 絶縁膜内に形成された複数の埋め込み配線と、前記各埋め込み配線間に形 成された、前記絶縁膜は、複数の絶縁膜の積層膜からなり、最上層の絶縁膜が酸化珪素膜よりも誘電率が低い低誘電率膜であって、前記低誘電率膜は、少なくとも珪素,酸素,炭素のすべてを含み、酸素原子数が珪素原子数の1.5倍以上であり、かつ炭素原子数が珪素原子の1倍以上2倍以下であり、かつ膜の内部まで十分に酸化した時の膜厚の収縮率が10%以下であることを特徴とする半導体装置。

Priority Applications (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2000013895A JP3615979B2 (ja) | 2000-01-18 | 2000-01-18 | 半導体装置及びその製造方法 |

| TW090101031A TW513763B (en) | 2000-01-18 | 2001-01-17 | Semiconductor device and process for producing the same |

| US09/760,777 US6358838B2 (en) | 2000-01-18 | 2001-01-17 | Semiconductor device and process for producing the same |

| KR1020010002929A KR100689917B1 (ko) | 2000-01-18 | 2001-01-18 | 반도체 장치 및 그 제조 방법 |

| US10/050,859 US6680541B2 (en) | 2000-01-18 | 2002-01-18 | Semiconductor device and process for producing the same |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2000013895A JP3615979B2 (ja) | 2000-01-18 | 2000-01-18 | 半導体装置及びその製造方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2001203200A JP2001203200A (ja) | 2001-07-27 |

| JP2001203200A5 JP2001203200A5 (ja) | 2004-12-24 |

| JP3615979B2 true JP3615979B2 (ja) | 2005-02-02 |

Family

ID=18541427

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2000013895A Expired - Fee Related JP3615979B2 (ja) | 2000-01-18 | 2000-01-18 | 半導体装置及びその製造方法 |

Country Status (4)

| Country | Link |

|---|---|

| US (2) | US6358838B2 (ja) |

| JP (1) | JP3615979B2 (ja) |

| KR (1) | KR100689917B1 (ja) |

| TW (1) | TW513763B (ja) |

Families Citing this family (33)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2000174123A (ja) * | 1998-12-09 | 2000-06-23 | Nec Corp | 半導体装置及びその製造方法 |

| US6500752B2 (en) * | 2000-07-21 | 2002-12-31 | Canon Sales Co., Inc. | Semiconductor device and semiconductor device manufacturing method |

| JP4270865B2 (ja) * | 2000-08-18 | 2009-06-03 | 三菱電機株式会社 | 実装基板及び実装基板を用いたバルブソケット |

| JP2002329722A (ja) * | 2001-04-27 | 2002-11-15 | Nec Corp | 半導体装置及びその製造方法 |

| US6699792B1 (en) * | 2001-07-17 | 2004-03-02 | Advanced Micro Devices, Inc. | Polymer spacers for creating small geometry space and method of manufacture thereof |

| US6887780B2 (en) * | 2001-08-31 | 2005-05-03 | Intel Corporation | Concentration graded carbon doped oxide |

| JP3913638B2 (ja) * | 2001-09-03 | 2007-05-09 | 東京エレクトロン株式会社 | 熱処理方法及び熱処理装置 |

| JP2003092349A (ja) * | 2001-09-18 | 2003-03-28 | Mitsubishi Electric Corp | 半導体装置およびその製造方法 |

| JP4063619B2 (ja) * | 2002-03-13 | 2008-03-19 | Necエレクトロニクス株式会社 | 半導体装置の製造方法 |

| JP3516446B2 (ja) | 2002-04-26 | 2004-04-05 | 東京応化工業株式会社 | ホトレジスト剥離方法 |

| US7071112B2 (en) * | 2002-10-21 | 2006-07-04 | Applied Materials, Inc. | BARC shaping for improved fabrication of dual damascene integrated circuit features |

| US6867126B1 (en) * | 2002-11-07 | 2005-03-15 | Taiwan Semiconductor Manufacturing Company, Ltd. | Method to increase cracking threshold for low-k materials |

| US20040152295A1 (en) * | 2003-02-03 | 2004-08-05 | International Business Machines Corporation | Sacrificial metal liner for copper |

| US7279410B1 (en) | 2003-03-05 | 2007-10-09 | Advanced Micro Devices, Inc. | Method for forming inlaid structures for IC interconnections |

| US8137764B2 (en) * | 2003-05-29 | 2012-03-20 | Air Products And Chemicals, Inc. | Mechanical enhancer additives for low dielectric films |

| US6767827B1 (en) | 2003-06-11 | 2004-07-27 | Advanced Micro Devices, Inc. | Method for forming dual inlaid structures for IC interconnections |

| US6919636B1 (en) * | 2003-07-31 | 2005-07-19 | Advanced Micro Devices, Inc. | Interconnects with a dielectric sealant layer |

| TWI285938B (en) * | 2003-08-28 | 2007-08-21 | Fujitsu Ltd | Semiconductor device |

| JP4282493B2 (ja) * | 2004-01-15 | 2009-06-24 | 株式会社東芝 | 膜形成方法及び基板処理装置 |

| TW200605220A (en) * | 2004-06-21 | 2006-02-01 | Hitachi Chemical Co Ltd | Organic siloxane film, semiconductor device using same, flat panel display and raw material liquid |

| JP4854938B2 (ja) | 2004-07-06 | 2012-01-18 | ルネサスエレクトロニクス株式会社 | 半導体装置およびその製造方法 |

| US7202564B2 (en) * | 2005-02-16 | 2007-04-10 | International Business Machines Corporation | Advanced low dielectric constant organosilicon plasma chemical vapor deposition films |

| US7332428B2 (en) * | 2005-02-28 | 2008-02-19 | Infineon Technologies Ag | Metal interconnect structure and method |

| US7214612B2 (en) * | 2005-08-31 | 2007-05-08 | United Microelectronics Corp. | Dual damascene structure and fabrication thereof |

| US7410899B2 (en) * | 2005-09-20 | 2008-08-12 | Enthone, Inc. | Defectivity and process control of electroless deposition in microelectronics applications |

| JP5154009B2 (ja) * | 2005-10-21 | 2013-02-27 | 株式会社ジャパンディスプレイイースト | 有機シロキサン系絶縁膜の製造方法、及び、この製造方法で製造した有機シロキサン系絶縁膜を層間絶縁として用いた液晶表示装置の製造方法 |

| US8043957B2 (en) | 2006-05-17 | 2011-10-25 | Nec Corporation | Semiconductor device, method for manufacturing semiconductor device and apparatus for manufacturing semiconductor |

| US8637396B2 (en) * | 2008-12-01 | 2014-01-28 | Air Products And Chemicals, Inc. | Dielectric barrier deposition using oxygen containing precursor |

| EP2306506B1 (en) * | 2009-10-01 | 2013-07-31 | ams AG | Method of producing a semiconductor device having a through-wafer interconnect |

| JP2013020530A (ja) * | 2011-07-13 | 2013-01-31 | Dainippon Printing Co Ltd | タッチセンサパネル部材、タッチセンサパネル部材を備えた表示装置、及びタッチセンサパネル部材の製造方法 |

| US10319630B2 (en) * | 2012-09-27 | 2019-06-11 | Stmicroelectronics, Inc. | Encapsulated damascene interconnect structure for integrated circuits |

| US8980740B2 (en) | 2013-03-06 | 2015-03-17 | Globalfoundries Inc. | Barrier layer conformality in copper interconnects |

| KR102756671B1 (ko) * | 2019-02-21 | 2025-01-17 | 삼성디스플레이 주식회사 | 감광성 수지 조성물, 이를 이용한 표시 장치 및 표시 장치의 제조 방법 |

Family Cites Families (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5407529A (en) * | 1992-03-04 | 1995-04-18 | Nec Corporation | Method for manufacturing semiconductor device |

| EP0686680A4 (en) * | 1993-12-27 | 1996-07-24 | Kawasaki Steel Co | INSULATING FILM FOR SEMICONDUCTOR DEVICES, COATING FLUID USED TO FORM THE FILM, AND PROCESS FOR PRODUCING SAID FILM |

| US6326318B1 (en) * | 1995-09-14 | 2001-12-04 | Sanyo Electric Co., Ltd. | Process for producing semiconductor devices including an insulating layer with an impurity |

| US5989998A (en) * | 1996-08-29 | 1999-11-23 | Matsushita Electric Industrial Co., Ltd. | Method of forming interlayer insulating film |

| JP3726226B2 (ja) | 1998-02-05 | 2005-12-14 | 日本エー・エス・エム株式会社 | 絶縁膜及びその製造方法 |

| US6054379A (en) * | 1998-02-11 | 2000-04-25 | Applied Materials, Inc. | Method of depositing a low k dielectric with organo silane |

| US6068884A (en) * | 1998-04-28 | 2000-05-30 | Silcon Valley Group Thermal Systems, Llc | Method of making low κ dielectric inorganic/organic hybrid films |

| US6383951B1 (en) * | 1998-09-03 | 2002-05-07 | Micron Technology, Inc. | Low dielectric constant material for integrated circuit fabrication |

| US6255232B1 (en) * | 1999-02-11 | 2001-07-03 | Taiwan Semiconductor Manufacturing Company | Method for forming low dielectric constant spin-on-polymer (SOP) dielectric layer |

| US6312793B1 (en) * | 1999-05-26 | 2001-11-06 | International Business Machines Corporation | Multiphase low dielectric constant material |

| US6225238B1 (en) * | 1999-06-07 | 2001-05-01 | Allied Signal Inc | Low dielectric constant polyorganosilicon coatings generated from polycarbosilanes |

| EP1077479A1 (en) * | 1999-08-17 | 2001-02-21 | Applied Materials, Inc. | Post-deposition treatment to enchance properties of Si-O-C low K film |

| US6365528B1 (en) * | 2000-06-07 | 2002-04-02 | Lsi Logic Corporation | Low temperature process for forming a low dielectric constant fluorine and carbon-containing silicon oxide dielectric-material characterized by improved resistance to oxidation and good gap-filling capabilities |

-

2000

- 2000-01-18 JP JP2000013895A patent/JP3615979B2/ja not_active Expired - Fee Related

-

2001

- 2001-01-17 US US09/760,777 patent/US6358838B2/en not_active Expired - Lifetime

- 2001-01-17 TW TW090101031A patent/TW513763B/zh not_active IP Right Cessation

- 2001-01-18 KR KR1020010002929A patent/KR100689917B1/ko not_active Expired - Fee Related

-

2002

- 2002-01-18 US US10/050,859 patent/US6680541B2/en not_active Expired - Lifetime

Also Published As

| Publication number | Publication date |

|---|---|

| KR100689917B1 (ko) | 2007-03-09 |

| US20010009295A1 (en) | 2001-07-26 |

| TW513763B (en) | 2002-12-11 |

| JP2001203200A (ja) | 2001-07-27 |

| US20020105085A1 (en) | 2002-08-08 |

| US6680541B2 (en) | 2004-01-20 |

| KR20010076349A (ko) | 2001-08-11 |

| US6358838B2 (en) | 2002-03-19 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP3615979B2 (ja) | 半導体装置及びその製造方法 | |

| TW432476B (en) | A silicon carbide deposition for use as a barrier layer and an etch stop | |

| US7763979B2 (en) | Organic insulating film, manufacturing method thereof, semiconductor device using such organic insulating film and manufacturing method thereof | |

| JP4090740B2 (ja) | 集積回路の作製方法および集積回路 | |

| KR100696033B1 (ko) | 반도체 기판 프로세싱 방법 | |

| US20030089992A1 (en) | Silicon carbide deposition for use as a barrier layer and an etch stop | |

| JP4068072B2 (ja) | 半導体装置及びその製造方法 | |

| WO2000054329A1 (en) | Semiconductor device and production method therefor | |

| US7960279B2 (en) | Semiconductor device and manufacturing method therefor | |

| US20030001278A1 (en) | Method for manufacturing a semiconductor device and a semiconductor device | |

| JP5174435B2 (ja) | ウェットエッチングアンダカットを最小にし且つ超低k(k<2.5)誘電体をポアシーリングする方法 | |

| JP2010267971A (ja) | 窒素含有前駆物質を用いる誘電体バリアの堆積 | |

| CN1186814C (zh) | 扩散阻挡层和带扩散阻挡层的半导体器件及其制造方法 | |

| JP3768480B2 (ja) | 半導体装置及びその製造方法 | |

| US6905909B2 (en) | Ultra low dielectric constant thin film | |

| CN1881577B (zh) | 半导体器件及其制造方法 | |

| JP3184177B2 (ja) | 層間絶縁膜の形成方法、半導体製造装置、及び半導体装置 | |

| JP2006024668A (ja) | 半導体装置の製造方法 | |

| JP4882893B2 (ja) | 半導体装置の製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20040114 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20040114 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20040114 |

|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20040309 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20041005 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20041012 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20041102 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313117 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20071112 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20081112 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20081112 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20091112 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20101112 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111112 Year of fee payment: 7 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111112 Year of fee payment: 7 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111112 Year of fee payment: 7 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111112 Year of fee payment: 7 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121112 Year of fee payment: 8 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121112 Year of fee payment: 8 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131112 Year of fee payment: 9 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| LAPS | Cancellation because of no payment of annual fees |