JP3614840B2 - 半導体装置 - Google Patents

半導体装置 Download PDFInfo

- Publication number

- JP3614840B2 JP3614840B2 JP2002345641A JP2002345641A JP3614840B2 JP 3614840 B2 JP3614840 B2 JP 3614840B2 JP 2002345641 A JP2002345641 A JP 2002345641A JP 2002345641 A JP2002345641 A JP 2002345641A JP 3614840 B2 JP3614840 B2 JP 3614840B2

- Authority

- JP

- Japan

- Prior art keywords

- integrated circuit

- semiconductor device

- wiring

- semiconductor chip

- sealing resin

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000004065 semiconductor Substances 0.000 title claims description 70

- 229920005989 resin Polymers 0.000 claims description 32

- 239000011347 resin Substances 0.000 claims description 32

- 238000007789 sealing Methods 0.000 claims description 31

- 230000001681 protective effect Effects 0.000 claims description 16

- 238000006243 chemical reaction Methods 0.000 claims description 6

- 238000000034 method Methods 0.000 description 18

- 238000010586 diagram Methods 0.000 description 11

- 238000004519 manufacturing process Methods 0.000 description 8

- 229910000679 solder Inorganic materials 0.000 description 8

- 230000015572 biosynthetic process Effects 0.000 description 7

- 238000004806 packaging method and process Methods 0.000 description 7

- 238000007747 plating Methods 0.000 description 6

- 239000000758 substrate Substances 0.000 description 4

- 238000003384 imaging method Methods 0.000 description 3

- 239000007788 liquid Substances 0.000 description 3

- 230000003287 optical effect Effects 0.000 description 3

- 238000004544 sputter deposition Methods 0.000 description 3

- 239000000919 ceramic Substances 0.000 description 2

- 230000000295 complement effect Effects 0.000 description 2

- 238000007688 edging Methods 0.000 description 2

- 229910044991 metal oxide Inorganic materials 0.000 description 2

- 150000004706 metal oxides Chemical class 0.000 description 2

- 230000002093 peripheral effect Effects 0.000 description 2

- 238000000206 photolithography Methods 0.000 description 2

- 239000004033 plastic Substances 0.000 description 2

- 238000005498 polishing Methods 0.000 description 2

- 230000000694 effects Effects 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 239000003822 epoxy resin Substances 0.000 description 1

- 238000005530 etching Methods 0.000 description 1

- 239000011521 glass Substances 0.000 description 1

- 239000000463 material Substances 0.000 description 1

- 238000002161 passivation Methods 0.000 description 1

- 229920000647 polyepoxide Polymers 0.000 description 1

- 229920001721 polyimide Polymers 0.000 description 1

- 238000004528 spin coating Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14601—Structural or functional details thereof

- H01L27/14618—Containers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14601—Structural or functional details thereof

- H01L27/14634—Assemblies, i.e. Hybrid structures

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/4805—Shape

- H01L2224/4809—Loop shape

- H01L2224/48091—Arched

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/481—Disposition

- H01L2224/48151—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/48221—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/48245—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being metallic

- H01L2224/48247—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being metallic connecting the wire to a bond pad of the item

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14601—Structural or functional details thereof

- H01L27/14625—Optical elements or arrangements associated with the device

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/30—Technical effects

- H01L2924/301—Electrical effects

- H01L2924/3025—Electromagnetic shielding

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L31/00—Semiconductor devices sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L31/02—Details

- H01L31/0203—Containers; Encapsulations, e.g. encapsulation of photodiodes

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L31/00—Semiconductor devices sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L31/02—Details

- H01L31/0232—Optical elements or arrangements associated with the device

Description

【発明が属する技術分野】

本発明は、光電変換素子(例えば、CCD(電荷結合素子),CMOS(相補性金属酸化膜半導体)センサなどの固体撮像素子、受光素子等)から構成される受光領域を集積回路に含む半導体装置に関する。

【0002】

【従来の技術】

従来、光電変換素子(例えば、固体撮像素子、受光素子等)を集積回路(受光領域)に含む半導体装置のパッケージングの形態としては、プラスチックパッケージ、セラミックパッケージと呼ばれるパーッケージがある。例えば、図13に示すような形態がある(特開平6−5665号公報参照)。この形態は、セラミックやプラスチックなどのケース70と、ケース70の内部から外部へと張出して延在する外部リード72とを有している。ケース70内には、個片化された半導体チップ74が収納されており、半導体チップ74上の電極パッド76とケース70内に位置する外部リード72との間はボンディングワイヤー78によって接続されている。半導体チップ74の受光領域(集積回路)には光電変換素子(図示せず)が形成されており、この受光領域上方に位置する部分には、光を透過する透明なキャップ80が設けられている。

【0003】

しかしながら、上記構成のパッケージは、外部リード72がケース70外壁から張出しているため、パッケージ全体に示す張出し部分の割合が大きくなってしう。このため、携帯電話、ハンディカメラなどといった、小さな空間に多数の部品を搭載しなければならない装置においては、このようなパッケージを使用することは困難となっていている。

【0004】

昨今、このような、電子機器の小型化に伴い、半導体装置を搭載する際、高密度搭載を可能にするため、半導体チップとほぼ同一のサイズをもつCSP(チップサイズパッケージ)と称するパッケージが提案されてきている。しかし、受光領域を有する半導体装置には、受光領域上に絶縁層や再層などを積層する必要があるため、そのまま適用することが出来ないと問題がある。

【0005】

このような問題を改善する目的で、例えば、特開2002−198463号公報には、受光領域を含む集積回路が形成された半導体チップの表面から側面或いは裏面にかけて接続配線が形成された半導体装置(CSP)が提案されている。この半導体装置(CSP)は、接続配線を、半導体チップの表面から側面或いは裏面にかけて形成することで、例えば、実装基板上などに集積回路(受光領域)が形成された表面を外側にして受光可能なように半導体装置を搭載させることができ、ウエハレベルCSPとして、超小型実装を実現している。

【0006】

【特許文献1】

特開平6−5665号公報

【特許文献2】

特開2002−198463号公報

【0007】

【発明が解決しようとする課題】

しかしながら、上記提案では、超小型実装を実現しているが、集積回路(受光領域)上には絶縁層が設けられているのみであり、さらに集積回路上に保護膜を形成する形態も記載されているが、パッケージングされた一つの部品として取り扱うことを考慮すると、耐久性については未だ不充分であるのが現状である。

【0008】

従って、本発明は、前記従来における諸問題を解決し、以下の目的を達成することを課題とする。即ち、本発明の目的は、受光領域を集積回路に含む半導体装置であって、超小型実装を実現しつつ、高い耐久性を有する半導体装置を提供することである。

【0009】

【課題を解決するための手段】

上記課題は、以下の手段により解決される。即ち、本発明は、

(1) 光電変換素子を含む集積回路が、表面に形成された半導体チップと、

前記半導体チップの集積回路及び外部端子の間を電気的に接続する第1の配線と、

前記半導体チップ表面及び前記第1の配線を封止すると共に、前記集積回路面上を開口するように形成された封止樹脂と、

前記封止樹脂の開口を覆う光透過性キャップと、

を備え、

且つ前記第1の配線として、前記集積回路周縁付近に形成されると共に、先端に段差が設けられた複数の柱状電極を備え、

前記光透過性キャップは、前記封止樹脂の開口を覆うと共に、前記柱状電極の段差に係合して設けられることを特徴とする半導体装置。

【0010】

(2) 前記光透過性キャップには、前記第1の配線及び外部端子の間を電気的に接続する第2の配線が設けられることを特徴とする前記(1)に記載の半導体装置。

【0011】

(3) 前記半導体チップ表面には、その集積回路面上が開口するように形成された保護膜が設けられることを特徴とする前記(1)に記載の半導体装置。

【0012】

(4) 前記(1)〜(3)のいずれかに記載の半導体装置を備えることを特徴とする光学装置。

【0013】

【発明の実施の形態】

以下、本発明の実施の形態を図面を参照して説明する。なお、実質的に同様の機能を有するものには、全図面通して同じ符号を付して説明し、場合によってはその説明を省略することがある。

【0014】

(第1の実施の形態)

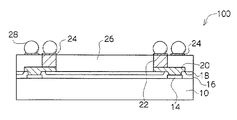

図1は、第1の実施の形態に係る半導体装置の構造を示す概略構成図であり、(a)は平面図であり、(b)は断面図である。図2は、第1の実施の形態に係る半導体装置の製造方法を説明する断面図である。

【0015】

図1に示す半導体装置100は、光電変換素子(例えば、CCD(電荷結合素子),CMOS(相補性金属酸化膜半導体)センサなどの固体撮像素子、受光素子等)を含む集積回路(ここで集積回路は、光電変化素子を含むため、以降、受光領域ということがある:図中、12で示される領域)が表面に形成された半導体チップ10を有する。半導体チップ10上には、集積回路と電気的に接続された電極14が形成されており、電極14を有する以外の部分に絶縁膜16(例えばパッシベーション膜)、保護膜18(例えばポリイミド膜)が順次形成されている。

【0016】

また、半導体装置100には、電極14から引き回した再配線層20と、再配線層20上に外部接続用パッド24と電気的に接続するためのバンプ22が形成されている。バンプ22は、集積回路周縁付近に形成されると共に、先端に段差22aが設けられており、半導体チップ10は、集積回路面上を開口するように再配線層20及びバンプ22周辺を封止樹脂26により封止されている。そして、光透過性キャップ30が、バンプ22先端の段差22aに係合し、封止樹脂26の開口を覆うように配設されている。

【0017】

ここで、光透過性キャップは、ガラスや、透明樹脂などにより構成することができ、紫外線カットフィルター機能を持つ材料により構成されていてもよい。また、受光領域に焦点を合わせられれば、レンズとしての機能させてもよい。

【0018】

そして、バンプ22と電気的に接続するように形成されたパッド24上に、外部接続端子として半田ボール28が形成されている。

【0019】

なお、図中では、半田ボール28は、2列で配設されているが、これに限られず、図3に示すように、3列やそれ以上で配設されていてもよい。

【0020】

以下、図1に示す半導体装置100の製造方法の一例を示す。

まず、半導体チップ10となる素子の集積回路が形成されウエハ32を電気特性を評価して後、準備する(図2(a))。電極14上の絶縁膜16が除去されたウエハ32上に保護膜18をスピンコートなどにより塗布し、電極14のコンタクトをとるため、マスクをかけて露光して、保護膜18のエッチングを行なう(図2(b))。スパッタ、メッキ等により電極14から引き回すための配線、及びバンプ22形成のためのベースとしての再配線層20を形成する(図2(c))。

【0021】

次に、バンプ22を形成するために、ウエハ32上にレジストを塗布し、マスクをかけ、露光後エッチングしてレジストに開口を形成する。そして、メッキなどによりバンプ22を形成して、レジストを除去して洗浄する(図2(d))。ここで、バンプ22先端には、光透過性キャップ30を嵌め込むための段差22aを形成するが、この段差形成方法としては、例えば、エッジングによりバンプ22の一部先端を除去する方法や、所定の高さまでバンプ22形成し、さらにバンプ22の一部先端のみバンプ22形成を行なう2段階に分けてバンプ22を形成する方法(例えば2段めっき)などが、好適に実施される。

【0022】

次に、集積回路面上を開口するように再配線層20及びバンプ22周辺を封止樹脂26により封止する(図2(e))。ここで、封止樹脂26により集積回路面上を開口するように封止する方法としては、例えば、図4に示すように、ウエハ32全体を覆い且つ表面に凸部34aを有する治具34を用いる方法が挙げられる。この方法では、凸部34aを集積回路形成領域に当該集積回路面に当接すると共にバンプ22側壁から段差22aかけて当接するように嵌め込んで、治具34を配設し、ウエハ32と治具34との間隙、即ちウエハ32の横側(図中矢印)から液状の封止樹脂26を注入し、封止する。また、他の方法としては、図5に示すように、集積回路形成領域毎に、当該集積回路面に当接すると共にバンプ22側壁から段差22aかけて当接するように嵌め込む治具36を用い、ウエハ32上面から液状の封止樹脂26を滴下して封止する方法や、図6に示すように、集積回路周縁に形成された複数のバンプ22間の間隙を塞ぐ突起を有する枠38を用い、ウエハ32上面から液状の封止樹脂26を滴下して封止する方法なども好適に実施される。また、図示しないが、一旦、封止樹脂26によりウエハ32全面を封止し、その後、フォトリソグラフィ処理などにより、集積回路形成領域をエッジングして開口させて封止する方法も挙げられる。

【0023】

そして、封止樹脂26により封止した後、ウエハ32上面から研磨機40などにより切削(バイト、砥石、バフ等)して、表面グラインド(表面研磨)を行い、封止樹脂26によって隠れたバンプ22を露出させる(図2(f))。

【0024】

次に、光透過性キャップを、バンプ22先端の段差22aに嵌め込めこみ、封止樹脂26の開口を覆う(図2(g))。

【0025】

その後、バンプ22先端及び光透過性キャップ周縁の一部に、スパッタやメッキによりパッド24を形成し(図2(h))、さらにパッド24上に半田ボール28を形成する(図2(i))。そして、最後に、そして、テスト後、スクライブにて個片して、半導体装置100が得られる(図2(j))。

【0026】

本実施形態では、集積回路周辺の再配線層20及びバンプ22は封止樹脂26されており、集積回路(受光領域)の上方(集積回路面の法線方向)には光透過性キャップ30が設けられ、半導体チップ10とほぼ同等の大きさでパッケージングされた構成としている。光透過性キャップ30を設けることで、半導体チップ10における集積回路を外部から遮蔽すると共に光が受光領域(集積回路)に照射可能となる。このため、受光領域を集積回路に含む半導体装置であっても、超小型実装を実現しつつ、耐久性を向上させることができる。

【0027】

また、本実施形態では、光透過性キャップ30を、集積回路周縁部付近に形成されたバンプ22の段差22aに嵌め込んで配設しているので、バンプ22の段差22aにより光透過性キャップ30の位置ズレなどが生じ難く、衝撃などに対して強く、耐久性が向上する。

【0028】

また、本実施形態では、殆どの製造工程をウエハ状態で一括して処理、即ち、ウエハーレベルCSPの技術を利用して製造することが可能であり、コストダウンを図ることが可能となる。

【0029】

(第2の実施の形態)

図7は、第2の実施の形態に係る半導体装置を示す構成図であり、(a)は平面図であり、(b)は断面図である。

【0030】

本実施形態は、集積回路(受光領域)上に開口18aを設けた保護膜18が設けられており、これ以外の構成は第1の実施の形態と同様の構成である。保護膜18に開口18aを設ける方法としては、例えば、第1の実施の形態で説明した製造工程において、保護膜18形成時(図2(b)参照)においてマスクを用いて選択的に保護膜18を形成し、開口18aを設ける方法や、再配線層20形成後(図2(c)参照)、フォトリソグラフィ処理などにより、集積回路形成領域をエッジングして保護膜18に開口18aを設ける方法や、などがある。

【0031】

通常、この回路付近に誘電率の高い樹脂膜(第1の実施の形態では絶縁膜16、保護膜18)が存在すると、回路の電流が流れ難くなる。これは、回路に電流が流れる際に発生する磁界を、誘電率の高い絶縁膜(通常、樹脂の誘電率は約4である)が妨げ、その結果、回路の抵抗が増大するためである。

【0032】

そこで、本実施形態では、集積回路付近に存在する、抵抗増大に起因する樹脂膜のうち、保護膜18を除去することで、少しでも空気の誘電率1に近づけ、より半導体装置の高速高周波対応を図ることができる。

【0033】

(第3の実施の形態)

図8は、第3の実施の形態に係る半導体装置を示す構成図であり、(a)は平面図であり、(b)は断面図である。

【0034】

本実施形態は、光透過性キャップ30が、配線基板30aと配線基板30a中央部に組み込まれたキャップ30bとから構成された形態である。配線基板30aの周縁部にはバンプ22とパッド24とを電気的に接続するため、スルーホールなどを設けて表裏に導通させた配線30cが設けられている。この配線30cは、通常のプリント基板と同様な配線パターンが形成される。また、この配線基板30aは多層配線構造であってもよい。光透過性キャップ30は、例えば、任意の配線パターンが施され、ソルダーレジスト等の保護膜が形成された配線基板30aの中央部に開口を設け、当該開口にキャップ30bを嵌め込むことで、容易に作製することができる。

【0035】

また、光透過性キャップ30(配線基板30a)とバンプとの接続は、例えば、Snメッキなどにより端子を配線基板30aに形成し、この端子とバンプ22とを熱圧着することで行なわれる。そして、第1の実施の形態と同様に、配線基板30aの配線30cと電気的に接続するように、スパッタやメッキなどによりパッド24を形成する。

【0036】

本実施形態では、光透過性キャップ30の一部を、予め配線パターンが施された配線基板30aで構成するため、バンプ22(半田ボール28)の配置位置(形成位置)の自由度が増す。

【0037】

また、本実施形態では、予め配線パターンが施された配線基板30aで構成される光透過性キャップ30を用いるため、殆どの製造工程をウエハ状態で一括して処理、即ち、ウエハーレベルCSPの技術を利用して製造することが可能であり、コストダウンを図ることが可能となる。

【0038】

また、本実施形態では、配線基板30aに予めバンプ22が形成されていれば、第1の実施の形態におけるバンプ22形成(図2(h)参照)を省くことも可能であり、よりコストダウンを図ることが可能となる。

【0039】

(第4の実施の形態)

図9は、第4の実施の形態に係る半導体装置を示す構成図であり、(a)は平面図であり、(b)は断面図である。

【0040】

本実施形態は、集積回路(受光領域)上に開口18aを設けた保護膜18が設けられており、これ以外の構成は第3の実施の形態と同様の構成である。

【0041】

本実施形態では、第2の実施形態と同様に、集積回路付近に存在する、抵抗増大に起因する樹脂膜のうち、保護膜18を除去することで、少しでも空気の誘電率1に近づけ、より半導体装置の高速高周波対応を図ることができる。

【0042】

(参考例)

図10は、参考例に係る半導体装置を示す断面図である。

【0043】

本参考例は、封止樹脂26として、例えば、エポキシ樹脂などの光透過性樹脂を用い、半導体チップ10上全面を封止した形態である。

【0044】

本参考例では、半導体チップ全面が光透過性の封止樹脂26により封止され、半導体チップ10とほぼ同等の大きさでパッケージングされた構成としている。光透過性の封止樹脂26により封止することで、半導体チップ10における集積回路を外部から遮蔽すると共に光が受光領域(集積回路)に照射可能となる。このため、受光領域を集積回路に含む半導体装置であっても、超小型実装を実現しつつ、耐久性を向上させることができる。

【0045】

また、本参考例は、第1の実施の形態に比べ、光透過性の封止樹脂26により封止する構造なため、より薄膜化が可能となる。

【0046】

また、本参考例は、第1の実施の形態に比べ、バンプ22の段差22a形成や、光透過性キャップ30の嵌め込み工程などが省かれ、よりコストダウンが図れる。

【0047】

(第5の実施の形態)

図11は、第5の実施の形態に係るカメラモジュールを示す概略構成図である。

【0048】

図11に示すカメラモジュール50(光学装置)は、レンズ56と、光軸後方に配置されるセンサ52と、入力されたデジタル信号に対して所定のデジタル信号処理を行うDSP54(Digital Signal Processor)と、筐体58と、から構成されている。センサ52及びDSP54は実装基板60に実装されており、センサ52は、図12に示すように、実装基板60に設けられた開口60aを介して受光するよう、受光領域(集積回路)を実装基板側に対面させて実装している。また、図示しないが、センサ52は、入力されたアナログ信号をデジタル信号に変換するアナログ/デジタル変換器を介してDSP54に接続されている。なお、図中、煩雑さを避けるため、その他の部材や配線は省略している。

【0049】

本実施形態では、このような構成のカメラモジュールのセンサ52として、上記第1乃至4の実施の形態に係る半導体装置100を適用させる。このため、センサ52を超小型実装可能となり、モジュールの小型化が図れ、また、耐久性を向上させることが可能となる。

【0050】

このように、本実施形態で示されるカメラモジュール50は、小型化が進んでいる、携帯電話、ハンディカメラなどといった電子機器に好適に適用可能である。

【0051】

なお、上記何れの実施の形態においても、限定的に解釈されるものではなく、本発明の要件を満足する範囲内で実現可能であることは、言うまでもない。

【0052】

【発明の効果】

以上、本発明によれば、受光領域を集積回路に含む半導体装置に、超小型実装を実現しつつ、高い耐久性を付与することが可能となる。

【図面の簡単な説明】

【図1】第1の実施の形態に係る半導体装置の構造を示す概略構成図であり、(a)は平面図であり、(b)は断面図である。

【図2】第1の実施の形態に係る半導体装置の製造方法を説明する断面図である。

【図3】第1の実施の形態に係る半導体装置における半田ボールの配置位置の他の一例を示す平面図である。

【図4】第1の実施の形態に係る半導体装置における封止樹脂を形成する方法の一例を説明する断面図である。

【図5】第1の実施の形態に係る半導体装置における封止樹脂を形成する方法の他のを説明する説明図であり、(a)は断面図であり、(b)は平面図である。

【図6】第1の実施の形態に係る半導体装置における封止樹脂を形成する方法の他のを説明する説明図であり、(a)は断面図であり、(b)は平面図である。

【図7】第2の実施の形態に係る半導体装置を示す構成図であり、(a)は平面図であり、(b)は断面図である。

【図8】第3の実施の形態に係る半導体装置を示す構成図であり、(a)は平面図であり、(b)は断面図である。

【図9】第4の実施の形態に係る半導体装置を示す構成図であり、(a)は平面図であり、(b)は断面図である。

【図10】参考例に係る半導体装置を示す断面図である。

【図11】第5の実施の形態に係るカメラモジュールを示す概略構成図である。

【図12】第5の実施の形態に係るカメラモジュールにおけるセンサの配設位置について説明する拡大図である。

【図13】従来の半導体装置を示す概略構成図である。

【符号の説明】

100 半導体装置

10 半導体チップ

14 電極(第1の配線)

16 絶縁膜

18 保護膜

20 再配線層(第1の配線)

22 バンプ(第1の配線:柱状電極)

24 パッド

26 封止樹脂

28 半田ボール(外部端子)

30 光透過性キャップ

32 ウエハ

50 カメラモジュール

52 センサ

56 レンズ

58 筐体

60 実装基板

Claims (3)

- 光電変換素子を含む集積回路が、表面に形成された半導体チップと、

前記半導体チップの集積回路及び外部端子の間を電気的に接続する第1の配線と、

前記半導体チップ表面及び前記第1の配線を封止すると共に、前記集積回路面上を開口するように形成された封止樹脂と、

前記封止樹脂の開口を覆う光透過性キャップと、

を備え、

且つ前記第1の配線として、前記集積回路周縁付近に形成されると共に、先端に段差が設けられた複数の柱状電極を備え、

前記光透過性キャップは、前記封止樹脂の開口を覆うと共に、前記柱状電極の段差に係合して設けられることを特徴とする半導体装置。 - 前記光透過性キャップには、前記第1の配線及び外部端子の間を電気的に接続する第2の配線が設けられることを特徴とする請求項1に記載の半導体装置。

- 前記半導体チップ表面には、その集積回路面上が開口するように形成された保護膜が設けられることを特徴とする請求項1に記載の半導体装置。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2002345641A JP3614840B2 (ja) | 2002-11-28 | 2002-11-28 | 半導体装置 |

| US10/722,520 US7009295B2 (en) | 2002-11-28 | 2003-11-28 | Semiconductor device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2002345641A JP3614840B2 (ja) | 2002-11-28 | 2002-11-28 | 半導体装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2004179495A JP2004179495A (ja) | 2004-06-24 |

| JP3614840B2 true JP3614840B2 (ja) | 2005-01-26 |

Family

ID=32376018

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2002345641A Expired - Fee Related JP3614840B2 (ja) | 2002-11-28 | 2002-11-28 | 半導体装置 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US7009295B2 (ja) |

| JP (1) | JP3614840B2 (ja) |

Families Citing this family (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7645635B2 (en) * | 2004-08-16 | 2010-01-12 | Micron Technology, Inc. | Frame structure and semiconductor attach process for use therewith for fabrication of image sensor packages and the like, and resulting packages |

| JP4057017B2 (ja) * | 2005-01-31 | 2008-03-05 | 富士通株式会社 | 電子装置及びその製造方法 |

| JP4486005B2 (ja) * | 2005-08-03 | 2010-06-23 | パナソニック株式会社 | 半導体撮像装置およびその製造方法 |

| JP4794354B2 (ja) * | 2006-05-23 | 2011-10-19 | Okiセミコンダクタ株式会社 | 半導体装置の製造方法 |

| JP5330697B2 (ja) * | 2007-03-19 | 2013-10-30 | 株式会社リコー | 機能素子のパッケージ及びその製造方法 |

| US20080265356A1 (en) * | 2007-04-27 | 2008-10-30 | Jin-Chyuan Biar | Chip size image sensing chip package |

| JP2009267122A (ja) | 2008-04-25 | 2009-11-12 | Oki Semiconductor Co Ltd | 半導体装置 |

| US7989950B2 (en) * | 2008-08-14 | 2011-08-02 | Stats Chippac Ltd. | Integrated circuit packaging system having a cavity |

| JP2011128140A (ja) * | 2009-11-19 | 2011-06-30 | Dainippon Printing Co Ltd | センサデバイス及びその製造方法 |

| JP5934109B2 (ja) * | 2010-01-11 | 2016-06-15 | フレクストロニクス エイピー エルエルシーFlextronics Ap,Llc | 成形テープフリップチップ画像装置実装を備えたカメラモジュールおよび製造方法 |

| JP2011210808A (ja) * | 2010-03-29 | 2011-10-20 | Casio Computer Co Ltd | 半導体構成体及び半導体装置 |

| JP5620698B2 (ja) * | 2010-03-29 | 2014-11-05 | 株式会社テラプローブ | 半導体構成体及び半導体構成体の製造方法 |

| CN107425031B (zh) * | 2017-09-05 | 2022-03-01 | 盛合晶微半导体(江阴)有限公司 | 背照式cmos传感器的封装结构及封装方法 |

Family Cites Families (14)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH07112050B2 (ja) * | 1986-07-16 | 1995-11-29 | キヤノン株式会社 | 光半導体装置 |

| JPH0724287B2 (ja) * | 1987-02-12 | 1995-03-15 | 三菱電機株式会社 | 光透過用窓を有する半導体装置とその製造方法 |

| TW332348B (en) * | 1992-06-23 | 1998-05-21 | Sony Co Ltd | Manufacturing method for solid state motion picture device provides a highly accurate and low cost solid state motion picture device by use of empty package made of resin. |

| JPH07297324A (ja) * | 1994-04-25 | 1995-11-10 | Sony Corp | 半導体装置およびその製造方法 |

| JPH0865579A (ja) * | 1994-08-23 | 1996-03-08 | Olympus Optical Co Ltd | 固体撮像装置 |

| US6105245A (en) * | 1997-02-17 | 2000-08-22 | Nippon Steel Semiconductor Corporation | Method of manufacturing a resin-encapsulated semiconductor package |

| JPH10242442A (ja) * | 1997-02-26 | 1998-09-11 | Fuji Photo Film Co Ltd | 撮像素子のチップサイズパッケージ |

| JP2001308349A (ja) * | 2000-04-14 | 2001-11-02 | Hiroaki Hayashi | フォトセンサチップの組立体およびその製造方法 |

| JP2002094035A (ja) | 2000-09-14 | 2002-03-29 | Shinko Electric Ind Co Ltd | 光透過用キャップ及びその製造方法 |

| JP3848080B2 (ja) * | 2000-12-19 | 2006-11-22 | 富士通株式会社 | 半導体装置の製造方法 |

| JP2003233805A (ja) * | 2001-12-04 | 2003-08-22 | Canon Inc | 画像入力装置 |

| JP3766034B2 (ja) * | 2002-02-20 | 2006-04-12 | 富士通株式会社 | 指紋センサ装置及びその製造方法 |

| JP2003282791A (ja) * | 2002-03-20 | 2003-10-03 | Fujitsu Ltd | 接触型センサ内蔵半導体装置及びその製造方法 |

| JP4126389B2 (ja) * | 2002-09-20 | 2008-07-30 | カシオ計算機株式会社 | 半導体パッケージの製造方法 |

-

2002

- 2002-11-28 JP JP2002345641A patent/JP3614840B2/ja not_active Expired - Fee Related

-

2003

- 2003-11-28 US US10/722,520 patent/US7009295B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| US7009295B2 (en) | 2006-03-07 |

| JP2004179495A (ja) | 2004-06-24 |

| US20040104478A1 (en) | 2004-06-03 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US7282693B2 (en) | Camera module for compact electronic equipments | |

| KR100616670B1 (ko) | 웨이퍼 레벨의 이미지 센서 모듈 및 그 제조방법 | |

| US7534656B2 (en) | Image sensor device and method of manufacturing the same | |

| US8513756B2 (en) | Semiconductor package and manufacturing method for a semiconductor package as well as optical module | |

| US6943423B2 (en) | Electronic package of photo-image sensors in cellular phone camera modules, and the fabrication and assembly thereof | |

| US8102039B2 (en) | Semiconductor device and manufacturing method thereof | |

| US7633133B2 (en) | Semiconductor device and manufacturing method of the same | |

| US7576402B2 (en) | Semiconductor device, method of manufacturing the same, and camera module | |

| US7084474B2 (en) | Photosensitive semiconductor package and method for fabricating the same | |

| US20080173792A1 (en) | Image sensor module and the method of the same | |

| JP5078725B2 (ja) | 半導体装置 | |

| US20030218251A1 (en) | Image sensor module and method of fabricating the same | |

| JP3614840B2 (ja) | 半導体装置 | |

| KR20080084759A (ko) | 빌드인 패키지 캐비티를 갖는 이미지 센서 모듈 및 그 방법 | |

| WO2005022631A1 (ja) | 半導体パッケージおよびその製造方法 | |

| US20080231693A1 (en) | Optical device, camera module, mobile phone, digital still camera, and medical endoscope | |

| JP2002198463A (ja) | チップサイズパッケージおよびその製造方法 | |

| KR100494474B1 (ko) | 카메라 모듈 및 그 제조방법 | |

| KR100526191B1 (ko) | 고체 촬상용 반도체 장치 | |

| KR100629467B1 (ko) | 이미지 센서용 패키지 | |

| JP3100560U (ja) | 映像センサーのフリップチップパッケージ構造とその映像センサーモジュール | |

| KR100640336B1 (ko) | 이미지 센서 조립체 | |

| KR200359949Y1 (ko) | 카메라 칩 패키지 | |

| CN116490967A (zh) | 成像装置、电子设备和成像装置的制造方法 | |

| KR19990002582U (ko) | 칩 크기의 패키지 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A975 | Report on accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A971005 Effective date: 20040803 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20040810 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20041001 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20041026 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20041027 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20081112 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20081112 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20091112 Year of fee payment: 5 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20091112 Year of fee payment: 5 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20101112 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20101112 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111112 Year of fee payment: 7 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111112 Year of fee payment: 7 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121112 Year of fee payment: 8 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121112 Year of fee payment: 8 |

|

| S533 | Written request for registration of change of name |

Free format text: JAPANESE INTERMEDIATE CODE: R313533 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121112 Year of fee payment: 8 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| LAPS | Cancellation because of no payment of annual fees |