JP3592870B2 - 半導体装置の製造方法 - Google Patents

半導体装置の製造方法 Download PDFInfo

- Publication number

- JP3592870B2 JP3592870B2 JP34750996A JP34750996A JP3592870B2 JP 3592870 B2 JP3592870 B2 JP 3592870B2 JP 34750996 A JP34750996 A JP 34750996A JP 34750996 A JP34750996 A JP 34750996A JP 3592870 B2 JP3592870 B2 JP 3592870B2

- Authority

- JP

- Japan

- Prior art keywords

- insulating film

- semiconductor substrate

- forming

- film

- conductive film

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000004065 semiconductor Substances 0.000 title claims description 456

- 238000004519 manufacturing process Methods 0.000 title claims description 174

- 238000000034 method Methods 0.000 title description 61

- 239000000758 substrate Substances 0.000 claims description 342

- 239000012535 impurity Substances 0.000 claims description 192

- 238000005530 etching Methods 0.000 claims description 185

- 239000011229 interlayer Substances 0.000 description 110

- 229920002120 photoresistant polymer Polymers 0.000 description 74

- 239000003990 capacitor Substances 0.000 description 57

- 239000010410 layer Substances 0.000 description 42

- 229910052814 silicon oxide Inorganic materials 0.000 description 39

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 37

- 238000005229 chemical vapour deposition Methods 0.000 description 25

- 239000013078 crystal Substances 0.000 description 23

- 230000007547 defect Effects 0.000 description 23

- 230000001681 protective effect Effects 0.000 description 21

- 230000006870 function Effects 0.000 description 18

- 238000009792 diffusion process Methods 0.000 description 15

- 239000007789 gas Substances 0.000 description 12

- 238000002955 isolation Methods 0.000 description 12

- 230000005684 electric field Effects 0.000 description 8

- 229910052581 Si3N4 Inorganic materials 0.000 description 6

- 230000000694 effects Effects 0.000 description 6

- 230000015572 biosynthetic process Effects 0.000 description 5

- 238000005468 ion implantation Methods 0.000 description 5

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 3

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 3

- 229910052796 boron Inorganic materials 0.000 description 3

- 230000001747 exhibiting effect Effects 0.000 description 3

- 230000007257 malfunction Effects 0.000 description 3

- 229910052698 phosphorus Inorganic materials 0.000 description 3

- 239000011574 phosphorus Substances 0.000 description 3

- 229910016570 AlCu Inorganic materials 0.000 description 2

- 229910008484 TiSi Inorganic materials 0.000 description 2

- 229910052785 arsenic Inorganic materials 0.000 description 2

- RQNWIZPPADIBDY-UHFFFAOYSA-N arsenic atom Chemical compound [As] RQNWIZPPADIBDY-UHFFFAOYSA-N 0.000 description 2

- 238000007796 conventional method Methods 0.000 description 2

- 150000002500 ions Chemical class 0.000 description 2

- 230000002093 peripheral effect Effects 0.000 description 2

- 208000032368 Device malfunction Diseases 0.000 description 1

- 229910052681 coesite Inorganic materials 0.000 description 1

- 229910052906 cristobalite Inorganic materials 0.000 description 1

- 230000006698 induction Effects 0.000 description 1

- 238000003475 lamination Methods 0.000 description 1

- 239000000203 mixture Substances 0.000 description 1

- 239000000377 silicon dioxide Substances 0.000 description 1

- 235000012239 silicon dioxide Nutrition 0.000 description 1

- 239000002356 single layer Substances 0.000 description 1

- 229910052682 stishovite Inorganic materials 0.000 description 1

- 229910052905 tridymite Inorganic materials 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/01—Manufacture or treatment

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76801—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing

- H01L21/76802—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing by forming openings in dielectrics

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76801—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing

- H01L21/76829—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing characterised by the formation of thin functional dielectric layers, e.g. dielectric etch-stop, barrier, capping or liner layers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76897—Formation of self-aligned vias or contact plugs, i.e. involving a lithographically uncritical step

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/01—Manufacture or treatment

- H10B12/02—Manufacture or treatment for one transistor one-capacitor [1T-1C] memory cells

- H10B12/03—Making the capacitor or connections thereto

- H10B12/033—Making the capacitor or connections thereto the capacitor extending over the transistor

Landscapes

- Engineering & Computer Science (AREA)

- Manufacturing & Machinery (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Semiconductor Memories (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

- Drying Of Semiconductors (AREA)

- Formation Of Insulating Films (AREA)

Description

【発明の属する技術分野】

この発明は、半導体基板の上方に形成される二層の配線層(ワード線及びビット線)と、上記配線層のさらに上方に形成されるキャパシタと、ビット線及びキャパシタを各々半導体基板に接続するための接続電極と、ワード線をゲート電極とするトランジスタとにより構成される半導体装置の製造方法に関するものである。

【0002】

【従来の技術】

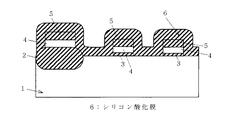

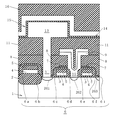

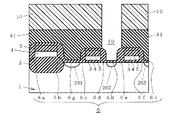

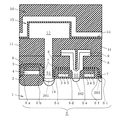

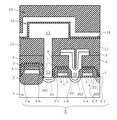

図111〜図122は、従来の技術として半導体装置(DRAM)の製造工程の一例を順に示す断面図である。まず、半導体(例えばSi)基板1上に素子分離絶縁膜2をLOCOS法により形成した後、素子分離絶縁膜2が形成されていない半導体基板1上にゲート酸化膜3、ゲート電極4、絶縁膜5の積層構造を選択的に形成する(図111)。ゲート電極4はDRAMのワード線として機能することとなる。次に、全面に、シリコン酸化膜6をCVD法により例えば数百nmの厚さに形成する(図112)。

【0003】

次に、半導体基板1に垂直な方向にエッチングレートの高い異方性の酸化膜エッチングを行うことにより、ゲート酸化膜3、ゲート電極4、絶縁膜5のそれぞれの側壁部にシリコン酸化膜6を残置させ、サイドウォール6a〜6fを形成する。その後、絶縁膜5及びサイドウォール6a〜6fをマスクとしてイオン注入を行い、半導体基板1内にソース/ドレイン領域261〜263をそれぞれ形成する(図113)。

【0004】

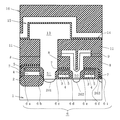

次に、全面にシリコン酸化膜をCVD法により堆積して、層間絶縁膜8を例えば数百nmの厚さに形成する(図114)。次に、層間絶縁膜8上に、所定のパターンを呈するホトレジスト10を通常の転写プロセスにより形成し、このホトレジスト10をマスクとして層間絶縁膜8をエッチングして、コンタクトホール50を形成してソース/ドレイン領域262を露出させる。その後ホトレジスト10を除去する(図115)。

【0005】

次に、例えばWSi/polySi又はTiSi/polySiなどの構造を有する導電性膜9を、コンタクトホール50を介してソース/ドレイン領域262に接続させるように形成する(図116)。この導電性膜9はDRAMのビット線として機能することとなる。

【0006】

次に、全面に、例えばシリコン酸化膜をCVD法により堆積し、層間絶縁膜11を形成し(図117)、層間絶縁膜11上に、所定のパターンを呈するホトレジスト12を通常の転写プロセスにより形成する(図118)。

【0007】

次に、ホトレジスト12をマスクとして、層間絶縁膜11,8を同一のエッチャントを用いてエッチングすることにより、コンタクトホール51を形成してソース/ドレイン領域261を露出させる。その後ホトレジスト12を除去する(図119)。

【0008】

次に、コンタクトホール51を埋めるようにpolySiをCVD法により堆積してキャパシタ下部電極13を形成する。キャパシタ下部電極13はコンタクトホール51を介してソース/ドレイン領域261に接続される。その後、全面にSi3N4膜を堆積してキャパシタ誘電膜14を形成する。さらに、キャパシタ誘電膜14上にpolySiをCVD法により堆積してキャパシタ上部電極15を形成する(図120)。

【0009】

次に、キャパシタ上部電極15上に、例えばシリコン酸化膜からなる層間絶縁膜16をCVD法により形成し(図121)、層間絶縁膜16上に、例えばAlCu、AlSiCuからなる配線層17を選択的に形成する(図122)。

【0010】

【発明が解決しようとする課題】

しかし、このような従来の半導体装置の製造方法によれば、サイドウォール6a〜6fを形成する際に数百nmという厚いシリコン酸化膜をエッチングする必要があるため、エッチングの制御が困難であり、半導体基板1の表面がオーバーエッチングによるダメージを受けていた。さらに、半導体基板1の表面はコンタクトホール50,51を形成する際においてもオーバーエッチングによるダメージを受ける。このようにしてソース/ドレイン領域261,262付近に結晶欠陥25が生じていたため(図113〜図122)、これらはリーク電流を誘発する原因となり、デバイスの誤動作を引き起こすという問題があった。

【0011】

例えば、DRAMにおいてはメモリセルに蓄積されたデータをある一定間隔で書き直す動作(リフレッシュ)を必要とするが、キャパシタ下部電極13が接続されるソース/ドレイン領域261付近に結晶欠陥25が存在すると、キャパシタ下部電極13に蓄積された電荷がリーク電流として半導体基板1へと流失してしまい、正しいデータを書き直すことができなくなるという問題があった。

【0012】

また、ホトレジスト10を形成する工程において、プロセスのばらつき等によりゲート電極4のパターンとホトレジスト10の重ね合せがずれた場合には、図116に示すようにビット線たる導電性膜9とワード線たるゲート電極4とが接触し、デバイスの動作不良を引き起こすという問題もあった。

【0013】

本発明はこのような問題を解決するためになされたものであり、ビット線をワード線と接触させることなく自己整合的に半導体基板に接続させ、かつリーク電流を誘発する原因となる半導体基板の結晶欠陥を生じないような半導体装置の製造方法を提供することを目的とする。

【0014】

【課題を解決するための手段】

この発明のうち請求項1に係る半導体装置の製造方法は、(a)半導体基板の表面上に、第1の導電性膜を選択的に形成する工程と、(b)第1の導電性膜上に、第1の絶縁膜を形成する工程と、(c)工程(a)及び(b)によって得られる構造上に、第2の絶縁膜を形成する工程と、(d)第2の絶縁膜上に、第3の絶縁膜を形成する工程と、(e)第3の絶縁膜上に、第4の絶縁膜を形成する工程と、(f)第4の絶縁膜、第3の絶縁膜、第2の絶縁膜を選択的に、かつ、この順に個別にエッチングして、半導体基板の表面のうち第1の導電性膜が形成されていない第1の位置に存在する部分を露出する工程と、(g)第1の位置において半導体基板と電気的に接触する第2の導電性膜を形成する工程とを備え、第3の絶縁膜は、第4の絶縁膜よりもエッチング速度が遅く、第2の絶縁膜は、第1の導電性膜及び第1の絶縁膜のそれぞれの側壁である第1領域と、半導体基板の表面のうち第1の導電性膜が形成されていない第2領域とに存在し、第1領域に存在する第2の絶縁膜の幅は、第2領域に存在する第2の絶縁膜の膜厚よりも厚く、(x)工程(d)と工程(e)との間に実行され、半導体基板の表面のうち、第1の位置とは異なる、第1の導電性膜が形成されていない第2の位置の上方に存在する第3の絶縁膜を除去する工程と、(y)工程(e)より後の工程において実行され、第2の位置の上方に存在する第4の絶縁膜及び第2の絶縁膜をこの順に連続してエッチングして、半導体基板の表面のうち第2の位置に存在する部分を露出する工程と、(z)第2の位置において半導体基板と電気的に接触する第3の導電性膜を形成する工程と、(s)工程(c)と工程(d)との間に実行され、半導体基板の表面のうち第2の位置に存在する部分から、第2の絶縁膜を通して半導体基板と反対の導電型を有する第1の不純物を導入して第1の不純物領域を形成する工程と、(t)工程(y)と工程(z)との間に実行され、半導体基板の表面のうち第2の位置に存在する部分から、半導体基板と反対の導電型を有する第2の不純物を導入して第2の不純物領域を形成する工程とを更に備え、第2の不純物領域は第1の不純物領域よりも広く、かつ、第2の不純物領域の不純物濃度は第1の不純物領域の不純物濃度よりも低いことを特徴とするものである。

【0015】

また、この発明のうち請求項2に係る半導体装置の製造方法は、(a)半導体基板の表面上に、第1の導電性膜を選択的に形成する工程と、(b)第1の導電性膜上に、第1の絶縁膜を形成する工程と、(c)工程(a)及び(b)によって得られる構造上に、第2の絶縁膜を形成する工程と、(d)第2の絶縁膜上に、第3の絶縁膜を形成する工程と、(e)第3の絶縁膜上に、第4の絶縁膜を形成する工程と、(f)第4の絶縁膜、第3の絶縁膜、第2の絶縁膜を選択的に、かつ、この順に個別にエッチングして、半導体基板の表面のうち第1の導電性膜が形成されていない第1の位置に存在する部分を露出する工程と、(g)第1の位置において半導体基板と電気的に接触する第2の導電性膜を形成する工程とを備え、第3の絶縁膜は、第4の絶縁膜よりもエッチング速度が遅く、第2の絶縁膜は、第1の導電性膜及び第1の絶縁膜のそれぞれの側壁である第1領域と、半導体基板の表面のうち第1の導電性膜が形成されていない第2領域とに存在し、第1領域に存在する第2の絶縁膜の幅は、第2領域に存在する第2の絶縁膜の膜厚よりも厚く、(y)工程(g)より後の工程において実行され、第4の絶縁膜、第3の絶縁膜、第2の絶縁膜を選択的に、かつ、この順に個別にエッチングして、半導体基板の表面のうち、第1の位置とは異なる、第1の導電性膜が形成されていない第2の位置に存在する部分を露出する工程と、(z)第2の位置において半導体基板と電気的に接触する第3の導電性膜を形成する工程と、(s)工程(c)と工程(d)との間に実行され、半導体基板の表面のうち第2の位置に存在する部分から、第2の絶縁膜を通して半導体基板と反対の導電型を有する第1の不純物を導入して第1の不純物領域を形成する工程と、(t)工程(y)と工程(z)との間に実行され、半導体基板の表面のうち第2の位置に存在する部分から、半導体基板と反対の導電型を有する第2の不純物を導入して第2の不純物領域を形成する工程とを更に備え、第2の不純物領域は第1の不純物領域よりも広く、かつ、第2の不純物領域の不純物濃度は第1の不純物領域の不純物濃度よりも低いことを特徴とするものである。

【0016】

また、この発明のうち請求項3に係る半導体装置の製造方法は、(a)半導体基板の表面上に、第1の導電性膜を選択的に形成する工程と、(b)第1の導電性膜上に、第1の絶縁膜を形成する工程と、(c)工程(a)及び(b)によって得られる構造上に、第2の絶縁膜を形成する工程と、(d)第2の絶縁膜上に、第3の絶縁膜を形成する工程と、(e)第3の絶縁膜上に、第4の絶縁膜を形成する工程と、(f)第4の絶縁膜、第3の絶縁膜、第2の絶縁膜を選択的に、かつ、この順に個別にエッチングして、半導体基板の表面のうち第1の導電性膜が形成されていない第1の位置に存在する部分を露出する工程と、(g)第1の位置において半導体基板と電気的に接触する第2の導電性膜を形成する工程とを備え、第3の絶縁膜は、第4の絶縁膜よりもエッチング速度が遅く、第2の絶縁膜は、第1の導電性膜及び第1の絶縁膜のそれぞれの側壁である第1領域と、半導体基板の表面のうち第1の導電性膜が形成されていない第2領域とに存在し、第1領域に存在する第2の絶縁膜の幅は、第2領域に存在する第2の絶縁膜の膜厚よりも厚く、(y)工程(f)とともに実行され、半導体基板の表面のうち、第1の位置とは異なる、第1の導電性膜が形成されていない第2の位置に存在する部分を露出する工程と、(z)工程(g)とともに実行され、第2の位置において半導体基板と電気的に接触する第3の導電性膜を形成する工程と、工程(g)及び(z)に引き続く、(h)第2及び第3の導電性膜及び第4の絶縁膜を覆う第5の絶縁膜を形成する工程と、(i)第5の絶縁膜を選択的にエッチングして第3の導電性膜の上方において開口を設ける工程と、(j)第5の絶縁膜の開口を介して第3の導電性膜と電気的に接続される第4の導電性膜を設ける工程と、(s)工程(c)と工程(d)との間に実行され、半導体基板の表面のうち第2の位置に存在する部分から、第2の絶縁膜を通して半導体基板と反対の導電型を有する第1の不純物を導入して第1の不純物領域を形成する工程と、(t)工程(y)と工程(z)との間に実行され、半導体基板の表面のうち第2の位置に存在する部分から、半導体基板と反対の導電型を有する第2の不純物を導入して第2の不純物領域を形成する工程とを更に備え、第2の不純物領域は第1の不純物領域よりも広く、かつ、第2の不純物領域の不純物濃度は第1の不純物領域の不純物濃度よりも低いことを特徴とするものである。

【0017】

また、この発明のうち請求項4に係る半導体装置の製造方法は、(a)半導体基板の表面上に、第1の導電性膜を選択的に形成する工程と、(b)第1の導電性膜上に、第1の絶縁膜を形成する工程と、(c)工程(a)及び(b)によって得られる構造上に、第2の絶縁膜を形成する工程と、(d)第2の絶縁膜上に、第3の絶縁膜を形成する工程と、(e)第3の絶縁膜上に、第4の絶縁膜を形成する工程と、(f)第4の絶縁膜、第3の絶縁膜、第2の絶縁膜を選択的に、かつ、この順に個別にエッチングして、半導体基板の表面のうち第1の導電性膜が形成されていない第1の位置に存在する部分を露出する工程と、(g)第1の位置において半導体基板と電気的に接触する第2の導電性膜を形成する工程とを備え、第3の絶縁膜は、第4の絶縁膜よりもエッチング速度が遅く、第2の絶縁膜は、第1の導電性膜及び第1の絶縁膜のそれぞれの側壁である第1領域と、半導体基板の表面のうち第1の導電性膜が形成されていない第2領域とに存在し、第1領域に存在する第2の絶縁膜の幅は、第2領域に存在する第2の絶縁膜の膜厚よりも厚く、(x)工程(d)と工程(e)との間に実行され、半導体基板の表面のうち、第1の位置とは異なる、第1の導電性膜が形成されていない第2の位置の上方に存在する第3の絶縁膜を除去する工程と、(y)工程(e)より後の工程において実行され、第2の位置の上方に存在する第4の絶縁膜及び第2の絶縁膜をこの順に連続してエッチングして、半導体基板の表面のうち第2の位置に存在する部分を露出する工程と、(z)第2の位置において半導体基板と電気的に接触する第3の導電性膜を形成する工程と、(s)工程(c)と工程(d)との間に実行され、半導体基板の表面のうち第1及び第2の位置に存在する部分から、第2の絶縁膜を通して半導体基板と反対の導電型を有する第1の不純物を導入して第1の不純物領域をそれぞれ形成する工程と、(t)工程(s)と工程(d)との間に実行され、半導体基板の表面のうち第1及び第2の位置に存在する部分から、半導体基板と反対の導電型を有する第2の不純物を導入して第2の不純物領域を形成する工程とを更に備え、第2の不純物領域は第1の不純物領域よりも広く、かつ、第2の不純物領域の不純物濃度は第1の不純物領域の不純物濃度よりも低いことを特徴とするものである。

【0018】

また、この発明のうち請求項5に係る半導体装置の製造方法は、(a)半導体基板の表面上に、第1の導電性膜を選択的に形成する工程と、(b)第1の導電性膜上に、第1の絶縁膜を形成する工程と、(c)工程(a)及び(b)によって得られる構造上に、第2の絶縁膜を形成する工程と、(d)第2の絶縁膜上に、第3の絶縁膜を形成する工程と、(e)第3の絶縁膜上に、第4の絶縁膜を形成する工程と、(f)第4の絶縁膜、第3の絶縁膜、第2の絶縁膜を選択的に、かつ、この順に個別にエッチングして、半導体基板の表面のうち第1の導電性膜が形成されていない第1の位置に存在する部分を露出する工程と、(g)第1の位置において半導体基板と電気的に接触する第2の導電性膜を形成する工程とを備え、第3の絶縁膜は、第4の絶縁膜よりもエッチング速度が遅く、第2の絶縁膜は、第1の導電性膜及び第1の絶縁膜のそれぞれの側壁である第1領域と、半導体基板の表面のうち第1の導電性膜が形成されていない第2領域とに存在し、第1領域に存在する第2の絶縁膜の幅は、第2領域に存在する第2の絶縁膜の膜厚よりも厚く、(y)工程(g)より後の工程において実行され、第4の絶縁膜、第3の絶縁膜、第2の絶縁膜を選択的に、かつ、この順に個別にエッチングして、半導体基板の表面のうち、第1の位置とは異なる、第1の導電性膜が形成されていない第2の位置に存在する部分を露出する工程と、(z)第2の位置において半導体基板と電気的に接触する第3の導電性膜を形成する工程と、(s)工程(c)と工程(d)との間に実行され、半導体基板の表面のうち第1及び第2の位置に存在する部分から、第2の絶縁膜を通して半導体基板と反対の導電型を有する第1の不純物を導入して第1の不純物領域をそれぞれ形成する工程と、(t)工程(s)と工程(d)との間に実行され、半導体基板の表面のうち第1及び第2の位置に存在する部分から、半導体基板と反対の導電型を有する第2の不純物を導入して第2の不純物領域を形成する工程とを更に備え、第2の不純物領域は第1の不純物領域よりも広く、かつ、第2の不純物領域の不純物濃度は第1の不純物領域の不純物濃度よりも低いことを特徴とするものである。

【0019】

また、この発明のうち請求項6に係る半導体装置の製造方法は、(a)半導体基板の表面上に、第1の導電性膜を選択的に形成する工程と、(b)第1の導電性膜上に、第1の絶縁膜を形成する工程と、(c)工程(a)及び(b)によって得られる構造上に、第2の絶縁膜を形成する工程と、(d)第2の絶縁膜上に、第3の絶縁膜を形成する工程と、(e)第3の絶縁膜上に、第4の絶縁膜を形成する工程と、(f)第4の絶縁膜、第3の絶縁膜、第2の絶縁膜を選択的に、かつ、この順に個別にエッチングして、半導体基板の表面のうち第1の導電性膜が形成されていない第1の位置に存在する部分を露出する工程と、(g)第1の位置において半導体基板と電気的に接触する第2の導電性膜を形成する工程とを備え、第3の絶縁膜は、第4の絶縁膜よりもエッチング速度が遅く、第2の絶縁膜は、第1の導電性膜及び第1の絶縁膜のそれぞれの側壁である第1領域と、半導体基板の表面のうち第1の導電性膜が形成されていない第2領域とに存在し、第1領域に存在する第2の絶縁膜の幅は、第2領域に存在する第2の絶縁膜の膜厚よりも厚く、(y)工程(f)とともに実行され、半導体基板の表面のうち、第1の位置とは異なる、第1の導電性膜が形成されていない第2の位置に存在する部分を露出する工程と、(z)工程(g)とともに実行され、第2の位置において半導体基板と電気的に接触する第3の導電性膜を形成する工程と、工程(g)及び(z)に引き続く、(h)第2及び第3の導電性膜及び第4の絶縁膜を覆う第5の絶縁膜を形成する工程と、(i)第5の絶縁膜を選択的にエッチングして第3の導電性膜の上方において開口を設ける工程と、(j)第5の絶縁膜の開口を介して第3の導電性膜と電気的に接続される第4の導電性膜を設ける工程と、(s)工程(c)と工程(d)との間に実行され、半導体基板の表面のうち第1及び第2の位置に存在する部分から、第2の絶縁膜を通して半導体基板と反対の導電型を有する第1の不純物を導入して第1の不純物領域をそれぞれ形成する工程と、(t)工程(s)と工程(d)との間に実行され、半導体基板の表面のうち第1及び第2の位置に存在する部分から、半導体基板と反対の導電型を有する第2の不純物を導入して第2の不純物領域を形成する工程とを更に備え、第2の不純物領域は第1の不純物領域よりも広く、かつ、第2の不純物領域の不純物濃度は第1の不純物領域の不純物濃度よりも低いことを特徴とするものである。

【0020】

また、この発明のうち請求項7に係る半導体装置の製造方法は、(a)半導体基板の表面上に、第1の導電性膜を選択的に形成する工程と、(b)第1の導電性膜上に、第1の絶縁膜を形成する工程と、(c)工程(a)及び(b)によって得られる構造上に、第2の絶縁膜を形成する工程と、(d)第2の絶縁膜上に、第3の絶縁膜を形成する工程と、(e)第3の絶縁膜上に、第4の絶縁膜を形成する工程と、(f)第4の絶縁膜、第3の絶縁膜、第2の絶縁膜を選択的に、かつ、この順に個別にエッチングして、半導体基板の表面のうち第1の導電性膜が形成されていない第1の位置に存在する部分を露出する工程と、(g)第1の位置において半導体基板と電気的に接触する第2の導電性膜を形成する工程とを備え、第3の絶縁膜は、第4の絶縁膜よりもエッチング速度が遅く、第2の絶縁膜は、第1の導電性膜及び第1の絶縁膜のそれぞれの側壁である第1領域と、半導体基板の表面のうち第1の導電性膜が形成されていない第2領域とに存在し、第1領域に存在する第2の絶縁膜の幅は、第2領域に存在する第2の絶縁膜の膜厚よりも厚く、(h)工程(c)と工程(d)との間に実行され、半導体基板の表面のうち、第1の位置とは異なる、第1の導電性膜が形成されていない第3の位置に存在する部分から、第2の絶縁膜を通して半導体基板と反対の導電型を有する第1の不純物を導入して第1の不純物領域を形成する工程と、(i)工程(d)と工程(e)との間に実行され、第3の位置の上方に存在する第3の絶縁膜を除去する工程と、(j)工程(i)と工程(e)との間に実行され、半導体基板の表面のうち第3の位置に存在する部分から、第2の絶縁膜を通して半導体基板と反対の導電型を有する第2の不純物を導入して第2の不純物領域を形成する工程と、(k)工程(f)と同時に実行され、第3の位置の上方に存在する、第4の絶縁膜及び第2の絶縁膜をこの順に連続してエッチングして、半導体基板の表面のうち第3の位置に存在する部分を露出する工程と、(l)工程(g)と同時に実行され、第3の位置において半導体基板と電気的に接触する第4の導電性膜を形成する工程とを更に備え、第2の不純物領域は第1の不純物領域よりも広く、かつ、第2の不純物領域の不純物濃度は第1の不純物領域の不純物濃度よりも低いことを特徴とするものである。

【0025】

【発明の実施の形態】

実施の形態1.

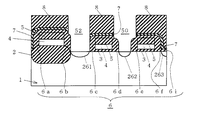

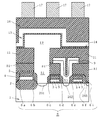

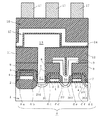

図1〜図15は、本発明の実施の形態1に係る半導体装置の製造工程を順に示す断面図である。まず、半導体(例えばSi)基板1上に素子分離絶縁膜2をLOCOS法により形成した後、素子分離絶縁膜2が形成されていない半導体基板1上にゲート酸化膜3、ゲート電極4、絶縁膜5の順に積層された構造を選択的に形成する(図1)。このゲート電極4はDRAMのワード線として機能することとなる。なお、図1において素子分離絶縁膜2上に設けられたゲート電極4の下方にはゲート酸化膜3が設けられていないが、紙面垂直方向で素子分離絶縁膜2の後方に隠れて上述の積層構造が形成される。

【0026】

次に、全面に、シリコン酸化膜6をCVD法により形成する(図2)。次に、半導体基板1に垂直な方向にエッチングレートの高い異方性の酸化膜エッチングを行うことによりシリコン酸化膜6をエッチングし、ゲート酸化膜3、ゲート電極4、絶縁膜5のそれぞれの側壁部にシリコン酸化膜6を残置させ、サイドウォール6a〜6fを形成する。但し、このエッチングの際には半導体基板1が露出しないよう、半導体基板1上に所定の膜厚のシリコン酸化膜6を残置させ、基板保護酸化膜6g〜6iを形成する。ここで、基板保護酸化膜6g〜6iの膜厚は、これらを異方性の酸化膜エッチングによって除去する際にそのエッチングを精度よく制御して半導体基板1がダメージを受けない範囲に設定される。例えば本実施の形態においては5〜20nmとする。その後、基板保護酸化膜6g〜6iを通して半導体基板1内に半導体基板1と反対の導電型のイオンを用いてイオン注入を行い、ソース/ドレイン領域261〜263をそれぞれ形成する(図3)。

【0027】

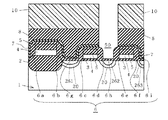

次に、全面に、例えばSi3N4又はSiONなどからなる絶縁膜7をCVD法により5〜100nmの厚さに堆積する(図4)。

【0028】

次に、全面に、例えばシリコン酸化膜をCVD法により堆積して、層間絶縁膜8を形成する(図5)。

【0029】

次に、層間絶縁膜8上に、ソース/ドレイン領域262の上方で開口を呈するホトレジスト10を通常の転写プロセスにより形成し、このホトレジスト10をマスクとして、例えばC4F8ガスを用いた酸化膜エッチングプロセスによって層間絶縁膜8のみをエッチングして、コンタクトホール50を形成する(図6)。この酸化膜エッチングプロセスにおいては、CVD法により形成されたSi3N4,SiONからなる絶縁膜7に対するエッチング速度が、CVD法により形成されたシリコン酸化膜からなる層間絶縁膜8よりも遅いことから、絶縁膜7が露出した時点でエッチングを容易に停止することができる。

【0030】

次に、ホトレジスト10をマスクとして、例えばCF4ガスを用いたエッチングプロセスによって絶縁膜7を除去する(図7)。さらに、ホトレジスト10をマスクとして、異方性の酸化膜エッチングを行うことにより基板保護酸化膜6hを除去してソース/ドレイン領域262を露出させる。このときサイドウォール6d,6eも除去されるが、基板保護酸化膜6hの膜厚分だけ除去されるにすぎない。その後ホトレジスト10を除去する(図8)。

【0031】

次に、例えばWSi/polySi又はTiSi/polySiなどの構造を有する導電性膜9を、コンタクトホール50を介してソース/ドレイン領域262に接続させるように形成する(図9)。この導電性膜9はDRAMのビット線として機能することとなる。

【0032】

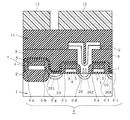

次に、全面に、例えばシリコン酸化膜をCVD法により堆積して、層間絶縁膜11を形成する(図10)。さらに、層間絶縁膜11上に、ソース/ドレイン領域261の上方で開口を呈するホトレジスト12を、通常の転写プロセスにより形成する(図11)。次に、このホトレジスト12をマスクとして、層間絶縁膜11,8、絶縁膜7、基板保護酸化膜6gをエッチングすることにより、コンタクトホール51を形成してソース/ドレイン領域261を露出させる。かかるエッチングは、公知の手法により、同一のエッチャントを用いて行うことができる。その後ホトレジスト12を除去する(図12)。

【0033】

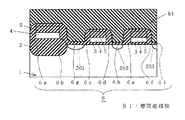

次に、コンタクトホール51を埋めるようにpolySiをCVD法により堆積してキャパシタ下部電極13を形成する。キャパシタ下部電極13はコンタクトホール51を介してソース/ドレイン領域261と接続される。その後、全面にSi3N4膜を堆積してキャパシタ誘電膜14を形成する。さらに、キャパシタ誘電膜14上にpolySiをCVD法により堆積してキャパシタ上部電極15を形成する(図13)。

【0034】

次に、キャパシタ上部電極15上に、例えばシリコン酸化膜をCVD法により堆積して、層間絶縁膜16を形成し(図14)、層間絶縁膜16上に、例えばAlCu、AlSiCuからなる配線層17を選択的に形成する(図17)。

【0035】

このように本実施の形態1に係る半導体装置の製造方法によれば、コンタクトホール50を形成する際、一旦絶縁膜7をストッパとして層間絶縁膜8をエッチングする。よってこの段階では基板保護酸化膜6hがエッチングされないので、層間絶縁膜8のエッチングがソース/ドレイン領域262にダメージを与えることはない。しかも、基板保護酸化膜6hは薄く、これをエッチングする際のエッチング量の制御は容易であるため、やはりソース/ドレイン領域262にダメージを与えない上、絶縁膜5やサイドウォール6d,6eが除去される量も各々における全体から見れば少ないので、コンタクトホール50がゲート電極4に接触することなく自己整合的に形成される。

【0036】

また、ソース/ドレイン領域261の状態に着目すると、従来の製造方法によればサイドウォール6a〜6f形成時及びコンタクトホール51形成時の2工程にわたって半導体基板1がオーバーエッチングされており、結晶欠陥25も大きかったのに対し、本実施の形態1に係る半導体装置の製造方法によれば、サイドウォール6a〜6fを形成する際に基板保護酸化膜6gを残置させるため、この際のエッチングにより半導体基板1がオーバーエッチングされることはなく、結晶欠陥25が生じることもない。従って、ソース/ドレイン領域261付近の結晶欠陥25は従来の製造方法と比較して抑制されているため、これにコンタクトホール51を介してキャパシタ下部電極13を接続したときに、デバイスの誤動作を引き起こすリーク電流が誘発されることも抑制される。

【0037】

実施の形態2.

実施の形態1では、絶縁膜7を形成した後の工程で層間絶縁膜8を形成したが、絶縁膜7を形成した後層間絶縁膜8を形成する前に、コンタクトホール50が形成される領域以外の絶縁膜7を除去してもよい。

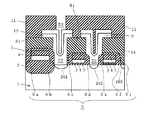

【0038】

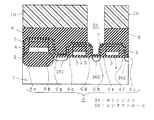

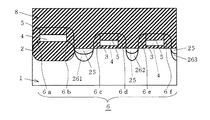

図16〜図27は、本発明の実施の形態2に係る半導体装置の製造工程を順に示す断面図である。まず、実施の形態1に係る工程と同様の工程を経て図4に示す構造と同様の構造を得る。その後、コンタクトホール50が形成される領域に、通常の転写プロセスによってホトレジスト24aを形成する(図16)。

【0039】

次に、ホトレジスト24aに覆われていない領域の絶縁膜7を、例えばCF4ガスを用いたエッチングプロセスによって除去した後、ホトレジスト24aを除去する(図17)。

【0040】

以下、実施の形態1に係る工程と同様の工程を経て層間絶縁膜11まで形成する。即ち、全面に層間絶縁膜8を堆積し(図18)、この上に形成したホトレジスト27をマスクとして、例えばC4F8ガスを用いた酸化膜エッチングプロセスによって層間絶縁膜8のみをエッチングしてコンタクトホール50を形成する(図19)。さらにホトレジスト27をマスクとして絶縁膜7をエッチングし(図20)、基板保護酸化膜6hを除去した後ホトレジスト27を除去する(図21)。次に、導電性膜9をコンタクトホール50を介してソース/ドレイン領域262に接続し(図22)、全面に層間絶縁膜11を形成する(図23)。

【0041】

その後、層間絶縁膜11上に通常の転写プロセスによりホトレジスト12を形成し、このホトレジスト12をマスクとして層間絶縁膜11,8、基板保護酸化膜6gを同一のエッチャントを用いてエッチングすることにより、コンタクトホール51を形成してソース/ドレイン領域261を露出させる(図24)。

【0042】

以下、実施の形態1に係る工程と同様の工程を経て配線層17まで形成する。即ち、キャパシタ下部電極13をコンタクトホール51を介してソース/ドレイン領域261に接続するように形成した後、全面に、キャパシタ誘電膜14、キャパシタ上部電極15をそれぞれ形成する(図25)。その後全面に層間絶縁膜16を形成し(図26)、この上に配線層17を選択的に形成する(図27)。

【0043】

コンタクトホール51はワード線たるゲート電極4及びビット線たる導電性膜9に接触しないように形成する必要があるため、必然的に微細なコンタクトホールを形成しなければならない。よって、微細なコンタクトホール51を形成する際に絶縁膜7のようなエッチング速度の遅い膜が存在することは望ましくない。本実施の形態2に係る半導体装置の製造方法によれば、コンタクトホール51を形成する際にエッチング速度の遅い絶縁膜7をエッチングする必要がないため、コンタクトホール51を容易に形成することが可能になる。

【0044】

実施の形態3.

実施の形態1では、層間絶縁膜11を形成した後、この上に通常の転写プロセスにより形成したホトレジスト12をマスクとして、層間絶縁膜11,8、絶縁膜7、基板保護酸化膜6gを同一のエッチャントを用いた単一の工程によりエッチングしてコンタクトホール51を形成したが、複数の工程によりコンタクトホール51を形成してもよい。

【0045】

図28〜図34は、本発明の実施の形態3に係る半導体装置の製造工程を順に示す断面図である。まず、実施の形態1に係る工程と同様の工程を経て図11に示す構造と同様の構造を得る(図28)。

【0046】

次に、ホトレジスト12をマスクとして例えばC4F8ガスを用いた酸化膜エッチングを行うことにより、層間絶縁膜11,8のみをエッチングし、絶縁膜7が露出した時点でエッチングを停止する(図29)。かかる酸化膜エッチングプロセスでは、Si3N4やSiONからなる絶縁膜7に対するエッチング速度が、シリコン酸化膜からなる層間絶縁膜8,11のそれよりも遅いため、絶縁膜7が露出した時点でエッチングを容易に停止することができることは、実施の形態1で述べたとおりである。

【0047】

次に、ホトレジスト12をマスクとして、例えばCF4ガスを用いたエッチングプロセスにより絶縁膜7のみを除去する(図30)。さらに、ホトレジスト12をマスクとして異方性の酸化膜エッチングを行うことにより、基板保護酸化膜6gを除去してソース/ドレイン領域261を露出させる。その後ホトレジスト12を除去する(図31)。

【0048】

以下、実施の形態1に係る工程と同様の工程を経て配線層17まで形成する。即ち、キャパシタ下部電極13をコンタクトホール51を介してソース/ドレイン領域261に接続するように形成した後、キャパシタ誘電膜14、キャパシタ上部電極15を形成する(図32)。その後全面に層間絶縁膜16を形成した後(図33)、この上に配線層17を選択的に形成する(図34)。

【0049】

このように本実施の形態3に係る半導体装置の製造方法によれば、コンタクトホール51を形成する際、エッチング速度の遅い絶縁膜7がストッパとして機能し、実施の形態1におけるコンタクトホール50と同様、コンタクトホール51がゲート電極4に接触することなく自己整合的に形成される。

【0050】

また、実施の形態1ではコンタクトホール51を形成する際に、層間絶縁膜11,8、基板保護酸化膜6gを同一のエッチャントを用いた単一の工程によりエッチングしていたため、除去すべき膜厚が厚く、エッチング量の制御は容易ではなかった。しかし、本実施の形態3に係る製造方法によれば、まず層間絶縁膜11,8のみをエッチングした後、絶縁膜7のみをエッチングするため、ソース/ドレイン領域261には影響せず、さらにその後基板保護酸化膜6gのみをエッチングする工程においても除去すべき膜厚が薄く、エッチング量の制御も容易となる。従って、コンタクトホール51を形成する際のエッチングによる半導体基板1のオーバーエッチング量も減少させることができ、実施の形態1に示す方法よりも、ソース/ドレイン領域261における結晶欠陥25の発生をさらに抑制することができる。

【0051】

実施の形態4.

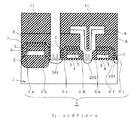

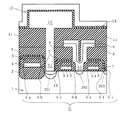

実施の形態1では、層間絶縁膜8を形成した後の工程において一旦ソース/ドレイン領域262のみを露出させていたが、ソース/ドレイン領域261を同時に露出させてもよい。

【0052】

図35〜図44は、本発明の実施の形態4に係る半導体装置の製造工程を順に示す断面図である。まず、実施の形態1に係る工程と同様の工程を経て図5と同様の構造を得る。その後、層間絶縁膜8上に、ソース/ドレイン領域261,262の上方に開口を呈するホトレジスト10aを通常の転写プロセスにより形成し、このホトレジスト10aをマスクとして、例えばC4F8ガスを用いた酸化膜エッチングを行うことにより層間絶縁膜8のみをエッチングして、コンタクトホール50,52を形成する(図35)。

【0053】

次に、ホトレジスト10aをマスクとして、例えばCF4ガスを用いたエッチングプロセスによって絶縁膜7のみを除去する(図36)。さらに、ホトレジスト10aをマスクとして、異方性の酸化膜エッチングを行うことにより基板保護酸化膜6g,6hを除去してソース/ドレイン領域261,262を露出させる。その後ホトレジスト10aを除去する(図37)。

【0054】

次に、ビット線たる導電性膜9をコンタクトホール50を介してソース/ドレイン領域262に接続させるように形成すると同時に、導電性膜9と同様の構造を呈する導電性膜19をコンタクトホール52を介してソース/ドレイン領域261に接続させるように形成する(図38)。この導電性膜19は、キャパシタ下部電極13とソース/ドレイン領域261とを接続するための接続電極として機能することとなる。

【0055】

次に、全面に、例えばシリコン酸化膜をCVD法により堆積し、層間絶縁膜11を形成する(図39)。次に、層間絶縁膜11上に、ソース/ドレイン領域261の上方に開口を呈するホトレジスト12を通常の転写プロセスにより形成する(図40)。

【0056】

その後、このホトレジスト12をマスクとして層間絶縁膜11をエッチングすることにより、コンタクトホール53を形成して導電性膜19を露出させる。その後ホトレジスト12を除去する(図41)。

【0057】

以下、実施の形態1に係る工程と同様の工程を経て配線層17まで形成する。即ち、キャパシタ下部電極13をコンタクトホール53を介して導電性膜19に接続するように形成した後、全面に、キャパシタ誘電膜14、キャパシタ上部電極15を形成する(図42)。次に、全面に層間絶縁膜16を形成した後(図43)、この上に配線層17を選択的に形成する(図44)。

【0058】

このように本実施の形態4に係る半導体装置の製造方法によれば、コンタクトホール50,52を形成する際、エッチング速度の遅い絶縁膜7が層間絶縁膜8をエッチングする際のストッパとして機能するため、コンタクトホール50,52がゲート電極4に接触することなく自己整合的に形成される。

【0059】

また、実施の形態3ではコンタクトホール51を形成する工程で絶縁膜7を露出する際に、層間絶縁膜11,8を同一のエッチャントを用いた単一の工程によってエッチングしていたため、除去すべき膜厚が厚くエッチングの制御は容易ではなかった。従って、層間絶縁膜11,8をエッチングする際のオーバーエッチングが過大になると、本来このエッチングのストッパとして機能すべき絶縁膜7が突き破られ、さらにその下の基板保護酸化膜6gはシリコン酸化膜であり容易にエッチングされることから、このエッチングがソース/ドレイン領域261の表面をもオーバーエッチングしてしまうおそれも考えられる。

【0060】

しかし、本実施の形態4に係る半導体装置の製造方法によれば、絶縁膜7を露出するにあたって層間絶縁膜11,8を単一の工程によってエッチングするのではなく、層間絶縁膜11を形成する前の工程において一旦層間絶縁膜8のみをエッチングして絶縁膜7を露出させ、その後別の工程において層間絶縁膜11のみをエッチングするため、それぞれの工程において除去すべき膜厚が薄く、容易にエッチング量を制御することができる。よって、ソース/ドレイン領域261のオーバーエッチングをより一層回避しやすい。

【0061】

実施の形態5.

実施の形態1では、サイドウォール6a〜6f、及び基板保護酸化膜6g〜6i上に絶縁膜7及び層間絶縁膜8を形成していたが、絶縁膜7及び層間絶縁膜8の代わりにシリコン酸化膜6よりもエッチング速度の速い絶縁膜を形成してもよい。

【0062】

図45〜図57は、本発明の実施の形態5に係る半導体装置の製造工程を順に示す断面図である。まず、実施の形態1に係る工程と同様の工程を経て図3と同様の構造を得る。即ち、半導体基板1上に素子分離絶縁膜2をLOCOS法により形成した後、素子分離絶縁膜2が形成されていない半導体基板1上にゲート酸化膜3、ゲート電極4、絶縁膜5の順に積層された構造を選択的に形成する(図45)。

【0063】

次に、全面にシリコン酸化膜6をCVD法により形成し(図46)、その後半導体基板1に垂直な方向にエッチングレートの高い異方性の酸化膜エッチングを行うことによりシリコン酸化膜6をエッチングしてサイドウォール6a〜6fを形成するとともに、基板保護酸化膜6g〜6iを形成する。その後、ソース/ドレイン領域261〜263をそれぞれ形成する(図47)。

【0064】

次に、全面に、シリコン酸化膜6よりもエッチング速度の速い層間絶縁膜(例えば、ボロンやリンなどの不純物を含むシリコン酸化膜)81を形成する(図48)。

【0065】

次に、層間絶縁膜81上に、ソース/ドレイン領域262の上方に開口を呈するホトレジスト10を通常の転写プロセスにより形成する。その後、このホトレジスト10をマスクとしてエッチングプロセスを行うことにより、層間絶縁膜81のみをエッチングする。このときのエッチャントとしては、例えばCHF3又はCF4、或いはこれらの混合ガスを、低密度のプラズマ(1010/cm2程度)として用いる。この際、エッチング速度の差で、シリコン酸化膜6(特にサイドウォール6d,6e及び基板保護酸化膜6h)がエッチングのストッパとして機能するため、サイドウォール6d,6e及び基板保護酸化膜6hを露出させるためのコンタクトホール50が形成される(図49)。

【0066】

次に、ホトレジスト10をマスクとして異方性の酸化膜エッチングを行うことにより、基板保護酸化膜6hを除去してソース/ドレイン領域262を露出させる。このときサイドウォール6d,6eも除去されるが、基板保護酸化膜6hの膜厚分だけ除去されるにすぎない。その後ホトレジスト10を除去する(図50)。

【0067】

次に、導電性膜9を、コンタクトホール50を介してソース/ドレイン領域262に接続するように形成し(図51)、その後全面に層間絶縁膜11を形成する(図52)。

【0068】

次に、層間絶縁膜11上に、ソース/ドレイン領域261の上方に開口を呈するホトレジスト12を通常の転写プロセスにより形成する(図53)。その後、このホトレジスト12をマスクとして、層間絶縁膜11,81、基板保護酸化膜6gを同一のエッチャントを用いてエッチングすることによりコンタクトホール51を形成し、ソース/ドレイン領域261を露出させる(図54)。

【0069】

以下、実施の形態1に係る工程と同様の工程を経て配線層17まで形成する。即ち、キャパシタ下部電極13をコンタクトホール51を介してソース/ドレイン領域261に接続するように形成した後、全面に、キャパシタ誘電膜14及びキャパシタ上部電極15を形成する(図55)。その後全面に層間絶縁膜16を形成した後(図56)、この上に配線層17を選択的に形成する(図57)。

【0070】

このように本実施の形態5に係る半導体装置の製造方法によれば、コンタクトホール50を形成する際に、層間絶縁膜81のみをエッチングして一旦サイドウォール6d,6e及び基板保護酸化膜6hを露出させるため、実施の形態1と同様の理由でコンタクトホ−ル50がゲート電極4に接触することなく自己整合的に形成され、かつ結晶欠陥25の発生も抑制される。また、実施の形態1に示す方法のように、エッチング速度の遅い絶縁膜7をエッチングする必要がないため、コンタクトホール50,51を形成する際のエッチング量の制御が容易となる。

【0071】

実施の形態6.

実施の形態5では、層間絶縁膜11を形成した後、通常の転写プロセスにより形成したホトレジスト12をマスクとして、層間絶縁膜11,81、基板保護酸化膜6gを同一のエッチャントを用いた単一の工程によりエッチングしてコンタクトホール51を形成したが、複数の工程によりコンタクトホール51を形成してもよい。

【0072】

図58〜図64は、本発明の実施の形態6に係る半導体装置の製造工程を順に示す断面図である。まず、実施の形態5に係る工程と同様の工程を経て図53に示す構造と同様の構造を得る(図58)。

【0073】

次に、ホトレジスト12をマスクとして異方性の酸化膜エッチングを行うことにより、層間絶縁膜11をエッチングする。この際、層間絶縁膜81のエッチング速度が層間絶縁膜11のそれよりも速いので、層間絶縁膜11をエッチングする際のオーバーエッチングにより層間絶縁膜81の上部も幾分エッチングされる(図59)。

【0074】

次に、ホトレジスト12をマスクとして層間絶縁膜81のみをエッチングする(図60)。この際、シリコン酸化膜6のエッチング速度が層間絶縁膜81のそれよりも遅いので、サイドウォール6b,6c及び基板保護酸化膜6gに施されるオーバーエッチング量は小さい。

【0075】

次に、ホトレジスト12をマスクとして異方性の酸化膜エッチングを行うことにより、基板保護酸化膜6gを除去してソース/ドレイン領域261を露出させる。その後ホトレジスト12を除去する(図61)。

【0076】

以下、実施の形態1に係る工程と同様の工程を経て配線層17まで形成する。即ち、キャパシタ下部電極13をコンタクトホール51を介してソース/ドレイン領域261に接続するように形成した後、キャパシタ誘電膜14、キャパシタ上部電極15を形成する(図62)。その後全面に層間絶縁膜16を形成した後(図63)、この上に配線層17を選択的に形成する(図64)。

【0077】

このように本実施の形態6に係る半導体装置の製造方法によれば、コンタクトホール51を形成する際に、一旦層間絶縁膜81のみをエッチングしてサイドウォール6b,6c及び基板保護酸化膜6gを露出させるため、実施の形態5と同様の理由でコンタクトホール51がゲート電極4に接触することなく自己整合的に形成され、かつ結晶欠陥25の発生も抑制される。

【0078】

また、実施の形態5ではコンタクトホール51を形成する際に、層間絶縁膜11,81、基板保護酸化膜6gを同一のエッチャントを用いた単一の工程によりエッチングしていたため、除去すべき膜厚が厚く、エッチングの制御は容易ではなかった。しかし、本実施の形態6に係る製造方法によれば、まず層間絶縁膜11のみをエッチングした後層間絶縁膜81のみをエッチングし、さらにその後基板保護酸化膜6gのみをエッチングするため、それぞれの工程において除去すべき膜厚が薄く、特に基板保護酸化膜6gのエッチング量の制御が容易となる。従って、コンタクトホール51を形成する際のエッチングによる半導体基板1のオーバーエッチング量も減少させることができ、実施の形態5に示す方法よりも、ソース/ドレイン領域261の結晶欠陥25の発生をさらに抑制することができる。

【0079】

実施の形態7.

実施の形態5では、層間絶縁膜81を形成した後の工程において一旦ソース/ドレイン領域262のみを露出させていたが、ソース/ドレイン領域261を同時に露出させてもよい。

【0080】

図65〜73は、本発明の実施の形態7に係る半導体装置の製造工程を順に示す断面図である。まず、実施の形態5に係る工程と同様の工程を経て図48と同様の構造を得る。その後、層間絶縁膜81上に、ソース/ドレイン領域261,262の上方に開口を呈するホトレジスト10aを通常の転写プロセスにより形成し、このホトレジスト10aをマスクとして、実施の形態5と同様のエッチャントを用いたエッチングプロセスによって層間絶縁膜81のみをエッチングして、コンタクトホール52,50をそれぞれ形成する(図65)。この際、シリコン酸化膜6のエッチング速度は層間絶縁膜81のそれよりも遅いので、サイドウォール6b,6c,6d,6e、及び基板保護酸化膜6g,6hに施されるオーバーエッチング量は小さい。

【0081】

次に、ホトレジスト10aをマスクとして、異方性の酸化膜エッチングを行うことにより基板保護酸化膜6g,6hを除去してソース/ドレイン領域261,262をそれぞれ露出させる。その後ホトレジスト10aを除去する(図66)。

【0082】

次に、ビット線たる導電性膜9をコンタクトホール50を介してソース/ドレイン領域262に接続させるように形成すると同時に、導電性膜9と同様の構造を呈する導電性膜19をコンタクトホール52を介してソース/ドレイン領域261に接続させるように形成する(図67)。既述のごとく、この電極19はキャパシタ下部電極13とソース/ドレイン領域261とを接続するための接続電極として機能することとなる。

【0083】

次に、全面に、例えばシリコン酸化膜をCVD法により堆積して、層間絶縁膜11を形成し(図68)、この上に、ソース/ドレイン領域261の上方に開口を呈するホトレジスト12を通常の転写プロセスにより形成する(図69)。

【0084】

その後、このホトレジスト12をマスクとして層間絶縁膜11をエッチングすることにより、コンタクトホール53を形成して導電性膜19を露出させる。その後ホトレジスト12を除去する(図70)。

【0085】

以下、実施の形態1に係る工程と同様の工程を経て配線層17まで形成する。即ち、キャパシタ下部電極13をコンタクトホール53を介して導電性膜19に接続するように形成した後、全面に、キャパシタ誘電膜14、キャパシタ上部電極15を形成する(図71)。次に、全面に層間絶縁膜16を形成した後(図72)、この上に配線層17を選択的に形成する(図73)。

【0086】

このように本実施の形態7に係る半導体装置の製造方法によれば、コンタクトホール50,52を形成する際に、酸化膜エッチングプロセスにより層間絶縁膜81のみをエッチングして一旦サイドウォール6b,6c,6d,6e及び基板保護酸化膜6g,6hを露出させるため、実施の形態5と同様の理由でコンタクトホール50,52がゲート電極4に接触することなく自己整合的に形成され、かつ結晶欠陥25の発生も抑制される。

【0087】

また、実施の形態6ではコンタクトホール51を形成する工程で、層間絶縁膜11をエッチングする際のオーバーエッチングにより層間絶縁膜81の上部も幾分エッチングされていた。従って、次の工程で層間絶縁膜81をエッチングするにあたっては、その上部がオーバーエッチングによりエッチングされた量を考慮する必要があり、しかも層間絶縁膜11と層間絶縁膜81のエッチング速度は互いに異なるため、層間絶縁膜81をエッチングすべき量を精度よく制御する必要があった。

【0088】

しかし、本実施の形態7に係る半導体装置の製造方法によれば、層間絶縁膜11をエッチングしてから層間絶縁膜81をエッチングするのではなく、層間絶縁膜11を形成する前の工程において一旦層間絶縁膜81をエッチングして基板保護酸化膜6gを露出させ、その後別の工程において層間絶縁膜11のみをエッチングするため、層間絶縁膜81をエッチングするにあたってその上部はエッチングされておらず、エッチング量を容易に制御することができる。

【0089】

実施の形態8.

実施の形態1では、コンタクトホール51を形成した後の工程で、すぐにキャパシタ下部電極13を形成したが、コンタクトホール51を形成した後キャパシタ下部電極13を形成する前に、半導体基板1内に不純物拡散層を形成する工程を追加してもよい。

【0090】

図74〜図77は、本発明の実施の形態8に係る半導体装置の製造工程を順に示す断面図である。まず、実施の形態1に係る工程と同様の工程を経て図11に示す構造と同様の構造を得る。その後、ホトレジスト12をマスクとして、半導体基板1と反対の導電型を有する不純物(半導体基板1の導電型がp型ならリン、ヒ素など/n型ならボロンなど)をコンタクトホール51を介して半導体基板1内にイオン注入法により導入し、不純物拡散層18をソース/ドレイン領域261よりも広く、かつ濃度を小さく形成する(図74)。

【0091】

以下、実施の形態1に係る工程と同様の工程を経て配線層17まで形成する。即ち、キャパシタ下部電極13をコンタクトホール51を介してソース/ドレイン領域261に接続するように形成した後、全面に、キャパシタ誘電膜14、キャパシタ上部電極15を形成する(図75)。次に、全面に層間絶縁膜16を形成した後(図76)、この上に配線層17を選択的に形成する(図77)。

【0092】

このように本実施の形態8に係る半導体装置の製造方法によれば、ソース/ドレイン領域261の外側に、半導体基板1と反対の導電型を有する不純物拡散層18を追加して形成するため、キャパシタ下部電極13と半導体基板1との接触抵抗が低減される。また、ソース/ドレイン領域261と半導体基板1との間での不純物濃度勾配が緩やかになり、キャパシタ下部電極13下の半導体基板1内の電界が緩和されるため、キャパシタ下部電極13から半導体基板1へ流れ出すリーク電流を低減することができる。

【0093】

なお、以上実施の形態8については実施の形態1を基礎としてその効果を述べたが、実施の形態5に係る製造方法を基礎としてもこれと同様の効果が得られることはいうまでもない。

【0094】

実施の形態9.

実施の形態1では、シリコン酸化膜6を途中までエッチングして基板保護酸化膜6g〜6iを形成した後の工程で、すぐに絶縁膜7を形成したが、絶縁膜7を形成する前に、半導体基板1内に不純物拡散層を形成する工程を追加してもよい。

【0095】

図78〜図90は、本発明の実施の形態9に係る半導体装置の製造工程を順に示す断面図である。まず、実施の形態1に係る工程と同様の工程を経て図3に示す構造と同様の構造を得る。その後、半導体基板1と反対の導電型を有する不純物を、基板保護酸化膜6g〜6iを通して半導体基板1にイオン注入法により導入し、不純物拡散層20をソース/ドレイン領域261,262よりも広く、かつ濃度を小さく形成する(図78)。

【0096】

以下、実施の形態1に係る工程と同様の工程を経て配線層17まで形成する。即ち、全面に絶縁膜7を形成した後(図79)、絶縁膜7上に層間絶縁膜8を形成し(図80)、その上に形成したホトレジスト10をマスクとして、例えばC4F8ガスを用いた酸化膜エッチングプロセスによって層間絶縁膜8をエッチングして、コンタクトホール50を形成する(図81)。さらにホトレジスト10をマスクとして絶縁膜7をエッチングし(図82)、その後基板保護酸化膜6hを除去する(図83)。次に、導電性膜9をコンタクトホール50を介してソース/ドレイン領域262に接続するように形成し(図84)、全面に層間絶縁膜11を形成する(図85)。次に、層間絶縁膜11上にホトレジスト12を形成し(図86)、これをマスクとして、層間絶縁膜11,8、絶縁膜7、基板保護酸化膜6gをエッチングしてコンタクトホール51を形成し、ソース/ドレイン領域261を露出させる(図87)。その後キャパシタ下部電極13をコンタクトホール51を介してソース/ドレイン領域261に接続するように形成し、全面に、キャパシタ誘電膜14、キャパシタ上部電極15を形成する(図88)。さらに全面に層間絶縁膜16を形成し(図89)、この上に配線層17を選択的に形成する(図90)。

【0097】

このように本実施の形態9に係る半導体装置の製造方法によれば、ソース/ドレイン領域261,262の外側に、半導体基板1と反対の導電型を有する不純物拡散層20を追加して形成するため、キャパシタ下部電極13及び導電性膜9と半導体基板1との接触抵抗が低減される。また、実施の形態8における効果と同様に、キャパシタ下部電極13から半導体基板1へ流れ出すリーク電流を低減することができる。さらに、不純物拡散層20を形成するためのイオン注入の際に半導体基板1が露出されることはないため、半導体基板1にダメージを与えることもない。

【0098】

なお、以上実施の形態9については実施の形態1を基礎としてその効果を述べたが、実施の形態5に係る製造方法を基礎としてもこれと同様の効果が得られることはいうまでもない。

【0099】

実施の形態10.

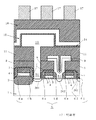

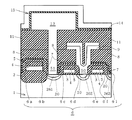

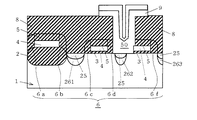

図91〜図108は、本発明の実施の形態10に係る半導体装置の製造工程を順に示す断面図である。まず、半導体(例えばSi)基板1上に素子分離絶縁膜2をLOCOS法により形成した後、素子分離絶縁膜2が形成されていない半導体基板1上に、ゲート酸化膜3、ゲート電極4、絶縁膜5の順に積層された構造を選択的に形成する(図91)。なお、半導体基板1は、図中に示すように周辺回路領域とメモリセル領域とに区分される。ここで、図91において素子分離絶縁膜2上に設けられたゲート電極4の下方にはゲート酸化膜3が設けられていないが、紙面垂直方向で素子分離絶縁膜2の後方に隠れて上述の積層構造が形成される。

【0100】

次に、全面に、シリコン酸化膜6をCVD法により形成する(図92)。次に、半導体基板1に垂直な方向にエッチングレートの高い異方性の酸化膜エッチングを行うことによりシリコン酸化膜6をエッチングして、ゲート酸化膜3、ゲート電極4、絶縁膜5のそれぞれの側壁部にシリコン酸化膜6を残置させ、サイドウォール6j〜6qを形成する。但し、このエッチングの際には半導体基板1が露出しないよう、半導体基板1上に所定の膜厚のシリコン酸化膜6を残置させ、基板保護酸化膜6r〜6vを形成する。ここで、基板保護酸化膜6r〜6vの膜厚は異方性の酸化膜エッチングによって半導体基板1がダメージを受けない範囲に設定される。例えば本実施の形態においては5〜20nmとする。その後、基板保護酸化膜6r〜6vを通して半導体基板1内にイオン注入を行い、ソース/ドレイン領域264〜268をそれぞれ形成する(図93)。

【0101】

次に、全面に、例えばSi3N4又はSiONなどからなる絶縁膜7をCVD法により5〜100nmの厚さに堆積する(図94)。

【0102】

次に、メモリセル領域にある絶縁膜7上に、通常の転写プロセスによってホトレジスト21を形成した後、このホトレジスト21に覆われていない領域の絶縁膜7及び基板保護酸化膜6r,6sを除去する。その後、ソース/ドレイン領域264,265よりも広く、半導体基板1と反対の導電型を有する不純物(半導体基板の導電型がp型ならリン、ヒ素など/n型ならボロンなど)をイオン注入法によりそれぞれ導入し、不純物拡散層22を形成する(図95)。その後ホトレジスト21を除去する(図96)。

【0103】

次に、全面にシリコン酸化膜をCVD法により堆積して、層間絶縁膜8を形成する(図97)。さらに層間絶縁膜8上に、ソース/ドレイン領域265,267の上方に開口を呈するホトレジスト10bを通常の転写プロセスにより形成し、このホトレジスト10bをマスクとして、絶縁膜7に対してエッチング速度の速い酸化膜エッチングプロセスによって、絶縁膜8をエッチングしてコンタクトホール53,50を形成する(図98)。この際、エッチング速度の差により、コンタクトホール50のエッチングは絶縁膜7が露呈した段階で停止することができる。

【0104】

次に、例えばCF4ガスを用いたエッチングプロセスによってコンタクトホール50内の絶縁膜7のみを除去する(図99)。

【0105】

さらに、ホトレジスト10bをマスクとして異方性の酸化膜エッチングを行うことにより、基板保護酸化膜6uを除去してソース/ドレイン領域267を露出させるまでコンタクトホール50を掘り進める。その後ホトレジスト10bを除去する(図100)。

【0106】

次に、ビット線たる導電性膜9をコンタクトホール50を介してソース/ドレイン領域267に接続させるように形成すると同時に、導電性膜9と同様の構造を呈する配線層23を、コンタクトホール53を介してソース/ドレイン領域265に接続させるように形成する(図101)。

【0107】

次に、全面に、例えばシリコン酸化膜をCVD法により堆積して層間絶縁膜11を形成し(図102)、この層間絶縁膜11上に、ソース/ドレイン領域266の上方に開口を呈するホトレジスト12aを通常の転写プロセスにより形成する。その後、このホトレジスト12aをマスクとして層間絶縁膜11,8、絶縁膜7、基板保護酸化膜6tを同一のエッチャントを用いてエッチングすることによりコンタクトホール51を形成してソース/ドレイン領域266を露出させる(図103)。その後ホトレジスト12aを除去する(図104)。

【0108】

次に、コンタクトホール51を埋めるようにpolySiをCVD法により堆積してキャパシタ下部電極13を形成する。その後、メモリセル領域のみにSi3N4膜を堆積してキャパシタ誘電膜14を形成する。さらに、キャパシタ誘電膜14上にpolySiをCVD法により堆積してキャパシタ上部電極15を形成する(図105)。

【0109】

次に、全面に、例えばシリコン酸化膜をCVD法により堆積して層間絶縁膜16を形成し(図106)、この層間絶縁膜16上に、ソースドレイン領域264の上方に開口を呈するホトレジスト24bを通常の転写プロセスにより形成する。その後、このホトレジスト24bをマスクとして層間絶縁膜16,11,8をエッチングすることによりコンタクトホール54を形成してソース/ドレイン領域264を露出させる(図107)。その後ホトレジスト24bを除去する。

【0110】

次に、層間絶縁膜16上に配線層17を選択的に形成する。その内の一つはコンタクトホール54を介してソース/ドレイン領域264に接続するように形成される(図108)。

【0111】

このように本実施の形態10に係る半導体装置の製造方法によれば、コンタクトホール50を形成する際、一旦絶縁膜7をストッパとして層間絶縁膜8のみをエッチングする。よってこの段階では基板保護酸化膜6uがエッチングされないので、層間絶縁膜8のエッチングがソース/ドレイン領域267にダメージを与えることはない。しかも、基板保護酸化膜6uは薄いため、これをエッチングする際のエッチング量の制御は容易であり、やはりソース/ドレイン領域267にダメージを与えない。さらに絶縁膜5やサイドウォール6o,6pが除去される量も、各々における全体から見れば少ないので、コンタクトホール50がゲート電極4に接触することなく自己整合的に形成される。

【0112】

また、コンタクトホール53,54を形成する際にエッチング速度の遅い絶縁膜7をエッチングする必要がないため、コンタクトホール53,54を形成する際のエッチング量の制御が容易である。

【0113】

さらに、ソース/ドレイン領域264,265よりも広く、半導体基板1と反対の導電型を有する不純物拡散層22を追加して形成するため、配線層17,23のそれぞれと半導体基板1との接触抵抗が低減される。

【0114】

実施の形態11.

実施の形態10では、周辺回路領域の絶縁膜7及び基板保護酸化膜6r,6sをエッチングした後、不純物拡散層22を形成したが、絶縁膜7のみをエッチングして、基板保護酸化膜6r,6sを通して不純物を導入することにより不純物拡散層22を形成してもよい。

【0115】

図109,110は本発明の実施の形態11に係る半導体装置の製造工程を順に示す断面図である。まず、実施の形態10に係る工程と同様の工程を経て図94に示す構造と同様の構造を得る。次に、メモリセル領域にある絶縁膜7上に通常の転写プロセスによってホトレジスト21を形成した後、このホトレジスト21をマスクとして、例えばCF4ガスを用いたエッチングプロセスによって絶縁膜7のみをエッチングする。その後、ソース/ドレイン領域264,265よりも広く、半導体基板1とは反対の導電型を有する不純物を基板保護酸化膜6r,6sを通してイオン注入法によりそれぞれ導入して、不純物拡散層22を形成する(図109)。

【0116】

以下、実施の形態10に係る工程と同様の工程を経て配線層17まで形成する(図110)。

【0117】

ここで、ソース/ドレイン領域264,265の状態に着目すると、実施の形態10に係る製造方法によれば不純物拡散層22の形成時及びコンタクトホール53,54の形成時の2工程にわたって半導体基板1がオーバーエッチングされており、表面の結晶欠陥25も大きかったのに対し、本実施の形態11に係る製造方法によれば、不純物拡散層22を形成する際に基板保護酸化膜6r,6sを残置させるため、この際のエッチングにより半導体基板1がオーバーエッチングされることはなく、表面付近に結晶欠陥25が生じることもない。従って、ソース/ドレイン領域264,265付近の結晶欠陥25は実施の形態10に係る製造方法と比較して抑制されているため、配線層23,17をそれぞれコンタクトホール53,54を介してソース/ドレイン領域264,265に接続したときに、デバイスの誤動作を引き起こすリーク電流が誘発されることも抑制される。

【0118】

【発明の効果】

この発明のうち請求項1に係る発明によれば、第2の絶縁膜のエッチングが第4の絶縁膜に連続してなされるのではなく、第3の絶縁膜が第4の絶縁膜をエッチングする際のストッパとして機能し、その後に第2の絶縁膜のエッチングが別途に行われるので、第2の絶縁膜のエッチング量を精度良く制御することができ、露出した半導体基板に対するオーバーエッチングを、ひいては半導体基板内における結晶欠陥の発生を抑制することができる。

【0119】

従って、工程(g)において第2の導電性膜を形成する際に、第2の導電性膜と半導体基板との接触において不要なリーク電流の発生を回避することができる。

また、第1領域に存在する第2の絶縁膜の幅の方が、第2領域に存在する第2の絶縁膜の膜厚よりも厚く、また第1の導電性膜上には第1の絶縁膜が存在するため、工程(f)において半導体基板の表面を選択的に露出する際に、第1の位置の設定精度が高くなくても、第1の導電性膜を露出させることなく半導体基板の表面のみを自己整合的に露出することができる。従って、工程(g)において第2の導電性膜を形成する際に、第2の導電性膜が第1の導電性膜と短絡することを回避することができる。

また、工程(y)において第2の位置に存在する半導体基板の表面を露出する際に、第2の位置の上方においてはエッチング速度の遅い第3の絶縁膜をエッチングする必要がないので、容易に半導体基板の表面を露出することができる。

また、第1の不純物領域よりも広く第2の不純物領域を形成するため、工程(z)において形成される第3の導電性膜と半導体基板との接触抵抗が低減される。また、第3の導電性膜と半導体基板との間での不純物濃度勾配が緩やかになるので、第3の導電性膜が形成される半導体基板内での電界が緩和される。従って、第3の導電性膜から半導体基板へ流れ出す不要なリーク電流の発生を一層抑制することができる。

【0120】

また、この発明のうち請求項2に係る発明によれば、第2の絶縁膜のエッチングが第4の絶縁膜に連続してなされるのではなく、第3の絶縁膜が第4の絶縁膜をエッチングする際のストッパとして機能し、その後に第2の絶縁膜のエッチングが別途に行われるので、第2の絶縁膜のエッチング量を精度良く制御することができ、露出した半導体基板に対するオーバーエッチングを、ひいては半導体基板内における結晶欠陥の発生を抑制することができる。

従って、工程(g)において第2の導電性膜を形成する際に、第2の導電性膜と半導体基板との接触において不要なリーク電流の発生を回避することができる。

また、第1領域に存在する第2の絶縁膜の幅の方が、第2領域に存在する第2の絶縁膜の膜厚よりも厚く、また第1の導電性膜上には第1の絶縁膜が存在するため、工程(f)において半導体基板の表面を選択的に露出する際に、第1の位置の設定精度が高くなくても、第1の導電性膜を露出させることなく半導体基板の表面のみを自己整合的に露出することができる。従って、工程(g)において第2の導電性膜を形成する際に、第2の導電性膜が第1の導電性膜と短絡することを回避することができる。

また、第2の絶縁膜のエッチングが第4の絶縁膜のエッチングに連続してなされるのではなく、第3の絶縁膜が第4の絶縁膜をエッチングする際のストッパとして機能するため、第2の絶縁膜のエッチング量を精度良く制御することができ、露出した半導体基板の表面に対するオーバーエッチングを、ひいては半導体基板内における結晶欠陥の発生を抑制することができる。従って、工程(z)において第3の導電性膜を形成する際に、第3の導電性膜と半導体基板との接触において不要なリーク電流の発生を回避する事ができる。

また、第1の不純物領域よりも広く第2の不純物領域を形成するため、工程(z)において形成される第3の導電性膜と半導体基板との接触抵抗が低減される。また、第3の導電性膜と半導体基板との間での不純物濃度勾配が緩やかになるので、第3の導電性膜が形成される半導体基板内での電界が緩和される。従って、第3の導電性膜から半導体基板へ流れ出す不要なリーク電流の発生を一層抑制することができる。

【0121】

また、この発明のうち請求項3に係る発明によれば、第2の絶縁膜のエッチングが第4の絶縁膜に連続してなされるのではなく、第3の絶縁膜が第4の絶縁膜をエッチングする際のストッパとして機能し、その後に第2の絶縁膜のエッチングが別途に行われるので、第2の絶縁膜のエッチング量を精度良く制御することができ、露出した半導体基板に対するオーバーエッチングを、ひいては半導体基板内における結晶欠陥の発生を抑制することができる。

従って、工程(g)において第2の導電性膜を形成する際に、第2の導電性膜と半導体基板との接触において不要なリーク電流の発生を回避することができる。

また、第1領域に存在する第2の絶縁膜の幅の方が、第2領域に存在する第2の絶縁膜の膜厚よりも厚く、また第1の導電性膜上には第1の絶縁膜が存在するため、工程(f)において半導体基板の表面を選択的に露出する際に、第1の位置の設定精度が高くなくても、第1の導電性膜を露出させることなく半導体基板の表面のみを自己整合的に露出することができる。従って、工程(g)において第2の導電性膜を形成する際に、第2の導電性膜が第1の導電性膜と短絡することを回避することができる。

また、第2の導電性膜とは第5の絶縁膜を介して層が異なる第4の導電性膜は、第2の位置に存在する半導体基板と第3の導電性膜を介して電気的に接続される。即ち、第5の絶縁膜に開口を設けるべくこれをエッチングする工程(i)と、第2の位置に存在する半導体基板の表面を露出すべく第4の絶縁膜をエッチングする工程(f)とは連続して行われない。従って、各工程においてエッチングすべき膜厚は、第4及び第5の絶縁膜を連続してエッチングする場合と比較して薄く、従ってエッチング量の制御が容易であり、第3の絶縁膜をオーバーエッチングする事を回避することができる。

また、第1の不純物領域よりも広く第2の不純物領域を形成するため、工程(z)において形成される第3の導電性膜と半導体基板との接触抵抗が低減される。また、第3の導電性膜と半導体基板との間での不純物濃度勾配が緩やかになるので、第3の導電性膜が形成される半導体基板内での電界が緩和される。従って、第3の導電性膜から半導体基板へ流れ出す不要なリーク電流の発生を一層抑制することができる。

【0122】

また、この発明のうち請求項4に係る発明によれば、第2の絶縁膜のエッチングが第4の絶縁膜に連続してなされるのではなく、第3の絶縁膜が第4の絶縁膜をエッチングする際のストッパとして機能し、その後に第2の絶縁膜のエッチングが別途に行われるので、第2の絶縁膜のエッチング量を精度良く制御することができ、露出した半導体基板に対するオーバーエッチングを、ひいては半導体基板内における結晶欠陥の発生を抑制することができる。

従って、工程(g)において第2の導電性膜を形成する際に、第2の導電性膜と半導体基板との接触において不要なリーク電流の発生を回避することができる。

また、第1領域に存在する第2の絶縁膜の幅の方が、第2領域に存在する第2の絶縁膜の膜厚よりも厚く、また第1の導電性膜上には第1の絶縁膜が存在するため、工程(f)において半導体基板の表面を選択的に露出する際に、第1の位置の設定精度が高くなくても、第1の導電性膜を露出させることなく半導体基板の表面のみを自己整合的に露出することができる。従って、工程(g)において第2の導電性膜を形成する際に、第2の導電性膜が第1の導電性膜と短絡することを回避することができる。

また、工程(y)において第2の位置に存在する半導体基板の表面を露出する際に、第2の位置の上方においてはエッチング速度の遅い第3の絶縁膜をエッチングする必要がないので、容易に半導体基板の表面を露出することができる。

また、第1の不純物領域よりも広く第2の不純物領域を形成するため、工程(z)において形成される第3の導電性膜と半導体基板との接触抵抗が低減される。また、第3の導電性膜と半導体基板との間での不純物濃度勾配が緩やかになるので、第3の導電性膜が形成される半導体基板内での電界が緩和される。従って、第3の導電性膜から半導体基板へ流れ出す不要なリーク電流の発生を一層抑制することができる。

さらに、第1及び第2の不純物領域を形成するにあたって、ともに半導体基板が露出されないため、半導体基板にダメージを与えることなく第1及び第2の不純物領域を形成することができる。

【0123】

また、この発明のうち請求項5に係る発明によれば、第2の絶縁膜のエッチングが第4の絶縁膜に連続してなされるのではなく、第3の絶縁膜が第4の絶縁膜をエッチングする際のストッパとして機能し、その後に第2の絶縁膜のエッチングが別途に行われるので、第2の絶縁膜のエッチング量を精度良く制御することができ、露出した半導体基板に対するオーバーエッチングを、ひいては半導体基板内における結晶欠陥の発生を抑制することができる。

従って、工程(g)において第2の導電性膜を形成する際に、第2の導電性膜と半導体基板との接触において不要なリーク電流の発生を回避することができる。

また、第1領域に存在する第2の絶縁膜の幅の方が、第2領域に存在する第2の絶縁膜の膜厚よりも厚く、また第1の導電性膜上には第1の絶縁膜が存在するため、工程(f)において半導体基板の表面を選択的に露出する際に、第1の位置の設定精度が高くなくても、第1の導電性膜を露出させることなく半導体基板の表面のみを自己整合的に露出することができる。従って、工程(g)において第2の導電性膜を形成する際に、第2の導電性膜が第1の導電性膜と短絡することを回避することができる。

また、第2の絶縁膜のエッチングが第4の絶縁膜のエッチングに連続してなされるのではなく、第3の絶縁膜が第4の絶縁膜をエッチングする際のストッパとして機能するため、第2の絶縁膜のエッチング量を精度良く制御することができ、露出した半導体基板の表面に対するオーバーエッチングを、ひいては半導体基板内における結晶欠陥の発生を抑制することができる。従って、工程(z)において第3の導電性膜を形成する際に、第3の導電性膜と半導体基板との接触において不要なリーク電流の発生を回避する事ができる。

また、第1の不純物領域よりも広く第2の不純物領域を形成するため、工程(z)において形成される第3の導電性膜と半導体基板との接触抵抗が低減される。また、第3の導電性膜と半導体基板との間での不純物濃度勾配が緩やかになるので、第3の導電性膜が形成される半導体基板内での電界が緩和される。従って、第3の導電性膜から半導体基板へ流れ出す不要なリーク電流の発生を一層抑制することができる。

さらに、第1及び第2の不純物領域を形成するにあたって、ともに半導体基板が露出されないため、半導体基板にダメージを与えることなく第1及び第2の不純物領域を形成することができる。

【0124】

また、この発明のうち請求項6に係る発明によれば、第2の絶縁膜のエッチングが第4の絶縁膜に連続してなされるのではなく、第3の絶縁膜が第4の絶縁膜をエッチングする際のストッパとして機能し、その後に第2の絶縁膜のエッチングが別途に行われるので、第2の絶縁膜のエッチング量を精度良く制御することができ、露出した半導体基板に対するオーバーエッチングを、ひいては半導体基板内における結晶欠陥の発生を抑制することができる。

従って、工程(g)において第2の導電性膜を形成する際に、第2の導電性膜と半導体基板との接触において不要なリーク電流の発生を回避することができる。

また、第1領域に存在する第2の絶縁膜の幅の方が、第2領域に存在する第2の絶縁膜の膜厚よりも厚く、また第1の導電性膜上には第1の絶縁膜が存在するため、工程(f)において半導体基板の表面を選択的に露出する際に、第1の位置の設定精度が高くなくても、第1の導電性膜を露出させることなく半導体基板の表面のみを自己整合的に露出することができる。従って、工程(g)において第2の導電性膜を形成する際に、第2の導電性膜が第1の導電性膜と短絡することを回避することができる。

また、第2の導電性膜とは第5の絶縁膜を介して層が異なる第4の導電性膜は、第2の位置に存在する半導体基板と第3の導電性膜を介して電気的に接続される。即ち、第5の絶縁膜に開口を設けるべくこれをエッチングする工程(i)と、第2の位置に存在する半導体基板の表面を露出すべく第4の絶縁膜をエッチングする工程(f)とは連続して行われない。従って、各工程においてエッチングすべき膜厚は、第4及び第5の絶縁膜を連続してエッチングする場合と比較して薄く、従ってエッチング量の制御が容易であり、第3の絶縁膜をオーバーエッチングする事を回避することができる。

また、第1の不純物領域よりも広く第2の不純物領域を形成するため、工程(z)において形成される第3の導電性膜と半導体基板との接触抵抗が低減される。また、第3の導電性膜と半導体基板との間での不純物濃度勾配が緩やかになるので、第3の導電性膜が形成される半導体基板内での電界が緩和される。従って、第3の導電性膜から半導体基板へ流れ出す不要なリーク電流の発生を一層抑制することができる。

さらに、第1及び第2の不純物領域を形成するにあたって、ともに半導体基板が露出されないため、半導体基板にダメージを与えることなく第1及び第2の不純物領域を形成することができる。

【0125】

また、この発明のうち請求項7に係る発明によれば、第2の絶縁膜のエッチングが第4の絶縁膜に連続してなされるのではなく、第3の絶縁膜が第4の絶縁膜をエッチングする際のストッパとして機能し、その後に第2の絶縁膜のエッチングが別途に行われるので、第2の絶縁膜のエッチング量を精度良く制御することができ、露出した半導体基板に対するオーバーエッチングを、ひいては半導体基板内における結晶欠陥の発生を抑制することができる。

従って、工程(g)において第2の導電性膜を形成する際に、第2の導電性膜と半導体基板との接触において不要なリーク電流の発生を回避することができる。

また、第1領域に存在する第2の絶縁膜の幅の方が、第2領域に存在する第2の絶縁膜の膜厚よりも厚く、また第1の導電性膜上には第1の絶縁膜が存在するため、工程(f)において半導体基板の表面を選択的に露出する際に、第1の位置の設定精度が高くなくても、第1の導電性膜を露出させることなく半導体基板の表面のみを自己整合的に露出することができる。従って、工程(g)において第2の導電性膜を形成する際に、第2の導電性膜が第1の導電性膜と短絡することを回避することができる。

また、工程(k)において第3の位置に存在する半導体基板の表面を露出する際に、第3の位置の上方においてはエッチング速度の遅い第3の絶縁膜をエッチングする必要がないので、容易に半導体基板の表面を露出することができる。

さらに、第1の不純物領域よりも広く第2の不純物領域を形成するため、工程(k)において形成される第4の導電性膜と半導体基板との接触抵抗が低減される。また、第4の導電性膜と半導体基板との間での不純物濃度勾配が緩やかになるので、第4の導電性膜が形成される半導体基板内での電界が緩和される。従って、第4の導電性膜から半導体基板へ流れ出す不要なリーク電流の発生を一層抑制することができる。

【図面の簡単な説明】

【図1】本発明の実施の形態1に係る半導体装置の製造工程を示す断面図である。

【図2】本発明の実施の形態1に係る半導体装置の製造工程を示す断面図である。

【図3】本発明の実施の形態1に係る半導体装置の製造工程を示す断面図である。

【図4】本発明の実施の形態1に係る半導体装置の製造工程を示す断面図である。

【図5】本発明の実施の形態1に係る半導体装置の製造工程を示す断面図である。

【図6】本発明の実施の形態1に係る半導体装置の製造工程を示す断面図である。

【図7】本発明の実施の形態1に係る半導体装置の製造工程を示す断面図である。

【図8】本発明の実施の形態1に係る半導体装置の製造工程を示す断面図である。

【図9】本発明の実施の形態1に係る半導体装置の製造工程を示す断面図である。

【図10】本発明の実施の形態1に係る半導体装置の製造工程を示す断面図である。

【図11】本発明の実施の形態1に係る半導体装置の製造工程を示す断面図である。

【図12】本発明の実施の形態1に係る半導体装置の製造工程を示す断面図である。

【図13】本発明の実施の形態1に係る半導体装置の製造工程を示す断面図である。

【図14】本発明の実施の形態1に係る半導体装置の製造工程を示す断面図である。

【図15】本発明の実施の形態1に係る半導体装置の製造工程を示す断面図である。

【図16】本発明の実施の形態2に係る半導体装置の製造工程を示す断面図である。

【図17】本発明の実施の形態2に係る半導体装置の製造工程を示す断面図である。

【図18】本発明の実施の形態2に係る半導体装置の製造工程を示す断面図である。

【図19】本発明の実施の形態2に係る半導体装置の製造工程を示す断面図である。

【図20】本発明の実施の形態2に係る半導体装置の製造工程を示す断面図である。

【図21】本発明の実施の形態2に係る半導体装置の製造工程を示す断面図である。

【図22】本発明の実施の形態2に係る半導体装置の製造工程を示す断面図である。

【図23】本発明の実施の形態2に係る半導体装置の製造工程を示す断面図である。

【図24】本発明の実施の形態2に係る半導体装置の製造工程を示す断面図である。

【図25】本発明の実施の形態2に係る半導体装置の製造工程を示す断面図である。

【図26】本発明の実施の形態2に係る半導体装置の製造工程を示す断面図である。

【図27】本発明の実施の形態2に係る半導体装置の製造工程を示す断面図である。

【図28】本発明の実施の形態3に係る半導体装置の製造工程を示す断面図である。

【図29】本発明の実施の形態3に係る半導体装置の製造工程を示す断面図である。

【図30】本発明の実施の形態3に係る半導体装置の製造工程を示す断面図である。

【図31】本発明の実施の形態3に係る半導体装置の製造工程を示す断面図である。

【図32】本発明の実施の形態3に係る半導体装置の製造工程を示す断面図である。

【図33】本発明の実施の形態3に係る半導体装置の製造工程を示す断面図である。

【図34】本発明の実施の形態3に係る半導体装置の製造工程を示す断面図である。

【図35】本発明の実施の形態4に係る半導体装置の製造工程を示す断面図である。

【図36】本発明の実施の形態4に係る半導体装置の製造工程を示す断面図である。

【図37】本発明の実施の形態4に係る半導体装置の製造工程を示す断面図である。

【図38】本発明の実施の形態4に係る半導体装置の製造工程を示す断面図である。

【図39】本発明の実施の形態4に係る半導体装置の製造工程を示す断面図である。

【図40】本発明の実施の形態4に係る半導体装置の製造工程を示す断面図である。

【図41】本発明の実施の形態4に係る半導体装置の製造工程を示す断面図である。

【図42】本発明の実施の形態4に係る半導体装置の製造工程を示す断面図である。

【図43】本発明の実施の形態4に係る半導体装置の製造工程を示す断面図である。

【図44】本発明の実施の形態4に係る半導体装置の製造工程を示す断面図である。

【図45】本発明の実施の形態5に係る半導体装置の製造工程を示す断面図である。

【図46】本発明の実施の形態5に係る半導体装置の製造工程を示す断面図である。

【図47】本発明の実施の形態5に係る半導体装置の製造工程を示す断面図である。

【図48】本発明の実施の形態5に係る半導体装置の製造工程を示す断面図である。

【図49】本発明の実施の形態5に係る半導体装置の製造工程を示す断面図である。

【図50】本発明の実施の形態5に係る半導体装置の製造工程を示す断面図である。

【図51】本発明の実施の形態5に係る半導体装置の製造工程を示す断面図である。

【図52】本発明の実施の形態5に係る半導体装置の製造工程を示す断面図である。

【図53】本発明の実施の形態5に係る半導体装置の製造工程を示す断面図である。

【図54】本発明の実施の形態5に係る半導体装置の製造工程を示す断面図である。

【図55】本発明の実施の形態5に係る半導体装置の製造工程を示す断面図である。

【図56】本発明の実施の形態5に係る半導体装置の製造工程を示す断面図である。

【図57】本発明の実施の形態5に係る半導体装置の製造工程を示す断面図である。

【図58】本発明の実施の形態6に係る半導体装置の製造工程を示す断面図である。

【図59】本発明の実施の形態6に係る半導体装置の製造工程を示す断面図である。

【図60】本発明の実施の形態6に係る半導体装置の製造工程を示す断面図である。

【図61】本発明の実施の形態6に係る半導体装置の製造工程を示す断面図である。

【図62】本発明の実施の形態6に係る半導体装置の製造工程を示す断面図である。

【図63】本発明の実施の形態6に係る半導体装置の製造工程を示す断面図である。

【図64】本発明の実施の形態6に係る半導体装置の製造工程を示す断面図である。

【図65】本発明の実施の形態7に係る半導体装置の製造工程を示す断面図である。

【図66】本発明の実施の形態7に係る半導体装置の製造工程を示す断面図である。

【図67】本発明の実施の形態7に係る半導体装置の製造工程を示す断面図である。

【図68】本発明の実施の形態7に係る半導体装置の製造工程を示す断面図である。

【図69】本発明の実施の形態7に係る半導体装置の製造工程を示す断面図である。

【図70】本発明の実施の形態7に係る半導体装置の製造工程を示す断面図である。

【図71】本発明の実施の形態7に係る半導体装置の製造工程を示す断面図である。

【図72】本発明の実施の形態7に係る半導体装置の製造工程を示す断面図である。

【図73】本発明の実施の形態7に係る半導体装置の製造工程を示す断面図である。

【図74】本発明の実施の形態8に係る半導体装置の製造工程を示す断面図である。

【図75】本発明の実施の形態8に係る半導体装置の製造工程を示す断面図である。

【図76】本発明の実施の形態8に係る半導体装置の製造工程を示す断面図である。

【図77】本発明の実施の形態8に係る半導体装置の製造工程を示す断面図である。

【図78】本発明の実施の形態9に係る半導体装置の製造工程を示す断面図である。

【図79】本発明の実施の形態9に係る半導体装置の製造工程を示す断面図である。

【図80】本発明の実施の形態9に係る半導体装置の製造工程を示す断面図である。

【図81】本発明の実施の形態9に係る半導体装置の製造工程を示す断面図である。

【図82】本発明の実施の形態9に係る半導体装置の製造工程を示す断面図である。

【図83】本発明の実施の形態9に係る半導体装置の製造工程を示す断面図である。

【図84】本発明の実施の形態9に係る半導体装置の製造工程を示す断面図である。

【図85】本発明の実施の形態9に係る半導体装置の製造工程を示す断面図である。

【図86】本発明の実施の形態9に係る半導体装置の製造工程を示す断面図である。

【図87】本発明の実施の形態9に係る半導体装置の製造工程を示す断面図である。

【図88】本発明の実施の形態9に係る半導体装置の製造工程を示す断面図である。

【図89】本発明の実施の形態9に係る半導体装置の製造工程を示す断面図である。

【図90】本発明の実施の形態9に係る半導体装置の製造工程を示す断面図である。

【図91】本発明の実施の形態10に係る半導体装置の製造工程を示す断面図である。

【図92】本発明の実施の形態10に係る半導体装置の製造工程を示す断面図である。

【図93】本発明の実施の形態10に係る半導体装置の製造工程を示す断面図である。

【図94】本発明の実施の形態10に係る半導体装置の製造工程を示す断面図である。

【図95】本発明の実施の形態10に係る半導体装置の製造工程を示す断面図である。

【図96】本発明の実施の形態10に係る半導体装置の製造工程を示す断面図である。

【図97】本発明の実施の形態10に係る半導体装置の製造工程を示す断面図である。

【図98】本発明の実施の形態10に係る半導体装置の製造工程を示す断面図である。

【図99】本発明の実施の形態10に係る半導体装置の製造工程を示す断面図である。

【図100】本発明の実施の形態10に係る半導体装置の製造工程を示す断面図である。

【図101】本発明の実施の形態10に係る半導体装置の製造工程を示す断面図である。

【図102】本発明の実施の形態10に係る半導体装置の製造工程を示す断面図である。

【図103】本発明の実施の形態10に係る半導体装置の製造工程を示す断面図である。

【図104】本発明の実施の形態10に係る半導体装置の製造工程を示す断面図である。

【図105】本発明の実施の形態10に係る半導体装置の製造工程を示す断面図である。

【図106】本発明の実施の形態10に係る半導体装置の製造工程を示す断面図である。

【図107】本発明の実施の形態10に係る半導体装置の製造工程を示す断面図である。

【図108】本発明の実施の形態10に係る半導体装置の製造工程を示す断面図である。

【図109】本発明の実施の形態11に係る半導体装置の製造工程を示す断面図である。

【図110】本発明の実施の形態11に係る半導体装置の製造工程を示す断面図である。

【図111】従来の半導体装置の製造工程を示す断面図である。

【図112】従来の半導体装置の製造工程を示す断面図である。

【図113】従来の半導体装置の製造工程を示す断面図である。

【図114】従来の半導体装置の製造工程を示す断面図である。

【図115】従来の半導体装置の製造工程を示す断面図である。

【図116】従来の半導体装置の製造工程を示す断面図である。

【図117】従来の半導体装置の製造工程を示す断面図である。

【図118】従来の半導体装置の製造工程を示す断面図である。

【図119】従来の半導体装置の製造工程を示す断面図である。

【図120】従来の半導体装置の製造工程を示す断面図である。

【図121】従来の半導体装置の製造工程を示す断面図である。

【図122】従来の半導体装置の製造工程を示す断面図である。

【符号の説明】

1 半導体基板、4 ゲート電極、6 シリコン酸化膜、6a〜6f,6j〜6q サイドウォール、6g〜6i,6r〜6v 基板保護酸化膜、261〜268 ソース/ドレイン領域、7 絶縁膜、8,11,16 層間絶縁膜、50〜53 コンタクトホール、9,19 導電性膜、13 キャパシタ下部電極、14 キャパシタ誘電膜、15 キャパシタ上部電極、18,20,22 不純物拡散層、23 配線層。

Claims (7)

- (a)半導体基板の表面上に、第1の導電性膜を選択的に形成する工程と、

(b)前記第1の導電性膜上に、第1の絶縁膜を形成する工程と、

(c)前記工程(a)及び(b)によって得られる構造上に、第2の絶縁膜を形成する工程と、

(d)前記第2の絶縁膜上に、第3の絶縁膜を形成する工程と、

(e)前記第3の絶縁膜上に、第4の絶縁膜を形成する工程と、

(f)前記第4の絶縁膜、前記第3の絶縁膜、前記第2の絶縁膜を選択的に、かつ、この順に個別にエッチングして、前記半導体基板の前記表面のうち前記第1の導電性膜が形成されていない第1の位置に存在する部分を露出する工程と、

(g)前記第1の位置において前記半導体基板と電気的に接触する第2の導電性膜を形成する工程と

を備え、

前記第3の絶縁膜は、前記第4の絶縁膜よりもエッチング速度が遅く、

前記第2の絶縁膜は、前記第1の導電性膜及び前記第1の絶縁膜のそれぞれの側壁である第1領域と、前記半導体基板の前記表面のうち前記第1の導電性膜が形成されていない第2領域とに存在し、前記第1領域に存在する前記第2の絶縁膜の幅は、前記第2領域に存在する前記第2の絶縁膜の膜厚よりも厚く、

(x)前記工程(d)と前記工程(e)との間に実行され、前記半導体基板の前記表面のうち、前記第1の位置とは異なる、前記第1の導電性膜が形成されていない第2の位置の上方に存在する前記第3の絶縁膜を除去する工程と、

(y)前記工程(e)より後の工程において実行され、前記第2の位置の上方に存在する前記第4の絶縁膜及び前記第2の絶縁膜をこの順に連続してエッチングして、前記半導体基板の前記表面のうち前記第2の位置に存在する部分を露出する工程と、

(z)前記第2の位置において前記半導体基板と電気的に接触する第3の導電性膜を形成する工程と、

(s)前記工程(c)と前記工程(d)との間に実行され、前記半導体基板の前記表面のうち前記第2の位置に存在する部分から、前記第2の絶縁膜を通して前記半導体基板と反対の導電型を有する第1の不純物を導入して第1の不純物領域を形成する工程と、

(t)前記工程(y)と前記工程(z)との間に実行され、前記半導体基板の前記表面のうち前記第2の位置に存在する部分から、前記半導体基板と反対の導電型を有する第2の不純物を導入して第2の不純物領域を形成する工程と

を更に備え、

前記第2の不純物領域は前記第1の不純物領域よりも広く、かつ、前記第2の不純物領域の不純物濃度は前記第1の不純物領域の不純物濃度よりも低いことを特徴とする、半導体装置の製造方法。 - (a)半導体基板の表面上に、第1の導電性膜を選択的に形成する工程と、

(b)前記第1の導電性膜上に、第1の絶縁膜を形成する工程と、

(c)前記工程(a)及び(b)によって得られる構造上に、第2の絶縁膜を形成する工程と、

(d)前記第2の絶縁膜上に、第3の絶縁膜を形成する工程と、

(e)前記第3の絶縁膜上に、第4の絶縁膜を形成する工程と、

(f)前記第4の絶縁膜、前記第3の絶縁膜、前記第2の絶縁膜を選択的に、かつ、この順に個別にエッチングして、前記半導体基板の前記表面のうち前記第1の導電性膜が形成されていない第1の位置に存在する部分を露出する工程と、

(g)前記第1の位置において前記半導体基板と電気的に接触する第2の導電性膜を形成する工程と

を備え、

前記第3の絶縁膜は、前記第4の絶縁膜よりもエッチング速度が遅く、

前記第2の絶縁膜は、前記第1の導電性膜及び前記第1の絶縁膜のそれぞれの側壁である第1領域と、前記半導体基板の前記表面のうち前記第1の導電性膜が形成されていない第2領域とに存在し、前記第1領域に存在する前記第2の絶縁膜の幅は、前記第2領域に存在する前記第2の絶縁膜の膜厚よりも厚く、

(y)前記工程(g)より後の工程において実行され、前記第4の絶縁膜、前記第3の絶縁膜、前記第2の絶縁膜を選択的に、かつ、この順に個別にエッチングして、前記半導体基板の前記表面のうち、前記第1の位置とは異なる、前記第1の導電性膜が形成されていない第2の位置に存在する部分を露出する工程と、

(z)前記第2の位置において前記半導体基板と電気的に接触する第3の導電性膜を形成する工程と、

(s)前記工程(c)と前記工程(d)との間に実行され、前記半導体基板の前記表面のうち前記第2の位置に存在する部分から、前記第2の絶縁膜を通して前記半導体基板と反対の導電型を有する第1の不純物を導入して第1の不純物領域を形成する工程と、

(t)前記工程(y)と前記工程(z)との間に実行され、前記半導体基板の前記表面のうち前記第2の位置に存在する部分から、前記半導体基板と反対の導電型を有する第2の不純物を導入して第2の不純物領域を形成する工程と

を更に備え、

前記第2の不純物領域は前記第1の不純物領域よりも広く、かつ、前記第2の不純物領域の不純物濃度は前記第1の不純物領域の不純物濃度よりも低いことを特徴とする、半導体装置の製造方法。 - (a)半導体基板の表面上に、第1の導電性膜を選択的に形成する工程と、

(b)前記第1の導電性膜上に、第1の絶縁膜を形成する工程と、

(c)前記工程(a)及び(b)によって得られる構造上に、第2の絶縁膜を形成する工程と、

(d)前記第2の絶縁膜上に、第3の絶縁膜を形成する工程と、

(e)前記第3の絶縁膜上に、第4の絶縁膜を形成する工程と、

(f)前記第4の絶縁膜、前記第3の絶縁膜、前記第2の絶縁膜を選択的に、かつ、この順に個別にエッチングして、前記半導体基板の前記表面のうち前記第1の導電性膜が形成されていない第1の位置に存在する部分を露出する工程と、

(g)前記第1の位置において前記半導体基板と電気的に接触する第2の導電性膜を形成する工程と

を備え、

前記第3の絶縁膜は、前記第4の絶縁膜よりもエッチング速度が遅く、

前記第2の絶縁膜は、前記第1の導電性膜及び前記第1の絶縁膜のそれぞれの側壁である第1領域と、前記半導体基板の前記表面のうち前記第1の導電性膜が形成されていない第2領域とに存在し、前記第1領域に存在する前記第2の絶縁膜の幅は、前記第2領域に存在する前記第2の絶縁膜の膜厚よりも厚く、

(y)前記工程(f)とともに実行され、前記半導体基板の前記表面のうち、前記第1の位置とは異なる、前記第1の導電性膜が形成されていない第2の位置に存在する部分を露出する工程と、

(z)前記工程(g)とともに実行され、前記第2の位置において前記半導体基板と電気的に接触する第3の導電性膜を形成する工程と、

前記工程(g)及び(z)に引き続く、

(h)前記第2及び第3の導電性膜及び前記第4の絶縁膜を覆う第5の絶縁膜を形成する工程と、

(i)前記第5の絶縁膜を選択的にエッチングして前記第3の導電性膜の上方において開口を設ける工程と、

(j)前記第5の絶縁膜の前記開口を介して前記第3の導電性膜と電気的に接続される 第4の導電性膜を設ける工程と、

(s)前記工程(c)と前記工程(d)との間に実行され、前記半導体基板の前記表面のうち前記第2の位置に存在する部分から、前記第2の絶縁膜を通して前記半導体基板と反対の導電型を有する第1の不純物を導入して第1の不純物領域を形成する工程と、

(t)前記工程(y)と前記工程(z)との間に実行され、前記半導体基板の前記表面のうち前記第2の位置に存在する部分から、前記半導体基板と反対の導電型を有する第2の不純物を導入して第2の不純物領域を形成する工程と

を更に備え、

前記第2の不純物領域は前記第1の不純物領域よりも広く、かつ、前記第2の不純物領域の不純物濃度は前記第1の不純物領域の不純物濃度よりも低いことを特徴とする、半導体装置の製造方法。 - (a)半導体基板の表面上に、第1の導電性膜を選択的に形成する工程と、

(b)前記第1の導電性膜上に、第1の絶縁膜を形成する工程と、

(c)前記工程(a)及び(b)によって得られる構造上に、第2の絶縁膜を形成する工程と、

(d)前記第2の絶縁膜上に、第3の絶縁膜を形成する工程と、

(e)前記第3の絶縁膜上に、第4の絶縁膜を形成する工程と、

(f)前記第4の絶縁膜、前記第3の絶縁膜、前記第2の絶縁膜を選択的に、かつ、この順に個別にエッチングして、前記半導体基板の前記表面のうち前記第1の導電性膜が形成されていない第1の位置に存在する部分を露出する工程と、

(g)前記第1の位置において前記半導体基板と電気的に接触する第2の導電性膜を形成する工程と

を備え、

前記第3の絶縁膜は、前記第4の絶縁膜よりもエッチング速度が遅く、

前記第2の絶縁膜は、前記第1の導電性膜及び前記第1の絶縁膜のそれぞれの側壁である第1領域と、前記半導体基板の前記表面のうち前記第1の導電性膜が形成されていない第2領域とに存在し、前記第1領域に存在する前記第2の絶縁膜の幅は、前記第2領域に存在する前記第2の絶縁膜の膜厚よりも厚く、

(x)前記工程(d)と前記工程(e)との間に実行され、前記半導体基板の前記表面のうち、前記第1の位置とは異なる、前記第1の導電性膜が形成されていない第2の位置の上方に存在する前記第3の絶縁膜を除去する工程と、

(y)前記工程(e)より後の工程において実行され、前記第2の位置の上方に存在する前記第4の絶縁膜及び前記第2の絶縁膜をこの順に連続してエッチングして、前記半導体基板の前記表面のうち前記第2の位置に存在する部分を露出する工程と、

(z)前記第2の位置において前記半導体基板と電気的に接触する第3の導電性膜を形成する工程と、

(s)前記工程(c)と前記工程(d)との間に実行され、前記半導体基板の前記表面のうち前記第1及び第2の位置に存在する部分から、前記第2の絶縁膜を通して前記半導体基板と反対の導電型を有する第1の不純物を導入して第1の不純物領域をそれぞれ形成する工程と、

(t)前記工程(s)と前記工程(d)との間に実行され、前記半導体基板の前記表面のうち前記第1及び第2の位置に存在する部分から、前記半導体基板と反対の導電型を有する第2の不純物を導入して第2の不純物領域を形成する工程と

を更に備え、

前記第2の不純物領域は前記第1の不純物領域よりも広く、かつ、前記第2の不純物領域の不純物濃度は前記第1の不純物領域の不純物濃度よりも低いことを特徴とする、半導体装置の製造方法。 - (a)半導体基板の表面上に、第1の導電性膜を選択的に形成する工程と、

(b)前記第1の導電性膜上に、第1の絶縁膜を形成する工程と、

(c)前記工程(a)及び(b)によって得られる構造上に、第2の絶縁膜を形成する工程と、

(d)前記第2の絶縁膜上に、第3の絶縁膜を形成する工程と、

(e)前記第3の絶縁膜上に、第4の絶縁膜を形成する工程と、

(f)前記第4の絶縁膜、前記第3の絶縁膜、前記第2の絶縁膜を選択的に、かつ、この順に個別にエッチングして、前記半導体基板の前記表面のうち前記第1の導電性膜が形成されていない第1の位置に存在する部分を露出する工程と、

(g)前記第1の位置において前記半導体基板と電気的に接触する第2の導電性膜を形成する工程と

を備え、

前記第3の絶縁膜は、前記第4の絶縁膜よりもエッチング速度が遅く、

前記第2の絶縁膜は、前記第1の導電性膜及び前記第1の絶縁膜のそれぞれの側壁である第1領域と、前記半導体基板の前記表面のうち前記第1の導電性膜が形成されていない第2領域とに存在し、前記第1領域に存在する前記第2の絶縁膜の幅は、前記第2領域に存在する前記第2の絶縁膜の膜厚よりも厚く、

(y)前記工程(g)より後の工程において実行され、前記第4の絶縁膜、前記第3の絶縁膜、前記第2の絶縁膜を選択的に、かつ、この順に個別にエッチングして、前記半導体基板の前記表面のうち、前記第1の位置とは異なる、前記第1の導電性膜が形成されていない第2の位置に存在する部分を露出する工程と、

(z)前記第2の位置において前記半導体基板と電気的に接触する第3の導電性膜を形成する工程と、

(s)前記工程(c)と前記工程(d)との間に実行され、前記半導体基板の前記表面のうち前記第1及び第2の位置に存在する部分から、前記第2の絶縁膜を通して前記半導体基板と反対の導電型を有する第1の不純物を導入して第1の不純物領域をそれぞれ形成する工程と、

(t)前記工程(s)と前記工程(d)との間に実行され、前記半導体基板の前記表面のうち前記第1及び第2の位置に存在する部分から、前記半導体基板と反対の導電型を有する第2の不純物を導入して第2の不純物領域を形成する工程と

を更に備え、

前記第2の不純物領域は前記第1の不純物領域よりも広く、かつ、前記第2の不純物領域の不純物濃度は前記第1の不純物領域の不純物濃度よりも低いことを特徴とする、半導体装置の製造方法。 - (a)半導体基板の表面上に、第1の導電性膜を選択的に形成する工程と、

(b)前記第1の導電性膜上に、第1の絶縁膜を形成する工程と、

(c)前記工程(a)及び(b)によって得られる構造上に、第2の絶縁膜を形成する工程と、

(d)前記第2の絶縁膜上に、第3の絶縁膜を形成する工程と、

(e)前記第3の絶縁膜上に、第4の絶縁膜を形成する工程と、

(f)前記第4の絶縁膜、前記第3の絶縁膜、前記第2の絶縁膜を選択的に、かつ、この順に個別にエッチングして、前記半導体基板の前記表面のうち前記第1の導電性膜が形成されていない第1の位置に存在する部分を露出する工程と、

(g)前記第1の位置において前記半導体基板と電気的に接触する第2の導電性膜を形成する工程と

を備え、

前記第3の絶縁膜は、前記第4の絶縁膜よりもエッチング速度が遅く、

前記第2の絶縁膜は、前記第1の導電性膜及び前記第1の絶縁膜のそれぞれの側壁である第1領域と、前記半導体基板の前記表面のうち前記第1の導電性膜が形成されていない第2領域とに存在し、前記第1領域に存在する前記第2の絶縁膜の幅は、前記第2領域に 存在する前記第2の絶縁膜の膜厚よりも厚く、

(y)前記工程(f)とともに実行され、前記半導体基板の前記表面のうち、前記第1の位置とは異なる、前記第1の導電性膜が形成されていない第2の位置に存在する部分を露出する工程と、

(z)前記工程(g)とともに実行され、前記第2の位置において前記半導体基板と電気的に接触する第3の導電性膜を形成する工程と、

前記工程(g)及び(z)に引き続く、

(h)前記第2及び第3の導電性膜及び前記第4の絶縁膜を覆う第5の絶縁膜を形成する工程と、

(i)前記第5の絶縁膜を選択的にエッチングして前記第3の導電性膜の上方において開口を設ける工程と、

(j)前記第5の絶縁膜の前記開口を介して前記第3の導電性膜と電気的に接続される第4の導電性膜を設ける工程と、

(s)前記工程(c)と前記工程(d)との間に実行され、前記半導体基板の前記表面のうち前記第1及び第2の位置に存在する部分から、前記第2の絶縁膜を通して前記半導体基板と反対の導電型を有する第1の不純物を導入して第1の不純物領域をそれぞれ形成する工程と、

(t)前記工程(s)と前記工程(d)との間に実行され、前記半導体基板の前記表面のうち前記第1及び第2の位置に存在する部分から、前記半導体基板と反対の導電型を有する第2の不純物を導入して第2の不純物領域を形成する工程と

を更に備え、

前記第2の不純物領域は前記第1の不純物領域よりも広く、かつ、前記第2の不純物領域の不純物濃度は前記第1の不純物領域の不純物濃度よりも低いことを特徴とする、半導体装置の製造方法。 - (a)半導体基板の表面上に、第1の導電性膜を選択的に形成する工程と、

(b)前記第1の導電性膜上に、第1の絶縁膜を形成する工程と、

(c)前記工程(a)及び(b)によって得られる構造上に、第2の絶縁膜を形成する工程と、

(d)前記第2の絶縁膜上に、第3の絶縁膜を形成する工程と、

(e)前記第3の絶縁膜上に、第4の絶縁膜を形成する工程と、

(f)前記第4の絶縁膜、前記第3の絶縁膜、前記第2の絶縁膜を選択的に、かつ、この順に個別にエッチングして、前記半導体基板の前記表面のうち前記第1の導電性膜が形成されていない第1の位置に存在する部分を露出する工程と、

(g)前記第1の位置において前記半導体基板と電気的に接触する第2の導電性膜を形成する工程と

を備え、

前記第3の絶縁膜は、前記第4の絶縁膜よりもエッチング速度が遅く、

前記第2の絶縁膜は、前記第1の導電性膜及び前記第1の絶縁膜のそれぞれの側壁である第1領域と、前記半導体基板の前記表面のうち前記第1の導電性膜が形成されていない第2領域とに存在し、前記第1領域に存在する前記第2の絶縁膜の幅は、前記第2領域に存在する前記第2の絶縁膜の膜厚よりも厚く、

(h)前記工程(c)と前記工程(d)との間に実行され、前記半導体基板の前記表面のうち、前記第1の位置とは異なる、前記第1の導電性膜が形成されていない第3の位置に存在する部分から、前記第2の絶縁膜を通して前記半導体基板と反対の導電型を有する第1の不純物を導入して第1の不純物領域を形成する工程と、

(i)前記工程(d)と前記工程(e)との間に実行され、前記第3の位置の上方に存在する前記第3の絶縁膜を除去する工程と、

(j)前記工程(i)と前記工程(e)との間に実行され、前記半導体基板の前記表面のうち前記第3の位置に存在する部分から、前記第2の絶縁膜を通して前記半導体基板と 反対の導電型を有する第2の不純物を導入して第2の不純物領域を形成する工程と、

(k)前記工程(f)と同時に実行され、前記第3の位置の上方に存在する、前記第4の絶縁膜及び前記第2の絶縁膜をこの順に連続してエッチングして、前記半導体基板の前記表面のうち前記第3の位置に存在する部分を露出する工程と、

(l)前記工程(g)と同時に実行され、前記第3の位置において前記半導体基板と電気的に接触する第4の導電性膜を形成する工程と

を更に備え、

前記第2の不純物領域は前記第1の不純物領域よりも広く、かつ、前記第2の不純物領域の不純物濃度は前記第1の不純物領域の不純物濃度よりも低いことを特徴とする、半導体装置の製造方法。

Priority Applications (6)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP34750996A JP3592870B2 (ja) | 1996-12-26 | 1996-12-26 | 半導体装置の製造方法 |

| TW086105273A TW332928B (en) | 1996-12-26 | 1997-04-23 | Producing method of semiconductor device |

| US08/841,783 US6100134A (en) | 1996-12-26 | 1997-05-05 | Method of fabricating semiconductor device |

| DE19724904A DE19724904A1 (de) | 1996-12-26 | 1997-06-12 | Verfahren zum Herstellen eines Halbleiterbauelements |

| KR1019970024652A KR100351929B1 (ko) | 1996-12-26 | 1997-06-13 | 반도체장치의제조방법 |

| CNB971177643A CN1155077C (zh) | 1996-12-26 | 1997-08-29 | 半导体装置的制造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP34750996A JP3592870B2 (ja) | 1996-12-26 | 1996-12-26 | 半導体装置の製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JPH10189901A JPH10189901A (ja) | 1998-07-21 |

| JP3592870B2 true JP3592870B2 (ja) | 2004-11-24 |

Family

ID=18390712

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP34750996A Expired - Fee Related JP3592870B2 (ja) | 1996-12-26 | 1996-12-26 | 半導体装置の製造方法 |

Country Status (6)

| Country | Link |

|---|---|

| US (1) | US6100134A (ja) |

| JP (1) | JP3592870B2 (ja) |

| KR (1) | KR100351929B1 (ja) |

| CN (1) | CN1155077C (ja) |

| DE (1) | DE19724904A1 (ja) |

| TW (1) | TW332928B (ja) |

Families Citing this family (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR100668221B1 (ko) * | 2004-12-31 | 2007-01-11 | 동부일렉트로닉스 주식회사 | Mim 캐패시터 형성 방법 |

| JP6123242B2 (ja) * | 2012-11-09 | 2017-05-10 | 大日本印刷株式会社 | パターン形成方法 |

| CN104617035A (zh) * | 2013-11-05 | 2015-05-13 | 中芯国际集成电路制造(上海)有限公司 | 半导体器件的形成方法 |

Family Cites Families (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR920004541B1 (ko) * | 1989-05-30 | 1992-06-08 | 현대전자산업 주식회사 | 반도체 소자에서 식각베리어층을 사용한 콘택홀 형성방법 |

| US5206187A (en) * | 1991-08-30 | 1993-04-27 | Micron Technology, Inc. | Method of processing semiconductor wafers using a contact etch stop |

| US5439835A (en) * | 1993-11-12 | 1995-08-08 | Micron Semiconductor, Inc. | Process for DRAM incorporating a high-energy, oblique P-type implant for both field isolation and punchthrough |

| JPH07235594A (ja) * | 1994-02-22 | 1995-09-05 | Mitsubishi Electric Corp | 半導体装置の製造方法 |

| JP2765478B2 (ja) * | 1994-03-30 | 1998-06-18 | 日本電気株式会社 | 半導体装置およびその製造方法 |

| US5501998A (en) * | 1994-04-26 | 1996-03-26 | Industrial Technology Research Institution | Method for fabricating dynamic random access memory cells having vertical sidewall stacked storage capacitors |

| JPH0846173A (ja) * | 1994-07-26 | 1996-02-16 | Mitsubishi Electric Corp | 半導体装置及びその製造方法 |

| US5482894A (en) * | 1994-08-23 | 1996-01-09 | Texas Instruments Incorporated | Method of fabricating a self-aligned contact using organic dielectric materials |

| US5489546A (en) * | 1995-05-24 | 1996-02-06 | Micron Technology, Inc. | Method of forming CMOS devices using independent thickness spacers in a split-polysilicon DRAM process |

| US5770498A (en) * | 1996-01-31 | 1998-06-23 | Micron Technology, Inc. | Process for forming a diffusion barrier using an insulating spacer layer |

-

1996

- 1996-12-26 JP JP34750996A patent/JP3592870B2/ja not_active Expired - Fee Related

-

1997

- 1997-04-23 TW TW086105273A patent/TW332928B/zh not_active IP Right Cessation

- 1997-05-05 US US08/841,783 patent/US6100134A/en not_active Expired - Lifetime

- 1997-06-12 DE DE19724904A patent/DE19724904A1/de not_active Withdrawn

- 1997-06-13 KR KR1019970024652A patent/KR100351929B1/ko not_active IP Right Cessation

- 1997-08-29 CN CNB971177643A patent/CN1155077C/zh not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| DE19724904A1 (de) | 1998-07-02 |

| CN1186336A (zh) | 1998-07-01 |

| CN1155077C (zh) | 2004-06-23 |

| TW332928B (en) | 1998-06-01 |

| US6100134A (en) | 2000-08-08 |

| KR19980063335A (ko) | 1998-10-07 |

| JPH10189901A (ja) | 1998-07-21 |

| KR100351929B1 (ko) | 2003-04-10 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US20020081799A1 (en) | Contact fabrication method for semiconductor device | |

| JP3592870B2 (ja) | 半導体装置の製造方法 | |

| JP3190659B2 (ja) | 半導体メモリ及びその製造方法 | |

| JP3209639B2 (ja) | 半導体装置の製造方法 | |

| KR19990005921A (ko) | 반도체 메모리 장치 및 그 제조 방법 | |

| KR20040048039A (ko) | 반도체 소자의 제조 방법 | |

| KR100228352B1 (ko) | 반도체 소자 제조방법 | |

| JP3172229B2 (ja) | 半導体装置の製造方法 | |

| KR20000045437A (ko) | 반도체소자의 자기정렬적인 콘택 형성방법 | |

| KR100267772B1 (ko) | 반도체 메모리 소자의 저항 패턴 형성 방법 | |

| KR0172513B1 (ko) | 반도체 소자의 콘택 형성 방법 | |

| KR100240249B1 (ko) | 서로 다른 게이트 산화막 및 게이트 전극을 갖는반도체 장치의 제조 방법 | |

| KR960006719B1 (ko) | 반도체 메모리장치의 셀프얼라인콘택 형성방법 | |

| JPH10303297A (ja) | 半導体装置およびその製造方法 | |

| KR100329750B1 (ko) | 반도체소자제조방법 | |

| KR950003912B1 (ko) | 고축적 용량을 갖는 캐패시터 콘택홀 제조방법 | |

| KR100586539B1 (ko) | 테스트 패턴 형성방법 | |

| KR20050002479A (ko) | 랜딩플러그 형성 방법 | |

| KR100321759B1 (ko) | 반도체소자제조방법 | |

| JP3374837B2 (ja) | スタックトキャパシタ型dramの製造方法 | |

| JP3111961B2 (ja) | 半導体装置の製造方法 | |

| JPH0685171A (ja) | パターン形成方法および半導体装置の製造方法 | |

| JPH1032245A (ja) | 半導体装置の製造方法 | |

| JP2000058640A (ja) | 半導体装置の製造方法 | |

| JPH10242275A (ja) | 半導体装置の製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20040430 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20040608 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20040729 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20040824 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20040826 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20080903 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20080903 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20090903 Year of fee payment: 5 |

|

| LAPS | Cancellation because of no payment of annual fees |