CN1155077C - 半导体装置的制造方法 - Google Patents

半导体装置的制造方法 Download PDFInfo

- Publication number

- CN1155077C CN1155077C CNB971177643A CN97117764A CN1155077C CN 1155077 C CN1155077 C CN 1155077C CN B971177643 A CNB971177643 A CN B971177643A CN 97117764 A CN97117764 A CN 97117764A CN 1155077 C CN1155077 C CN 1155077C

- Authority

- CN

- China

- Prior art keywords

- dielectric film

- film

- semiconductor substrate

- etching

- conducting film

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 342

- 238000004519 manufacturing process Methods 0.000 title claims abstract description 184

- 239000000758 substrate Substances 0.000 claims abstract description 217

- 238000005530 etching Methods 0.000 claims abstract description 195

- 238000000034 method Methods 0.000 claims description 98

- 239000012535 impurity Substances 0.000 claims description 47

- 230000015572 biosynthetic process Effects 0.000 claims description 34

- PMOWTIHVNWZYFI-WAYWQWQTSA-N cis-2-coumaric acid Chemical compound OC(=O)\C=C/C1=CC=CC=C1O PMOWTIHVNWZYFI-WAYWQWQTSA-N 0.000 claims description 6

- 239000011229 interlayer Substances 0.000 abstract description 112

- 230000001681 protective effect Effects 0.000 abstract description 48

- 229910052814 silicon oxide Inorganic materials 0.000 abstract description 31

- 239000013078 crystal Substances 0.000 abstract description 19

- 230000007547 defect Effects 0.000 abstract description 19

- 229910052581 Si3N4 Inorganic materials 0.000 abstract description 3

- 238000002955 isolation Methods 0.000 abstract 1

- 239000010410 layer Substances 0.000 description 79

- 229920002120 photoresistant polymer Polymers 0.000 description 70

- 239000003990 capacitor Substances 0.000 description 54

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 26

- 238000005229 chemical vapour deposition Methods 0.000 description 25

- 238000009792 diffusion process Methods 0.000 description 14

- 238000009413 insulation Methods 0.000 description 12

- 230000004888 barrier function Effects 0.000 description 11

- 239000003795 chemical substances by application Substances 0.000 description 11

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 10

- 229920005591 polysilicon Polymers 0.000 description 10

- 230000003647 oxidation Effects 0.000 description 9

- 238000007254 oxidation reaction Methods 0.000 description 9

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 8

- 230000000694 effects Effects 0.000 description 8

- 229910052710 silicon Inorganic materials 0.000 description 8

- 239000010703 silicon Substances 0.000 description 8

- 150000002500 ions Chemical class 0.000 description 5

- 238000010276 construction Methods 0.000 description 4

- 230000005684 electric field Effects 0.000 description 4

- 230000006870 function Effects 0.000 description 4

- 238000005468 ion implantation Methods 0.000 description 4

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 3

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 3

- 229910052796 boron Inorganic materials 0.000 description 3

- 229910052698 phosphorus Inorganic materials 0.000 description 3

- 239000011574 phosphorus Substances 0.000 description 3

- 230000001052 transient effect Effects 0.000 description 3

- 229910008484 TiSi Inorganic materials 0.000 description 2

- 229910052785 arsenic Inorganic materials 0.000 description 2

- RQNWIZPPADIBDY-UHFFFAOYSA-N arsenic atom Chemical compound [As] RQNWIZPPADIBDY-UHFFFAOYSA-N 0.000 description 2

- 238000000151 deposition Methods 0.000 description 2

- 230000008021 deposition Effects 0.000 description 2

- 230000005611 electricity Effects 0.000 description 2

- 230000005764 inhibitory process Effects 0.000 description 2

- 230000002093 peripheral effect Effects 0.000 description 2

- 229910016570 AlCu Inorganic materials 0.000 description 1

- 230000002950 deficient Effects 0.000 description 1

- 239000002019 doping agent Substances 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 238000003475 lamination Methods 0.000 description 1

- 239000003595 mist Substances 0.000 description 1

- 239000000203 mixture Substances 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/01—Manufacture or treatment

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76801—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing

- H01L21/76802—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing by forming openings in dielectrics

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76801—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing

- H01L21/76829—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing characterised by the formation of thin functional dielectric layers, e.g. dielectric etch-stop, barrier, capping or liner layers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76897—Formation of self-aligned vias or contact plugs, i.e. involving a lithographically uncritical step

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/01—Manufacture or treatment

- H10B12/02—Manufacture or treatment for one transistor one-capacitor [1T-1C] memory cells

- H10B12/03—Making the capacitor or connections thereto

- H10B12/033—Making the capacitor or connections thereto the capacitor extending over the transistor

Landscapes

- Engineering & Computer Science (AREA)

- Manufacturing & Machinery (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Semiconductor Memories (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

- Drying Of Semiconductors (AREA)

- Formation Of Insulating Films (AREA)

Abstract

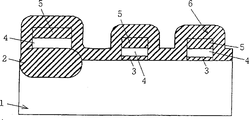

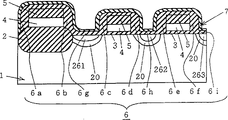

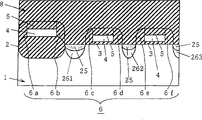

提供一种不使位线与字线连接而以自行调整的方式连接在半导体衬底上且不产生成结晶缺陷的半导体装置。在半导体(例如Si)衬底1上依次分别形成元件分离绝缘膜2、栅氧化膜3、栅极4(字线)、绝缘膜5之后,形成侧壁6a~6f。此时,形成衬底保护氧化膜6g~6i,从而不使半导体衬底1露出。在形成源/漏区261~263之后,淀积由Si3N4或SiON等构成的绝缘膜7,此后在全部表面上形成层间绝缘膜8。绝缘膜7与层间绝缘膜8相比刻蚀速度慢。

Description

本发明涉及半导体装置的制造方法,该半导体装置由在半导体衬底的上方形成的两层布线层(字线及位线)、再在上述布线层的上方形成的电容器、用于将位线及电容器分别连接在半导体衬底上的连接电极、以及将字线作为栅极的晶体管构成。

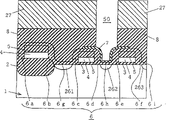

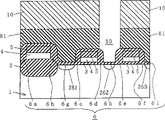

图111~图122是作为现有技术依次表示半导体装置(DRAM)的制造工序之一例的剖面图。首先,利用LOCOS法在半导体(例如Si)衬底1上形成元件分离绝缘膜2之后,在不形成元件分离绝缘膜2的半导体衬底1上有选择地形成栅氧化膜3、栅极4及绝缘膜5的叠层结构(图111)。栅极4具有作为DRAM的字线的功能。然后,利用CVD法在全部表面上形成厚度为例如数百nm的硅氧化膜(图112)。

其次,通过沿垂直于半导体衬底1的方向进行刻蚀速率高的各向异性的氧化膜刻蚀,在栅氧化膜3、栅极4及绝缘膜5各自的侧壁部分形成侧壁6a~6f。然后,将绝缘膜5及侧壁6a~6f作为掩模,进行离子注入,在半导体衬底1内分别形成源/漏区261~263(图113)。

其次,利用CVD法在全部表面上淀积硅氧化膜,形成例如数百nm厚度的层间绝缘膜8(图114)。其次,利用通常的复制方法,在层间绝缘膜8上形成呈规定图形的光致抗蚀剂10,形成接触孔50,使源/漏区262露出来。然后将光致抗蚀剂10除去(图115)。

其次,形成具有WSi/多晶硅或TiSi/多晶硅等结构的导电膜9,以便通过接触孔50与源/漏区262相连接(图116)。该导电膜9具有作为DRAM的位线的功能。

其次,利用CVD法在全部表面上淀积例如硅氧化膜,形成层间绝缘膜11(图117),利用通常的复制方法,在层间绝缘膜11上形成呈规定图形的光致抗蚀剂12(图118)。

其次,将光致抗蚀剂12作为掩模,通过利用相同的刻蚀剂对层间绝缘膜11、8进行刻蚀,形成接触孔51,使源/漏区261露出来。然后将光致抗蚀剂12除去(图119)。

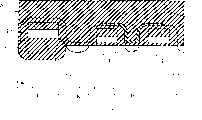

其次,为了填充接触孔51,利用CVD法淀积多晶硅,形成电容器下部电极13。电容器下部电极13通过接触孔51与源/漏区261相连接。然后在全部表面上淀积Si3N4膜,形成电容器介质膜14。利用CVD法再在电容器介质膜14上淀积多晶硅,形成电容器上部电极15(图120)。

其次,利用CVD法在电容器上部电极15上形成由例如硅氧化膜构成的层间绝缘膜16(图121),在层间绝缘膜16上有选择地形成由AlSiCu构成的布线层17(图122)。

可是,如果采用这种现有的半导体装置的制造方法,则由于在形成侧壁6a~6f时,必须对数百nm厚的硅氧化膜进行刻蚀,所以难以控制刻蚀,由于过量刻蚀而使半导体衬底1的表面受到损伤。再者,在半导体衬底1的表面上形成接触孔50、51时,也会由于过量刻蚀而受到损伤。这样就会在源/漏区261、262附近产生结晶缺陷25(图113~图122),所以这些缺陷成为诱发漏泄电流的原因,存在引起器件的误操作的问题。

例如在DRAM中,假定需要进行以某一定的间隔改写存储单元中存储的数据的工作(更新),但如果在电容器下部电极13连接的源/漏区261附近存在结晶缺陷25,则在电容器下部电极13上蓄积的电荷就会作为漏泄电流向半导体衬底1流失,存在不能正确地改写数据的问题。

另外,在形成光致抗蚀剂10的工序中,当由于工艺中的偏差等使得栅极4的图形和光致抗蚀剂10的叠合发生偏移时,如图116所示,作为位线的导电膜9与作为字线的栅极4接触,存在引起器件的工作不良的问题。

本发明就是为了解决这样的问题而开发的,其目的在于提供这样一种半导体装置的制造方法,该方法不会使位线和字线接触而能以自行调整方式连接在半导体衬底上,而且不会产生成为诱发漏泄电流的原因的半导体衬底的结晶缺陷。

本发明的第1方面的半导体装置的制造方法的特征在于包括以下工序:(a)在半导体衬底的表面上有选择地形成第1导电膜的工序;(b)在第1导电膜上形成第1绝缘膜的工序;(c)在由工序(a)及(b)获得的结构上形成第2绝缘膜的工序;(d)在第2绝缘膜上形成第3绝缘膜的工序;(e)在第3绝缘膜上形成第4绝缘膜的工序;(f)对第4绝缘膜、第3绝缘膜、第2绝缘膜有选择地、而且按照该顺序进行个别地刻蚀,使存在于半导体衬底的表面内未形成第1导电膜的第1位置的部分露出的工序;以及(g)在第1位置形成与半导体衬底导电性接触的第2导电膜的工序,其中:第3绝缘膜比第4绝缘膜的刻蚀速度慢。

另外,本发明的第2方面的方法的特征在于:在第1方面的半导体装置的制造方法中,第2绝缘膜存在于作为第1导电膜及第1绝缘膜各自的侧壁的第1区和半导体衬底的表面内未形成第1导电膜的第2区,存在于第1区的第2绝缘膜的宽度比存在于第2区的第2绝缘膜的厚度要厚。

另外,本发明的第3方面的方法的特征在于,第2方面的半导体装置的制造方法还包括以下工序:(x)在工序(d)和工序(e)之间执行的、将存在于半导体衬底的表面内与第1位置不同的未形成第1导电膜的第2位置的上方的第3绝缘膜除去的工序;(y)在由工序(e)以后的工序中执行的、对存在于第2位置的上方的第4绝缘膜及第2绝缘膜按照该顺序连续地进行刻蚀,使存在于半导体衬底的表面内第2位置的部分露出的工序;以及(z)在第2位置形成与半导体衬底导电性地接触的第3导电膜的工序。

另外,本发明的第4方面的方法的特征在于,第2方面的半导体装置的制造方法还包括以下工序:(y)在由工序(g)以后的工序中执行的对第4绝缘膜、第3绝缘膜、第2绝缘膜有选择地、而且按照该顺序进行个别地刻蚀,使存在于半导体衬底的表面内与第1位置不同的未形成第1导电膜的第2位置的部分露出的工序;以及(z)在第2位置形成与半导体衬底导电性地接触的第3导电膜的工序。

另外,本发明的第5方面的方法的特征在于,第2方面的半导体装置的制造方法中:在工序(f)中使存在于半导体衬底的表面内与第1位置不同的未形成第1导电膜的第2位置的部分露出,在工序(g)中在第2位置还形成与半导体衬底导电性地接触的第3导电膜,继工序(g)之后还包括以下工序:(h)形成覆盖第2及第3导电膜及第4绝缘膜的第5绝缘膜的工序;(i)对第5绝缘膜有选择地进行刻蚀,在第3导电膜的上方设置开口的工序;以及(j)通过第5绝缘膜的开口设置与第3导电膜导电性地接触的第4导电膜的工序。

另外,本发明的第6方面的半导体装置的制造方法的特征在于,包括以下工序:(a)在半导体衬底的表面上有选择地形成第1导电膜的工序;(b)在第1导电膜上形成第1绝缘膜的工序;(c)在由工序(a)及(b)获得的结构上形成第2绝缘膜的工序;(d)在第2绝缘膜上形成第3绝缘膜的工序;(e)对第3绝缘膜及第2绝缘膜有选择地、而且按照该顺序进行个别地刻蚀,使存在于半导体衬底的表面内未形成第1导电膜的第1位置的部分露出的工序;以及(f)在第1位置形成与半导体衬底导电性接触的第2导电膜的工序,其中:第2绝缘膜比第3绝缘膜的刻蚀速度慢,另外,第2绝缘膜存在于作为第1导电膜及第1绝缘膜各自的侧壁的第1区和半导体衬底的表面内未形成第1导电膜的第2区,存在于第1区的第2绝缘膜的宽度大于存在于第2区的第2绝缘膜的厚度。

另外,本发明的第7方面的方法的特征在于,第6方面的半导体装置的制造方法还包括以下工序:(y)在由工序(d)以后的工序中执行的、对第3绝缘膜、第2绝缘膜有选择地、而且按照该顺序进行个别地刻蚀,使存在于半导体衬底的表面内与第1位置不同的未形成第1导电膜的第2位置的部分露出的工序;以及(z)在第2位置形成与半导体衬底导电性地接触的第3导电膜的工序。

另外,本发明的第8方面的方法的特征在于,在第6方面的半导体装置的制造方法中:在工序(e)中使存在于半导体衬底的表面内与第1位置不同的未形成第1导电膜的第2位置的部分露出,在工序(f)中在第2位置还形成与半导体衬底导电性地接触的第3导电膜,继工序(f)之后还包括以下工序:(g)形成覆盖第2及第3导电膜及第3绝缘膜的第4绝缘膜的工序;(h)对第4绝缘膜有选择地进行刻蚀,在第3导电膜的上方设置开口的工序;以及(i)通过第4绝缘膜的开口设置与第3导电膜导电性地接触的第4导电膜的工序,第4绝缘膜比第3绝缘膜的刻蚀速度慢。

另外,本发明的第9方面的方法的特征在于,第3、4、5、7、8任意一方面所述的半导体装置的制造方法还包括以下工序:(s)在工序(c)和工序(d)之间执行的、从存在于半导体衬底的表面内的第2位置的部分通过第2绝缘膜掺入呈与半导体衬底相反的导电类型的第1种杂质而形成第1掺杂区的工序;以及(t)在工序(y)和工序(z)之间执行的、从存在于半导体衬底的表面内的第2位置的部分将呈与半导体衬底相反的导电类型的第2种杂质掺入而形成第2掺杂区的工序,第2掺杂区比第1掺杂区宽,而且第2掺杂区的杂质浓度比第1掺杂区的杂质浓度低。

另外,本发明的第10方面的方法的特征在于,第3、4、5、7、8任意一方面所述的半导体装置的制造方法还包括以下工序:(s)在工序(c)和工序(d)之间执行的、从存在于半导体衬底的表面内的第1及第2位置的部分通过第2绝缘膜掺入呈与半导体衬底相反的导电类型的第1种杂质而分别形成第1掺杂区的工序;以及(t)在工序(s)和工序(d)之间执行的从存在于半导体衬底的表面内的第1及第2位置的部分,掺入呈与半导体衬底相反的导电类型的第2种杂质而形成第2掺杂区的工序,第2掺杂区比第1掺杂区宽,而且第2掺杂区的杂质浓度比第1掺杂区的杂质浓度低。

另外,本发明的第11方面的方法的特征在于,第2方面的半导体装置的制造方法还包括以下工序:(h)在工序(c)和工序(d)之间执行的、从存在于半导体衬底的表面内与第1位置不同的未形成第1导电膜的第3位置的部分通过第2绝缘膜掺入呈与半导体衬底相反的导电类型的第1种杂质而形成第1掺杂区的工序;(i)在工序(d)和工序(e)之间执行的、将存在于第3位置的上方的第3绝缘膜除去的工序;(j)在工序(i)和工序(e)之间执行的、从存在于半导体衬底的表面内的第3位置的部分通过第2绝缘膜掺入呈与半导体衬底相反的导电类型的第2种杂质而形成第2掺杂区的工序;(k)与工序(f)同时执行的对存在于第3位置的上方的第4绝缘膜及第2绝缘膜按照该顺序连续地进行刻蚀,使存在于半导体衬底的表面内第3位置的部分露出的工序;以及(l)与工序(g)同时执行的、在第3位置形成与半导体衬底导电性接触的第4导电膜的工序,第2掺杂区比第1掺杂区宽,而且第2掺杂区的杂质浓度比第1掺杂区的杂质浓度低。

图1是表示本发明的实施例1的半导体装置的制造工序的剖面图。

图2是表示本发明的实施例1的半导体装置的制造工序的剖面图。

图3是表示本发明的实施例1的半导体装置的制造工序的剖面图。

图4是表示本发明的实施例1的半导体装置的制造工序的剖面图。

图5是表示本发明的实施例1的半导体装置的制造工序的剖面图。

图6是表示本发明的实施例1的半导体装置的制造工序的剖面图。

图7是表示本发明的实施例1的半导体装置的制造工序的剖面图。

图8是表示本发明的实施例1的半导体装置的制造工序的剖面图。

图9是表示本发明的实施例1的半导体装置的制造工序的剖面图。

图10是表示本发明的实施例1的半导体装置的制造工序的剖面图。

图11是表示本发明的实施例1的半导体装置的制造工序的剖面图。

图12是表示本发明的实施例1的半导体装置的制造工序的剖面图。

图13是表示本发明的实施例1的半导体装置的制造工序的剖面图。

图14是表示本发明的实施例1的半导体装置的制造工序的剖面图。

图15是表示本发明的实施例1的半导体装置的制造工序的剖面图。

图16是表示本发明的实施例2的半导体装置的制造工序的剖面图。

图17是表示本发明的实施例2的半导体装置的制造工序的剖面图。

图18是表示本发明的实施例2的半导体装置的制造工序的剖面图。

图19是表示本发明的实施例2的半导体装置的制造工序的剖面图。

图20是表示本发明的实施例2的半导体装置的制造工序的剖面图。

图21是表示本发明的实施例2的半导体装置的制造工序的剖面图。

图22是表示本发明的实施例2的半导体装置的制造工序的剖面图。

图23是表示本发明的实施例2的半导体装置的制造工序的剖面图。

图24是表示本发明的实施例2的半导体装置的制造工序的剖面图。

图25是表示本发明的实施例2的半导体装置的制造工序的剖面图。

图26是表示本发明的实施例2的半导体装置的制造工序的剖面图。

图27是表示本发明的实施例2的半导体装置的制造工序的剖面图。

图28是表示本发明的实施例3的半导体装置的制造工序的剖面图。

图29是表示本发明的实施例3的半导体装置的制造工序的剖面图。

图30是表示本发明的实施例3的半导体装置的制造工序的剖面图。

图31是表示本发明的实施例3的半导体装置的制造工序的剖面图。

图32是表示本发明的实施例3的半导体装置的制造工序的剖面图。

图33是表示本发明的实施例3的半导体装置的制造工序的剖面图。

图34是表示本发明的实施例3的半导体装置的制造工序的剖面图。

图35是表示本发明的实施例4的半导体装置的制造工序的剖面图。

图36是表示本发明的实施例4的半导体装置的制造工序的剖面图。

图37是表示本发明的实施例4的半导体装置的制造工序的剖面图。

图38是表示本发明的实施例4的半导体装置的制造工序的剖面图。

图39是表示本发明的实施例4的半导体装置的制造工序的剖面图。

图40是表示本发明的实施例4的半导体装置的制造工序的剖面图。

图41是表示本发明的实施例4的半导体装置的制造工序的剖面图。

图42是表示本发明的实施例4的半导体装置的制造工序的剖面图。

图43是表示本发明的实施例4的半导体装置的制造工序的剖面图。

图44是表示本发明的实施例4的半导体装置的制造工序的剖面图。

图45是表示本发明的实施例5的半导体装置的制造工序的剖面图。

图46是表示本发明的实施例5的半导体装置的制造工序的剖面图。

图47是表示本发明的实施例5的半导体装置的制造工序的剖面图。

图48是表示本发明的实施例5的半导体装置的制造工序的剖面图。

图49是表示本发明的实施例5的半导体装置的制造工序的剖面图。

图50是表示本发明的实施例5的半导体装置的制造工序的剖面图。

图51是表示本发明的实施例5的半导体装置的制造工序的剖面图。

图52是表示本发明的实施例5的半导体装置的制造工序的剖面图。

图53是表示本发明的实施例5的半导体装置的制造工序的剖面图。

图54是表示本发明的实施例5的半导体装置的制造工序的剖面图。

图55是表示本发明的实施例5的半导体装置的制造工序的剖面图。

图56是表示本发明的实施例5的半导体装置的制造工序的剖面图。

图57是表示本发明的实施例5的半导体装置的制造工序的剖面图。

图58是表示本发明的实施例6的半导体装置的制造工序的剖面图。

图59是表示本发明的实施例6的半导体装置的制造工序的剖面图。

图60是表示本发明的实施例6的半导体装置的制造工序的剖面图。

图61是表示本发明的实施例6的半导体装置的制造工序的剖面图。

图62是表示本发明的实施例6的半导体装置的制造工序的剖面图。

图63是表示本发明的实施例6的半导体装置的制造工序的剖面图。

图64是表示本发明的实施例6的半导体装置的制造工序的剖面图。

图65是表示本发明的实施例7的半导体装置的制造工序的剖面图。

图66是表示本发明的实施例7的半导体装置的制造工序的剖面图。

图67是表示本发明的实施例7的半导体装置的制造工序的剖面图。

图68是表示本发明的实施例7的半导体装置的制造工序的剖面图。

图69是表示本发明的实施例7的半导体装置的制造工序的剖面图。

图70是表示本发明的实施例7的半导体装置的制造工序的剖面图。

图71是表示本发明的实施例7的半导体装置的制造工序的剖面图。

图72是表示本发明的实施例7的半导体装置的制造工序的剖面图。

图73是表示本发明的实施例7的半导体装置的制造工序的剖面图。

图74是表示本发明的实施例8的半导体装置的制造工序的剖面图。

图75是表示本发明的实施例8的半导体装置的制造工序的剖面图。

图76是表示本发明的实施例8的半导体装置的制造工序的剖面图。

图77是表示本发明的实施例8的半导体装置的制造工序的剖面图。

图78是表示本发明的实施例9的半导体装置的制造工序的剖面图。

图79是表示本发明的实施例9的半导体装置的制造工序的剖面图。

图80是表示本发明的实施例9的半导体装置的制造工序的剖面图。

图81是表示本发明的实施例9的半导体装置的制造工序的剖面图。

图82是表示本发明的实施例9的半导体装置的制造工序的剖面图。

图83是表示本发明的实施例9的半导体装置的制造工序的剖面图。

图84是表示本发明的实施例9的半导体装置的制造工序的剖面图。

图85是表示本发明的实施例9的半导体装置的制造工序的剖面图。

图86是表示本发明的实施例9的半导体装置的制造工序的剖面图。

图87是表示本发明的实施例9的半导体装置的制造工序的剖面图。

图88是表示本发明的实施例9的半导体装置的制造工序的剖面图。

图89是表示本发明的实施例9的半导体装置的制造工序的剖面图。

图90是表示本发明的实施例9的半导体装置的制造工序的剖面图。

图91是表示本发明的实施例10的半导体装置的制造工序的剖面图。

图92是表示本发明的实施例10的半导体装置的制造工序的剖面图。

图93是表示本发明的实施例10的半导体装置的制造工序的剖面图。

图94是表示本发明的实施例10的半导体装置的制造工序的剖面图。

图95是表示本发明的实施例10的半导体装置的制造工序的剖面图。

图96是表示本发明的实施例10的半导体装置的制造工序的剖面图。

图97是表示本发明的实施例10的半导体装置的制造工序的剖面图。

图98是表示本发明的实施例10的半导体装置的制造工序的剖面图。

图99是表示本发明的实施例10的半导体装置的制造工序的剖面图。

图100是表示本发明的实施例10的半导体装置的制造工序的剖面图。

图101是表示本发明的实施例10的半导体装置的制造工序的剖面图。

图102是表示本发明的实施例10的半导体装置的制造工序的剖面图。

图103是表示本发明的实施例10的半导体装置的制造工序的剖面图。

图104是表示本发明的实施例10的半导体装置的制造工序的剖面图。

图105是表示本发明的实施例10的半导体装置的制造工序的剖面图。

图106是表示本发明的实施例10的半导体装置的制造工序的剖面图。

图107是表示本发明的实施例10的半导体装置的制造工序的剖面图。

图108是表示本发明的实施例10的半导体装置的制造工序的剖面图。

图109是表示本发明的实施例11的半导体装置的制造工序的剖面图。

图110是表示本发明的实施例11的半导体装置的制造工序的剖面图。

图111是表示现有的半导体装置的制造工序的剖面图。

图112是表示现有的半导体装置的制造工序的剖面图。

图113是表示现有的半导体装置的制造工序的剖面图。

图114是表示现有的半导体装置的制造工序的剖面图。

图115是表示现有的半导体装置的制造工序的剖面图。

图116是表示现有的半导体装置的制造工序的剖面图。

图117是表示现有的半导体装置的制造工序的剖面图。

图118是表示现有的半导体装置的制造工序的剖面图。

图119是表示现有的半导体装置的制造工序的剖面图。

图120是表示现有的半导体装置的制造工序的剖面图。

图121是表示现有的半导体装置的制造工序的剖面图。

图122是表示现有的半导体装置的制造工序的剖面图。

实施例1

图1~图15是依次表示本发明的实施例1的半导体装置的制造工序的剖面图。首先,利用LOCOS法在半导体(例如Si)衬底1上形成元件分离绝缘膜2之后,在不形成元件分离绝缘膜2的半导体衬底1上有选择地形成按照栅氧化膜3、栅极4、绝缘膜5的顺序叠层的结构(图1)。该栅极4具有作为DRAM的字线的功能。另外,在图1中设在元件分离绝缘膜2上的栅极4的下方不设栅氧化膜3,但在垂直于纸面的方向上,隐藏在元件分离绝缘膜2的后方形成上述的叠层结构。

其次,利用CVD法在全部表面上淀积硅氧化膜6(图2)。其次,通过沿垂直于半导体衬底1的方向进行刻蚀速率高的各向异性的氧化膜刻蚀,来刻蚀硅氧化膜6,在栅氧化膜3、栅极4、绝缘膜5各自的侧壁部分留下硅氧化膜6,形成侧壁6a~6f。但进行该刻蚀时,在半导体衬底1上留有规定厚度的硅氧化膜6,以便不使半导体衬底1露出,形成衬底保护氧化膜6g~6i。这里,在通过各向异性的氧化膜刻蚀将硅氧化膜除去时,精确地控制该刻蚀,将衬底保护氧化膜6g~6i的厚度设定在不使半导体衬底1受损伤的范围。例如在本实施例中为5~20nm。此后,利用呈与半导体衬底1相反的导电类型的离子,将离子通过衬底保护氧化膜6g~6i注入半导体衬底1内,分别形成源/漏区261~263(图3)。

其次。用CVD法在全部表面上淀积厚度为5~100nm的由Si3N4或SiON等构成的绝缘膜7(图4)。

其次,利用CVD法淀积例如硅氧化膜,形成层间绝缘膜8(图5)。

其次,利用通常的复制方法,在层间绝缘膜8上且在源/漏区262的上方形成呈开口的光致抗蚀剂10,将该光致抗蚀剂10作为掩模,利用例如使用C4F8气体的氧化膜刻蚀方法,只刻蚀层间绝缘膜8,形成接触孔50(图6)。在该氧化膜刻蚀蚀方法中,对用CVD法形成的由Si3N4、SiON构成的绝缘膜7的刻蚀速度比用CVD法形成的由硅氧化膜构成的层间绝缘膜8慢,所以在绝缘膜7露出来的时刻,能容易地停止腐蚀。

其次,将光致抗蚀剂10作为掩模,利用例如使用CF4气体的刻蚀方法,将绝缘膜7除去(图7)。再将光致抗蚀剂10作为掩模,通过进行各向异性的氧化膜刻蚀,将衬底保护氧化膜6h除去,使源/漏区262露出来。这时侧壁6d、6e也被除去,但只不过除去相当于衬底保护氧化膜6h的厚度,然后将光致抗蚀剂10除去(图8)。

其次,形成具有WSi/多晶硅或TiSi/多晶硅等结构的导电膜9,以便通过接触孔50与源/漏区262相连接(图9)。该导电膜9具有作为DRAM的位线的功能。

其次,利用CVD法在全部表面上淀积例如硅氧化膜,形成层间绝缘膜11(图10)。再利用通常的复制方法,在层间绝缘膜11上且在源/漏区261的上方形成呈开口的光致抗蚀剂12(图11)。其次,将光致抗蚀剂12作为掩模,通过刻蚀层间绝缘膜11、8、绝缘膜7及保护膜6g,形成接触孔51,使源/漏区261露出来。这样的刻蚀可以利用已知的方法、使用同一种刻蚀剂进行。然后将光致抗蚀剂12除去(图12)。

其次,为了填充接触孔51,利用CVD法淀积多晶硅,形成电容器下部电极13。电容器下部电极13通过接触孔51与源/漏区261相连接。然后在全部表面上淀积Si3N4膜,形成电容器介质膜14。利用CVD法再在电容器介质膜14上淀积多晶硅,形成电容器上部电极15(图13)。

其次,利用CVD法在电容器上部电极15上淀积例如硅氧化膜,形成层间绝缘膜16(图14),在层间绝缘膜16上有选择地形成例如由AlCu、AlSiCu构成的布线层17(图15)。

这样,如果采用本实施例1的半导体装置的制造方法,则在形成接触孔50时,暂时将绝缘膜7作为阻挡层,对层间绝缘膜8进行刻蚀。因此在该阶段不刻蚀衬底保护氧化膜6h,所以层间绝缘膜8的刻蚀不会损伤源/漏区262。而且,衬底保护氧化膜6h薄,对其进行刻蚀时的刻蚀量容易控制,所以仍然不会损伤源/漏区262,同时绝缘膜5和侧壁6d、6e分别除去的量从总体来看很少,所以接触孔50能不与栅极4接触而以自行调整的方式形成。

另外,如果着眼于源/漏区261的状态,若采用现有的制造方法,则在形成侧壁6a~6f时及形成接触孔51时的2个工序中,半导体衬底1被过量刻蚀,结晶缺陷也大,与此不同,如果采用本实施例1的半导体装置的制造方法,则在形成侧壁6a~6f时,由于有留下来的衬底保护氧化膜6g,所以不会由这时的刻蚀造成半导体衬底1的过量刻蚀,也不会产生结晶缺陷25。因此,与现有的制造方法相比,能抑制源/漏区261附近的结晶缺陷25,所以通过接触孔51将电容器下部电极13与其连接时,还能抑制诱发引起器件误操作的漏泄电流。

实施例2

在实施例1中,在形成了绝缘膜7以后的工序中形成了层间绝缘膜8,但也可以在形成了绝缘膜7以后而在形成层间绝缘膜8之前,将形成接触孔50的区域以外的绝缘膜7除去。

图16~图27是依次表示本发明的实施例2的半导体装置的制造工序的剖面图。首先,经过与实施例1的工序相同的工序,获得与图4所示的结构相同的结构。此后,利用通常的复制方法,在形成接触孔50的区域形成光致抗蚀剂24(图16)。

以下,经过与实施例1的工序相同的工序,在形成层间绝缘膜11之前,在全部表面上淀积层间绝缘膜8(图18),将在它上面形成的光致抗蚀剂27作为掩模,利用例如使用C4F8气体的氧化膜刻蚀方法,只刻蚀层间绝缘膜8,形成接触孔50(图19)。再将光致抗蚀剂27作为掩模,刻蚀绝缘膜7(图20),在将衬底保护氧化膜6h除去后,将光致抗蚀剂27除去(图21)。其次,通过接触孔50将导电膜9与源/漏区262连接起来(图22)。在全部表面上形成层间绝缘膜11(图23)。

此后,利用通常的复制方法,在层间绝缘膜11上形成光致抗蚀剂12,将该光致抗蚀剂12作为掩膜,通过用同一种刻蚀剂刻蚀层间绝缘膜11、8、衬底保护氧化膜6g,形成接触孔51,使源/漏区261露出来(图24)。

以下,经过与实施例1的工序相同的工序,直到形成布线层17。即,形成电容器下部电极13,以便通过接触孔51与源/漏区261连接,然后在全部表面上分别形成电容器介质膜14、电容器上部电极15(图25)。此后在全部表面上形成层间绝缘膜16后(图26),有选择地在它上面形成布线层17(图27)。

由于需要这样来形成接触孔51,使其不与作为字线的栅极4及作为位线的导电膜9接触,所以当然必须形成微细的接触孔。因此,在形成微细的接触孔51时,不希望存在象绝缘膜7这样的刻蚀速度慢的膜。如果采用本实施例2的半导体装置的制造方法,则由于在形成微细的接触孔51时,不需要刻蚀这种刻蚀速度慢的绝缘膜7,所以能容易地形成接触孔51。

实施例3

在实施例1中,在形成了绝缘膜11之后,将用通常的复制方法形成的光致抗蚀剂12作为掩模,通过使用同一种刻蚀剂的单一的工序刻蚀层间绝缘膜11、8、绝缘膜7、衬底保护氧化膜6g,形成了接触孔51,但也可以通过多个工序形成接触孔51。

图28~图34是依次表示本发明的实施例3的半导体装置的制造工序的剖面图。首先,经过与实施例1的工序相同的工序,获得与图11所示的结构相同的结构(图28)。

其次,将光致抗蚀剂12作为掩模,通过进行例如使用C4F8气体的氧化膜刻蚀,只刻蚀层间绝缘膜11、8,在绝缘膜7露出的时刻停止刻蚀(图29)。在这种氧化膜刻蚀方法中,由于对由Si3N4或SiON构成的绝缘膜7的刻蚀速度比由硅氧化膜构成的层间绝缘膜8、11慢,所以在绝缘膜7露出的时刻能容易地停止刻蚀,这在实施例1中已说明过。

其次,将光致抗蚀剂12作为掩模,利用例如使用CF4气体的刻蚀方法,只将绝缘膜7除去(图30)。再将光致抗蚀剂12作为掩模,通过进行各向异性的氧化膜刻蚀,将衬底保护氧化膜6g除去,使源/漏区261露出来。然后将光致抗蚀剂12除去(图31)。

以下,经过与实施例1的工序相同的工序,直到形成布线层17。即,形成电容器下部电极13,以便通过接触孔51与源/漏区261连接,然后形成电容器介质膜14、电容器上部电极15(图32)。此后在全部表面上形成层间绝缘膜16之后(图33),有选择地在它上面形成布线层17(图34)。

如果采用本实施例3的半导体装置的制造方法,则在形成接触孔51时,刻蚀速度慢的绝缘膜7起阻挡层的作用,与实施例1中的接触孔50一样,接触孔51能不与栅极4接触而以自行调整的方式形成。

另外,在实施例1中形成接触孔51时,由于通过使用同一种刻蚀剂的单一的工序,刻蚀层间绝缘膜11、8、衬底保护氧化膜6g,所以膜的应除去的厚度较厚,不容易控制刻蚀量。可是,如果采用本实施形态3的制造方法,由于在首先只刻蚀层间绝缘膜11、8之后,只刻蚀绝缘膜7,所以不影响源/漏区261,再者,此后在只刻蚀衬底保护氧化膜6g的工序中,膜的应除去的厚度也薄,容易控制刻蚀量。因此,能减少形成接触孔51时由于刻蚀而对半导体衬底1造成的过量刻蚀,比实施例1所示的方法更能抑制源/漏区261的结晶缺陷25的产生。

实施例4

在实施例1中,在形成了层间绝缘膜8之后的工序中只将源/漏区262露出,但也可同时将源/漏区261露出。

图35~图44是依次表示本发明的实施例4的半导体装置的制造工序的剖面图。首先,经过与实施例1的工序相同的工序,获得与图5相同的结构。此后,利用通常的复制方法,在层间绝缘膜8上且在源/漏区262的上方形成呈开口的光致抗蚀剂10a,将该光致抗蚀剂10a作为掩模,利用例如使用C4F8气体的氧化膜刻蚀方法,只刻蚀层间绝缘膜8,形成接触孔50、52(图35)。

其次,将光致抗蚀剂10a作为掩模,利用例如使用CF4气体的刻蚀方法,将绝缘膜7除去(图36)。再将光致抗蚀剂10a作为掩模,通过进行各向异性的氧化膜刻蚀,将衬底保护氧化膜6g、6h除去,使源/漏区261、262露出来。然后将光致抗蚀剂10a除去(图37)。

其次,形成作为位线的导电膜9,以便通过接触孔50与源/漏区262连接,与此同时,形成与导电膜9呈同样结构的导电膜19,以便通过接触孔52与源/漏区261连接(图38)。该导电膜19具有作为连接电容器下部电极13和源/漏区261用的连接电极的作用。

其次,利用CVD法在全部表面上淀积例如硅氧化膜,形成层间绝缘膜11(图39)。其次,利用通常的复制方法,在层间绝缘膜11上且在源/漏区261的上方形成呈开口的光致抗蚀剂12(图40)。

此后,将该光致抗蚀剂12作为掩模,通过刻蚀层间绝缘膜11,形成接触孔53,使导电膜19露出。此后除去光致抗蚀剂12(图41)。

以下,经过与实施例1的工序相同的工序,直到形成布线层17。即,形成电容器下部电极13,以便通过接触孔53与导电膜19连接,然后在全部表面上形成电容器介质膜14、电容器上部电极15(图42)。其次,在全部表面上形成层间绝缘膜16之后(图43),有选择地在它上面形成布线层17(图44)。

这样,如果采用本实施例4的半导体装置的制造方法,则在形成接触孔50、52时,由于刻蚀速度慢的绝缘膜7在刻蚀层间绝缘膜8时起阻挡层的作用,所以接触孔50、52能不与栅极4接触而自行调整地形成。

另外,在实施例3中,在形成接触孔51的工序中使绝缘膜7露出时,由于通过使用同一种刻蚀剂的单一的工序刻蚀层间绝缘膜11、8,所以膜的应除去的厚度较厚,不容易进行刻蚀的控制。因此,如果刻蚀层间绝缘膜11、8时的过刻蚀量过大,就会破坏本来应起刻蚀的阻挡层作用的绝缘膜7,另外,其下面的衬底保护氧化膜6g是硅氧化膜,容易被刻蚀,可以认为该刻蚀还会使源/漏区261的表面过度刻蚀。

可是,如果采用本实施例4的半导体装置的制造方法,则由于使绝缘膜7露出时,不是用单一的工序刻蚀层间绝缘膜11、8,在形成层间绝缘膜11之前的工序中,暂时只刻蚀层间绝缘膜8,使绝缘膜7露出,在此后的另一工序中,只刻蚀层间绝缘膜11,所以在各工序中膜的应除去的厚度薄,能容易地控制刻蚀量。因此,更能容易地避免源/漏区261的过刻蚀。

实施例5

在实施例1中,在侧壁6a~6f及衬底保护氧化膜6g~6i上形成了绝缘膜7及层间绝缘膜8,但也可以形成比硅氧化膜6的刻蚀速度还快的绝缘膜以代替绝缘膜7及层间绝缘膜8。

图45~图57是依次表示本发明的实施例5的半导体装置的制造工序的剖面图。首先,经过与实施例1的工序相同的工序,获得与图3相同的结构。即,利用LOCOS法在半导体衬底1形成元件分离绝缘膜2之后,在不形成元件分离绝缘膜2的半导体衬底1上有选择地形成按照栅氧化膜3、栅极4及绝缘膜5的顺序重叠的结构(图45)。

其次,利用CVD法在全部表面上形成硅氧化膜6(图46),此后通过沿垂直于半导体衬底1的方向进行刻蚀速率高的各向异性的氧化膜刻蚀,来刻蚀硅氧化膜6,形成侧壁6a~6f,同时形成衬底保护氧化膜6g~6i。此后,分别形成源/漏区261~263(图47)。

其次,在全部表面上形成比硅氧化膜6的刻蚀速度还快的层间绝缘膜(例如含有硼或磷等杂质的硅氧化膜)81(图48)。

其次,利用通常的复制方法,在层间绝缘膜81上且在源/漏区262的上方形成呈开口的光致抗蚀剂10。此后,将该光致抗蚀剂10作为掩模,通过进行刻蚀工艺,只刻蚀层间绝缘膜81。作为这时的刻蚀,是将例如CHF3或CF4、或它们的混合气体作为低密度的等离子体(1010/cm2左右)使用。这时,利用刻蚀速度的差别,硅氧化膜6(特别是侧壁6d、6e及衬底保护氧化膜6h)具有刻蚀阻挡层的作用,所以形成使侧壁6d、6e及衬底保护氧化膜6h露出用的接触孔50(图49)。

其次,将光致抗蚀剂10作为掩模,通过进行各向异性的氧化膜刻蚀,将衬底保护氧化膜6h除去,使源/漏区262露出来。这时虽然侧壁6d、6e也被除去,但只不过除去相当于衬底保护氧化膜6h的厚度。然后将光致抗蚀剂10除去(图50)。

其次,形成导电膜9,以便通过接触孔50与源/漏区262连接(图51),此后在全部表面上形成层间绝缘膜11(图52)。

其次,利用通常的复制方法,在层间绝缘膜11上且在源/漏区261的上方形成呈开口的光致抗蚀剂12(图53)。此后,将该光致抗蚀剂12作为掩膜,通过用同一种刻蚀剂刻蚀层间绝缘膜11、81、衬底保护氧化膜6g,形成接触孔51,使源/漏区261露出来(图54)。

以下,经过与实施例1的工序相同的工序,直到形成到布线层17。即,形成电容器下部电极13,以便通过接触孔51与源/漏区261连接,然后在全部表面上形成电容器介质膜14、电容器上部电极15(图55)。此后在全部表面上形成层间绝缘膜16之后(图56),有选择地在它上面形成布线层17(图57)。

这样,如果采用本实施例5的半导体装置的制造方法,则由于在形成接触孔50时只刻蚀层间绝缘膜81,暂时使侧壁6d、6e及衬底保护氧化膜6h露出,所以由于与实施例1相同的原因,接触孔50能不与栅极4接触而自行调整地形成,而且还能抑制结晶缺陷25的产生。另外,由于不需要如实施例1所示的方法那样对刻蚀速度慢的绝缘膜7进行刻蚀,所以在形成接触孔50、51时容易控制刻蚀量。

实施例6

在实施例5中,在形成层间绝缘膜11之后,将用通常的复制方法形成的光致抗蚀剂12作为掩模,通过使用同一种刻蚀剂的单一的工序刻蚀层间绝缘膜11、81、衬底保护氧化膜6g,形成了接触孔51,但也可以通过多个工序形成接触孔51。

图58~图64是依次表示本发明的实施例6的半导体装置的制造工序的剖面图。首先,经过与实施例5的工序相同的工序,获得与图53所示的结构相同的结构(图58)。

其次,将光致抗蚀剂12作为掩模,通过进行各向异性的氧化膜刻蚀,来刻蚀层间绝缘膜11。这时由于层间绝缘膜81的刻蚀速度比层间绝缘膜11快,所以刻蚀层间绝缘膜11时,由于过刻蚀而使层间绝缘膜81的上部也被刻蚀了一些(图59)。

其次,将光致抗蚀剂12作为掩模,只刻蚀层间绝缘膜81(图60)。这时由于硅氧化膜6的刻蚀速度比层间绝缘膜81慢,所以对侧壁6b、6c及衬底保护氧化膜6g进行的过刻蚀量小。

其次,将光致抗蚀剂12作为掩模,通过进行各向异性的氧化膜刻蚀,将衬底保护氧化膜6g除去,使源/漏区261露出来。然后将光致抗蚀剂12除去(图61)。

以下,经过与实施例1的工序相同的工序,直到形成布线层17。即,形成电容器下部电极13,以便通过接触孔51与源/漏区261连接,然后在全部表面上形成电容器介质膜14、电容器上部电极15(图62)。此后在全部表面上形成了层间绝缘膜16后(图63),有选择地在它上面形成布线层17(图64)。

这样,如果采用本实施例6的半导体装置的制造方法,则由于在形成接触孔51时,暂时只刻蚀层间绝缘膜81,使侧壁6b、6c及衬底保护氧化膜6g露出,所以由于与实施例5相同的原因,接触孔51能不与栅极4接触而自行调整地形成,而且还能抑制结晶缺陷25的产生。

另外,在实施例5中,在形成接触孔51时,由于通过使用同一种刻蚀剂的单一的工序刻蚀层间绝缘膜11、81、衬底保护氧化膜6g,所以膜的应除去的厚度厚,不容易进行刻蚀的控制。可是,如果采用本实施形态6的制造方法,由于在首先只刻蚀层间绝缘膜11之后,只刻蚀层间绝缘膜81,然后再只刻蚀衬底保护氧化膜6g,所以在这些工序中膜的应除去的厚度薄,特别是衬底保护氧化膜6g的刻蚀量变得容易控制。因此,在形成接触孔51时能减少因刻蚀而造成的半导体衬底1的过刻蚀量,比实施例5所示的方法更能抑制源/漏区261的结晶缺陷25的产生。

实施例7

在实施例5中,在形成了层间绝缘膜81之后的工序中,暂时只将源/漏区262露出,但也可同时将源/漏区261露出。

图65~73是依次表示本发明的实施例4的半导体装置的制造工序的剖面图。首先,经过与实施例5的工序相同的工序,获得与图48相同的结构。此后,利用通常的复制方法,在层间绝缘膜81上且在源/漏区261、262的上方形成呈开口的光致抗蚀剂10a,将该光致抗蚀剂10a作为掩模,通过使用与实施例5同样的刻蚀剂的刻蚀方法,只刻蚀层间绝缘膜81,分别形成接触孔52、50(图65)。这时,由于硅氧化膜6的刻蚀速度比层间绝缘膜81慢,所以对侧壁6b、6c、6d、6e及衬底保护氧化膜6g、6h的过刻蚀量小。

其次,将光致抗蚀剂10a作为掩模,通过进行各向异性的氧化膜刻蚀,将衬底保护氧化膜6g、6h除去,使源/漏区261、262露出来。然后将光致抗蚀剂10a除去(图66)。

其次,形成作为位线的导电膜9,以便通过接触孔50与源/漏区262连接,与此同时,形成与导电膜9呈同样结构的导电膜19,以便通过接触孔52与源/漏区261连接(图67)。已经说明过,该导电膜19具有作为连接电容器下部电极13和源/漏区261用的连接电极的作用。

其次,利用CVD法在全部表面上淀积例如硅氧化膜,形成层间绝缘膜11(图68),利用通常的复制方法,在层间绝缘膜11上且在源/漏区261的上方形成呈开口的光致抗蚀剂12(图69)。

此后,将该光致抗蚀剂12作为掩模,通过刻蚀层间绝缘膜11,形成接触孔53,使导电膜19露出。此后除去光致抗蚀剂12(图70)。

以下,经过与实施例1的工序相同的工序,直到形成布线层17。即,形成电容器下部电极13,以便通过接触孔53与导电膜19连接,然后在全部表面上形成电容器介质膜14、电容器上部电极15(图71)。其次,在全部表面上形成层间绝缘膜16之后(图72),有选择地在它上面形成布线层17(图73)。

这样,如果采用本实施例7的半导体装置的制造方法,则由于在形成接触孔50、52时通过氧化膜刻蚀只刻蚀层间绝缘膜81,暂时使侧壁6b、6c、6d、6e及衬底保护氧化膜6g、6h露出,所以由于与实施形态5相同的原因,接触孔50、52能不与栅极4接触而自行调整地形成,而且还能抑制结晶缺陷25的产生。

另外,在实施例6中,在形成接触孔51的工序中,由于刻蚀层间绝缘膜11时的过刻蚀,层间绝缘膜81的上部也被刻蚀了一些。因此,在下一工序中刻蚀层间绝缘膜81时必须考虑其上部由于过刻蚀而被刻蚀的量,而且由于层间绝缘膜11和层间绝缘膜81的刻蚀速度互不相同,所以有必要更精确地控制应刻蚀层间绝缘膜81的量。

可是,如果采用本实施例7的半导体装置的制造方法,则在刻蚀层间绝缘膜11后不刻蚀层间绝缘膜81,在形成层间绝缘膜11之前的工序中刻蚀一次层间绝缘膜81,使衬底保护氧化膜6g露出,此后在另一工序中,因只刻蚀层间绝缘膜11,所以在刻蚀层间绝缘膜81时其上部未被刻蚀,故能容易地控制刻蚀量。

实施例8

在实施例1中,在形成了接触孔51之后的工序中已经形成了电容器下部电极13,但在形成接触孔51之后而形成电容器下部电极13之前,还可以增加在半导体衬底1内形成杂质扩散层的工序。

图74~图77是依次表示本发明的实施例8的半导体装置的制造工序的剖面图。首先,经过与实施例1的工序相同的工序,获得与图11所示的结构相同的结构。此后,将光致抗蚀剂12作为掩模,利用离子注入法,通过接触孔51将呈与半导体衬底1相反的导电类型的杂质(如果半导体衬底1的导电类型为p型,则为磷、砷等,如果为n型,则为硼等)注入半导体衬底1内,形成比源/漏区261宽且浓度小的杂质扩散层18(图74)。

以下,经过与实施例1的工序相同的工序,直到形成布线层17。即,形成电容器下部电极13,以便通过接触孔51与源/漏区261连接,然后在全部表面上分别形成电容器介质膜14、电容器上部电极15(图75)。此后在全部表面上形成层间绝缘膜16后(图76),有选择地在它上面形成布线层17(图77)。

这样,如果采用本实施例8的半导体装置的制造方法,则由于在源/漏区261的外侧增加形成呈与半导体衬底1相反的导电类型的杂质扩散层18,所以能降低电容器下部电极13与半导体衬底1的接触电阻。另外,由于源/漏区261和半导体衬底1之间的杂质浓度梯度变缓,而缓和了电容器下部电极13下面的半导体衬底1内的电场强度,所以能降低从电容器下部电极13流向半导体衬底1的漏泄电流。

另外,以上以实施例1为基础,说明了实施例8的效果,但即使以实施例5的制造方法为基础,也能获得与其同样的效果,这是当然的。

实施例9

在实施例1中,在中间工序之前刻蚀硅氧化膜6以形成衬底保护氧化膜6g~6i之后的工序中,已经形成了绝缘膜7,但在形成绝缘膜7之前也可以增加在半导体衬底1内形成杂质扩散层的工序。

图78~图90是依次表示本发明的实施例9的半导体装置的制造工序的剖面图。首先,经过与实施例1的工序相同的工序,获得与图3所示的结构相同的结构。此后,利用离子注入法,通过衬底保护氧化膜6g~6i将呈与半导体衬底1相反的导电类型的杂质注入半导体衬底1内,形成比源/漏区261、262宽且浓度小的杂质扩散层20(图78)。

以下,经过与实施例1的工序相同的工序,直到形成布线层17。即,在全部表面上形成了绝缘膜7之后(图79),在绝缘膜7上形成层间绝缘膜8(图80),将在它上面形成的光致抗蚀剂10作为掩模,利用例如使用C4F8气体的氧化膜刻蚀方法,刻蚀层间绝缘膜8,形成接触孔50(图81)。再将光致抗蚀剂10作为掩模,刻蚀绝缘膜7(图82),然后将衬底保护氧化膜6h除去(图83)。其次,形成导电膜9,以便通过接触孔50与源/漏区262连接(图84),在全部表面上形成层间绝缘膜11(图85)。其次,在层间绝缘膜11上形成光致抗蚀剂1 2(图86),将其作为掩模,刻蚀层间绝缘膜11、8、绝缘膜7、衬底保护氧化膜7g,形成接触孔51,使源/漏区261露出(图87)。此后形成电容器下部电极13,以便通过接触孔51与源/漏区261连接,在全部表面上分别形成电容器介质膜14、电容器上部电极15(图88)。再在全部表面上形成层间绝缘膜16(图89),有选择地在它上面形成布线层17(图90)。

这样,如果采用本实施例9的半导体装置的制造方法,则由于在源/漏区261、262的外侧增加形成呈与半导体衬底1相反的导电类型的杂质扩散层20,所以能降低电容器下部电极13及导电膜9与半导体衬底1的接触电阻。另外,与实施例8中的效果一样,能降低从电容器下部电极13流向半导体衬底1的漏泄电流。再者,由于在进行形成杂质扩散层20用的离子注入时,不使半导体衬底1露出,所以不会损伤半导体衬底1。

另外,以上以实施例1为基础,说明了实施例9的效果,但即使以实施例5的制造方法为基础,也能获得与其同样的效果,这是当然的。

实施例10

图91~图108是依次表示本发明的实施例10的半导体装置的制造工序的剖面图。首先,利用LOCOS法在半导体(例如Si)衬底1上形成元件分离绝缘膜2之后,在不形成元件分离绝缘膜2的半导体衬底1上有选择地按照栅氧化膜3、栅极4及绝缘膜5的顺序形成叠层结构(图91)。另外,如图中所示,被分成外围电路区和存储单元区。这里,在图91中,在元件分离绝缘膜2上设的栅极4的下方不设栅氧化膜3,但在垂直于纸面的方向上,隐藏在元件分离绝缘膜2的后方形成上述的叠层结构。

其次,利用CVD法在全部表面上淀积硅氧化膜6(图92)。其次,通过沿垂直于半导体衬底1的方向进行刻蚀速率高的各向异性的氧化膜刻蚀,来刻蚀硅氧化膜6,在栅氧化膜3、栅极4、绝缘膜5各自的侧壁部分留下硅氧化膜6,形成侧壁6j~6q。但进行该刻蚀时,不使半导体衬底1露出,在半导体衬底1上留有规定厚度的硅氧化膜6,形成衬底保护氧化膜6r~6v。这里,通过各向异性的氧化膜刻蚀,将衬底保护氧化膜6r~6v的厚度设定在不使半导体衬底1受损伤的范围内。例如在本实施例中为5~20nm。此后,将离子通过衬底保护氧化膜6r~6v注入半导体衬底1内,分别形成源/漏区264~268(图93)。

其次。用CVD法在全部表面上淀积厚度为5~100nm的由Si3N4或SiON等构成的绝缘膜7(图94)。

其次,利用通常的复制方法,在存在于存储单元区的绝缘膜7上形成光致抗蚀剂21后,将不被该光致抗蚀剂21覆盖的区域的绝缘膜7及衬底保护氧化膜6r、6s除去。此后,利用离子注入法,分别注入呈与半导体衬底1相反的导电类型的杂质(如果半导体衬底1的导电类型为p型,则为磷、砷等,如果为n型,则为硼等),形成比源/漏区264、265大的杂质扩散层22(图96)。

其次,利用CVD法在全部表面上淀积例如硅氧化膜,形成层间绝缘膜8(图97)。再利用通常的复制方法,在层间绝缘膜8上且在源/漏区265、267的上方形成呈开口的光致抗蚀剂10b,将该光致抗蚀剂10b作为掩模,利用对绝缘膜7刻蚀速度快的氧化膜刻蚀方法,刻蚀绝缘膜8,形成接触孔53、50(图98)。这时,利用刻蚀速度的差别,在绝缘膜7露出的阶段就能停止接触孔50的刻蚀。

其次,利用例如使用CF4气体的刻蚀方法,只将绝缘膜7除去(图99)。

再者,将光致抗蚀剂10b作为掩模,通过进行各向异性的氧化膜刻蚀,将衬底保护氧化膜6u除去,挖进接触孔50,直至使源/漏区267露出来为止。然后将光致抗蚀剂10b除去(图100)。

其次,形成作为位线的导电膜9,以便通过接触孔50与源/漏区267连接,与此同时,形成与导电膜9呈同样结构的布线层23,以便通过接触孔53与源/漏区265连接(图101)。

其次,例如利用CVD法在全部表面上淀积硅氧化膜,形成层间绝缘膜11(图102)。其次,利用通常的复制方法,在层间绝缘膜11上且在源/漏区266的上方形成呈开口的光致抗蚀剂12a。此后,将该光致抗蚀剂12a作为掩模,通过使用同一种刻蚀剂刻蚀层间绝缘膜11、8、绝缘膜7、衬底保护氧化膜6t,形成接触孔51,使源/漏区266露出(图103)。此后除去光致抗蚀剂12a(图104)。

其次,为了填充接触孔51,利用CVD法淀积多晶硅,形成电容器下部电极13。此后,只在存储单元区淀积Si3N4膜,形成电容器介质膜14。利用CVD法再在电容器介质膜14上淀积多晶硅,形成电容器上部电极15(图105)。

其次,利用CVD法在全部表面上淀积例如硅氧化膜,形成层间绝缘膜16(图106)。再利用通常的复制方法,在该层间绝缘膜16上且在源/漏区264的上方形成呈开口的光致抗蚀剂24。此后,将该光致抗蚀剂24作为掩模,通过刻蚀层间绝缘膜16、11、8,形成接触孔54,使源/漏区264露出(图107)。然后除去光致抗蚀剂24。

其次,在层间绝缘膜16上有选择地形成布线层17。形成其中的一个布线层,以便通过接触孔54与源/漏区264连接(图108)。

这样,如果采用本实施例10的半导体装置的制造方法,则在形成接触孔50时,暂时将绝缘膜7作为阻挡层,只刻蚀层间绝缘膜8。因此,在该阶段不刻蚀衬底保护氧化膜6u,所以层间绝缘膜8的刻蚀不会损伤源/漏区267。而且,由于衬底保护氧化膜6u薄,所以刻蚀它时容易控制刻蚀量,仍然不会损伤源/漏区267。再者绝缘膜5和侧壁6o、6p分别除去的量从总体来看很少,所以接触孔50能不与栅极4接触而自行调整地形成。

另外,由于在形成接触孔53、54时,不需要对刻蚀速度慢的绝缘膜7进行刻蚀,所以形成接触孔53、54时的刻蚀量容易控制。

再者,由于增加形成比源/漏区264、265大的呈与半导体衬底1相反的导电类型的杂质扩散层22,所以能降低布线层17、23各自与半导体衬底1的接触电阻。

实施例11

在实施例10中,在刻蚀外围电路区的绝缘膜7及衬底保护氧化膜6r、6s之后,形成了杂质扩散层22,但也可以只刻蚀绝缘膜7,通过衬底保护氧化膜6r、6s注入杂质,形成杂质扩散层22。

图109~图110是依次表示本发明的实施例11的半导体装置的制造工序的剖面图。首先,经过与实施例10的工序相同的工序,获得与图9所示的结构相同的结构。其次,利用通常的复制方法,在存储单元区的绝缘膜7上形成光致抗蚀剂21之后,将该光致抗蚀剂21作为掩模,利用例如使用CF4气体的刻蚀方法,只刻蚀绝缘膜7。此后,利用离子注入法,通过衬底保护氧化膜6r、6s分别注入呈与半导体衬底1相反的导电类型的杂质,形成比源/漏区264、265宽的杂质扩散层22(图109)。

以下,经过与实施例10的工序相同的工序,直到形成布线层17(图110)。

这里,如果着眼于源/漏区264、265的状态,若采用实施例10的制造方法,则在形成杂质扩散层22时及形成接触孔53、54时的2个工序中,半导体衬底1被过量刻蚀,结晶缺陷也多,与此不同,如果采用本实施例11的半导体装置的制造方法,则在形成杂质扩散层22时,由于有留下来的衬底保护氧化膜6r、6s,所以不会由于这时的刻蚀造成半导体衬底1的过量刻蚀,也不会产生结晶缺陷25。因此,与实施例10的制造方法相比,能抑制源/漏区264、265附近的结晶缺陷25,所以通过接触孔53、54将布线层23、17与源/漏区264、265相连接时,还能抑制诱发引起器件误操作的漏泄电流。

如果采用本发明的第1方面,则由于第2绝缘膜的刻蚀不在第4绝缘膜上连续地进行,第3绝缘膜在刻蚀第4绝缘膜时起阻挡层的作用,此后另外进行第2绝缘膜的刻蚀,因此能精确地控制第2绝缘膜的刻蚀量,能抑制对露出的半导体衬底的过刻蚀,进而能抑制半导体衬底内的结晶缺陷的产生。

因此,在工序(g)中形成第2导电膜时,能避免在第2导电膜和半导体衬底接触处发生不需要的漏泄电流。

另外,如果采用本发明的第2方面,则由于存在于第1区的第2绝缘膜的宽度比存在于第2区的第2绝缘膜的厚度要厚,另外第1绝缘膜存在于第1导电膜上,所以在工序(f)中有选择地使半导体衬底露出时,即使第1位置的设定精度不高,也能不使第1导电膜露出,而只使半导体衬底的表面自行调整地露出。因此,在工序(g)中形成第2导电膜时,能避免第2导电膜与第1导电膜短路。

另外,如果采用本发明的第3方面,则由于在工序(y)中使存在于第2位置的半导体衬底的表面露出时,不需要在第2位置的上方对刻蚀速度慢的第3绝缘膜进行刻蚀,所以能容易地使半导体衬底的表面露出。

另外,如果采用本发明的第4方面,则由于第2绝缘膜的刻蚀不在第4绝缘膜上连续地进行,第3绝缘膜在刻蚀第4绝缘膜时起阻挡层的作用,因此能精确地控制第2绝缘膜的刻蚀量,能抑制对露出的半导体衬底表面的过刻蚀,进而能抑制半导体衬底内的结晶缺陷的产生。因此,在工序(z)中形成第3导电膜时,能避免在第3导电膜和半导体衬底接触处发生不需要的漏泄电流。

另外,如果采用本发明的第5方面,则中间介入第5绝缘膜与第2导电膜处于不同层的第4导电膜,通过第3导电膜与存在于第2位置的半导体衬底进行导电连接。即,将开口应设在第5绝缘膜上而对其进行刻蚀的工序(i)和应使存在于第2位置的半导体衬底的表面露出而刻蚀第4绝缘膜的工序(f)不连续进行。因此,与连续地刻蚀第4及第5绝缘膜的情况相比较,在各工序中应刻蚀的膜厚度较薄,因此容易控制刻蚀量,能避免第3绝缘膜过刻蚀。

另外,如果采用本发明的第6方面,则由于存在于第1区的第2绝缘膜的宽度大于存在于第2区的第2绝缘膜的厚度,另外第1绝缘膜存在于第1导电膜上,所以在工序(e)中有选择地使半导体衬底的表面露出时,即使第1位置的设定精度不高,也能不使第1导电膜露出,而只使半导体衬底的表面自行调整地露出。

再者,由于第2绝缘膜的刻蚀不在第3绝缘膜处连续地进行,第2绝缘膜在刻蚀第3绝缘膜时起阻挡层的作用,此后另外进行第2绝缘膜的刻蚀,因此能精确地控制第2绝缘膜的刻蚀量,能抑制对已露出的半导体衬底的过刻蚀,进而能抑制半导体衬底内的结晶缺陷的产生。

因此,在工序(g)中形成第2导电膜时,能避免第2导电膜和第1导电膜短路,同时能避免在第2导电膜和半导体衬底接触处发生不需要的漏泄电流。

另外,如果采用本发明的第7方面,则由于第2绝缘膜的刻蚀不在第3绝缘膜处连续地进行,第2绝缘膜在刻蚀第3绝缘膜时起阻挡层的作用,因此能精确地控制第2绝缘膜的刻蚀量,能抑制对已露出的半导体衬底的过刻蚀,进而能抑制半导体衬底内的结晶缺陷的产生。因此,在工序(z)中形成第3导电膜时,能避免在第3导电膜和半导体衬底接触处发生不需要的漏泄电流。

另外,如果采用本发明的第8方面,则中间介入第4绝缘膜与第2导电膜处于不同层的第4导电膜,通过第3导电膜与存在于第2位置的半导体衬底进行导电连接。因此将开口应设在第4绝缘膜上而对其进行刻蚀的工序(h)和应使存在于第2位置的半导体衬底的表面露出而刻蚀第2及第3绝缘膜的工序(f)不连续进行。因此,与连续地刻蚀第3绝缘膜的情况相比较,在各工序中应刻蚀的膜厚度较薄,因此容易控制刻蚀量。

而且,在工序(h)中,第3导电膜起刻蚀的阻挡层的作用,能避免刻蚀速度比第4绝缘膜快的第3绝缘膜的过刻蚀。因此,不需要考虑过刻蚀量而控制第3绝缘膜的刻蚀量。

另外,如果采用本发明的第9方面,则由于形成比第1掺杂区宽的第2掺杂区,所以能降低在工序(z)中形成的第3导电膜与半导体衬底的接触电阻。另外,由于第3导电膜和半导体衬底之间的杂质浓度梯度变得缓和,所以能缓和在形成第3导电膜的半导体衬底内的电场强度。因此,更能抑制从第3导电膜流向半导体衬底的不需要的漏泄电流的发生。

另外,如果采用本发明的第10方面,则由于形成比第1掺杂区宽的第2掺杂区,所以能降低在工序(z)中形成的第3导电膜和半导体衬底的接触电阻。另外,由于第3导电膜和半导体衬底之间的杂质浓度梯度变得缓和,所以能缓和在形成第3导电膜的半导体衬底内的电场强度。因此,更能抑制从第3导电膜流向半导体衬底的不需要的漏泄电流的发生。

再者,由于在形成第1及第2掺杂区时都不使半导体衬底露出,所以能不使半导体衬底受损伤地形成第1及第2掺杂区。

另外,如果采用本发明的第11方面,则由于在工序(k)中使存在于第3位置的半导体衬底的表面露出时,不需要在第3位置的上方对刻蚀速度慢的第3绝缘膜进行刻蚀,所以能容易地使半导体衬底的表面露出。

再者,由于形成比第1掺杂区宽的第2掺杂区,所以能降低在工序(k)中形成的第4导电膜与半导体衬底的接触电阻。另外,由于第4导电膜和半导体衬底之间的杂质浓度梯度变得缓和,所以能缓和在形成第4导电膜的半导体衬底内的电场强度。因此,更能抑制从第4导电膜流向半导体衬底的不需要的漏泄电流的发生。

Claims (11)

1.一种半导体装置的制造方法,其特征在于,包括以下工序:

(a)在半导体衬底的表面上有选择地形成第1导电膜的工序;

(b)在所述第1导电膜上形成第1绝缘膜的工序;

(c)在由所述工序(a)及(b)获得的结构上形成第2绝缘膜的工序;

(d)在所述第2绝缘膜上形成第3绝缘膜的工序;

(e)在所述第3绝缘膜上形成第4绝缘膜的工序;

(f)对所述第4绝缘膜、所述第3绝缘膜、所述第2绝缘膜有选择地、而且按照该顺序进行个别地刻蚀,使存在于所述半导体衬底的所述表面内未形成所述第1导电膜的第1位置的部分露出的工序;

(g)在所述第1位置形成与所述半导体衬底导电性接触的第2导电膜的工序,

其中,所述第3绝缘膜比所述第4绝缘膜的刻蚀速度慢;通过将所述第2绝缘膜蚀刻,在所述第1导电膜和所述第1绝缘膜的各侧面上形成侧壁;所述侧壁由所述第2绝缘膜的没有被蚀刻的部分形成;所述侧壁与所述第1导电膜和所述第1绝缘膜接触。

2.根据权利要求1所述的半导体装置的制造方法,其特征在于,所述第2绝缘膜存在于作为所述第1导电膜及所述第1绝缘膜各自的侧壁的第1区和所述半导体衬底的所述表面内未形成所述第1导电膜的第2区,存在于所述第1区的所述第2绝缘膜的宽度大于存在于所述第2区的所述第2绝缘膜的厚度。

3.根据权利要求2所述的半导体装置的制造方法,其特征在于,还包括以下工序:

(x)在工序(d)和工序(e)之间执行的、将存在于所述半导体衬底的所述表面内与所述第1位置不同的未形成所述第1导电膜的第2位置的上方的所述第3绝缘膜除去的工序;

(y)在由所述工序(e)以后的工序中执行的、对存在于所述第2位置的上方的所述第4绝缘膜及所述第2绝缘膜按照该顺序连续地进行刻蚀,使存在于所述半导体衬底的所述表面内所述第2位置的部分露出的工序;

(z)在所述第2位置形成与所述半导体衬底导电性地接触的第3导电膜的工序。

4.根据权利要求2所述的半导体装置的制造方法,其特征在于,还包括以下工序:

(y)在由所述工序(g)以后的工序中执行的、对所述第4绝缘膜、所述第3绝缘膜、所述第2绝缘膜有选择地、而且按照该顺序进行个别地刻蚀,使存在于所述半导体衬底的所述表面内与所述第1位置不同的未形成所述第1导电膜的第2位置的部分露出的工序;

(z)在所述第2位置形成与所述半导体衬底导电性地接触的第3导电膜的工序。

5.根据权利要求2所述的半导体装置的制造方法,其特征在于,在所述工序(f)中使存在于所述半导体衬底的所述表面内与所述第1位置不同的未形成所述第1导电膜的第2位置的部分露出,

在所述工序(g)中在所述第2位置还形成与所述半导体衬底导电性地接触的第3导电膜,

继工序(g)之后还包括以下工序:

(h)形成覆盖所述第2及第3导电膜及所述第4绝缘膜的第5绝缘膜的工序;

(i)对所述第5绝缘膜有选择地进行刻蚀,在所述第3导电膜的上方设置开口的工序;

(j)通过所述第5绝缘膜的所述开口设置与所述第3导电膜导电性地接触的第4导电膜的工序。

6.一种半导体装置的制造方法,其特征在于,包括以下工序:

(a)在半导体衬底的表面上有选择地形成第1导电膜的工序;

(b)在所述第1导电膜上形成第1绝缘膜的工序;

(c)在由所述工序(a)及(b)获得的结构上形成第2绝缘膜的工序;

(d)在所述第2绝缘膜上形成第3绝缘膜的工序;

(e)对所述第3绝缘膜及所述第2绝缘膜有选择地、而且按照该顺序进行个别地刻蚀,使存在于所述半导体衬底的所述表面内未形成所述第1导电膜的第1位置的部分露出的工序;

(f)在所述第1位置形成与所述半导体衬底导电性接触的第2导电膜的工序,

其中所述第2绝缘膜比所述第3绝缘膜的刻蚀速度慢,

另外所述第2绝缘膜存在于所述第1导电膜及所述第1绝缘膜各自的侧壁的第1区和所述半导体衬底的所述表面内未形成所述第1导电膜的第2区,存在于所述第1区的所述第2绝缘膜的宽度大于存在于所述第2区的所述第2绝缘膜的厚度。

7.根据权利要求6所述的半导体装置的制造方法,其特征在于,还包括以下工序:

(y)在由所述工序(d)以后的工序中执行的、对所述第3绝缘膜、所述第2绝缘膜有选择地、而且按照该顺序进行个别地刻蚀,使存在于所述半导体衬底的所述表面内与所述第1位置不同的未形成所述第1导电膜的第2位置的部分露出的工序;

(z)在所述第2位置形成与所述半导体衬底导电性地接触的第3导电膜的工序。

8.根据权利要求6所述的半导体装置的制造方法,其特征在于,在所述工序(e)中使存在于所述半导体衬底的所述表面内与所述第1位置不同的未形成所述第1导电膜的第2位置的部分露出,

在所述工序(f)中在所述第2位置还形成与所述半导体衬底导电性地接触的第3导电膜,

继所述工序(f)之后还包括以下工序:

(g)形成覆盖所述第2及第3导电膜及所述第3绝缘膜的第4绝缘膜的工序;

(h)对所述第4绝缘膜有选择地进行刻蚀,在所述第3导电膜的上方设开口的工序;

(i)通过所述第4绝缘膜的所述开口设置与所述第3导电膜导电性地接触的第4导电膜的工序,

其中所述第4绝缘膜比所述第3绝缘膜的刻蚀速度慢。

9.根据权利要求3、4、5、7、8任意一项所述的半导体装置的制造方法,其特征在于,还包括以下工序:

(s)在所述工序(c)和所述工序(d)之间执行的、从存在于所述半导体衬底的所述表面内的所述第2位置的部分,通过所述第2绝缘膜掺入呈与所述半导体衬底相反的导电类型的第1种杂质而形成第1掺杂区的工序;

(t)在所述工序(y)和所述工序(z)之间执行的、从存在于所述半导体衬底的所述表面内的所述第2位置的部分,将呈与所述半导体衬底相反的导电类型的第2种杂质掺入而形成第2掺杂区的工序,

所述第2掺杂区比所述第1掺杂区宽,而且所述第2掺杂区的杂质浓度比所述第1掺杂区的杂质浓度低。

10.根据权利要求3、4、5、7、8任意一项所述的半导体装置的制造方法,其特征在于,还包括以下工序:

(s)在所述工序(c)和所述工序(d)之间执行的、从存在于所述半导体衬底的所述表面内的所述第1及第2位置的部分,通过所述第2绝缘膜掺入呈与所述半导体衬底相反的导电类型的第1种杂质而分别形成第1掺杂区的工序;

(t)在所述工序(s)和所述工序(d)之间执行的、从存在于所述半导体衬底的所述表面内的所述第1及第2位置的部分,掺入呈与所述半导体衬底相反的导电类型的第2种杂质而形成第2掺杂区的工序,

所述第2掺杂区比所述第1掺杂区宽,而且所述第2掺杂区的杂质浓度比所述第1掺杂区的杂质浓度低。

11.根据权利要求2所述的半导体装置的制造方法,其特征在于,还包括以下工序:

(h)在所述工序(c)和所述工序(d)之间执行的、从存在于所述半导体衬底的所述表面内与所述第1位置不同的未形成所述第1导电膜的第3位置的部分,通过所述第2绝缘膜掺入呈与所述半导体衬底相反的导电类型的第1种杂质而形成第1掺杂区的工序;

(i)在所述工序(d)和所述工序(e)之间执行的、将存在于所述第3位置的上方的所述第3绝缘膜除去的工序;

(j)在所述工序(i)和所述工序(e)之间执行的、从存在于所述半导体衬底的所述表面内的所述第3位置的部分,通过所述第2绝缘膜掺入呈与所述半导体衬底相反的导电类型的第2种杂质而形成第2掺杂区的工序;

(k)与所述工序(f)同时执行的对存在于所述第3位置的上方的所述第4绝缘膜及所述第2绝缘膜按照该顺序连续地进行刻蚀,使存在于所述半导体衬底的所述表面内所述第3位置的部分露出的工序;

(l)与所述工序(g)同时执行的、在所述第3位置形成与所述半导体衬底导电性接触的第4导电膜的工序,

所述第2掺杂区比所述第1掺杂区宽,而且所述第2掺杂区的杂质浓度比所述第1掺杂区的杂质浓度低。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP34750996A JP3592870B2 (ja) | 1996-12-26 | 1996-12-26 | 半導体装置の製造方法 |

| JP347509/96 | 1996-12-26 | ||

| JP347509/1996 | 1996-12-26 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN1186336A CN1186336A (zh) | 1998-07-01 |

| CN1155077C true CN1155077C (zh) | 2004-06-23 |

Family

ID=18390712

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CNB971177643A Expired - Fee Related CN1155077C (zh) | 1996-12-26 | 1997-08-29 | 半导体装置的制造方法 |

Country Status (6)

| Country | Link |

|---|---|

| US (1) | US6100134A (zh) |

| JP (1) | JP3592870B2 (zh) |

| KR (1) | KR100351929B1 (zh) |

| CN (1) | CN1155077C (zh) |

| DE (1) | DE19724904A1 (zh) |

| TW (1) | TW332928B (zh) |

Families Citing this family (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR100668221B1 (ko) * | 2004-12-31 | 2007-01-11 | 동부일렉트로닉스 주식회사 | Mim 캐패시터 형성 방법 |

| JP6123242B2 (ja) * | 2012-11-09 | 2017-05-10 | 大日本印刷株式会社 | パターン形成方法 |

| CN104617035A (zh) * | 2013-11-05 | 2015-05-13 | 中芯国际集成电路制造(上海)有限公司 | 半导体器件的形成方法 |

Family Cites Families (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR920004541B1 (ko) * | 1989-05-30 | 1992-06-08 | 현대전자산업 주식회사 | 반도체 소자에서 식각베리어층을 사용한 콘택홀 형성방법 |

| US5206187A (en) * | 1991-08-30 | 1993-04-27 | Micron Technology, Inc. | Method of processing semiconductor wafers using a contact etch stop |

| US5439835A (en) * | 1993-11-12 | 1995-08-08 | Micron Semiconductor, Inc. | Process for DRAM incorporating a high-energy, oblique P-type implant for both field isolation and punchthrough |

| JPH07235594A (ja) * | 1994-02-22 | 1995-09-05 | Mitsubishi Electric Corp | 半導体装置の製造方法 |

| JP2765478B2 (ja) * | 1994-03-30 | 1998-06-18 | 日本電気株式会社 | 半導体装置およびその製造方法 |

| US5501998A (en) * | 1994-04-26 | 1996-03-26 | Industrial Technology Research Institution | Method for fabricating dynamic random access memory cells having vertical sidewall stacked storage capacitors |

| JPH0846173A (ja) * | 1994-07-26 | 1996-02-16 | Mitsubishi Electric Corp | 半導体装置及びその製造方法 |

| US5482894A (en) * | 1994-08-23 | 1996-01-09 | Texas Instruments Incorporated | Method of fabricating a self-aligned contact using organic dielectric materials |

| US5489546A (en) * | 1995-05-24 | 1996-02-06 | Micron Technology, Inc. | Method of forming CMOS devices using independent thickness spacers in a split-polysilicon DRAM process |

| US5770498A (en) * | 1996-01-31 | 1998-06-23 | Micron Technology, Inc. | Process for forming a diffusion barrier using an insulating spacer layer |

-

1996

- 1996-12-26 JP JP34750996A patent/JP3592870B2/ja not_active Expired - Fee Related

-

1997

- 1997-04-23 TW TW086105273A patent/TW332928B/zh not_active IP Right Cessation

- 1997-05-05 US US08/841,783 patent/US6100134A/en not_active Expired - Lifetime

- 1997-06-12 DE DE19724904A patent/DE19724904A1/de not_active Withdrawn

- 1997-06-13 KR KR1019970024652A patent/KR100351929B1/ko not_active IP Right Cessation

- 1997-08-29 CN CNB971177643A patent/CN1155077C/zh not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| DE19724904A1 (de) | 1998-07-02 |

| JPH10189901A (ja) | 1998-07-21 |

| KR100351929B1 (ko) | 2003-04-10 |

| TW332928B (en) | 1998-06-01 |

| US6100134A (en) | 2000-08-08 |

| KR19980063335A (ko) | 1998-10-07 |

| JP3592870B2 (ja) | 2004-11-24 |

| CN1186336A (zh) | 1998-07-01 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN1135626C (zh) | 半导体器件及其制造方法 | |

| CN1284224C (zh) | 半导体器件及其制造工艺 | |

| CN1873953A (zh) | 半导体元件及其制造方法 | |

| CN1134058C (zh) | 槽型元件分离结构的制造方法 | |

| CN1187811C (zh) | 半导体装置及其制造方法 | |

| CN101069279A (zh) | 半导体器件及其制造方法 | |

| CN1249816C (zh) | 半导体装置及其制造方法 | |

| CN1449040A (zh) | 半导体集成电路器件及其制造方法 | |

| CN1303698C (zh) | 半导体器件及其制造方法 | |

| CN1728401A (zh) | 半导体器件及其制造方法 | |

| CN1445838A (zh) | 半导体器件及其制造方法 | |

| CN1913120A (zh) | 半导体装置的制造方法及半导体装置 | |

| CN1449045A (zh) | 半导体装置及其制造方法 | |

| CN1655361A (zh) | 半导体装置 | |

| CN1828902A (zh) | 半导体器件和用于制造该半导体器件的方法 | |

| CN1909249A (zh) | 具有薄膜晶体管的半导体器件及其制造方法 | |

| CN1303693C (zh) | 半导体存储器件 | |

| CN1790743A (zh) | 晶体管及其制造方法 | |

| CN1870267A (zh) | 半导体器件和半导体器件的制造方法 | |

| CN1423305A (zh) | 制造半导体器件的方法 | |

| CN1043587A (zh) | 超大规模集成电路静态随机存储器 | |

| CN1375113A (zh) | 薄膜晶体管及其制造方法 | |

| CN1421914A (zh) | 半导体装置及其制造方法 | |

| CN1303127A (zh) | 非易失性半导体存储器及其制造方法 | |

| CN1801491A (zh) | 半导体器件及其制造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C06 | Publication | ||

| PB01 | Publication | ||

| C14 | Grant of patent or utility model | ||

| GR01 | Patent grant | ||

| C17 | Cessation of patent right | ||

| CF01 | Termination of patent right due to non-payment of annual fee |

Granted publication date: 20040623 Termination date: 20090929 |