関連出願の相互参照

本出願は、全体として参照により本明細書に援用される、2014年2月10日に提出された、米国仮特許出願第61/937,736号明細書の利益を主張する。

多種多様な用途で高性能および低消費電力が可能な半導体デバイスに対する要求に対処するために、半導体産業における進歩は望まれ続けている。1つまたは複数の用途において、強化されたショットキーダイオード、PINダイオード、絶縁ゲート・バイポーラ・トランジスタ(IGBT)、バイポーラ・ジャンクション・トランジスタ(BJT)などの、強化された高電圧半導体デバイスは、例えば、高速電力スイッチング用途のために望まれる場合がある。

例として、高電圧半導体デバイスは、製造の間に半導体デバイスの構造的支持のために設けられる、比較的厚い半導体基板上で製造することができる。不都合なことに、このような比較的厚い半導体基板は、例えば、半導体デバイスの過度の加熱さらには過熱をもたらす、半導体基板における低いキャリア移動度などの、最終的なデバイスの性能問題の一因となり得る。

したがって、大電力デバイスなどの、半導体デバイスのための製造技術におけるさらなる改良が望まれ続けている。

半導体層を含む多層構造を設けるステップであって、半導体層が、ドーパントを含みそして増加した導電率を有する前記ステップと、少なくとも部分的に、半導体層の気孔率を、電気化学処理を使用して、選択的に増加させるステップであって、気孔率を選択的に増加させるステップが、半導体層の増加した導電率を利用する前記ステップと、多層構造から選択的に増加された気孔率を持つ半導体層を、少なくとも部分的に、除去するステップとを含む方法の、1つの実施態様における、提供を通じて先行技術の欠点が克服されさらなる利点が提供される。

さらなる特徴および利点が本発明の技術を通じて実現される。本発明の他の実施形態および実施態様は、本明細書で詳細に説明され、特許請求された発明の一部とみなされる。

本発明の1つまたは複数の実施態様は、明細書の結びで特許請求の範囲における実施例として具体的に指摘され明確に主張される。本発明の、前述のおよび他の目的、特徴、および利点は、添付の図面に関連してなされる次の詳細な説明から明らかである。

本発明の1つまたは複数の実施態様に従って、例えば、第2の半導体層から第1の半導体層を除去することを容易にするように、第1の半導体層の気孔率を選択的に増加させるための電気化学プロセスの1つの実施形態を描写する。

本発明の1つまたは複数の実施態様に従って、電解質溶液の中で第1の半導体層を電気化学的に処理するための図1Bのアセンブリの代替描写である。

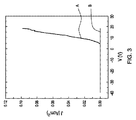

本発明の1つまたは複数の実施態様による、半導体層の電気化学処理の間に取得される電流密度−電圧プロファイルグラフである。

本発明の1つまたは複数の実施態様に従って、例えば、図1A〜図1Cの選択的半導体層除去処理を利用する、例示的な半導体構造を製造するためのプロセスの1つの実施形態を描写する。

本発明の1つまたは複数の実施態様に従って、例えば、図1A〜図1Cの選択的半導体層除去処理を利用する、別の半導体構造を製造するためのプロセスの1つの実施形態を描写する。

本発明の1つまたは複数の実施態様に従って、多層構造から半導体基板を分離することを容易にするように、半導体層の気孔率を選択的に増加させるための電気化学プロセスの1つの実施形態を描写する。

本発明の1つまたは複数の実施態様に従って、図6A〜図6Cの選択的半導体層除去処理を、部分的に、利用する半導体構造を製造するためのプロセスの1つの実施形態を描写する。

本発明の1つまたは複数の実施態様に従って、半導体基板を薄くするように多層構造の半導体基板の気孔率を選択的に増加させるための電気化学プロセスの1つの実施形態を描写する。

本発明の1つまたは複数の実施態様に従って、図8A〜図8Cの選択的半導体基板薄化処理を、部分的に、使用する半導体構造を製造するためのプロセスの1つの実施形態を描写する。

発明の詳細な説明

本発明の実施態様ならびにその一定の特徴、利点、および詳細は、添付の図面に例示される非限定的実施形態を参照して以下により完全に解説される。周知の材料、製造ツール、加工技術などの説明は、本発明を不必要に不明瞭にしないように詳細を省略する。しかしながら、詳細な説明および具体的な実施例は、本発明の実施形態を指し示すが、限定としてではなく、例示としてのみ与えられることを理解されたい。基礎をなす発明の概念の精神および/または範囲の中のさまざまな代替、変更、付加および/または配列は、本開示から当業者に明らかであろう。

1つまたは複数の特定の実装において、高濃度ドープ半導体層の気孔率を、電気化学処理を使用して、選択的に増加させることによって、ショットキーダイオード、PINダイオードなどの、高電圧電源デバイスから、炭化ケイ素(SiC)基板などの、高濃度ドープ半導体層を選択的に除去するための方法が本明細書で開示される。慣習的に、そして述べたように、ショットキーダイオード、PINダイオード、絶縁ゲート・バイポーラ・トランジスタ(IGBT)、バイポーラ・ジャンクション・トランジスタ(BJT)などの、高電圧半導体デバイスは、比較的厚い単結晶シリコン半導体ウェーハなどの、比較的厚い半導体基板上で製造されてきた。改良として、III−Vおよび/またはII−VI化合物(例えば、炭化ケイ素(SiC)、窒化ガリウム(GaN)など)などの、広バンドギャップ半導体材料は、製造される半導体デバイスの速度を向上させるために使用することができる。例えば、炭化ケイ素および/または窒化ガリウムなどの広バンドギャップ半導体材料は、それらの比較的広いバンドギャップ、高い破壊電界強度、高い電子移動度、および高い熱伝導特性に起因して、トランジスタ性能を強化するために望ましい場合がある。有利には、このような半導体材料上に形成された大電力半導体デバイスは、より高い温度、より高い電力レベルおよび/またはより低いオン抵抗で動作することができ、それによってトランジスタ性能および効率を改善することができる。

エピタキシャル層の結晶品質および輸送特性に劣化をもたらさない、それぞれ、エピタキシャルな炭化ケイ素または窒化ガリウム層からの、炭化ケイ素または窒化ガリウム基板などの広バンドギャップ半導体基板の除去は、エピタキシャルな炭化ケイ素または窒化ガリウム層の両側上でのバイポーラ電源デバイスの製造に特に有利であると考えられている。しかしながら、エピタキシャル層からの、例えば、350ミクロン以上の厚さの、厚い広バンドギャップ基板の除去は、簡単ではない。例えば、炭化ケイ素および窒化ガリウム結晶は硬質基板であり、したがって、これらの基板に対する機械研磨速度は非常に遅くなる。例えば、炭化ケイ素または窒化ガリウム結晶基板の化学機械研磨は、1時間当たりわずか数ミクロンの速度で進むことができる。より速い研削は、可能であるが、エピタキシャル薄膜上に機械的ストレスをもたらしエピタキシャル薄膜をやがて破壊する場合があり、それは、この手法を使用する処理に対してウェーハサイズを限定する。さらに、この構造で、機械研磨プロセスを停止させるためにエピタキシャル層と基板の界面に明白な「エッチング停止」層がない。加えるに、ウェーハは、エピタキシャル層成長後に曲率を有する場合があり、したがって、研磨速度は全ウェーハ上で一様ではない場合がある。

さらに、炭化ケイ素基板で、C面基板上の炭化ケイ素のエピタキシャル成長は、Si面基板上のエピタキシャル成長と比較して簡単ではない。有利には、本明細書に開示される処理を使用して炭化ケイ素基板から剥離されるエピタキシャル炭化ケイ素層は、さらなるデバイス製造のために準備ができている、高品質のC面およびSi面両方を有する。したがって、Si面炭化ケイ素基板上で炭化ケイ素薄膜を成長させ、そして次に基板からエピタキシャル炭化ケイ素薄膜を剥離することによって、高品質のC面エピタキシャル層はデバイス製造のために有利に取得される。

本開示は、例えば、高濃度ドープ半導体層の電気化学処理を使用して高濃度ドープ半導体層の気孔率を選択的に増加させることによって、低濃度ドープエピタキシャル成長半導体層から、炭化ケイ素(SiC)基板などの、高濃度ドープ半導体層を選択的に除去するための技術を(1つまたは複数の実施態様で)提供する。本明細書で開示される方法は、有利には、ショットキーダイオード、PINダイオード、IGBT、BJTなどの、高電圧電源デバイスを製造するために使用され得る、エピタキシャル成長半導体層の結晶性を高めることを容易にする。さらに、低濃度ドープされた、エピタキシャル成長半導体層は、エピタキシャル成長半導体層の任意の利用可能な結晶面上でデバイスを製造するために使うことができる。さらに、一度除去されると、増加した気孔率の高濃度ドープ半導体層は、例えば、非常に効率的なガスセンサ、分子フィルタ、電子フィールドエミッタ用電極などを製造することにおいてを含む、さまざまな目的のために使用することができる。

したがって、半導体構造を製造することを容易にするための方法であって、例えば、半導体層を含む多層構造を設けるステップであって、半導体層はドーパントを含み、増加した導電率を有する、ステップと、少なくとも部分的に、半導体層の気孔率を、電気化学処理を使用して、選択的に増加させるステップであって、気孔率を選択的に増加させるステップは半導体層の増加した導電率を利用する、ステップと、多層構造から選択的に増加された気孔率を持つ半導体層を、少なくとも部分的に、除去するステップとを含む方法が、1つまたは複数の実施態様で、概説され、本明細書で開示される。

1つまたは複数の実施形態において、気孔率を選択的に増加させるステップは、半導体層を、少なくとも部分的に、陽極酸化するステップを含む。例えば、気孔率を選択的に増加させるステップは、半導体層を、少なくとも部分的に、選択的に陽極酸化するために無機酸および酸化種を含む電解質溶液の中で半導体層を電気化学処理するステップを含むことができ、半導体層のドーパントは、半導体層の気孔率を選択的に増加させ、多層構造から半導体層を、少なくとも部分的に、除去するステップを容易にするために、半導体層の陽極酸化を強化する。電気化学処理するステップは、電解質溶液および半導体層を通して印加される電流密度を制御するステップを含むことができ、気孔率を選択的に増加させるステップは、少なくとも部分的に、印加される電流密度の関数である。

1つまたは複数の実装において、半導体層は第1の半導体層であり、方法は、第1の半導体層の気孔率を選択的に増加させるステップの前に、第1の半導体層の上に第2の半導体層をエピタキシャル成長させるステップをさらに含む。例として、第1の半導体層および第2の半導体層は、それぞれ広バンドギャップ半導体材料を含み得る。例えば、第1の半導体層および第2の半導体層は、それぞれ炭化ケイ素または炭化ケイ素合金を含み得る。あるいは、第1の半導体層および第2の半導体層は、それぞれ窒化ガリウムまたは窒化ガリウム合金を含んでもよい。

ある一定の実施形態において、第1の半導体層の増加した導電率は第1の導電率とすることができ、第2の半導体層は第2の導電率を有することができ、第1の半導体層の第1の導電率は第2の半導体層の第2の導電率より大きく、第1の半導体層の陽極酸化は、第2の半導体層の気孔率を増加させることなく、少なくとも部分的に、第1の半導体層の気孔率を選択的に増加させるために、第1の半導体層のより大きい導電率を利用することができる。例として、第1の半導体層の第1の導電率は、第2の半導体層の第2の導電率より10倍以上大きくすることができる。

1つまたは複数の実施形態において、多層構造を設けるステップは、半導体基板として半導体層を設けるステップを含むことができ、気孔率を選択的に増加させるステップは、半導体基板を、少なくとも部分的に、除去することを容易にする。この手法で、方法は、半導体層の気孔率を選択的に増加させるステップの前に、半導体層の上に多層半導体デバイスを設けるステップをさらに含み得る。例として、多層半導体デバイスは、PINダイオードまたはショットキーダイオードなどの、ダイオードとするかまたはこれを含むことができる。

1つまたは複数の他の実施形態において、多層構造を設けるステップは、半導体基板の上に半導体層を設けるステップを含むことができ、気孔率を選択的に増加させるステップは、多層構造から半導体基板を除去することを容易にすることができる。加えるに、多層構造を設けるステップは、半導体層の気孔率を選択的に増加させるステップの前に、半導体層の上に多層半導体デバイスを設けるステップを含み得る。1つまたは複数の実装において、方法は、多層構造の半導体基板の除去の前に支持基板に多層構造を接着するステップを含み得る。1つまたは複数のさらなる実施形態において、除去するステップは、多層構造の一部として薄化された半導体層を残して、多層構造から半導体層を部分的にのみ除去するステップを含み得る。これらの実施形態とともに、多層構造を設けるステップは、半導体層の上に多層半導体デバイスを設けるステップを同様に含み得る。同様に、多層構造を設けるステップは、多層構造の半導体基板として半導体層を設けるステップを含むことができ、薄化された半導体層は、多層構造の薄化された半導体基板である。

図面に以下で言及するが、図面は理解の容易さのため原寸に比例して描写されておらず、異なる図面を通じて使用される同じ参照番号は、同じまたは類似の層または構成要素を指定する。

述べたように、1つまたは複数の実施態様において、紫外線照射なしで、電気化学エッチング(ECE)プロセスを使用して、半導体材料を多孔質にすることによって、炭化ケイ素および窒化ガリウム、ならびにそれらの合金を含む、高濃度ドープされた、n型広バンドギャップ半導体などの、高濃度ドープされた、広バンドギャップ半導体を選択的にエッチングする方法が本明細書で開示される。ECEプロセスにおいて、(例えば、異なる導電率を持つ2つ以上の層を有する炭化ケイ素または窒化ガリウムウェーハを含む)多層構造は、作用電極としての役割を果たし、例えば、白金(Pt)電線が対電極として設けられる。電解液セルで、作用電極は正にバイアスされ得るが、高濃度ドープ炭化ケイ素または窒化ガリウム基板と電解液との間の接合部は逆バイアスされる。印加電圧がショットキー接合の降伏電圧(例えば、5〜20V)より大きいとき電流が流れることができ、高濃度ドープ炭化ケイ素または窒化ガリウム層は、酸化物形成を経て選択的に多孔質になり、その後分離して、電解液の中で(1つの実施形態で)溶解する。この手法で、無機酸の酸化剤との混合物を電解液として使用することができる。例えば、電解液として酸化物を溶解する酸を用いて、炭化ケイ素は多孔質になり、50〜100ミクロンの厚さの(またはより大きい)多孔質炭化ケイ素は単一層として基板から剥離することができる。1つまたは複数の実装において、この自己剥離プロセスは、格子不整合に起因する多孔質炭化ケイ素における大きな応力成長に関連している。プロセスは、例えば、実質的にすべての高導電性の、広バンドギャップ基板材料が分離され消費されるまで、繰り返すことができる。有利には、このプロセスは、高導電性基板と(より低い導電率を持つ)エピタキシャル層の界面で自己限定的である。さらに、高導電層が、例えば、半絶縁性基板と低濃度ドープエピタキシャル層との中間に埋め込まれる場合、半絶縁性基板および低濃度ドープエピタキシャル層は、説明したECEプロセスを介して埋め込まれた導電層を多孔質にすることによって分離することができる。これは、有利には、デバイス製造のためのエピタキシャル層の除去の後に、高価な半絶縁性の炭化ケイ素または窒化ガリウム基板の潜在的な再利用を容易にする。

例として、図1A〜図1Cは、本発明の1つまたは複数の実施態様に従って、例えば、第2の半導体層から第1の半導体層を(少なくとも部分的に)除去することを容易にするように、第1の半導体層の気孔率を、電気化学処理を使用して、選択的に増加させるためのプロセスの1つの実施形態を描写する。

図1Aは、本発明の1つまたは複数の実施態様に従って、高電圧電源デバイス(例えば、IGBTまたはBJTデバイス、ショットキーまたはPINダイオード、など)などの、半導体デバイスの製造の間に取得される中間の多層構造100の1つの実施形態を例示する。示されているように、半導体構造100は、第1の半導体層102および第1の半導体層102の上に配置された第2の半導体層104を含む。1つまたは複数の実装において、第1の半導体層102は、より高濃度でドープされた、より高い導電性のn+層を含み、第2の半導体層104は、より低濃度でドープされた、より低い導電性のn−層である。

より具体的には、1つまたは複数の実施形態において、第1の半導体層102は、バルク半導体材料などの、半導体基板とすることができる。例えば、第1の半導体層102は、III−Vおよび/またはII−VI化合物(例えば、炭化ケイ素(SiC)、窒化ガリウム(GaN)など)などの、広バンドギャップ半導体材料とするかまたはこれを含むことができ、n型ドーパントまたはp型ドーパントをドープされ得る。本明細書で使用される、広バンドギャップ半導体材料は、約1eVより大きいバンドギャップエネルギーを有する半導体材料を意味することに留意されたい。ただ例として、第1の半導体層102は、高導電性n+半導体層102(あるいは本明細書では、実装に応じて、n+基板102またはn+層102と呼ばれる)を作るために高濃度のn型ドーパントを注入されると想定される。n型ドーピングは、例えば、真性(非ドープ)半導体材料への、n型ドーパント不純物の付加を意味することに留意されたい。不純物は、真性材料に比べてより多くの電子が、部分的に、ドープ半導体層の電気伝導率を規定することに寄与する。可能なn型ドーパントの実施例は、(例えば)リン、ヒ素またはアンチモンを含む。1つの実施例において、炭化ケイ素半導体層は、例えば、n+基板102の中に望ましい濃度のn型ドーパントを供給するために1つまたは複数のイオン注入プロセスおよび/または拡散プロセスを使用してn型ドーパントを、注入され得る。特定の実施例において、n+基板102の中に注入されるn型ドーパントの濃度は、約1017atoms/cm3以上とすることができ、それは述べたように、基板の電気伝導率を増加させる。n+基板102の厚さは、第2の半導体層104に、そしてある一定の実施形態において、その後のデバイス処理の間に形成されるさらなる半導体デバイス層に、構造安定性を提供するのに十分である。1つの実施例で、n+基板102の厚さは300から600ミクロンの範囲内、またはそれ以上とすることができる。あるいは、基板は、特定の用途のために所望される場合、高導電性p+基板を作るためにp型ドーパントを注入され得ることに留意されたい。

述べたように、この実施例で、多層構造100は、n+基板102の上にエピタキシャル成長または析出することができる、第2の半導体層104を同様に含む。例えば、1つまたは複数の実施形態において、第2の半導体層104は、エピタキシャル単結晶半導体層とすることができる。第2の半導体層104の材料は、n+基板102の材料と類似とすることができ、(例えば)超高真空化学気相成長(UHV−CVD)、分子線エピタキシ(MBE)などの、さまざまなエピタキシャル成長プロセスによって形成され得る。さらに、第2の半導体層104は、より低い導電性のn−半導体層(あるいは本明細書ではn−エピ層104と呼ばれる)を作るために、同様に、しかしより低い濃度で、n型ドーパントを注入され得ることに留意されたい。例として、述べたように、n−エピ層104の導電率を規定する、n−エピ層104の中に注入されるn型ドーパントの濃度は、約1016atoms/cm3以下とすることができる。当業者はしたがって、n+基板102は、n−エピ層104と比較して高濃度にn型ドーパントをドープされ、例えば、(例として)n+基板102の導電率はn−エピ層104の導電率より約10倍以上大きいことを理解するであろう。

図1Bに例示されるように、多層構造100、そして特にn+基板102は、本発明の1つまたは複数の実施態様に従って、電気化学処理を受けることができる。例として、n+基板102の電気化学処理は、例えば、電気化学セル106、そして特に、陽極セルの中に配置された電解質溶液107を利用して達成することができ、多層構造100は、電解質溶液107の中に、導電性電極108とともに、浸されるまたは少なくとも部分的に沈められる。1つの実施形態において、n+基板102およびn−エピ層104を含む、多層構造100は、作用電極としての役割を果たし、一方、(例えば、白金などの金属とするかまたはこれを含むことができる)導電性電極108は、対電極としての役割を果たすことに留意されたい。1つの実施形態において、電解質溶液107は、電気が通過し得る液体とすることができ、無機酸および酸化種を含み得る。特定の実施例において、無機酸は、(SiLまたはGaN除去のための)フッ化水素酸(HF)、または(GaN除去のための)塩酸(HCl)などの、酸とするかまたはこれを含むことができ、一方酸化種は、過酸化水素(H2O2)または硝酸カリウム(KNO2)などの酸素含有酸化剤とするかまたはこれを含むことができる。多層構造100は、例えば、電源110を、使用して導電性電極108に電気的に接続することができ、電源110は、構造、そして特に、n+基板102を、n+基板102が陽極エッチングされ得るように導電性電極108に対して望ましいバイアス電圧にバイアスする。

例として、n+基板102を含む、多層構造100は、電源110によって正にバイアスすることができ、一方n+基板102と電解質溶液107との間の接合部は逆バイアスされる。印加される電圧がショットキー接合の降伏電圧より大きいとき、電流フローは、例えば、電解質溶液107からn+基板102へ、方向を示すことができ、n+基板102の露出した表面の陽極酸化をもたらし得る。n+基板102がn+炭化ケイ素層であると想定すると、1つの実施例において、n+基板102の露出した表面は、酸化ケイ素および二酸化炭素を形成するように酸化され得る。このような酸化は、有利には、例えば、ショットキーダイオード効果に起因する移動性キャリアの枯渇により、n+基板102の表面の気孔率を増加させる。上で論じたように、n−エピ層104の導電率と比較してより大きいn+基板102の導電率は、電流が基板を選択的に通過することを可能にし、それによって、n−エピ層104の気孔率を変更することまたは著しく変更することなく、n+基板102の気孔率を変更することに留意されたい。1つまたは複数の実施形態において、n+基板102の酸化表面の厚さは、電解質溶液107を通して印加される電流密度を制御することによって制御され得ることに留意されたい。これは、今度は、酸化表面の気孔率における増加を制御することを容易にし、n+基板102の増加する気孔率は、少なくとも部分的に、電解質溶液を通して印加される電流密度の関数である。1つまたは複数の実装において、印加される電流密度は、0.1A/cm2から1A/cm2の範囲内とすることができる。

述べたように、n+基板102の電気化学処理は、例えば、n+基板102の酸化部分と未酸化部分との間の格子不整合により、n+基板102の酸化された多孔質表面/層内で固有応力を引き起こし得る。酸化された多孔質表面内の固有応力は、望ましい臨界値に到達することができ、結果として、例えば、酸化された多孔質層は、n+基板102の未酸化部分から剥離し、1つまたは複数の実施形態においては、その後電解質溶液107に溶解する。n+基板の未酸化部分からの酸化された多孔質部分の除去の速度は、印加される電流密度、電解質溶液中の無機酸の濃度および/または酸化時間などのプロセスパラメータに依存し得るが、酸化された多孔質部分の除去の速度は、1つの実施例において、約200μm/時以上とすることができ、それは化学機械研磨手法を用いる基板除去より著しく速い。気孔率を増加させるためのn+基板の電気化学処理と酸化された多孔質部分の剥離は、例えば、n+基板が完全に消費され、および/または酸化された多孔質n+基板が臨界の厚さに到達するまで、1つまたは複数の反復サイクルで継続することができ、図1Cに描写されるように、多孔質n+基板102’をn−エピ層104から完全に除去することを可能にし得ることに同様に留意されたい。1つの実施例で、多孔質n+基板102’の臨界の厚さは約50から100μmの範囲内、またはそれ以上とすることができる。描写されるように、n−エピ層104は、n+基板の電気化学処理の間影響されないままであり、結果として、例えば、独立のエピタキシャル成長n−エピ層104となることに留意されたい。有利には、この独立のn−エピ層104は、n−エピ層104の任意の利用可能な結晶面(例えば、炭化ケイ素材料のSi面またはC面、または窒化ガリウム材料のGa面またはN面)上で、強化された半導体デバイス、例えば、電子デバイスまたは光電子デバイスを製造するために使用することができる。さらに、独立のエピタキシャル成長n−エピ層104は、本明細書で論じたように、PINダイオード、ショットキーダイオード、IGBTデバイスなどの、高電圧電源デバイスを製造するために、それ自体で半導体基板として使用することができる。このような用途において、より薄い半導体基板層は、有利には、大電力デバイスの動作の間により良好な熱放散を容易にすることができる。さらに、多孔質n+基板102’は、有利には、例えば、非常に効率的なガスセンサ、分子フィルタ、電子フィールドエミッタ用電極などを製造することにおいてなど、他の用途に再利用することができる。

さらなる例として、n+基板102およびn−エピ層104を含む、多層構造100は、図2の電気化学プロセスアセンブリで描写されるように、キャリア基板112に取り付けることができる。例示されるように、例えば、インジウムなどの、非導電性金属を含むかまたはこれで製造され得る、キャリア基板112は、台座114(例えば、真鍮基板などの金属基板)の上に置いて、多層構造100が電解質溶液107の中に浸されるまたは少なくとも部分的に沈められるように電気化学セル106に差し込むことができる。半導体層はn+炭化ケイ素基板およびn−炭化ケイ素エピ層であると想定すると、1つの実施例において、電解質溶液は、約90mLの、過酸化水素(H2O2)などの酸化種の中に、約10mLの、HClなどの無機酸を含むことができる。さらに、例えば、台座114を、例えば、蝋または他の適切な保護材料などの、不活性保護材料116の中に封入することによって、電気化学処理の間に望ましくないエッチングから任意の露出した表面を保護するように注意することができる。

述べたように、描写された多層構造は、本明細書に記載のようにn+基板102が陽極酸化およびエッチングされ得るように、導電性電極108に対して望ましいバイアス電圧に多層構造、そして特に、n+基板102をバイアスするために、例えば、電源110を使用して、導電性電極108に電気的に接続することができる。1つの実施形態において、望ましい電流密度を印加すると、多層構造の電気化学処理は、n+基板102の露出した表面を陽極酸化するという結果をもたらし、陽極酸化は、n−エピ層104に向かって進み、n+基板102とn−エピ層104の界面で終了し、n−エピ層104の気孔率を変更するおよび/またはこれに影響を与えることはない。図3に描写された電流密度−電圧プロファイル(ここで縦軸は電流密度(A/Cm2)を表し、横軸は印加電圧(V)を表す)によって証明されるように、適当な電流密度(例えば、約0.1アンペアまたは0.2アンペア)を確立すると、多層構造は陽極酸化を受け、結果として多孔質n+基板102の酸化およびエッチングが生じる。図3において、曲線Aは、電解質溶液を通して最初に印加される電流密度を描写し、曲線Bは、n+基板102が消費された後、例えば、ゼロに接近して、著しく減少する電流密度を描写し、エッチングプロセスがn+基板102とn−エピ層104の界面で自己限定すること、およびn+基板102の増加する気孔率が電解質溶液を通して印加される電流密度の関数であることを示す。

例として、図4A〜図4Gは、本明細書で説明した処理を(部分的に)利用する、PINダイオードなどの、多層半導体デバイスを含む半導体構造を製造するためのプロセスの1つの実施形態を描写する。

図4Aを参照すると、多層構造400は、上述の処理フローの図1Aの構造100と最初は類似または同一で例示される。簡単に、構造400は、n+基板102およびn−エピ層104を含む。述べたように、n+基板102およびn−エピ層104は、図1A〜図1Cに関連して上述したような、半導体材料とするかまたはこれらを含むことができる。例として、n+基板102は、n+炭化ケイ素層を作るためにn型ドーパントをドープされた半導体層(例えば、炭化ケイ素)とするかまたはこれを含むことができる。特定の実施例において、n+基板102の中に注入されるn型ドーパントの濃度は、約1017atoms/cm3以上とすることができる。さらに、n−エピ層104は、エピタキシャル成長し、例えば、より低い導電性のn−半導体層を作るためにn型ドーパントを、より少なくドープされた半導体層(例えば、炭化ケイ素)を含むかまたはこれで製造され得る。例えば、図1A〜図1Cに関連して上述したように、n−エピ層104は、例えば、n+基板102の上にエピタキシャル成長または析出することができ、n−エピ層104に注入されるn型ドーパントの濃度は、約1016atoms/cm3以下とすることができる。

図4Bは、n−エピ層104の上に多層半導体デバイス410が設けられた状態で、図4Aの多層構造を例示する。1つの実施例において、多層半導体デバイス410は、PINダイオードとすることができ、PINダイオード構造を形成するために、非ドープおよび/または低導電性の半導体層によって分離される、異なる導電率および/またはドーパントを持つ1つまたは複数の半導体層を含むことができる。描写されるように、多層半導体デバイス410は、例えば、オーム性接触層412、オーム性接触層412の上に配置されたドリフト層414、およびドリフト層414の上に配置されたオーム性接触層416を含み得る。多層半導体デバイス410の層の材料は、n+基板102およびn−エピ層104の材料と類似または同一とすることができ、(例えば)分子線エピタキシ(MBE)、超高真空化学気相成長(UHV−CVD)などの、さまざまなエピタキシャル成長プロセスによって形成され得る。描写された層412、414、416の厚さは、使われる製造プロセスおよび結果として生じるダイオードの望ましい機能性に応じて、変化し得る。1つの実施例において、n−エピ層104は、有利には、本明細書で説明した電気化学エッチング処理の間に、PINダイオードの1つまたは複数の高導電性半導体層412、416をエッチングされることから保護することを容易にする、停止層としての役割を果たし得ることに留意されたい。

1つまたは複数の特定の実施形態において、例えば、広バンドギャップ半導体材料(例えば、炭化ケイ素(SiC)、窒化ガリウム(GaN))を含むかまたはこれで製造され得る、オーム性接触層412は、n−エピ層104の上にエピタキシャル成長または析出することができ、高導電性n+オーム性接触層412を作るためにn型ドーパントを注入され得る。ドリフト層414は、オーム性接触層412の上にエピタキシャル成長または析出することができる。理解されるように、ドリフト層は、PINダイオードに対するドリフト領域としての役割を果たし、したがって、オーム性接触層412、416と比べて、ドーパント、例えば、n型ドーパントおよび/またはp型ドーパントを低濃度にドープされ得る。あるいは、ドリフト層414は、PINダイオード構造の真性領域とすることができ、したがって実質的に非ドープの、または意図せずドープされた半導体層とすることができる。さらに、例えば、オーム性接触層412の導電率と異なる導電率を有する、オーム性接触層416は、ドリフト層414の上にエピタキシャル成長または析出することができる。例として、そして述べたように、オーム性接触層412にn型ドーパントを注入することができ、一方オーム性接触層416にp型ドーパントをドープすることができ、またはその逆も同様である。

図4Cは、接触層418が多層半導体デバイス410の上に設けられた後、図4Bの半導体構造を例示する。接触層418は、オーム性接触層416へのオーム性接触としての役割を果たし、例えば、タンタル、タングステンまたはそれらの組み合わせもしくは合金などの、金属を含むかまたはこれで製造され得る。1つの実施形態において、接触層418は、スパッタリング、蒸着などの1つまたは複数の加工技術を使用して形成され得る。

1つまたは複数の実装において、多層構造400は、反転されて、例えば、適当な接着材料420を使用して、支持基板422に取り付けられる。例として、支持基板422は、例えば、真鍮、銅、アルミニウム、または、窒化アルミニウム(AlN)などの金属合金で、製造される金属基板とすることができ、接着材料420は、例えば、支持基板422を接触層418に接着することを容易にする、インジウムなどの接着金属とすることができる。

本明細書で開示されたように、多層構造400、そして特に、n+基板102は、上述のように、電気化学セルの中に配置された電解質溶液の中でn+基板を陽極酸化するように電気化学処理を受ける。述べたように、電気化学処理は、有利には、陽極酸化によってn+基板102の気孔率を選択的に増加させることを容易にし、そしてそれは、多層構造からn+基板102を除去することを容易にし、例示された残っている多層構造400と同様に、多孔質n+基板102’(図4Eに描写される)を作り出す。1つの実施例において、n−エピ層104は、電気化学処理の間にエッチング停止層として機能し、多層半導体デバイス410のより高導電性の半導体層を保護することを容易にすることに留意されたい。述べたように、多孔質n+基板102’は、有利には、所望される場合、例えば、非常に効率的なガスセンサ、分子フィルタ、および/または電子線エミッタ用電極を製造することなどの、他の用途に再利用することができる。

図4Fに示されるように、n−エピ層104(図4E)は、例示される独立の多層デバイス構造を残して、除去することができる。例として、n−エピ層は、化学機械研磨、または、エッチング停止として多層半導体デバイス410のオーム性接触層412を(1つの実施形態で)使用する反応性イオンエッチング(RIE)などの1つまたは複数のエッチングプロセスを使って除去することができる。図4Gに描写されるように、露出したオーム性接触層412をパターン形成し、その上に接触構造424を形成するために、1つまたは複数のリソグラフィプロセスをその後行うことができる。接触構造424は、オーム性接触層412へのオーム性接触としての役割を果たすことができ、例えば、タンタル、タングステンまたはそれらの組み合わせもしくは合金などの、金属を含むかまたはこれで製造され得る。

さらなる例として、図5A〜図5Fは、本明細書で説明した処理を(部分的に)利用する、ショットキーダイオードなどの、多層半導体デバイスを含む半導体構造を製造するためのプロセスの1つの実施形態を描写する。

図5Aを参照すると、多層構造500は、上述の処理フローの図1Aの構造100と最初は類似または同一で例示される。簡単に、構造500は、n+基板102、およびその上に配置されたn−エピ層104を含む。述べたように、n+基板102およびn−エピ層104は、図1A〜図1Cに関連して上述したような、半導体材料とするかまたはこれらを含むことができる。例として、n+基板102は、n+炭化ケイ素層を作るためにn型ドーパントをドープされた(炭化ケイ素などの)半導体層とするかまたはこれを含むことができる。特定の実施例において、n+基板102の中に注入されるn型ドーパントの濃度は、約1017atoms/cm3以上とすることができる。さらに、n−エピ層104は、エピタキシャル成長し、例えば、より低い導電性のn−半導体層を作るためにn型ドーパントを、より少なくドープされた半導体層(例えば、炭化ケイ素)を含むかまたはこれで製造され得る。例えば、図1A〜図1Cに関連して上述したように、n−エピ層104は、例えば、n+基板102の上にエピタキシャル成長または析出することができ、n−エピ層104に注入されるn型ドーパントの濃度は、約1016atoms/cm3以下とすることができる。

図5Bに例示されるように、さらなる半導体層512は、任意選択で、例えば、ショットキーダイオードなどの多層半導体デバイス510を規定することを容易にするように、n−エピ層104の上にエピタキシャル成長または析出することができる。半導体層512の材料は、n−エピ層104の材料と類似または同一とすることができ、層は(例えば)、例えばMBE、UHV−CVDなどの、さまざまなエピタキシャル成長プロセスによって形成され得る。さらに、(1つまたは複数の実施形態において)半導体層512は、例えば、n−エピ層104の導電率より実質的に大きい導電率を持つ、高導電性n+エピ層を作るためにn型ドーパントを、注入され得ることに留意されたい。この実施例において、多層半導体デバイス510は、デバイスの一部としてn−エピ層104を含むことに同様に留意されたい。

図5Cは、多層半導体デバイス510の上に接触層514を設けた後、図5Bの多層構造500を例示する。接触層514は、半導体層512へのオーム性接触としての役割を果たすことができ、例えば、タンタル、タングステンまたはそれらの組み合わせもしくは合金などの、金属を含むかまたはこれで製造され得る。1つの実施形態において、接触層514は、スパッタリング、蒸着などの1つまたは複数の加工技術を使用して形成され得る。

図4A〜図4Gに関連して上述した処理と類似して、多層構造500は、反転して、例えば、適当な接着材料420を介して、支持基板422に取り付けることができる。1つまたは複数の実装において、支持基板422は、真鍮、銅、アルミニウム基板などの金属基板、または窒化アルミニウム基板などの金属合金基板を含むことができ、接着材料420は、例えば、支持基板422を半導体構造の接触層514に接着する、インジウムなどの非導電性金属を含むことができる。

一度構造が支持基板422に接着されると、電気化学処理は、図1A〜図1Cに関連して上述したような、電解質溶液の中でn+基板102を少なくとも部分的に陽極酸化するために、使うことができる。n+基板102の陽極酸化は、n+基板102の気孔率を選択的に増加させるという結果をもたらし、そしてそれは、今度は、多層構造500から多孔質n+基板102’(図5E)を除去することを容易にする。

図5Fに例示されるように、ショットキー接触520は、任意選択で、例えば、結果として生じるショットキーダイオードの逆阻止電圧を最大化し順電圧降下を最小化するために、露出したn−エピ層104の上に形成され得る。ショットキー接触層520は、低導電性n−エピ層104と金属−半導体界面を形成し、ショットキー接合をもたらす。ショットキー接触520は、アルミニウム(Al)、チタン(Ti)、モリブデン(Mo)または金(Au)などの、1つまたは複数の低仕事関数金属を含むかまたはこれらで製造され得る。

例として、図6A〜図6Cは、本発明の1つまたは複数の実施態様に従って、半導体基板とエピタキシャル成長層を分離することを容易にするように、半導体層の気孔率を選択的に増加させるプロセスの代替実施形態を描写する。

図6Aを参照すると、一般に600と表示された、多層構造の1つの実施形態が描写されており、これは、例えば、本明細書に記載のような、高電圧電源デバイス用の製造プロセスで、使用することができる。例示されるように、多層構造600は、バルク半導体材料、例えば、バルク・シリコン・ウェーハ、などの半導体基板601を含む。別の実施例として、半導体基板601は、単結晶Si、多結晶Si、非晶質Si基板などを含むがこれらに限定されない、任意のケイ素含有基板を含むことができ、特定の用途のために所望されるように、低濃度ドープされたn型またはp型材料とすることができる。

示されているように、多層構造600は、薄いn+層102、およびその上に配置された低導電性n−エピ層104をさらに含む。述べたように、n+層102およびn−エピ層104は、図1A〜図1Cに関連して上述したような、半導体材料とするかまたはこれらを含むことができる。例として、n+層102は、(炭化ケイ素または窒化ガリウムなどの)半導体層とするかまたはこれを含むことができ、半導体基板601の上にエピタキシャル成長または析出することができる。n+層102の厚さは、使われる製造プロセスおよび望ましい機能性に依存し得るが、1つの実施例において、n+層102は、(ウェーハ層の末端への電流フローを容易にするように)約10から30μmの範囲内の厚さを持つ、薄い半導体層として形成することができる。1つの実施例において、n+層102の中に注入されるn型ドーパントの濃度は、約1017atoms/cm3以上とすることができる。さらに、n−エピ層104は、エピタキシャル成長し、例えば、より低い導電性のn−半導体層を作るためにn型ドーパントを、より少なくドープされた半導体層(例えば、炭化ケイ素または窒化ガリウム)を含むかまたはこれで製造され得る。例えば、図1A〜図1Cに関連して上述したように、n−エピ層104は、例えば、n+層102の上にエピタキシャル成長または析出することができ、n−エピ層104に注入されるn型ドーパントの濃度は、約1016atoms/cm3以下とすることができる。

図6Bに例示されるように、多層構造600は、上述のように電気化学セルの中に配置された電解質溶液を、部分的に、利用して、本明細書に記載のように、電気化学処理を受けることができる。例として、多層構造の電気化学処理は、有利には、説明したように、n+層102を選択的に陽極酸化することを容易にし、その気孔率を選択的に増加させる。この選択的に増加した気孔率は、今度は、(図6Cに描写されるように)半導体基板601およびn−エピ層104を、n+層102(図6B)とのそれらのそれぞれの界面に沿って、多層構造から分離することを容易にする。1つまたは複数の実装において、分離された層が電解質溶液107の中で溶解され、結果として生じる酸化多孔質層がさらなる使用のために回復され得ないように、n+層102の厚さは、十分に薄くすることができることに留意されたい。論じたように、n+層102の陽極酸化の速度は、印加される電流密度および/または酸化時間などのプロセスパラメータに依存することができ、所望される場合、プロセスパラメータは、半導体基板601とn−エピ層104との間に挟まれたn+層102を完全に酸化するように選択または延長することができる。有利には、このプロセスで、半導体基板601は、さらなる、繰り返されるエピタキシャル成長プロセスのために再利用することができる。

例として、図7A〜図7Fは、図6A〜図6Cに関連して上述した処理を、部分的に、使用して、ショットキーダイオードなどの、半導体構造を製造するためのプロセスの1つの実施形態を描写する。この点に関して、図7A〜図7Fはショットキーダイオードを製造する1つの実施例を描写するが、説明される処理は、例えば、PINダイオードなどの他のダイオード構造、または、IGBTまたはBJTなどのトランジスタ構造を含む、他の多層半導体デバイスを製造するために、当業者によって使われ得ることに留意されたい。ショットキーダイオードを製造するための図7A〜図7Fで描写された例示的なプロセスは、ただ例として提示されるにすぎない。

図7Aを参照すると、多層構造700は、図6Aの多層構造600と最初は類似または同一で例示される。簡単に、多層構造700は、半導体基板601、半導体基板601の上に配置された薄いn+層102、およびn+層102の上に配置されたn−エピ層104を含む。述べたように、描写された層の材料は、図6Aに関連して上述したような、半導体材料とするかまたはこれらを含むことができる。

多層半導体デバイス710は、n−エピ層104の上にさらなる半導体層712を設けることによって形成され得る。このさらなる半導体層712は、任意選択で、例えば、ショットキーダイオードを、規定することを容易にするようにn−エピ層104の上にエピタキシャル成長または析出することができる。半導体層712の材料は、半導体層512(図5B)の材料と類似または同一とすることができ、上述の析出プロセスのいずれかを使用して形成され得る。半導体層712およびn−エピ層104は、ともに多層半導体デバイス710の1つの実施例を規定する。所望される場合、半導体層712は、例えば、n−エピ層104の導電率より実質的に大きい導電率を持つ、高導電性n+エピ層を作る、n型ドーパントを含み得る。

図7Cは、多層半導体デバイス710の上に接触層712を設けた後、図7Bの多層構造を例示する。接触層714は、例えば、半導体層712へのオーム性接触としての役割を果たすことができ、接触層514(図5C)の材料と類似とすることができ、例えば、接触層514に対して上で述べた析出プロセスの1つを使用して形成され得る。

図7Dに例示されるように、上述の処理と類似して、多層構造700は、反転して、例えば、上述のような接着材料420を使用して、支持基板422に取り付けることができる。1つまたは複数の実装において、支持基板422は、真鍮、銅、アルミニウムなどの金属、または、窒化アルミニウム(AlN)などの金属合金を含むかまたはこれで製造され得る。接着材料420は、非導電性接着用金属、例えば、インジウムなどの、接着用金属とすることができる。

多層構造に付着した支持基板422で、電気化学処理は、図7Eに例示されるように、そして図6A〜図6Cに関連して上述したように、多層構造700から半導体基板601を分離することを容易にするようにn+層102の気孔率を選択的に増加させるために、使うことができる。述べたように、一度酸化されると、多孔質層が電気化学処理の間に電解質溶液の中で溶解され得るように、n+層102の厚さは十分に薄くなるよう選択することができる。

所望される場合、ショットキー接触720(図7F)は、任意選択で、例えば、結果として生じるショットキーダイオードの逆阻止電圧を最大化し順電圧降下を最小化するために、露出したn−エピ層104の上に形成され得る。ショットキー接触720の材料および形成プロセスは、図5Fに関して上述した、ショットキー接触520の材料および形成プロセスと類似とすることができる。

さらなる例として、図8A〜図8Cは、本発明の1つまたは複数の実施態様に従って、半導体基板を部分的に薄くすることを容易にするように、半導体基板の気孔率を選択的に増加させるプロセスの1つの実施形態を描写する。

図8Aを参照すると、多層構造800は、上述の図1Aの構造100と類似または同一で例示される。簡単に、多層構造800は、n+基板102、およびその上に配置されたn−エピ層104を含む。述べたように、n+基板102およびn−エピ層104は、図1A〜図1Cに関連して上述したような、半導体材料とするかまたはこれらを含むことができる。例として、n+基板102は、例えば、n+炭化ケイ素層基板を作るためにn型ドーパントをドープされた炭化ケイ素基板などの、半導体層またはウェーハとするかまたはこれを含むことができる。特定の実施例において、n+基板102の中のn型ドーパントの濃度は、約1017atoms/cm3以上とすることができる。さらに、n−エピ層104は、エピタキシャル成長し、例えば、低導電性のn−半導体層を作るためにn型ドーパントを、より少なくドープされた半導体層(例えば、炭化ケイ素)を含むかまたはこれで製造され得る。例えば、図1A〜図1Cに関連して上述したように、n−エピ層104は、例えば、n+基板102の上にエピタキシャル成長または析出することができ、n−エピ層104に注入されるn型ドーパントの濃度は、約1016atoms/cm3以下とすることができる。

上述のように、そして図8Bに例示されるように、多層構造800、そして特に、n+基板102は、電解質溶液の中でn+基板102を陽極酸化するように電気化学処理を受ける。1つまたは複数の実施形態において、n+基板102の気孔率における増加が、n−エピ層104からn+基板102を部分的にのみ除去するまたは薄くするために使用される、望ましい厚さに制御されるように、この電気化学処理の間に使われるプロセスパラメータが調整され得ることに留意されたい。例えば、電気化学プロセスは、n+基板102の規定されたまたは望ましい量が酸化したまたは気孔率において増加した後、電流密度を増加させることによって、調整され得る。増加した電流密度は、図8Cに描写されるように、n−エピ層104に付着した未酸化の薄化されたn+基板102を残して、多孔質のまたは酸化された層が外れるという結果をもたらし得る。薄化されたn+基板の減少した厚さは、望ましい機能性に応じて、変化し得るが、1つの実施例において、n+基板102の厚さは、約50%から90%減少させることができる。さらに、上述のように、n+基板102の除去された多孔質部分は、有利には、他の用途に再利用することができる。

例として、図9A〜図9Dは、図8A〜図8Cの上述の処理を(部分的に)利用して、PINダイオードなどの、半導体構造を製造するためのプロセスの1つの実施形態を描写する。図9A〜図9Dの実施例は、ただ例として提供されるにすぎないことに留意されたい。他の多層デバイス構造は、本明細書に記載のように、上で開示された処理概念を使用して製造することができる。

これらの図に例示されるように、図8A〜図8Cの薄化プロセスの変形形態を使うことができ、ここでは、半導体構造900は、多層半導体デバイス910がn+基板102上に直接配置されている状態で、上述のような、n+基板102を含む。すなわち、この実施例においては、n+基板102の一部が最終的な構造の中に残存し、したがって、電気化学処理の間にエッチングから多層半導体デバイス910を保護するので、上で論じた実施例の第2の半導体層(104)は、省略することができる。

例として、半導体層(またはn+基板)102は、バルク半導体材料とすることができる。例えば、半導体層102は、III−Vおよび/またはII−VI半導体化合物(例えば、炭化ケイ素、窒化ガリウム)などの、広バンドギャップ半導体材料とするかまたはこれを含むことができ、n型ドーパントまたはp型ドーパントをドープされ得る。描写されるように、半導体層102は、高導電性n+半導体層または基板102(すなわち、n+基板102)を作るためにn型ドーパントを注入され得る。例として、n+基板102の中に注入されるn型ドーパントの濃度は、約1017atoms/cm3以上とすることができる。

述べたように、多層半導体デバイス910は、例として、PINダイオードを規定する。多層半導体デバイス910の多数の層は、図4Bに関連して上述した多層半導体デバイス410の層と類似または同一とすることができる。例えば、多層半導体デバイス910は、PINダイオード構造を形成するために、非ドープおよび/またはより低い導電性の半導体層によって分離された、(例えば、オーム性接触層としての役割を果たす)異なる導電率および/またはドーパントを持つ1つまたは複数の半導体層を含み得る。1つの実施例において、多層半導体デバイス910は、オーム性接触層912、オーム性接触層912の上に配置されたドリフト層914、およびドリフト層914の上に配置されたオーム性接触層916を含み得る。1つの実施例において、オーム性接触層912にn型ドーパントを大量に注入することができ、オーム性接触層916にp型ドーパントを大量に注入することができ、またはその逆も同様である。さらに、ドリフト層914は、ドリフト領域としての役割を果たすように低濃度にドープしてもよく、または真性領域としての役割を果たすように非ドープのままであってもよい。

図9Bは、多層半導体デバイス910の上に接触層918を設けた後、図9Aの構造を例示する。接触層918は、例えば、タンタル、タングステンまたはそれらの組み合わせもしくは合金などの、金属を含むかまたはこれで製造され得る。1つの実施形態において、接触層918は、スパッタリング、蒸着などの1つまたは複数の加工技術を使用して形成され得る。

図9Cに示されるように、多層構造900は、上述のように、電解質溶液の中でn+基板102を陽極酸化するように電気化学処理を受けることができる。述べたように、電気化学処理は、有利には、陽極酸化によってn+基板102の気孔率を選択的に増加させることを容易にし、そしてそれは、多層構造900からのn+基板102の一部の選択的な除去を容易にする。この実施形態において、n+基板102の増加した気孔率が、n+基板102を部分的にのみ除去するまたは薄くするために、望ましい厚さに制御されるように、電気化学処理の間に使われるプロセスパラメータが調整されることに留意されたい。これは、今度は、図9Cに描写されるように、減少した厚さの薄化されたn+基板102の上に多層半導体デバイス910を残す。有利には、上述のように、所望される場合、除去された多孔質n+基板102’は、他の用途に再利用することができる。

図9Dに描写されるように、1つまたは複数のリソグラフィプロセスは、多層半導体デバイス910の接触層918をパターン形成するために行うことができ、オーム性接触920は、多層半導体デバイスへの電気接続を容易にするように薄化されたn+基板102に付加することができる。接触層918、920は、オーム性接触としての役割を果たすことができ、それぞれ、nドープまたはpドープされた、例えば、タンタル、タングステンまたはそれらの組み合わせもしくは合金などの金属を含むかまたはこれで製造され得る。

本明細書で使用される専門用語は、ただ特定の実施形態を説明する目的のために使用されるにすぎず、本発明を限定しているように意図されない。本明細書で使用される、単数形「1つの(a)」、「1つの(an)」および「この(the)」は、文脈が別途明らかに示さない限り、同様に複数形を含むように意図される。用語「含む(comprise)」(および「含む(comprises)」および「含む(comprising)」などの、含む(comprise)の任意の形態)、「有する(have)」(および「有する(has)」および「有する(having)」などの、有する(have)の任意の形態)、「含む(include)」(および「含む(includes)」、「含む(including)」などの含む(include)の任意の形態)、および「含む(contain)」(および「含む(contains)」および「含む(containing)」などの含む(contain)の任意の形態)が非限定的な連結動詞であることは、さらに理解されるであろう。結果として、1つまたは複数のステップまたは要素を「含む(comprises)」、「有する(has)」、「含む(includes)」または「含む(contains)」方法またはデバイスは、それらの1つまたは複数のステップまたは要素を保有するが、それらの1つまたは複数のステップまたは要素だけを保有するように限定されない。同様に、1つまたは複数の特徴を「含む(comprises)」、「有する(has)」、「含む(includes)」または「含む(contains)」方法のステップまたはデバイスの要素は、それらの1つまたは複数の特徴を保有するが、それらの1つまたは複数の特徴だけを保有するように限定されない。さらに、ある一定の方法で構成されるデバイスまたは構造は、少なくともその方法で構成されるが、列挙されていない方法で同様に構成され得る。

以下の特許請求の範囲におけるすべてのミーンズ・プラス・ファンクション要素またはステップ・プラス・ファンクション要素の、対応する構造、材料、作用、および均等物は、もしあれば、具体的に特許請求された他の請求の要素とともに機能を行うための、任意の構造、材料または作用を含むように意図される。本発明の説明は、例示および説明の目的のために提示されたが、網羅的であるようにまたは開示された形での発明に限定されるように意図されない。多くの変更および変形形態は、本発明の範囲および精神から逸脱することなく、当業者に明らかであろう。実施形態は、本発明の1つまたは複数の実施態様の原理および実用的応用を最もよく解説するために、および当業者が企図される特定の使用に適するようなさまざまな変更を伴うさまざまな実施形態のために本発明の1つまたは複数の実施態様を理解することを可能にするために、選択され説明された。