JP2010251663A - 半導体装置 - Google Patents

半導体装置 Download PDFInfo

- Publication number

- JP2010251663A JP2010251663A JP2009102278A JP2009102278A JP2010251663A JP 2010251663 A JP2010251663 A JP 2010251663A JP 2009102278 A JP2009102278 A JP 2009102278A JP 2009102278 A JP2009102278 A JP 2009102278A JP 2010251663 A JP2010251663 A JP 2010251663A

- Authority

- JP

- Japan

- Prior art keywords

- inductor

- circuit

- semiconductor device

- wiring layer

- substrate

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- H10W20/497—

-

- H10W44/501—

-

- H10W70/60—

-

- H10W70/611—

-

- H10W72/00—

-

- H10W90/00—

-

- H10W90/293—

Landscapes

- Engineering & Computer Science (AREA)

- Semiconductor Integrated Circuits (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

Abstract

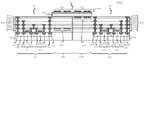

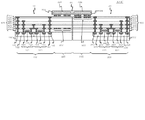

【解決手段】配線基板60は、半導体チップ10の第1インダクタ302上から半導体チップ20の第2インダクタ322上に亘って取り付けられている。配線基板60は、第3インダクタ304及び第4インダクタ324を有している。第3インダクタ304は第1インダクタ302の上方に位置している。第1インダクタ302から第3インダクタ304までの距離は、第2インダクタ322から第4インダクタ324までの距離より長い。

【選択図】図1

Description

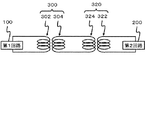

前記一つまたは二つの半導体チップは、

信号を生成する第1回路と、

前記配線層に形成され、前記第1回路に接続された第1インダクタと、

前記信号を処理する第2回路と、

前記配線層に形成され、前記第2回路に接続された第2インダクタと、

を有し、

前記配線基板は、

前記第1インダクタの上方に位置する第3インダクタと、

前記第2インダクタの上方に位置し、前記第3インダクタに接続している第4インダクタと、

を有し、

前記第1インダクタから前記第3インダクタまでの距離は、前記第2インダクタから前記第4インダクタまでの距離と異なる半導体装置が提供される。

12 第1領域

14 第2領域

20 半導体チップ

60 配線基板

100 第1回路

102 第1基板

104 シリコン基板

106 絶縁層

108 シリコン層

109 絶縁分離層

120 ウェル

121 第1トランジスタ

122 不純物領域

124 不純物領域

126 ゲート電極

140 ウェル

141 第1トランジスタ

142 不純物領域

144 不純物領域

146 ゲート電極

200 第2回路

202 第2基板

220 ウェル

221 第2トランジスタ

222 不純物領域

224 不純物領域

226 ゲート電極

240 ウェル

241 第2トランジスタ

242 不純物領域

244 不純物領域

246 ゲート電極

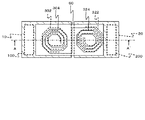

300 第1信号伝達素子

302 第1インダクタ

304 第3インダクタ

320 第2信号伝達素子

322 第2インダクタ

324 第4インダクタ

400 多層配線層

410 絶縁層

412 配線層

420 絶縁層

422 配線層

430 絶縁層

432 配線層

440 絶縁層

442 配線層

500 多層配線層

510 絶縁層

512 配線層

520 絶縁層

522 配線層

530 絶縁層

532 配線層

540 絶縁層

542 配線層

602 シリコン基板

604 配線層

606 送受信回路

Claims (8)

- 配線層を有する一つまたは二つの半導体チップ、及び前記一つまたは二つの半導体チップの配線層側に取り付けられた配線基板を備え、

前記一つまたは二つの半導体チップは、

信号を生成する第1回路と、

前記配線層に形成され、前記第1回路に接続された第1インダクタと、

前記信号を処理する第2回路と、

前記配線層に形成され、前記第2回路に接続された第2インダクタと、

を有し、

前記配線基板は、

前記第1インダクタの上方に位置する第3インダクタと、

前記第2インダクタの上方に位置し、前記第3インダクタに接続している第4インダクタと、

を有し、

前記第1インダクタから前記第3インダクタまでの距離は、前記第2インダクタから前記第4インダクタまでの距離と異なる半導体装置。 - 請求項1に記載の半導体装置において、

前記第1インダクタから前記第3インダクタまでの距離は、前記第2インダクタから前記第4インダクタまでの距離より長い半導体装置。 - 請求項1又は2に記載の半導体装置において、

前記配線基板はシリコン基板を用いて形成されている半導体装置。 - 請求項3に記載の半導体装置において、

前記一つまたは二つの半導体チップはシリコン基板を用いて形成されており、

前記配線基板における基板不純物濃度は、前記一つまたは二つの半導体チップの基板不純物濃度より低い半導体装置。 - 請求項3又は4に記載の半導体装置において、

前記配線基板に形成され、回路上において前記第3インダクタと前記第4インダクタの間に設けられた送受信回路を備える半導体装置。 - 請求項1〜5のいずれか一つに記載の半導体装置において、

前記第3インダクタ及び前記第4インダクタは、前記配線基板のうち前記一つまたは二つの半導体チップとは反対側の面に形成されている半導体装置。 - 請求項1〜6のいずれか一つに記載の半導体装置において、

前記第1回路及び前記第1インダクタは第1の前記半導体チップに形成されており、

前記第2回路及び前記第2インダクタは第2の前記半導体チップに形成されており、

前記配線基板は、前記第1の半導体チップ上から前記第2の半導体チップ上に亘って取り付けられている半導体装置。 - 請求項1〜6のいずれか一つに記載の半導体装置において、

前記第1回路、前記第2回路、前記第1インダクタ、及び前記第2インダクタは一つの前記半導体チップに形成されており、

前記第1回路及び前記第1インダクタは前記半導体チップの第1領域に形成されており、

前記第2回路及び前記第2インダクタは前記半導体チップの第2領域に形成されており、

前記第1領域及び前記第2領域は絶縁されている半導体装置。

Priority Applications (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009102278A JP5496541B2 (ja) | 2009-04-20 | 2009-04-20 | 半導体装置 |

| US12/662,442 US8310025B2 (en) | 2009-04-20 | 2010-04-16 | Semiconductor device |

| US13/667,955 US8810042B2 (en) | 2009-04-20 | 2012-11-02 | Semiconductor device |

| US14/328,458 US9496220B2 (en) | 2009-04-20 | 2014-07-10 | Semiconductor device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009102278A JP5496541B2 (ja) | 2009-04-20 | 2009-04-20 | 半導体装置 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2014042515A Division JP5749366B2 (ja) | 2014-03-05 | 2014-03-05 | 半導体装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2010251663A true JP2010251663A (ja) | 2010-11-04 |

| JP2010251663A5 JP2010251663A5 (ja) | 2012-06-07 |

| JP5496541B2 JP5496541B2 (ja) | 2014-05-21 |

Family

ID=42980368

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2009102278A Expired - Fee Related JP5496541B2 (ja) | 2009-04-20 | 2009-04-20 | 半導体装置 |

Country Status (2)

| Country | Link |

|---|---|

| US (3) | US8310025B2 (ja) |

| JP (1) | JP5496541B2 (ja) |

Cited By (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2016157387A1 (ja) * | 2015-03-30 | 2016-10-06 | 株式会社PEZY Computing | 半導体装置 |

| US10269734B2 (en) | 2015-07-16 | 2019-04-23 | Ultramemory Inc. | Semiconductor element |

| JP2019153685A (ja) * | 2018-03-02 | 2019-09-12 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

| JP2023046880A (ja) * | 2021-09-24 | 2023-04-05 | 株式会社東芝 | 半導体装置 |

| JP2024039782A (ja) * | 2022-09-12 | 2024-03-25 | 株式会社東芝 | アイソレータ |

Families Citing this family (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5578797B2 (ja) * | 2009-03-13 | 2014-08-27 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

| IT1404038B1 (it) * | 2010-12-29 | 2013-11-08 | St Microelectronics Srl | Dispositivo elettronico a semiconduttore provvisto di un elemento isolatore galvanico integrato, e relativo procedimento di assemblaggio |

| US9337905B2 (en) * | 2013-07-01 | 2016-05-10 | Texas Instruments Incorporated | Inductive structures with reduced emissions and interference |

| US20150077208A1 (en) * | 2013-09-16 | 2015-03-19 | Ken Goldman | High-q parallel-trace planar spiral coil for biomedical implants |

| JP6395304B2 (ja) * | 2013-11-13 | 2018-09-26 | ローム株式会社 | 半導体装置および半導体モジュール |

| CN105659340B (zh) * | 2014-01-15 | 2019-03-22 | 株式会社村田制作所 | 电路 |

| US9997495B2 (en) * | 2014-12-19 | 2018-06-12 | Elwha Llc | Non-contacting inductive interconnects |

| CN209590845U (zh) * | 2016-12-02 | 2019-11-05 | 株式会社村田制作所 | 辅助天线、rfid系统 |

| US10438906B2 (en) * | 2016-12-07 | 2019-10-08 | Nxp Usa, Inc. | Radio frequency (RF) inductive signal coupler and method therefor |

| JP7437275B2 (ja) | 2020-09-09 | 2024-02-22 | 株式会社東芝 | 電子デバイス |

| JP7686394B2 (ja) * | 2020-12-24 | 2025-06-02 | ローム株式会社 | ゲートドライバ |

| JP7638183B2 (ja) * | 2021-09-02 | 2025-03-03 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2006246372A (ja) * | 2005-03-07 | 2006-09-14 | Fuji Xerox Co Ltd | Rfid用中継アンテナおよびrfidシステム |

| JP2007235034A (ja) * | 2006-03-03 | 2007-09-13 | Seiko Epson Corp | 電子基板、半導体装置および電子機器 |

| JP2008502215A (ja) * | 2004-06-03 | 2008-01-24 | シリコン・ラボラトリーズ・インコーポレイテッド | スペクトル拡散アイソレータ |

| JP2010103611A (ja) * | 2008-10-21 | 2010-05-06 | Keio Gijuku | 電子回路 |

Family Cites Families (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5952849A (en) | 1997-02-21 | 1999-09-14 | Analog Devices, Inc. | Logic isolator with high transient immunity |

| US6201287B1 (en) * | 1998-10-26 | 2001-03-13 | Micron Technology, Inc. | Monolithic inductance-enhancing integrated circuits, complementary metal oxide semiconductor (CMOS) inductance-enhancing integrated circuits, inductor assemblies, and inductance-multiplying methods |

| US6882239B2 (en) | 2001-05-08 | 2005-04-19 | Formfactor, Inc. | Electromagnetically coupled interconnect system |

| JP2004039867A (ja) * | 2002-07-03 | 2004-02-05 | Sony Corp | 多層配線回路モジュール及びその製造方法 |

| JP2005327931A (ja) | 2004-05-14 | 2005-11-24 | Sony Corp | 集積化インダクタおよびそれを用いた受信回路 |

| JP5070511B2 (ja) | 2006-10-27 | 2012-11-14 | シャープ株式会社 | インダクタ対の磁気結合を利用したシリアルデータ伝送装置 |

-

2009

- 2009-04-20 JP JP2009102278A patent/JP5496541B2/ja not_active Expired - Fee Related

-

2010

- 2010-04-16 US US12/662,442 patent/US8310025B2/en active Active

-

2012

- 2012-11-02 US US13/667,955 patent/US8810042B2/en active Active

-

2014

- 2014-07-10 US US14/328,458 patent/US9496220B2/en active Active

Patent Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2008502215A (ja) * | 2004-06-03 | 2008-01-24 | シリコン・ラボラトリーズ・インコーポレイテッド | スペクトル拡散アイソレータ |

| JP2006246372A (ja) * | 2005-03-07 | 2006-09-14 | Fuji Xerox Co Ltd | Rfid用中継アンテナおよびrfidシステム |

| JP2007235034A (ja) * | 2006-03-03 | 2007-09-13 | Seiko Epson Corp | 電子基板、半導体装置および電子機器 |

| JP2010103611A (ja) * | 2008-10-21 | 2010-05-06 | Keio Gijuku | 電子回路 |

Cited By (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2016157387A1 (ja) * | 2015-03-30 | 2016-10-06 | 株式会社PEZY Computing | 半導体装置 |

| JPWO2016157387A1 (ja) * | 2015-03-30 | 2018-01-25 | 株式会社PEZY Computing | 半導体装置 |

| US10192836B2 (en) | 2015-03-30 | 2019-01-29 | Pezy Computing K.K. | Semiconductor device |

| US10269734B2 (en) | 2015-07-16 | 2019-04-23 | Ultramemory Inc. | Semiconductor element |

| JP2019153685A (ja) * | 2018-03-02 | 2019-09-12 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

| JP7038570B2 (ja) | 2018-03-02 | 2022-03-18 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

| JP2023046880A (ja) * | 2021-09-24 | 2023-04-05 | 株式会社東芝 | 半導体装置 |

| JP2024039782A (ja) * | 2022-09-12 | 2024-03-25 | 株式会社東芝 | アイソレータ |

| JP7775167B2 (ja) | 2022-09-12 | 2025-11-25 | 株式会社東芝 | アイソレータ |

Also Published As

| Publication number | Publication date |

|---|---|

| US8810042B2 (en) | 2014-08-19 |

| JP5496541B2 (ja) | 2014-05-21 |

| US20130056849A1 (en) | 2013-03-07 |

| US9496220B2 (en) | 2016-11-15 |

| US20100264515A1 (en) | 2010-10-21 |

| US8310025B2 (en) | 2012-11-13 |

| US20140319691A1 (en) | 2014-10-30 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5496541B2 (ja) | 半導体装置 | |

| JP5214525B2 (ja) | 半導体装置 | |

| JP5324829B2 (ja) | 半導体装置 | |

| JP5578797B2 (ja) | 半導体装置 | |

| JP5435029B2 (ja) | 半導体装置及び信号伝達方法 | |

| JP5238562B2 (ja) | 半導体装置 | |

| JP5749366B2 (ja) | 半導体装置 | |

| JP6062486B2 (ja) | 半導体装置 | |

| JP5968968B2 (ja) | 半導体装置 | |

| JP5562459B2 (ja) | 半導体装置 | |

| JP6081961B2 (ja) | 半導体装置 | |

| JP2013239731A (ja) | 半導体装置 | |

| JP2014064015A (ja) | 半導体装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120412 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20120412 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20131119 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20131121 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20131211 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140106 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20140212 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20140305 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5496541 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| LAPS | Cancellation because of no payment of annual fees |