JP2010079653A - 定電圧電源回路 - Google Patents

定電圧電源回路 Download PDFInfo

- Publication number

- JP2010079653A JP2010079653A JP2008248062A JP2008248062A JP2010079653A JP 2010079653 A JP2010079653 A JP 2010079653A JP 2008248062 A JP2008248062 A JP 2008248062A JP 2008248062 A JP2008248062 A JP 2008248062A JP 2010079653 A JP2010079653 A JP 2010079653A

- Authority

- JP

- Japan

- Prior art keywords

- current

- load current

- output

- transistor

- power supply

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- G—PHYSICS

- G05—CONTROLLING; REGULATING

- G05F—SYSTEMS FOR REGULATING ELECTRIC OR MAGNETIC VARIABLES

- G05F1/00—Automatic systems in which deviations of an electric quantity from one or more predetermined values are detected at the output of the system and fed back to a device within the system to restore the detected quantity to its predetermined value or values, i.e. retroactive systems

- G05F1/10—Regulating voltage or current

- G05F1/46—Regulating voltage or current wherein the variable actually regulated by the final control device is dc

- G05F1/56—Regulating voltage or current wherein the variable actually regulated by the final control device is dc using semiconductor devices in series with the load as final control devices

- G05F1/575—Regulating voltage or current wherein the variable actually regulated by the final control device is dc using semiconductor devices in series with the load as final control devices characterised by the feedback circuit

-

- G—PHYSICS

- G05—CONTROLLING; REGULATING

- G05F—SYSTEMS FOR REGULATING ELECTRIC OR MAGNETIC VARIABLES

- G05F1/00—Automatic systems in which deviations of an electric quantity from one or more predetermined values are detected at the output of the system and fed back to a device within the system to restore the detected quantity to its predetermined value or values, i.e. retroactive systems

- G05F1/10—Regulating voltage or current

- G05F1/46—Regulating voltage or current wherein the variable actually regulated by the final control device is dc

- G05F1/56—Regulating voltage or current wherein the variable actually regulated by the final control device is dc using semiconductor devices in series with the load as final control devices

- G05F1/565—Regulating voltage or current wherein the variable actually regulated by the final control device is dc using semiconductor devices in series with the load as final control devices sensing a condition of the system or its load in addition to means responsive to deviations in the output of the system, e.g. current, voltage, power factor

- G05F1/569—Regulating voltage or current wherein the variable actually regulated by the final control device is dc using semiconductor devices in series with the load as final control devices sensing a condition of the system or its load in addition to means responsive to deviations in the output of the system, e.g. current, voltage, power factor for protection

- G05F1/573—Regulating voltage or current wherein the variable actually regulated by the final control device is dc using semiconductor devices in series with the load as final control devices sensing a condition of the system or its load in addition to means responsive to deviations in the output of the system, e.g. current, voltage, power factor for protection with overcurrent detector

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Electromagnetism (AREA)

- General Physics & Mathematics (AREA)

- Radar, Positioning & Navigation (AREA)

- Automation & Control Theory (AREA)

- Continuous-Control Power Sources That Use Transistors (AREA)

- Control Of Electrical Variables (AREA)

Abstract

【解決手段】定電圧電源回路は、誤差増幅部50と、出力用PMOS81を有する出力部80と、PMOS81に流れる負荷電流をモニタし、負荷電流に応じて誤差増幅部50のバイアス電流を増加させる負荷電流モニタ部60と、電流制限用の抵抗62を有し、負荷電流をモニタしてこの負荷電流に応じて誤差増幅部50のゲインを低下させるゲイン調整部70とを備えている。そのため、起動時や過負荷時にゲイン調整部70をリミッタ回路として動作するようになるため、起動時や過負荷時に内部の消費電流を制限できる。しかも、起動時においては、このリミッタ動作により、起動時の応答を遅くすることとなるため、オーバシュートの発生を抑制できる。

【選択図】図1

Description

この定電圧電源回路は、基準電圧Vrefと出力端子30から出力される出力電圧Voutに比例した電圧Vfbとの差分を増幅する誤差増幅部10と、この誤差増幅部10の出力側に接続され、誤差増幅部10の出力により制御されて出力端子30から出力する出力電圧Voutを一定に制御する出力部20とにより構成されている。

外部にコンデンサ31が接続された図4の回路構成の場合、定電圧電源回路の誤差増幅部10と出力部20の周波数特性は、図5に示すように、誤差増幅部10のポールよりも出力部20のポールが低周波域に存在する場合がある。2つのポールが存在する場合は、2つのポールが近い周波数域に存在すると、位相余裕がとれず、出力電圧Voutの発振を生じるおそれがあるため、十分に2つのポールを分離する必要がある。

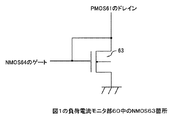

この定電圧電源回路では、図4の回路に、負荷電流モニタ部40が付加されている。負荷電流モニタ部40は、出力端子30の出力電流に比例したバイアス電流を誤差増幅部10へフィードバックすることで、高速応答と低消費電流を実現する回路であり、PMOS41及びNMOS42,43により構成されている。

図8は、図6の定電圧電源回路において負荷電流が小さい場合の周波数特性を示す図である。

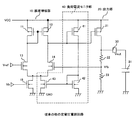

図1は、本発明の実施例1における定電圧電源回路を示す回路図である。

この定電圧電源回路は、例えば、半導体集積回路に搭載される回路であって、従来と同様の誤差増幅部50を有し、この誤差増幅部50の出力側に、従来とは異なる構成の負荷電流モニタ部60、新たに追加されたゲイン調整部70、及び従来と同様の出力部80が縦続接続され、更に、この出力部80の出力側に、出力電圧Voutを出力する出力端子90が接続されている。

電源電圧VCC、基準電圧Vref、及びバイアス電圧Vbが印加されると、誤差増幅部50は、基準電圧Vrefと、出力電圧Voutを抵抗82,83で分圧したフィードバック電圧Vfbとの差分を増幅して、出力用PMOS81のゲート電圧を生成する。出力用PMOS81は、このゲート電圧により制御され、出力電圧Voutを一定に制御する。

図1の定電圧電源回路において、起動時や過負荷時には出力用PMOS81に大きな電流が流れるため、PMOS81のドレイン電流をコピーする負荷電流モニタ部60のPMOS61のドレイン電流も大きくなる。しかし、抵抗62が挿入されているので、PMOS61のドレイン電流がある電流値以上になった時に、抵抗62の電圧降下により、NMOS63のソース・ドレイン間電圧が低くなる。これに伴い、NMOS64のゲート電圧が低くなるため、ドレイン電流が減少し、誤差増幅部50のバイアス電流が減少する。

本実施例1によれば、図1に示す回路構成とすることにより、起動時や過負荷時にゲイン調整部70をリミッタ回路として動作するようになるため、起動時や過負荷時に内部の消費電流を制限できる。しかも、起動時においては、このリミッタ動作により、起動時の応答を遅くすることとなるため、オーバシュートの発生を抑制できる。

本発明は、上記実施例1に限定されず、種々の利用形態や変形が可能である。この利用形態や変形例としては、例えば、次の(a)〜(c)のようなものがある。

60 負荷電流モニタ部

62 抵抗

70 ゲイン調整部

80 出力部

Claims (6)

- バイアス電圧によりバイアス電流が流れ、基準電圧と出力端子から出力される出力電圧に対応する第1の電圧との差分を増幅する誤差増幅部と、

前記出力端子と電源ノードとの間に接続され、前記誤差増幅部の出力により制御されて前記出力電圧を一定に制御する出力トランジスタと、

前記出力トランジスタに流れる負荷電流をモニタし、前記負荷電流に応じて前記バイアス電流を増加させる負荷電流モニタ部と、

前記負荷電流をモニタし、前記負荷電流に応じて前記誤差増幅部のゲインを低下させるゲイン調整部と、

前記負荷電流モニタ部内に設けられ、起動時あるいは過負荷時における前記負荷電流モニタ部の消費電流あるいは前記バイアス電流を制限する電流制限抵抗と、

を有することを特徴とする定電圧電源回路。 - 前記誤差増幅部は、

前記基準電圧及び前記第1の電圧をそれぞれ入力して差動増幅する第1及び第2の入力トランジスタと、

前記バイアス電圧に基づき、前記第1及び第2の入力トランジスタに前記バイアス電流を流す定電流源用の第1のトランジスタと、

を有する差動増幅器により構成されていることを特徴とする請求項1記載の定電圧電源回路。 - 前記負荷電流モニタ部は、

前記第1のトランジスタに対して並列に接続されたバイアス電流調整用の第2のトランジスタと、

前記出力トランジスタと共にカレントミラー回路を構成して前記負荷電流をモニタする第3のトランジスタと、

前記第3のトランジスタに対して直列に接続され、前記第2のトランジスタと共にカレントミラー回路を構成して、前記第3のトランジスタに流れる電流に対応した電流を、前記第2のトランジスタに流す第4のトランジスタと、

前記第4のトランジスタに対して直列に接続された前記電流制限抵抗と、

を有することを特徴とする請求項2記載の定電圧電源回路。 - 前記第1の電圧は、前記出力電圧を抵抗で分圧して生成されることを特徴とする請求項1〜3のいずれか1項に記載の定電圧電源回路。

- 前記出力端子には、安定化用コンデンサが接続されることを特徴とする請求項1〜4のいずれか1項に記載の定電圧電源回路。

- 前記定電圧電源回路は、半導体集積回路に搭載されていることを特徴とする請求項1〜5のいずれか1項に記載の定電圧電源回路。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008248062A JP5097664B2 (ja) | 2008-09-26 | 2008-09-26 | 定電圧電源回路 |

| US12/556,068 US8232783B2 (en) | 2008-09-26 | 2009-09-09 | Constant-voltage power supply circuit |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008248062A JP5097664B2 (ja) | 2008-09-26 | 2008-09-26 | 定電圧電源回路 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010079653A true JP2010079653A (ja) | 2010-04-08 |

| JP5097664B2 JP5097664B2 (ja) | 2012-12-12 |

Family

ID=42056711

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008248062A Active JP5097664B2 (ja) | 2008-09-26 | 2008-09-26 | 定電圧電源回路 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US8232783B2 (ja) |

| JP (1) | JP5097664B2 (ja) |

Cited By (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2011053765A (ja) * | 2009-08-31 | 2011-03-17 | Sanyo Electric Co Ltd | オーバーシュート防止回路 |

| JP2012123705A (ja) * | 2010-12-10 | 2012-06-28 | Seiko Epson Corp | 集積回路装置及び電子機器 |

| US8232783B2 (en) | 2008-09-26 | 2012-07-31 | Oki Semiconductor Co., Ltd. | Constant-voltage power supply circuit |

| JP2015210673A (ja) * | 2014-04-25 | 2015-11-24 | セイコーインスツル株式会社 | 過電流保護回路、半導体装置、及びボルテージレギュレータ |

| JP2017091316A (ja) * | 2015-11-12 | 2017-05-25 | 新日本無線株式会社 | 安定化電源回路 |

| JP2017207902A (ja) * | 2016-05-18 | 2017-11-24 | 新日本無線株式会社 | 安定化電源回路 |

| CN108491020A (zh) * | 2018-06-08 | 2018-09-04 | 长江存储科技有限责任公司 | 低压差稳压器和快闪存储器 |

| DE102018109823A1 (de) | 2017-04-25 | 2018-10-25 | New Japan Radio Co. Ltd. | Konstantspannungs-Leistungsversorgungsschaltung |

| US10558232B2 (en) | 2015-05-26 | 2020-02-11 | Sony Corporation | Regulator circuit and control method |

| JP2020505679A (ja) * | 2017-01-07 | 2020-02-20 | 日本テキサス・インスツルメンツ合同会社 | 低ドロップアウトレギュレータを補償する方法及び回路要素 |

| JP2020194269A (ja) * | 2019-05-27 | 2020-12-03 | エイブリック株式会社 | ボルテージレギュレータ |

Families Citing this family (23)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5402530B2 (ja) * | 2009-10-27 | 2014-01-29 | 株式会社リコー | 電源回路 |

| US9112422B1 (en) | 2010-03-09 | 2015-08-18 | Vlt, Inc. | Fault tolerant power converter |

| JP5385237B2 (ja) * | 2010-09-28 | 2014-01-08 | 旭化成エレクトロニクス株式会社 | レギュレータ回路 |

| EP2533126B1 (en) * | 2011-05-25 | 2020-07-08 | Dialog Semiconductor GmbH | A low drop-out voltage regulator with dynamic voltage control |

| US8710809B2 (en) * | 2011-06-28 | 2014-04-29 | Stmicroelectronics International N.V. | Voltage regulator structure that is operationally stable for both low and high capacitive loads |

| CN103048542A (zh) * | 2011-10-14 | 2013-04-17 | 鸿富锦精密工业(深圳)有限公司 | 电流校准电阻的测定装置及系统 |

| US8922179B2 (en) * | 2011-12-12 | 2014-12-30 | Semiconductor Components Industries, Llc | Adaptive bias for low power low dropout voltage regulators |

| US8729951B1 (en) | 2012-11-27 | 2014-05-20 | Freescale Semiconductor, Inc. | Voltage ramp-up protection |

| US20140266106A1 (en) * | 2013-03-14 | 2014-09-18 | Vidatronic, Inc. | Ldo and load switch supporting a wide range of load capacitance |

| US8917070B2 (en) * | 2013-03-14 | 2014-12-23 | Vidatronic, Inc. | LDO and load switch supporting a wide range of load capacitance |

| US20140347026A1 (en) * | 2013-05-21 | 2014-11-27 | Nxp B.V. | Circuit for voltage regulation |

| US9229462B2 (en) * | 2013-06-27 | 2016-01-05 | Stmicroelectronics International N.V. | Capless on chip voltage regulator using adaptive bulk bias |

| US9395730B2 (en) * | 2013-06-27 | 2016-07-19 | Stmicroelectronics International N.V. | Voltage regulator |

| US9395733B2 (en) * | 2013-08-23 | 2016-07-19 | Macronix International Co., Ltd. | Voltage adjusting circuit applied to reference circuit |

| WO2017164197A1 (ja) * | 2016-03-25 | 2017-09-28 | パナソニックIpマネジメント株式会社 | レギュレータ回路 |

| US11336167B1 (en) | 2016-04-05 | 2022-05-17 | Vicor Corporation | Delivering power to semiconductor loads |

| US10277105B1 (en) | 2016-04-05 | 2019-04-30 | Vlt, Inc. | Method and apparatus for delivering power to semiconductors |

| US10785871B1 (en) | 2018-12-12 | 2020-09-22 | Vlt, Inc. | Panel molded electronic assemblies with integral terminals |

| US10903734B1 (en) | 2016-04-05 | 2021-01-26 | Vicor Corporation | Delivering power to semiconductor loads |

| US10158357B1 (en) | 2016-04-05 | 2018-12-18 | Vlt, Inc. | Method and apparatus for delivering power to semiconductors |

| US9904305B2 (en) * | 2016-04-29 | 2018-02-27 | Cavium, Inc. | Voltage regulator with adaptive bias network |

| JP7063753B2 (ja) * | 2018-07-13 | 2022-05-09 | エイブリック株式会社 | ボルテージレギュレータ及びボルテージレギュレータの制御方法 |

| GB2599474B (en) * | 2020-05-08 | 2023-04-05 | Cirrus Logic Int Semiconductor Ltd | Circuitry for providing an output voltage |

Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH03158912A (ja) * | 1989-11-17 | 1991-07-08 | Seiko Instr Inc | ボルテージ・レギュレーター |

| JP2001034351A (ja) * | 1999-07-21 | 2001-02-09 | Hitachi Ltd | 電圧安定化回路およびそれを用いた半導体装置 |

| US20020130646A1 (en) * | 2001-01-26 | 2002-09-19 | Zadeh Ali Enayat | Linear voltage regulator using adaptive biasing |

| US20030111986A1 (en) * | 2001-12-19 | 2003-06-19 | Xiaoyu (Frank) Xi | Miller compensated nmos low drop-out voltage regulator using variable gain stage |

| JP2006285854A (ja) * | 2005-04-04 | 2006-10-19 | Ricoh Co Ltd | 定電圧回路 |

| JP2007233657A (ja) * | 2006-02-28 | 2007-09-13 | Oki Electric Ind Co Ltd | 増幅器とそれを用いた降圧レギュレータ及び演算増幅器 |

Family Cites Families (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5085238B2 (ja) * | 2007-08-31 | 2012-11-28 | ラピスセミコンダクタ株式会社 | 基準電圧回路 |

| JP5097664B2 (ja) * | 2008-09-26 | 2012-12-12 | ラピスセミコンダクタ株式会社 | 定電圧電源回路 |

-

2008

- 2008-09-26 JP JP2008248062A patent/JP5097664B2/ja active Active

-

2009

- 2009-09-09 US US12/556,068 patent/US8232783B2/en not_active Expired - Fee Related

Patent Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH03158912A (ja) * | 1989-11-17 | 1991-07-08 | Seiko Instr Inc | ボルテージ・レギュレーター |

| JP2001034351A (ja) * | 1999-07-21 | 2001-02-09 | Hitachi Ltd | 電圧安定化回路およびそれを用いた半導体装置 |

| US20020130646A1 (en) * | 2001-01-26 | 2002-09-19 | Zadeh Ali Enayat | Linear voltage regulator using adaptive biasing |

| US20030111986A1 (en) * | 2001-12-19 | 2003-06-19 | Xiaoyu (Frank) Xi | Miller compensated nmos low drop-out voltage regulator using variable gain stage |

| JP2006285854A (ja) * | 2005-04-04 | 2006-10-19 | Ricoh Co Ltd | 定電圧回路 |

| JP2007233657A (ja) * | 2006-02-28 | 2007-09-13 | Oki Electric Ind Co Ltd | 増幅器とそれを用いた降圧レギュレータ及び演算増幅器 |

Cited By (16)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8232783B2 (en) | 2008-09-26 | 2012-07-31 | Oki Semiconductor Co., Ltd. | Constant-voltage power supply circuit |

| JP2011053765A (ja) * | 2009-08-31 | 2011-03-17 | Sanyo Electric Co Ltd | オーバーシュート防止回路 |

| JP2012123705A (ja) * | 2010-12-10 | 2012-06-28 | Seiko Epson Corp | 集積回路装置及び電子機器 |

| TWI658665B (zh) * | 2014-04-25 | 2019-05-01 | 日商艾普凌科有限公司 | 過電流保護電路、半導體裝置、及電壓調節器 |

| JP2015210673A (ja) * | 2014-04-25 | 2015-11-24 | セイコーインスツル株式会社 | 過電流保護回路、半導体装置、及びボルテージレギュレータ |

| US10558232B2 (en) | 2015-05-26 | 2020-02-11 | Sony Corporation | Regulator circuit and control method |

| JP2017091316A (ja) * | 2015-11-12 | 2017-05-25 | 新日本無線株式会社 | 安定化電源回路 |

| JP2017207902A (ja) * | 2016-05-18 | 2017-11-24 | 新日本無線株式会社 | 安定化電源回路 |

| JP2020505679A (ja) * | 2017-01-07 | 2020-02-20 | 日本テキサス・インスツルメンツ合同会社 | 低ドロップアウトレギュレータを補償する方法及び回路要素 |

| JP7108166B2 (ja) | 2017-01-07 | 2022-07-28 | テキサス インスツルメンツ インコーポレイテッド | 低ドロップアウトレギュレータを補償する方法及び回路要素 |

| DE102018109823A1 (de) | 2017-04-25 | 2018-10-25 | New Japan Radio Co. Ltd. | Konstantspannungs-Leistungsversorgungsschaltung |

| US10838445B2 (en) | 2017-04-25 | 2020-11-17 | New Japan Radio Co., Ltd. | Constant-voltage power supply circuit |

| CN108491020A (zh) * | 2018-06-08 | 2018-09-04 | 长江存储科技有限责任公司 | 低压差稳压器和快闪存储器 |

| CN108491020B (zh) * | 2018-06-08 | 2024-06-07 | 长江存储科技有限责任公司 | 低压差稳压器和快闪存储器 |

| JP2020194269A (ja) * | 2019-05-27 | 2020-12-03 | エイブリック株式会社 | ボルテージレギュレータ |

| JP7292108B2 (ja) | 2019-05-27 | 2023-06-16 | エイブリック株式会社 | ボルテージレギュレータ |

Also Published As

| Publication number | Publication date |

|---|---|

| JP5097664B2 (ja) | 2012-12-12 |

| US20100079121A1 (en) | 2010-04-01 |

| US8232783B2 (en) | 2012-07-31 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5097664B2 (ja) | 定電圧電源回路 | |

| JP5008472B2 (ja) | ボルテージレギュレータ | |

| JP4953246B2 (ja) | ボルテージレギュレータ | |

| US7304540B2 (en) | Source follower and current feedback circuit thereof | |

| US7301322B2 (en) | CMOS constant voltage generator | |

| JP6316632B2 (ja) | ボルテージレギュレータ | |

| JP5343698B2 (ja) | 電圧調整装置 | |

| JP2009116679A (ja) | リニアレギュレータ回路、リニアレギュレーション方法及び半導体装置 | |

| JP2008217203A (ja) | レギュレータ回路 | |

| JP2010191619A (ja) | ボルテージレギュレータ | |

| JP6564691B2 (ja) | 安定化電源回路 | |

| JP2017126259A (ja) | 電源装置 | |

| TWI629581B (zh) | 電壓調節器 | |

| JP2008211707A (ja) | 入力回路 | |

| JP2020166384A (ja) | 電源回路 | |

| JP2010141589A (ja) | 差動増幅回路 | |

| JP4552569B2 (ja) | 定電圧電源回路 | |

| JP2010258509A (ja) | バイアス安定化機能付き増幅回路 | |

| JP2010003115A (ja) | 定電流回路 | |

| JP4892366B2 (ja) | 過電流保護回路およびボルテージレギュレータ | |

| US20060267568A1 (en) | Voltage regulating circuit and method thereof | |

| JP3907640B2 (ja) | 過電流防止回路 | |

| JP2011118865A (ja) | 過電流保護回路及び定電圧電源回路 | |

| JP2020087192A (ja) | 電源回路 | |

| KR102658159B1 (ko) | 과열 보호 회로 및 이것을 구비한 반도체 장치 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110922 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20111220 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120808 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20120828 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20120924 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5097664 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150928 Year of fee payment: 3 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |