JP2010062404A - 半導体装置の製造方法 - Google Patents

半導体装置の製造方法 Download PDFInfo

- Publication number

- JP2010062404A JP2010062404A JP2008227884A JP2008227884A JP2010062404A JP 2010062404 A JP2010062404 A JP 2010062404A JP 2008227884 A JP2008227884 A JP 2008227884A JP 2008227884 A JP2008227884 A JP 2008227884A JP 2010062404 A JP2010062404 A JP 2010062404A

- Authority

- JP

- Japan

- Prior art keywords

- resin material

- sealing

- resin

- sealing resin

- semiconductor device

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 110

- 238000004519 manufacturing process Methods 0.000 title claims description 33

- 229920005989 resin Polymers 0.000 claims abstract description 182

- 239000011347 resin Substances 0.000 claims abstract description 182

- 238000007789 sealing Methods 0.000 claims abstract description 122

- 239000000463 material Substances 0.000 claims abstract description 109

- 229910052751 metal Inorganic materials 0.000 claims abstract description 48

- 239000002184 metal Substances 0.000 claims abstract description 48

- 229920001187 thermosetting polymer Polymers 0.000 claims abstract description 44

- 239000007787 solid Substances 0.000 claims description 39

- 238000000034 method Methods 0.000 claims description 28

- 239000000758 substrate Substances 0.000 claims description 8

- 239000000843 powder Substances 0.000 claims description 7

- 238000010438 heat treatment Methods 0.000 claims description 4

- 239000011164 primary particle Substances 0.000 claims 1

- 239000002245 particle Substances 0.000 abstract description 49

- 239000000126 substance Substances 0.000 abstract description 4

- CSCPPACGZOOCGX-UHFFFAOYSA-N Acetone Chemical compound CC(C)=O CSCPPACGZOOCGX-UHFFFAOYSA-N 0.000 description 38

- 230000008569 process Effects 0.000 description 19

- 238000010298 pulverizing process Methods 0.000 description 16

- 239000011342 resin composition Substances 0.000 description 14

- 238000000748 compression moulding Methods 0.000 description 11

- 230000002411 adverse Effects 0.000 description 10

- 239000000945 filler Substances 0.000 description 8

- 238000004898 kneading Methods 0.000 description 8

- 238000009826 distribution Methods 0.000 description 7

- 239000000203 mixture Substances 0.000 description 6

- 238000001721 transfer moulding Methods 0.000 description 6

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 5

- 239000003822 epoxy resin Substances 0.000 description 5

- 229920000647 polyepoxide Polymers 0.000 description 5

- 239000003795 chemical substances by application Substances 0.000 description 4

- 230000000694 effects Effects 0.000 description 4

- 238000012856 packing Methods 0.000 description 4

- 238000001816 cooling Methods 0.000 description 3

- 238000000151 deposition Methods 0.000 description 3

- 239000008187 granular material Substances 0.000 description 3

- 230000001788 irregular Effects 0.000 description 3

- VTYYLEPIZMXCLO-UHFFFAOYSA-L Calcium carbonate Chemical compound [Ca+2].[O-]C([O-])=O VTYYLEPIZMXCLO-UHFFFAOYSA-L 0.000 description 2

- 238000006243 chemical reaction Methods 0.000 description 2

- 230000007547 defect Effects 0.000 description 2

- 230000008021 deposition Effects 0.000 description 2

- 239000012535 impurity Substances 0.000 description 2

- 238000002844 melting Methods 0.000 description 2

- 230000008018 melting Effects 0.000 description 2

- 230000004048 modification Effects 0.000 description 2

- 238000012986 modification Methods 0.000 description 2

- 239000000377 silicon dioxide Substances 0.000 description 2

- 229920002050 silicone resin Polymers 0.000 description 2

- KXGFMDJXCMQABM-UHFFFAOYSA-N 2-methoxy-6-methylphenol Chemical compound [CH]OC1=CC=CC([CH])=C1O KXGFMDJXCMQABM-UHFFFAOYSA-N 0.000 description 1

- 239000006087 Silane Coupling Agent Substances 0.000 description 1

- GWEVSGVZZGPLCZ-UHFFFAOYSA-N Titan oxide Chemical compound O=[Ti]=O GWEVSGVZZGPLCZ-UHFFFAOYSA-N 0.000 description 1

- PNEYBMLMFCGWSK-UHFFFAOYSA-N aluminium oxide Inorganic materials [O-2].[O-2].[O-2].[Al+3].[Al+3] PNEYBMLMFCGWSK-UHFFFAOYSA-N 0.000 description 1

- 229910000019 calcium carbonate Inorganic materials 0.000 description 1

- 230000008859 change Effects 0.000 description 1

- 239000003638 chemical reducing agent Substances 0.000 description 1

- 239000000470 constituent Substances 0.000 description 1

- 230000006870 function Effects 0.000 description 1

- 238000005469 granulation Methods 0.000 description 1

- 230000003179 granulation Effects 0.000 description 1

- 239000011256 inorganic filler Substances 0.000 description 1

- 229910003475 inorganic filler Inorganic materials 0.000 description 1

- 238000005259 measurement Methods 0.000 description 1

- 238000002156 mixing Methods 0.000 description 1

- 229920001568 phenolic resin Polymers 0.000 description 1

- 239000005011 phenolic resin Substances 0.000 description 1

- 229920001721 polyimide Polymers 0.000 description 1

- 239000009719 polyimide resin Substances 0.000 description 1

- 239000010453 quartz Substances 0.000 description 1

- 238000007873 sieving Methods 0.000 description 1

- 229920002545 silicone oil Polymers 0.000 description 1

- 229910000679 solder Inorganic materials 0.000 description 1

- 239000012798 spherical particle Substances 0.000 description 1

- OGIDPMRJRNCKJF-UHFFFAOYSA-N titanium oxide Inorganic materials [Ti]=O OGIDPMRJRNCKJF-UHFFFAOYSA-N 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/50—Assembly of semiconductor devices using processes or apparatus not provided for in a single one of the subgroups H01L21/06 - H01L21/326, e.g. sealing of a cap to a base of a container

- H01L21/56—Encapsulations, e.g. encapsulation layers, coatings

- H01L21/565—Moulds

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/481—Disposition

- H01L2224/48151—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/48221—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/48225—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

- H01L2224/48227—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation connecting the wire to a bond pad of the item

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2225/00—Details relating to assemblies covered by the group H01L25/00 but not provided for in its subgroups

- H01L2225/03—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00

- H01L2225/04—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers

- H01L2225/065—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers the devices being of a type provided for in group H01L27/00

- H01L2225/06503—Stacked arrangements of devices

- H01L2225/06555—Geometry of the stack, e.g. form of the devices, geometry to facilitate stacking

- H01L2225/06568—Geometry of the stack, e.g. form of the devices, geometry to facilitate stacking the devices decreasing in size, e.g. pyramidical stack

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Manufacturing & Machinery (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Encapsulation Of And Coatings For Semiconductor Or Solid State Devices (AREA)

- Structures Or Materials For Encapsulating Or Coating Semiconductor Devices Or Solid State Devices (AREA)

Abstract

【解決手段】配線基板2上に搭載されると共に、配線基板2と電気的に接続された半導体素子4を、樹脂封止装置11に配置する。樹脂封止装置11内に熱硬化性の封止樹脂材料15を供給する。封止樹脂材料15は熱硬化性樹脂の硬化物を有する固形状異物を含んでいるが、予め樹脂封止時に半導体素子4や金属ワイヤ6に悪影響を及ぼさない粒径まで微粉化されている。微粉化した封止樹脂材料15を用いて、半導体素子4を樹脂封止する。

【選択図】図2

Description

Claims (5)

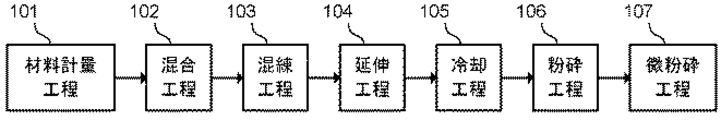

- 熱硬化性樹脂の硬化物を有する固形状異物を含有し、かつ前記固形状異物を含めて微粉化された熱硬化性の封止樹脂材料を用意する工程と、

回路基材上に搭載されると共に、前記回路基材と電気的に接続された半導体素子を、前記微粉化された封止樹脂材料を用いて封止する工程と

を具備することを特徴とする半導体装置の製造方法。 - 請求項1記載の半導体装置の製造方法において、

前記樹脂封止工程は、前記半導体素子の近傍に前記封止樹脂材料を供給する工程と、前記封止樹脂材料を加圧しつつ加熱し、流動化させた前記封止樹脂材料で前記半導体素子を覆う工程と、前記封止樹脂材料を熱硬化させ、前記封止樹脂材料の硬化物で前記半導体素子を封止する工程とを備えることを特徴とする半導体装置の製造方法。 - 請求項1または請求項2記載の半導体装置の製造方法において、

前記半導体素子上における前記封止樹脂材料の硬化物の厚さをTとしたとき、前記封止樹脂材料は前記固形状異物の最大径がT未満となるように微粉化されていることを特徴とする半導体装置の製造方法。 - 請求項1ないし請求項3のいずれか1項記載の半導体装置の製造方法において、

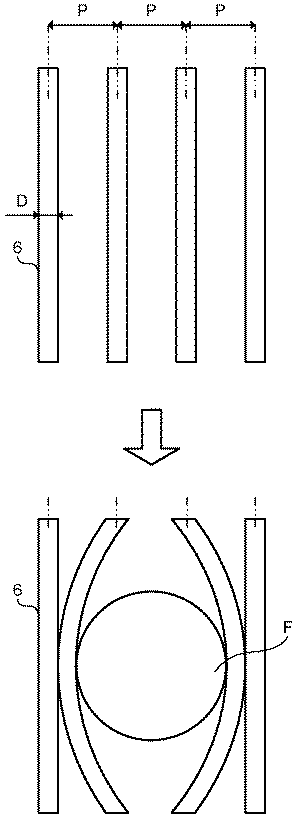

前記半導体素子と前記回路基材とを接続する金属ワイヤの配置ピッチをP、前記金属ワイヤの直径をDとしたとき、前記封止樹脂材料は前記固形状異物の最大径が3P−3D未満となるように微粉化されていることを特徴とする半導体装置の製造方法。 - 請求項3または請求項4記載の半導体装置の製造方法において、

前記封止樹脂材料は造粒されており、前記封止樹脂材料の造粒粉は前記固形状異物の最大径を超える一次粒子を含まないことを特徴とする半導体装置の製造方法。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008227884A JP5086945B2 (ja) | 2008-09-05 | 2008-09-05 | 半導体装置の製造方法 |

| US12/553,217 US8859341B2 (en) | 2008-09-05 | 2009-09-03 | Manufacturing method of semiconductor device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008227884A JP5086945B2 (ja) | 2008-09-05 | 2008-09-05 | 半導体装置の製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010062404A true JP2010062404A (ja) | 2010-03-18 |

| JP5086945B2 JP5086945B2 (ja) | 2012-11-28 |

Family

ID=41799643

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008227884A Active JP5086945B2 (ja) | 2008-09-05 | 2008-09-05 | 半導体装置の製造方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US8859341B2 (ja) |

| JP (1) | JP5086945B2 (ja) |

Cited By (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2011009394A (ja) * | 2009-06-25 | 2011-01-13 | Nitto Denko Corp | 光半導体封止用樹脂タブレットの製法およびそれによって得られる光半導体封止用樹脂タブレット、並びにそれを用いた光半導体装置 |

| JP2013176875A (ja) * | 2012-02-28 | 2013-09-09 | Towa Corp | 樹脂封止用材料及びその製造方法 |

| JP2013176874A (ja) * | 2012-02-28 | 2013-09-09 | Towa Corp | 樹脂封止装置及び樹脂封止体の製造方法 |

| JP2016122712A (ja) * | 2014-12-24 | 2016-07-07 | Towa株式会社 | 樹脂成形装置及び樹脂成形方法 |

Families Citing this family (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP6282564B2 (ja) * | 2014-09-16 | 2018-02-21 | 東芝メモリ株式会社 | 半導体装置の製造方法 |

| WO2016196189A1 (en) | 2015-05-31 | 2016-12-08 | Skyworks Solutions, Inc. | Shielded module having compression overmold |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO1999008321A1 (en) * | 1997-08-07 | 1999-02-18 | Matsushita Electric Works, Ltd. | Epoxy resin sealing material for molding semiconductor chip and method for manufacturing the same |

| JP2002327044A (ja) * | 2001-05-02 | 2002-11-15 | Sumitomo Bakelite Co Ltd | 半導体封止用エポキシ樹脂組成物の製造方法、半導体封止用エポキシ樹脂組成物及び半導体装置 |

| JP2007067164A (ja) * | 2005-08-31 | 2007-03-15 | Sumitomo Bakelite Co Ltd | 半導体封止用エポキシ樹脂組成物及びその製造方法 |

Family Cites Families (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2656350B2 (ja) | 1989-05-30 | 1997-09-24 | 日東電工株式会社 | 光半導体装置およびその製法ならびにそれに用いる光半導体封止用樹脂組成物 |

| JP3037552B2 (ja) * | 1994-02-23 | 2000-04-24 | 日東電工株式会社 | 半導体封止用樹脂タブレット及び半導体封止装置とその製造方法 |

| JP3469446B2 (ja) * | 1996-11-29 | 2003-11-25 | 株式会社東芝 | 樹脂組成物およびこれを用いた樹脂封止型半導体装置の製造方法 |

| JP3489025B2 (ja) * | 2000-01-14 | 2004-01-19 | 大塚化学ホールディングス株式会社 | エポキシ樹脂組成物及びそれを用いた電子部品 |

| TW517263B (en) * | 2000-03-29 | 2003-01-11 | Nitto Denko Corp | Semiconductor device and process for producing the same, and tablet comprising epoxy resin composition |

| US6906425B2 (en) * | 2002-03-05 | 2005-06-14 | Resolution Performance Products Llc | Attachment of surface mount devices to printed circuit boards using a thermoplastic adhesive |

| JP4270969B2 (ja) | 2002-07-16 | 2009-06-03 | 長瀬産業株式会社 | 半導体装置の樹脂封止方法 |

| JP2004235530A (ja) | 2003-01-31 | 2004-08-19 | Tsukuba Seiko Co Ltd | 封止成形装置及びそれを用いた封止成形体の製造方法 |

| TW200726784A (en) * | 2003-04-07 | 2007-07-16 | Hitachi Chemical Co Ltd | Epoxy resin molding material for sealing use and semiconductor device |

| WO2005106942A1 (ja) | 2004-04-30 | 2005-11-10 | Sumitomo Bakelite Co., Ltd. | 樹脂封止型半導体パッケージ並びにその製造方法及び製造装置 |

| JP4479442B2 (ja) | 2004-09-27 | 2010-06-09 | 住友ベークライト株式会社 | 封止成形装置及びそれを用いた樹脂封止型半導体パッケージの製造方法 |

| JP5036563B2 (ja) * | 2006-01-17 | 2012-09-26 | スパンション エルエルシー | 半導体装置およびその製造方法 |

| WO2008041555A1 (en) * | 2006-10-02 | 2008-04-10 | Hitachi Chemical Co., Ltd. | Epoxy resin molding material for sealing and electronic component device |

-

2008

- 2008-09-05 JP JP2008227884A patent/JP5086945B2/ja active Active

-

2009

- 2009-09-03 US US12/553,217 patent/US8859341B2/en active Active

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO1999008321A1 (en) * | 1997-08-07 | 1999-02-18 | Matsushita Electric Works, Ltd. | Epoxy resin sealing material for molding semiconductor chip and method for manufacturing the same |

| JP2002327044A (ja) * | 2001-05-02 | 2002-11-15 | Sumitomo Bakelite Co Ltd | 半導体封止用エポキシ樹脂組成物の製造方法、半導体封止用エポキシ樹脂組成物及び半導体装置 |

| JP2007067164A (ja) * | 2005-08-31 | 2007-03-15 | Sumitomo Bakelite Co Ltd | 半導体封止用エポキシ樹脂組成物及びその製造方法 |

Cited By (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2011009394A (ja) * | 2009-06-25 | 2011-01-13 | Nitto Denko Corp | 光半導体封止用樹脂タブレットの製法およびそれによって得られる光半導体封止用樹脂タブレット、並びにそれを用いた光半導体装置 |

| JP2013176875A (ja) * | 2012-02-28 | 2013-09-09 | Towa Corp | 樹脂封止用材料及びその製造方法 |

| JP2013176874A (ja) * | 2012-02-28 | 2013-09-09 | Towa Corp | 樹脂封止装置及び樹脂封止体の製造方法 |

| TWI513049B (zh) * | 2012-02-28 | 2015-12-11 | Towa Corp | Resin sealing device and resin sealing body |

| JP2016122712A (ja) * | 2014-12-24 | 2016-07-07 | Towa株式会社 | 樹脂成形装置及び樹脂成形方法 |

| KR20170099957A (ko) * | 2014-12-24 | 2017-09-01 | 토와 가부시기가이샤 | 수지 성형 장치 및 수지 성형 방법 |

| KR102010680B1 (ko) | 2014-12-24 | 2019-10-21 | 토와 가부시기가이샤 | 수지 성형 장치 및 수지 성형 방법 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP5086945B2 (ja) | 2012-11-28 |

| US20100062572A1 (en) | 2010-03-11 |

| US8859341B2 (en) | 2014-10-14 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5086945B2 (ja) | 半導体装置の製造方法 | |

| US10163865B2 (en) | Integrated circuit package assembly | |

| US6560122B2 (en) | Chip package with molded underfill | |

| TWI484601B (zh) | Semiconductor device and method for manufacturing semiconductor device | |

| US8084301B2 (en) | Resin sheet, circuit device and method of manufacturing the same | |

| JP2000003922A (ja) | 半導体装置の製法 | |

| JP2017045995A (ja) | 電子部品装置の製造方法及び電子部品装置 | |

| TW200908243A (en) | Flip chip with interposer, and methods of making same | |

| TW201739015A (zh) | 樹脂封裝裝置及樹脂封裝方法 | |

| JP2009016714A (ja) | 半導体装置のアンダーフィルの充填方法 | |

| JP2010086993A (ja) | 樹脂シートおよびそれを用いた回路装置の製造方法 | |

| TW201316462A (zh) | 封裝件及其製法 | |

| JP2001064522A (ja) | 半導体封止用樹脂組成物 | |

| JP2000332165A (ja) | 半導体封止用樹脂組成物およびそれを用いた半導体装置 | |

| TWI692066B (zh) | 半導體密封用環氧樹脂粒狀體之製造方法、半導體密封用環氧樹脂粒狀體、半導體裝置之製造方法及半導體裝置 | |

| JP2010165748A (ja) | 電子装置 | |

| TWI485789B (zh) | 積體電路封裝以及裝配積體電路封裝之方法 | |

| JP2003197680A (ja) | 半導体装置の製造方法 | |

| TW200935527A (en) | Chip package apparatus and chip package process | |

| JP2656350B2 (ja) | 光半導体装置およびその製法ならびにそれに用いる光半導体封止用樹脂組成物 | |

| JP2011035283A (ja) | 半導体装置およびその製造方法 | |

| KR101900549B1 (ko) | 과립상 반도체 소자 봉지용 에폭시 수지 조성물 및 이를 사용하여 봉지된 반도체 소자 | |

| JP4462779B2 (ja) | 樹脂層付ウェハ、半導体装置およびそれらの製法ならびにそれらに用いられるエポキシ樹脂組成物製タブレット、エポキシ樹脂組成物製タブレットの製造方法 | |

| JP3990814B2 (ja) | 電子部品の製造方法および電子部品の製造装置 | |

| TW201913917A (zh) | 封裝結構及其製作方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20100908 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20111013 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20111018 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20111213 |

|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20111213 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120605 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120726 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20120814 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20120907 |

|

| R151 | Written notification of patent or utility model registration |

Ref document number: 5086945 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R151 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150914 Year of fee payment: 3 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |