JP2010033683A - 不揮発性半導体記憶装置 - Google Patents

不揮発性半導体記憶装置 Download PDFInfo

- Publication number

- JP2010033683A JP2010033683A JP2008197608A JP2008197608A JP2010033683A JP 2010033683 A JP2010033683 A JP 2010033683A JP 2008197608 A JP2008197608 A JP 2008197608A JP 2008197608 A JP2008197608 A JP 2008197608A JP 2010033683 A JP2010033683 A JP 2010033683A

- Authority

- JP

- Japan

- Prior art keywords

- data

- memory cell

- voltage

- write

- wiring

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C13/00—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00

- G11C13/0002—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using resistive RAM [RRAM] elements

- G11C13/0021—Auxiliary circuits

- G11C13/0069—Writing or programming circuits or methods

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C13/00—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00

- G11C13/0002—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using resistive RAM [RRAM] elements

- G11C13/0004—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using resistive RAM [RRAM] elements comprising amorphous/crystalline phase transition cells

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C13/00—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00

- G11C13/0002—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using resistive RAM [RRAM] elements

- G11C13/0007—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using resistive RAM [RRAM] elements comprising metal oxide memory material, e.g. perovskites

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C13/00—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00

- G11C13/0002—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using resistive RAM [RRAM] elements

- G11C13/0009—RRAM elements whose operation depends upon chemical change

- G11C13/0011—RRAM elements whose operation depends upon chemical change comprising conductive bridging RAM [CBRAM] or programming metallization cells [PMCs]

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C13/00—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00

- G11C13/0002—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using resistive RAM [RRAM] elements

- G11C13/0021—Auxiliary circuits

- G11C13/0061—Timing circuits or methods

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C13/00—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00

- G11C13/0002—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using resistive RAM [RRAM] elements

- G11C13/0021—Auxiliary circuits

- G11C13/0097—Erasing, e.g. resetting, circuits or methods

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C7/00—Arrangements for writing information into, or reading information out from, a digital store

- G11C7/10—Input/output [I/O] data interface arrangements, e.g. I/O data control circuits, I/O data buffers

- G11C7/1006—Data managing, e.g. manipulating data before writing or reading out, data bus switches or control circuits therefor

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C7/00—Arrangements for writing information into, or reading information out from, a digital store

- G11C7/10—Input/output [I/O] data interface arrangements, e.g. I/O data control circuits, I/O data buffers

- G11C7/1051—Data output circuits, e.g. read-out amplifiers, data output buffers, data output registers, data output level conversion circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C7/00—Arrangements for writing information into, or reading information out from, a digital store

- G11C7/10—Input/output [I/O] data interface arrangements, e.g. I/O data control circuits, I/O data buffers

- G11C7/1075—Input/output [I/O] data interface arrangements, e.g. I/O data control circuits, I/O data buffers for multiport memories each having random access ports and serial ports, e.g. video RAM

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C7/00—Arrangements for writing information into, or reading information out from, a digital store

- G11C7/22—Read-write [R-W] timing or clocking circuits; Read-write [R-W] control signal generators or management

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C8/00—Arrangements for selecting an address in a digital store

- G11C8/16—Multiple access memory array, e.g. addressing one storage element via at least two independent addressing line groups

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C13/00—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00

- G11C13/0002—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using resistive RAM [RRAM] elements

- G11C13/0021—Auxiliary circuits

- G11C13/0069—Writing or programming circuits or methods

- G11C2013/0076—Write operation performed depending on read result

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C13/00—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00

- G11C13/0002—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using resistive RAM [RRAM] elements

- G11C13/0021—Auxiliary circuits

- G11C13/0069—Writing or programming circuits or methods

- G11C2013/0078—Write using current through the cell

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C13/00—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00

- G11C13/0002—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using resistive RAM [RRAM] elements

- G11C13/0021—Auxiliary circuits

- G11C13/0069—Writing or programming circuits or methods

- G11C2013/0092—Write characterized by the shape, e.g. form, length, amplitude of the write pulse

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C2213/00—Indexing scheme relating to G11C13/00 for features not covered by this group

- G11C2213/30—Resistive cell, memory material aspects

- G11C2213/31—Material having complex metal oxide, e.g. perovskite structure

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C2213/00—Indexing scheme relating to G11C13/00 for features not covered by this group

- G11C2213/70—Resistive array aspects

- G11C2213/72—Array wherein the access device being a diode

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C2216/00—Indexing scheme relating to G11C16/00 and subgroups, for features not directly covered by these groups

- G11C2216/12—Reading and writing aspects of erasable programmable read-only memories

- G11C2216/24—Nonvolatile memory in which programming can be carried out in one memory bank or array whilst a word or sector in another bank or array is being erased simultaneously

Abstract

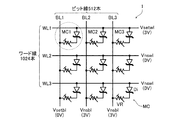

【解決手段】複数の第1の配線、これら複数の配線と交差する複数の第2の配線、並びに前記第1及び第2の配線の交差部で両配線間に接続された電気的書き換えが可能で抵抗値をデータとして不揮発に記憶する可変抵抗素子及び非オーミック素子の直列回路からなるメモリセルを有する複数のMATをマトリクス配列してなるセルアレイと、前記各MATに接続されて各MAT毎に内部のメモリセルに対して、入力データに応じたデータの書き込み又は消去を行う複数の書き込み/消去回路とを有し、複数の前記書き込み/消去回路の一部が、対応するMAT内のメモリセルに対してデータを書き込むと同時に、複数の前記書き込み/消去回路の他の一部が対応するMAT内のメモリセルに対してデータの消去を実行する。

【選択図】図7

Description

図1は、本発明の第1の実施形態に係る不揮発性メモリのブロック図である。

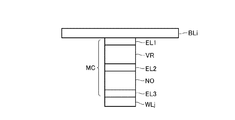

第1の実施形態における場合、選択メモリセルMCの保持データに関わらず、最低1回のデータ書き込み動作をともなった。そのため、保持データが“0”の場合であっても、さらに“0”を書き込むことになる。この場合、メモリセルMCの可変抵抗素子VRは低抵抗状態にあるため大電流が流れ、メモリセルMC等の破壊が生じかねない。

第2の実施形態では、入力データ及び選択メモリセルMCの保持データが共に“0”であった場合、データ書き込み動作が行われなかった。しかし、メモリセルMCに使用する可変抵抗素子VRの抵抗状態が低抵抗状態にある場合、障壁ポテンシャルを越えるような熱エネルギーが加わることで、より電気化学ポテンシャルが低く熱的安定状態にある高抵抗状態に遷移するという性質がある。そのため、メモリセルMCの保持データが“0”である場合であっても、高抵抗状態への遷移を抑制するため、敢えて“0”を上書きしたい場合がある。

第1〜第3の実施形態では、メモリセルMCの非オーミック素子NOにダイオードDiを使用していたため、ワード線WLからビット線BLの方向にしか電流が流れないユニポーラ動作であった。しかし、これら実施形態は、バイポーラ動作する不揮発性メモリにも応用することができる。

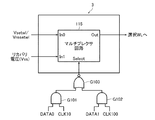

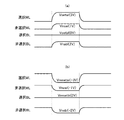

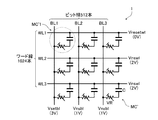

図17は、本発明の第5の実施形態に係る不揮発性メモリの“0”書き込み時(a)及び“1”書き込み時(b)の各MAT1の動作波形図である。また、図18は、同実施形態におけるMAT1の回路と“1”書き込み時の各配線に対する供給電圧を示す図である。

以上、不揮発性メモリ、特に抵抗変化型メモリについて説明したが、第1〜第3の実施形態については、他の半導体記憶装置にも適用することができる。

Claims (5)

- 複数の第1の配線、これら複数の配線と交差する複数の第2の配線、並びに前記第1及び第2の配線の交差部で両配線間に接続された電気的書き換えが可能で抵抗値をデータとして不揮発に記憶する可変抵抗素子及び非オーミック素子の直列回路からなるメモリセルを有する複数のMAT(単位セルアレイ)をマトリクス配列してなるセルアレイと、

前記各MATに接続されて各MAT毎に内部のメモリセルに対して、入力データに応じたデータの書き込み又は消去を行う複数の書き込み/消去回路と

を有し、

複数の前記書き込み/消去回路の一部が、対応するMAT内のメモリセルに対してデータを書き込むと同時に、複数の前記書き込み/消去回路の他の一部が対応するMAT内のメモリセルに対してデータの消去を実行する

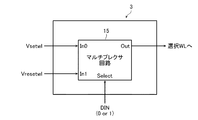

ことを特徴とする不揮発性半導体記憶装置。 - データ書き込み用の書き込み電圧とデータ消去用の消去電圧とを同時に発生させるパルスジェネレータを備え、

前記書き込み/消去回路は、前記パルスジェネレータからの書き込み電圧と消去電圧を入力しこれら電圧を入力データに応じて選択して前記第1の配線又は第2の配線に転送する選択回路を備えている

ことを特徴とする請求項1記載の不揮発性半導体記憶装置。 - 前記選択回路は、前記書き込み電圧又は消去電圧をそれらの印加時間だけ選択して前記第1の配線又は第2の配線に転送し、それ以外はリカバリ電圧を選択して前記第1の配線又は第2の配線に転送する

ことを特徴とする請求項2記載の不揮発性半導体記憶装置。 - 前記書き込み/消去回路は、選択メモリセルの保持データを読み出すと共に入力データを入力し、前記保持データが入力データと等しい場合には、対応するMATに対するアクセスを行わない

ことを特徴とする請求項1記載の不揮発性半導体記憶装置。 - 前記入力データが書き込みデータである場合に前記メモリセルに流れる電流値を制限する電流リミッタ回路を有する

ことを特徴とする請求項1記載の不揮発性半導体記憶装置。

Priority Applications (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008197608A JP5268481B2 (ja) | 2008-07-31 | 2008-07-31 | 不揮発性半導体記憶装置 |

| US12/511,443 US7957203B2 (en) | 2008-07-31 | 2009-07-29 | Nonvolatile semiconductor memory device |

| US13/099,540 US8391082B2 (en) | 2008-07-31 | 2011-05-03 | Nonvolatile semiconductor memory device |

| US13/768,359 US8842481B2 (en) | 2008-07-31 | 2013-02-15 | Nonvolatile semiconductor memory device |

| US14/479,563 US9324427B2 (en) | 2008-07-31 | 2014-09-08 | Nonvolatile semiconductor memory device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008197608A JP5268481B2 (ja) | 2008-07-31 | 2008-07-31 | 不揮発性半導体記憶装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010033683A true JP2010033683A (ja) | 2010-02-12 |

| JP5268481B2 JP5268481B2 (ja) | 2013-08-21 |

Family

ID=41608198

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008197608A Expired - Fee Related JP5268481B2 (ja) | 2008-07-31 | 2008-07-31 | 不揮発性半導体記憶装置 |

Country Status (2)

| Country | Link |

|---|---|

| US (4) | US7957203B2 (ja) |

| JP (1) | JP5268481B2 (ja) |

Cited By (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2011175723A (ja) * | 2010-02-24 | 2011-09-08 | Hynix Semiconductor Inc | 半導体メモリ装置 |

| JP2012119018A (ja) * | 2010-11-30 | 2012-06-21 | Hitachi Ltd | 半導体装置および情報処理システム |

| JP2012123892A (ja) * | 2010-12-07 | 2012-06-28 | Hynix Semiconductor Inc | 半導体メモリ装置及びその駆動方法 |

| JP2012198968A (ja) * | 2011-03-22 | 2012-10-18 | Toshiba Corp | 不揮発性半導体記憶装置 |

| JP2012212477A (ja) * | 2011-03-30 | 2012-11-01 | Toshiba Corp | 抵抗変化メモリ |

| JP2013041649A (ja) * | 2011-08-17 | 2013-02-28 | Kanazawa Univ | 抵抗変化型不揮発性記憶素子の書き込み回路 |

| JP2013077681A (ja) * | 2011-09-30 | 2013-04-25 | Nec Corp | 抵抗変化素子及びそのプログラミング方法 |

| WO2022259653A1 (ja) * | 2021-06-08 | 2022-12-15 | ソニーセミコンダクタソリューションズ株式会社 | メモリセルアレイユニット |

Families Citing this family (14)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5268481B2 (ja) * | 2008-07-31 | 2013-08-21 | 株式会社東芝 | 不揮発性半導体記憶装置 |

| JP2010044827A (ja) | 2008-08-13 | 2010-02-25 | Toshiba Corp | 不揮発性半導体記憶装置 |

| US8289749B2 (en) * | 2009-10-08 | 2012-10-16 | Sandisk 3D Llc | Soft forming reversible resistivity-switching element for bipolar switching |

| US8848430B2 (en) * | 2010-02-23 | 2014-09-30 | Sandisk 3D Llc | Step soft program for reversible resistivity-switching elements |

| JP2013004143A (ja) | 2011-06-16 | 2013-01-07 | Toshiba Corp | 不揮発性半導体記憶装置 |

| JP5802625B2 (ja) * | 2012-08-24 | 2015-10-28 | 株式会社東芝 | 不揮発性半導体記憶装置 |

| US8995166B2 (en) * | 2012-12-20 | 2015-03-31 | Intermolecular, Inc. | Multi-level memory array having resistive elements for multi-bit data storage |

| US9349450B2 (en) * | 2013-06-10 | 2016-05-24 | Micron Technology, Inc. | Memory devices and memory operational methods including single erase operation of conductive bridge memory cells |

| US9178143B2 (en) * | 2013-07-29 | 2015-11-03 | Industrial Technology Research Institute | Resistive memory structure |

| KR102151183B1 (ko) | 2014-06-30 | 2020-09-02 | 삼성전자주식회사 | 저항성 메모리 장치 및 저항성 메모리 장치의 동작방법 |

| KR102261817B1 (ko) | 2014-12-15 | 2021-06-07 | 삼성전자주식회사 | 다수의 레이어들을 포함하는 저항성 메모리 장치, 저항성 메모리 시스템 및 저항성 메모리 시스템의 동작방법 |

| KR102620562B1 (ko) * | 2016-08-04 | 2024-01-03 | 삼성전자주식회사 | 비휘발성 메모리 장치 |

| US11017838B2 (en) | 2016-08-04 | 2021-05-25 | Samsung Electronics Co., Ltd. | Nonvolatile memory devices |

| US11043497B1 (en) * | 2019-12-19 | 2021-06-22 | Micron Technology, Inc. | Integrated memory having non-ohmic devices and capacitors |

Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2005108395A (ja) * | 2003-09-12 | 2005-04-21 | Renesas Technology Corp | 記憶装置 |

| WO2008012871A1 (fr) * | 2006-07-25 | 2008-01-31 | Fujitsu Limited | Dispositif à mémoire à semi-conducteur rémanente |

| WO2008032394A1 (fr) * | 2006-09-15 | 2008-03-20 | Renesas Technology Corp. | Dispositif semi-conducteur |

| JP2008159178A (ja) * | 2006-12-25 | 2008-07-10 | Elpida Memory Inc | 半導体記憶装置とその書き込み制御方法 |

Family Cites Families (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2003152117A (ja) * | 2001-11-19 | 2003-05-23 | Mitsubishi Electric Corp | 不揮発性半導体記憶装置 |

| JP4124635B2 (ja) * | 2002-12-05 | 2008-07-23 | シャープ株式会社 | 半導体記憶装置及びメモリセルアレイの消去方法 |

| JP4537680B2 (ja) * | 2003-08-04 | 2010-09-01 | 株式会社東芝 | 不揮発性半導体記憶装置及びその動作方法、製造方法、半導体集積回路及びシステム |

| JP4189395B2 (ja) * | 2004-07-28 | 2008-12-03 | シャープ株式会社 | 不揮発性半導体記憶装置及び読み出し方法 |

| KR100610014B1 (ko) * | 2004-09-06 | 2006-08-09 | 삼성전자주식회사 | 리키지 전류 보상 가능한 반도체 메모리 장치 |

| KR101202340B1 (ko) * | 2005-01-21 | 2012-11-16 | 삼성디스플레이 주식회사 | 청색 발광 화합물 및 이를 채용한 유기 전계 발광 소자 |

| JP5268481B2 (ja) * | 2008-07-31 | 2013-08-21 | 株式会社東芝 | 不揮発性半導体記憶装置 |

| JP2010044827A (ja) | 2008-08-13 | 2010-02-25 | Toshiba Corp | 不揮発性半導体記憶装置 |

| JP4846813B2 (ja) * | 2009-03-12 | 2011-12-28 | 株式会社東芝 | 不揮発性半導体記憶装置 |

| JP2010225227A (ja) * | 2009-03-23 | 2010-10-07 | Toshiba Corp | 不揮発性半導体記憶装置 |

| WO2012001944A1 (ja) * | 2010-06-29 | 2012-01-05 | パナソニック株式会社 | 不揮発性記憶装置及びその駆動方法 |

| KR20130021199A (ko) * | 2011-08-22 | 2013-03-05 | 삼성전자주식회사 | 비휘발성 메모리 소자 및 그 구동 방법 |

| JP5655173B2 (ja) * | 2012-03-29 | 2015-01-14 | パナソニックIpマネジメント株式会社 | クロスポイント型不揮発性記憶装置とその駆動方法 |

-

2008

- 2008-07-31 JP JP2008197608A patent/JP5268481B2/ja not_active Expired - Fee Related

-

2009

- 2009-07-29 US US12/511,443 patent/US7957203B2/en active Active

-

2011

- 2011-05-03 US US13/099,540 patent/US8391082B2/en active Active

-

2013

- 2013-02-15 US US13/768,359 patent/US8842481B2/en active Active

-

2014

- 2014-09-08 US US14/479,563 patent/US9324427B2/en active Active

Patent Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2005108395A (ja) * | 2003-09-12 | 2005-04-21 | Renesas Technology Corp | 記憶装置 |

| WO2008012871A1 (fr) * | 2006-07-25 | 2008-01-31 | Fujitsu Limited | Dispositif à mémoire à semi-conducteur rémanente |

| WO2008032394A1 (fr) * | 2006-09-15 | 2008-03-20 | Renesas Technology Corp. | Dispositif semi-conducteur |

| JP2008159178A (ja) * | 2006-12-25 | 2008-07-10 | Elpida Memory Inc | 半導体記憶装置とその書き込み制御方法 |

Cited By (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2011175723A (ja) * | 2010-02-24 | 2011-09-08 | Hynix Semiconductor Inc | 半導体メモリ装置 |

| JP2012119018A (ja) * | 2010-11-30 | 2012-06-21 | Hitachi Ltd | 半導体装置および情報処理システム |

| JP2012123892A (ja) * | 2010-12-07 | 2012-06-28 | Hynix Semiconductor Inc | 半導体メモリ装置及びその駆動方法 |

| JP2012198968A (ja) * | 2011-03-22 | 2012-10-18 | Toshiba Corp | 不揮発性半導体記憶装置 |

| JP2012212477A (ja) * | 2011-03-30 | 2012-11-01 | Toshiba Corp | 抵抗変化メモリ |

| JP2013041649A (ja) * | 2011-08-17 | 2013-02-28 | Kanazawa Univ | 抵抗変化型不揮発性記憶素子の書き込み回路 |

| JP2013077681A (ja) * | 2011-09-30 | 2013-04-25 | Nec Corp | 抵抗変化素子及びそのプログラミング方法 |

| WO2022259653A1 (ja) * | 2021-06-08 | 2022-12-15 | ソニーセミコンダクタソリューションズ株式会社 | メモリセルアレイユニット |

Also Published As

| Publication number | Publication date |

|---|---|

| US9324427B2 (en) | 2016-04-26 |

| JP5268481B2 (ja) | 2013-08-21 |

| US20110205784A1 (en) | 2011-08-25 |

| US7957203B2 (en) | 2011-06-07 |

| US8391082B2 (en) | 2013-03-05 |

| US20140376302A1 (en) | 2014-12-25 |

| US20130155756A1 (en) | 2013-06-20 |

| US8842481B2 (en) | 2014-09-23 |

| US20100027318A1 (en) | 2010-02-04 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5268481B2 (ja) | 不揮発性半導体記憶装置 | |

| JP5178448B2 (ja) | 不揮発性半導体記憶装置 | |

| JP5049814B2 (ja) | 不揮発性半導体記憶装置のデータ書き込み方法 | |

| US20210343337A1 (en) | Nonvolatile semiconductor memory device | |

| JP5100554B2 (ja) | 半導体記憶装置 | |

| JP5006369B2 (ja) | 不揮発性半導体記憶装置 | |

| JP4719233B2 (ja) | 不揮発性半導体記憶装置 | |

| KR100855585B1 (ko) | 소오스 라인 공유구조를 갖는 저항성 랜덤 억세스 메모리및 그에 따른 데이터 억세스 방법 | |

| JP5049733B2 (ja) | 情報処理システム | |

| JP2010040150A (ja) | 不揮発性半導体記憶装置 | |

| JP2010225227A (ja) | 不揮発性半導体記憶装置 | |

| JP5450846B2 (ja) | 不揮発性半導体記憶装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20100915 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120821 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120828 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20121026 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20121120 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130115 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130205 |

|

| RD01 | Notification of change of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7421 Effective date: 20130221 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130228 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20130409 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20130507 |

|

| LAPS | Cancellation because of no payment of annual fees |