JP2010027205A - 半導体メモリ - Google Patents

半導体メモリ Download PDFInfo

- Publication number

- JP2010027205A JP2010027205A JP2009252416A JP2009252416A JP2010027205A JP 2010027205 A JP2010027205 A JP 2010027205A JP 2009252416 A JP2009252416 A JP 2009252416A JP 2009252416 A JP2009252416 A JP 2009252416A JP 2010027205 A JP2010027205 A JP 2010027205A

- Authority

- JP

- Japan

- Prior art keywords

- word line

- sub

- signal

- line driver

- decoding

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/21—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements

- G11C11/34—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices

- G11C11/40—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors

- G11C11/401—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming cells needing refreshing or charge regeneration, i.e. dynamic cells

- G11C11/4063—Auxiliary circuits, e.g. for addressing, decoding, driving, writing, sensing or timing

- G11C11/407—Auxiliary circuits, e.g. for addressing, decoding, driving, writing, sensing or timing for memory cells of the field-effect type

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C8/00—Arrangements for selecting an address in a digital store

- G11C8/08—Word line control circuits, e.g. drivers, boosters, pull-up circuits, pull-down circuits, precharging circuits, for word lines

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C8/00—Arrangements for selecting an address in a digital store

- G11C8/14—Word line organisation; Word line lay-out

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Computer Hardware Design (AREA)

- Dram (AREA)

- Static Random-Access Memory (AREA)

- Semiconductor Memories (AREA)

Abstract

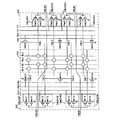

【解決手段】グローバルワードラインイネーブル信号の反転信号GWLB0,GWLB1が入力端子に連結され、プリデコーディング信号P0〜P3が電源端子に連結され、出力端子が第1〜第8サブワードラインSWL0〜SWL7にそれぞれ連結される第1〜第4サブワードライン駆動器SWLD101〜SWLD104、SWLD201’〜SWLD204’と、同一のプリデコーディング信号が入力される隣接したサブワードライン駆動器の出力端子に連結されたサブワードライン間に連結され、プリデコーディング信号により制御される複数のトランジスタNM101〜NM103,NM201〜NM203と、から第1,第2サブワードライン駆動部200,300’が構成される。

【選択図】図3

Description

200:第1サブワードライン駆動部

300,300’:第2サブワードライン駆動部

400:メモリセルアレイ

SWLD101〜SWLD104,SWLD201〜SWLD204,SWLD201’〜SWLD204’:第1〜第4サブワードライン駆動器

NM101〜NM103,NM111〜NM114,NM201〜NM203,NM211〜NM214,NM211’〜NM214’:NMOSトランジスタ

PM111〜PM114,PM211〜PM214,PM211’〜PM214’:PMOSトランジスタ

Claims (3)

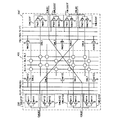

- ワードライン信号及びローデコーディング信号によって特定のサブワードラインを駆動する信号を出力する複数のサブワードライン駆動器を持つ、第1サブワードライン駆動部及び第2サブワードライン駆動部と、

前記第1及び第2サブワードライン駆動部の出力信号によって特定のメモリセルを選択して、ビットラインを介してデータを格納または出力するメモリセルアレイが一つの単位で交番して配列されているサブワードライン駆動回路とを備えた半導体メモリにおいて、

前記第1及び第2サブワードライン駆動部は、ローデコーダーによるワードライン信号を入力端子に連結して、前記ローデコーダーによるデコーディング信号を電源端子に連結し、サブワードラインに出力端子を連結するインバータで構成された複数のサブワードライン駆動器で構成され、

前記サブワードライン駆動器は、同一のデコーディング信号が入力され、他のグローバルワードラインイネーブル信号が入力される隣接した前記ワードラインドライバの出力端のサブワードラインとの間に、前記サブワードライン駆動器に入力されるデコーディング信号の反転信号によって制御されるトランジスタを含み、

前記他のグローバルワードラインイネーブル信号のラインは、前記メモリセルアレイで互いに交差して配列されることを特徴とするサブワードライン駆動回路を備えた半導体メモリ。 - 第1グローバルワードラインイネーブル信号に応答して、ローアドレス信号をプリデコーディングした複数のプリデコーディング信号または接地電位を複数のサブワードラインにそれぞれ提供するサブワードライン駆動器を含む上部サブワードライン駆動器グループと、

第2グローバルワードラインイネーブル信号に応答して、ローアドレス信号をプリデコーディングした複数のプリデコーディング信号または接地電位を複数のサブワードラインにそれぞれ提供するサブワードライン駆動器を含む下部サブワードライン駆動器グループとを含む第1サブワードライン駆動部と、

前記第2グローバルワードラインイネーブル信号に応答して、ローアドレス信号をプリデコーディングした複数のプリデコーディング信号または接地電位を複数のサブワードラインにそれぞれ提供するサブワードライン駆動器を含む上部サブワードライン駆動器グループと、

前記第1グローバルワードラインイネーブル信号に応答して、ローアドレス信号をプリデコーディングした複数のプリデコーディング信号または接地電位を複数のサブワードラインにそれぞれ提供するサブワードライン駆動器を含む下部サブワードライン駆動器グループとを含む第2サブワードライン駆動部と、

を含み、

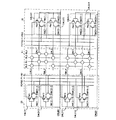

前記第1及び第2サブワードライン駆動部それぞれの上部サブワードライン駆動器グループと、下部サブワードライン駆動器グループに含まれたサブワードライン駆動器の中で、同一のデコーディング信号が入力され、互いに異なるグローバルワードラインイネーブル信号が印加される隣接したワードライン駆動器の出力端の間に連結されるトランジスタを含み、それぞれのトランジスタはそれぞれ連結されているサブワードライン駆動器に印加されるプリデコーディング信号の反転信号によって制御されることを特徴とするサブワードライン駆動回路とを備えることを特徴とする半導体メモリ。 - 第1グローバルワードラインイネーブル信号に応答して、ローアドレス信号をプリデコーディングした第1プリデコーディング信号または接地電位を第1サブワードラインに提供する第1サブワードライン駆動器と、

前記第1グローバルワードラインイネーブル信号に応答して、ローアドレス信号をプリデコーディングした第2プリデコーディング信号または接地電位を第3サブワードラインに提供する第2サブワードライン駆動器と、

第2グローバルワードラインイネーブル信号に応答して、ローアドレス信号をプリデコーディングした前記第1プリデコーディング信号または接地電位を第6サブワードラインに提供する第3サブワードライン駆動器と、

前記第2グローバルワードラインイネーブル信号に応答して、ローアドレス信号をプリデコーディングした前記第2プリデコーディング信号または接地電位を第8サブワードラインに提供する第4サブワードライン駆動器とを含む第1サブワードライン駆動部と、

前記第2グローバルワードラインイネーブル信号に応答して、ローアドレス信号をプリデコーディングした第4プリデコーディング信号または接地電位を第2サブワードラインに提供する第1サブワードライン駆動器と、

前記第2グローバルワードラインイネーブル信号に応答して、ローアドレス信号をプリデコーディングした第3プリデコーディング信号または接地電位を第4サブワードラインに提供する第2サブワードライン駆動器と、

前記第1グローバルワードラインイネーブル信号に応答して、ローアドレス信号をプリデコーディングした第4プリデコーディング信号または接地電位を第5サブワードラインに提供する第3サブワードライン駆動器と、

前記第1グローバルワードラインイネーブル信号に応答して、ローアドレス信号をプリデコーディングした第3プリデコーディング信号または接地電位を第7サブワードラインに提供する第4サブワードライン駆動器とを含む第2サブワードライン駆動部と、

前記第1サブワードライン及び接地電位の間に提供され、反転された第1プリデコーディング信号に応じて動作する第1スイッチング素子と、

前記第3及び第4サブワードラインの間に提供され、反転された第2プリデコーディング信号に応じて動作する第2スイッチング素子と、

前記第8サブワードラインに提供され、前記反転された第1プリデコーディング信号に応じて動作する第3スイッチング素子と、

前記第2サブワードライン及び接地電位の間に提供され、反転された第4プリデコーディング信号に応じて動作する第4スイッチング素子と、

前記第4及び第5サブワードラインの間に提供され、反転された第3プリデコーディング信号に応じて動作する第5スイッチング素子と、

前記第7サブワードラインに提供され、前記反転された第4プリデコーディング信号に応じて動作する第6スイッチング素子とを含む半導体メモリ。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1019980053909A KR100283907B1 (ko) | 1998-12-09 | 1998-12-09 | 서브워드라인 구동회로를 구비한 반도체 메모리 |

| KR53909/1998 | 1998-12-09 |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP11348837A Division JP2000173265A (ja) | 1998-12-09 | 1999-12-08 | 半導体メモリ |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2010027205A true JP2010027205A (ja) | 2010-02-04 |

| JP2010027205A5 JP2010027205A5 (ja) | 2010-04-22 |

| JP5159745B2 JP5159745B2 (ja) | 2013-03-13 |

Family

ID=19562008

Family Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP11348837A Pending JP2000173265A (ja) | 1998-12-09 | 1999-12-08 | 半導体メモリ |

| JP2009252416A Expired - Fee Related JP5159745B2 (ja) | 1998-12-09 | 2009-11-02 | 半導体メモリ |

Family Applications Before (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP11348837A Pending JP2000173265A (ja) | 1998-12-09 | 1999-12-08 | 半導体メモリ |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US6069838A (ja) |

| JP (2) | JP2000173265A (ja) |

| KR (1) | KR100283907B1 (ja) |

| DE (1) | DE19906200A1 (ja) |

| TW (1) | TW416059B (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2012087484A2 (en) * | 2010-12-22 | 2012-06-28 | Intel Corporation | Nand logic word line selection |

Families Citing this family (17)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6889379B1 (en) | 1998-12-31 | 2005-05-03 | Microsoft Corporation | Transporting objects between a client and a server |

| KR100303364B1 (ko) * | 1999-06-29 | 2001-11-01 | 박종섭 | 서브 워드라인 구동 회로 |

| KR100610458B1 (ko) * | 1999-06-29 | 2006-08-09 | 주식회사 하이닉스반도체 | 워드라인 부스팅신호 발생장치 |

| KR100399891B1 (ko) * | 2001-05-02 | 2003-09-29 | 주식회사 하이닉스반도체 | 서브워드라인 드라이버 |

| KR100414715B1 (ko) * | 2001-07-03 | 2004-01-13 | (주)실리콘세븐 | 메모리 어레이별 구동이 가능한 분할 워드라인 구조의반도체 메모리 장치 |

| JP4397210B2 (ja) | 2003-10-20 | 2010-01-13 | ローム株式会社 | 半導体装置 |

| KR100666173B1 (ko) * | 2005-02-04 | 2007-01-09 | 삼성전자주식회사 | 네가티브로 제어되는 서브 워드라인 구조의 반도체 메모리장치 및 이의 구동방법 |

| KR100648861B1 (ko) * | 2005-09-29 | 2006-11-24 | 주식회사 하이닉스반도체 | 워드라인 구동 장치 |

| KR100704039B1 (ko) * | 2006-01-20 | 2007-04-04 | 삼성전자주식회사 | 디코딩 신호가 워드라인 방향으로 버싱되는 반도체 메모리장치 |

| US7440354B2 (en) * | 2006-05-15 | 2008-10-21 | Freescale Semiconductor, Inc. | Memory with level shifting word line driver and method thereof |

| KR100827694B1 (ko) * | 2006-11-09 | 2008-05-07 | 삼성전자주식회사 | 반도체 메모리 장치의 서브워드라인 드라이버들의 레이아웃구조 |

| KR100934858B1 (ko) * | 2008-03-19 | 2009-12-31 | 주식회사 하이닉스반도체 | 반도체 메모리 장치 |

| KR101850536B1 (ko) | 2010-10-27 | 2018-04-19 | 삼성전자주식회사 | 반도체 메모리 장치 및 반도체 메모리 시스템 |

| KR20130068145A (ko) * | 2011-12-15 | 2013-06-25 | 에스케이하이닉스 주식회사 | 서브 워드 라인 드라이버 및 이를 포함하는 반도체 집적 회로 장치 |

| KR102109416B1 (ko) | 2013-05-21 | 2020-05-12 | 삼성전자주식회사 | 서브 워드라인 드라이버를 갖는 반도체 메모리 장치 및 그것의 구동방법 |

| US10957369B2 (en) * | 2019-08-21 | 2021-03-23 | Micron Technology, Inc. | Word line drivers sharing a transistor, and related memory devices and systems |

| KR20220060381A (ko) * | 2020-11-04 | 2022-05-11 | 삼성전자주식회사 | 집적회로 장치 |

Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0224896A (ja) * | 1988-07-13 | 1990-01-26 | Toshiba Corp | 半導体メモリ |

| JPH10241365A (ja) * | 1997-02-19 | 1998-09-11 | Lg Semicon Co Ltd | 半導体メモリ装置 |

| JPH11162173A (ja) * | 1997-11-21 | 1999-06-18 | Shijie Xianjin Jiti Electric Co Ltd | メモリー中にn型金属酸化物半導体素子を備えて第1ローカルワード線デコーダーと第2ローカルワード線デコーダーとが共用できるローカルワード線デコーダー回路の構成方法とその構造 |

| JP2000030445A (ja) * | 1998-07-08 | 2000-01-28 | Matsushita Electric Ind Co Ltd | 半導体記憶装置 |

Family Cites Families (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3666671B2 (ja) * | 1994-12-20 | 2005-06-29 | 株式会社日立製作所 | 半導体装置 |

| KR0170903B1 (ko) * | 1995-12-08 | 1999-03-30 | 김주용 | 하위 워드 라인 구동 회로 및 이를 이용한 반도체 메모리 장치 |

| JPH10326496A (ja) * | 1997-05-26 | 1998-12-08 | Hitachi Ltd | 半導体記憶装置 |

-

1998

- 1998-12-09 KR KR1019980053909A patent/KR100283907B1/ko not_active IP Right Cessation

-

1999

- 1999-01-25 TW TW088101071A patent/TW416059B/zh not_active IP Right Cessation

- 1999-02-15 DE DE19906200A patent/DE19906200A1/de not_active Withdrawn

- 1999-03-29 US US09/280,065 patent/US6069838A/en not_active Expired - Lifetime

- 1999-12-08 JP JP11348837A patent/JP2000173265A/ja active Pending

-

2009

- 2009-11-02 JP JP2009252416A patent/JP5159745B2/ja not_active Expired - Fee Related

Patent Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0224896A (ja) * | 1988-07-13 | 1990-01-26 | Toshiba Corp | 半導体メモリ |

| JPH10241365A (ja) * | 1997-02-19 | 1998-09-11 | Lg Semicon Co Ltd | 半導体メモリ装置 |

| JPH11162173A (ja) * | 1997-11-21 | 1999-06-18 | Shijie Xianjin Jiti Electric Co Ltd | メモリー中にn型金属酸化物半導体素子を備えて第1ローカルワード線デコーダーと第2ローカルワード線デコーダーとが共用できるローカルワード線デコーダー回路の構成方法とその構造 |

| JP2000030445A (ja) * | 1998-07-08 | 2000-01-28 | Matsushita Electric Ind Co Ltd | 半導体記憶装置 |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2012087484A2 (en) * | 2010-12-22 | 2012-06-28 | Intel Corporation | Nand logic word line selection |

| WO2012087484A3 (en) * | 2010-12-22 | 2013-02-14 | Intel Corporation | Nand logic word line selection |

Also Published As

| Publication number | Publication date |

|---|---|

| JP5159745B2 (ja) | 2013-03-13 |

| KR100283907B1 (ko) | 2001-03-02 |

| DE19906200A1 (de) | 2000-06-15 |

| US6069838A (en) | 2000-05-30 |

| TW416059B (en) | 2000-12-21 |

| JP2000173265A (ja) | 2000-06-23 |

| KR20000038795A (ko) | 2000-07-05 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5159745B2 (ja) | 半導体メモリ | |

| US6310806B1 (en) | Semiconductor memory device with redundant circuit | |

| KR100246311B1 (ko) | 반도체 메모리소자 | |

| US20010002176A1 (en) | Semiconductor memory device having a large band width and allowing efficient execution of redundant repair | |

| KR100898661B1 (ko) | 플래시 메모리 소자의 블럭 디코더 | |

| US6704226B2 (en) | Semiconductor memory device having row repair circuitry | |

| US6765832B1 (en) | Semiconductor memory device with word line shift configuration | |

| US20050128858A1 (en) | Negative word line driver | |

| US5319595A (en) | Semiconductor memory device with split read data bus system | |

| JP2006073110A (ja) | 半導体記憶装置 | |

| KR100280468B1 (ko) | 반도체 메모리장치의 워드라인 드라이버 | |

| EP3144937B1 (en) | Row decoder for a non-volatile memory device, having reduced area occupation | |

| KR102115638B1 (ko) | Otp 메모리 장치 | |

| JP3715805B2 (ja) | 半導体メモリ装置のワードライン駆動回路 | |

| US7035162B2 (en) | Memory devices including global row decoders and operating methods thereof | |

| KR100935590B1 (ko) | 서브 워드라인 드라이버를 포함하는 반도체 집적 회로 | |

| JP4125448B2 (ja) | 半導体メモリ装置 | |

| JP2016062625A (ja) | 半導体装置 | |

| KR100265603B1 (ko) | 계층형 워드라인 구조의 로우 디코더 | |

| KR100254473B1 (ko) | 로오 디코더 회로 | |

| KR100399975B1 (ko) | 포지티브 챠지 펌핑 전압 스위칭 회로 및 그를 이용한플래쉬 메모리의 로우 디코더 회로 | |

| KR20020013418A (ko) | 메모리 매트릭스의 워드라인용 전자 드라이버 회로 및메모리 장치 | |

| JPS59225615A (ja) | ゲ−トアレイ内のram構成方法 | |

| KR100321655B1 (ko) | 간략한 구조의 디코더를 갖는 메모리 디바이스 | |

| JP3846277B2 (ja) | 半導体記憶装置及び電子機器 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20091127 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100304 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120112 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120117 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20120417 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20120420 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120424 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20121113 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20121211 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20151221 Year of fee payment: 3 |

|

| LAPS | Cancellation because of no payment of annual fees |