JP2009260313A - Soi基板の作製方法及び半導体装置の作製方法 - Google Patents

Soi基板の作製方法及び半導体装置の作製方法 Download PDFInfo

- Publication number

- JP2009260313A JP2009260313A JP2009069508A JP2009069508A JP2009260313A JP 2009260313 A JP2009260313 A JP 2009260313A JP 2009069508 A JP2009069508 A JP 2009069508A JP 2009069508 A JP2009069508 A JP 2009069508A JP 2009260313 A JP2009260313 A JP 2009260313A

- Authority

- JP

- Japan

- Prior art keywords

- single crystal

- semiconductor substrate

- crystal semiconductor

- substrate

- oxide film

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Withdrawn

Links

Images

Classifications

-

- H10P90/1916—

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

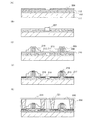

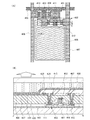

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/76—Making of isolation regions between components

- H01L21/762—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers

- H01L21/7624—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers using semiconductor on insulator [SOI] technology

- H01L21/76251—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers using semiconductor on insulator [SOI] technology using bonding techniques

- H01L21/76254—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers using semiconductor on insulator [SOI] technology using bonding techniques with separation/delamination along an ion implanted layer, e.g. Smart-cut, Unibond

-

- H10W10/181—

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Manufacturing & Machinery (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

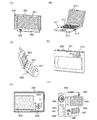

- Thin Film Transistor (AREA)

- Recrystallisation Techniques (AREA)

- Pressure Welding/Diffusion-Bonding (AREA)

- Electroluminescent Light Sources (AREA)

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009069508A JP2009260313A (ja) | 2008-03-26 | 2009-03-23 | Soi基板の作製方法及び半導体装置の作製方法 |

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008079509 | 2008-03-26 | ||

| JP2009069508A JP2009260313A (ja) | 2008-03-26 | 2009-03-23 | Soi基板の作製方法及び半導体装置の作製方法 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2014099380A Division JP2014179643A (ja) | 2008-03-26 | 2014-05-13 | 半導体装置の作製方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2009260313A true JP2009260313A (ja) | 2009-11-05 |

| JP2009260313A5 JP2009260313A5 (enExample) | 2012-04-12 |

Family

ID=41117876

Family Applications (3)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2009069508A Withdrawn JP2009260313A (ja) | 2008-03-26 | 2009-03-23 | Soi基板の作製方法及び半導体装置の作製方法 |

| JP2014099380A Withdrawn JP2014179643A (ja) | 2008-03-26 | 2014-05-13 | 半導体装置の作製方法 |

| JP2016024294A Expired - Fee Related JP6154926B2 (ja) | 2008-03-26 | 2016-02-12 | Soi基板の作製方法 |

Family Applications After (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2014099380A Withdrawn JP2014179643A (ja) | 2008-03-26 | 2014-05-13 | 半導体装置の作製方法 |

| JP2016024294A Expired - Fee Related JP6154926B2 (ja) | 2008-03-26 | 2016-02-12 | Soi基板の作製方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US9633892B2 (enExample) |

| JP (3) | JP2009260313A (enExample) |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2012199762A (ja) * | 2011-03-22 | 2012-10-18 | Murata Mfg Co Ltd | 圧電デバイスの製造方法 |

| KR20210156817A (ko) * | 2018-11-30 | 2021-12-27 | 타이완 세미콘덕터 매뉴팩쳐링 컴퍼니 리미티드 | 무금속 soi 웨이퍼의 제조 방법 |

| JP2022148013A (ja) * | 2021-03-24 | 2022-10-06 | 株式会社東京精密 | シリコンウエハの表面改質方法 |

Families Citing this family (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2009260315A (ja) * | 2008-03-26 | 2009-11-05 | Semiconductor Energy Lab Co Ltd | Soi基板の作製方法及び半導体装置の作製方法 |

| JP5654206B2 (ja) * | 2008-03-26 | 2015-01-14 | 株式会社半導体エネルギー研究所 | Soi基板の作製方法及び該soi基板を用いた半導体装置 |

| US9190294B2 (en) * | 2012-08-23 | 2015-11-17 | Michael Xiaoxuan Yang | Methods and apparatus for separating a substrate |

| CN106409650B (zh) * | 2015-08-03 | 2019-01-29 | 沈阳硅基科技有限公司 | 一种硅片直接键合方法 |

| DE102016112139B3 (de) * | 2016-07-01 | 2018-01-04 | Infineon Technologies Ag | Verfahren zum Reduzieren einer Verunreinigungskonzentration in einem Halbleiterkörper |

| US11232976B2 (en) | 2017-07-20 | 2022-01-25 | National Research Council Of Canada | Treating a silicon on insulator wafer in preparation for manufacturing an atomistic electronic device interfaced with a CMOS electronic device |

Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS5638828A (en) * | 1979-09-07 | 1981-04-14 | Sony Corp | Manufacture of semiconductor device |

| JPS56103425A (en) * | 1980-01-21 | 1981-08-18 | Nippon Telegr & Teleph Corp <Ntt> | Improving method for semiconductor substrate |

| JPH0254532A (ja) * | 1988-08-17 | 1990-02-23 | Sony Corp | Soi基板の製造方法 |

| JPH0456223A (ja) * | 1990-06-25 | 1992-02-24 | Matsushita Electron Corp | シリコン酸化膜の形成方法および薄膜形成装置 |

| JP2000036583A (ja) * | 1998-05-15 | 2000-02-02 | Canon Inc | 半導体基板、半導体薄膜の作製方法および多層構造体 |

| JP2000077287A (ja) * | 1998-08-26 | 2000-03-14 | Nissin Electric Co Ltd | 結晶薄膜基板の製造方法 |

| WO2007142852A2 (en) * | 2006-05-31 | 2007-12-13 | Corning Incorporated | Producing soi structure using ion shower |

Family Cites Families (35)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US3929529A (en) * | 1974-12-09 | 1975-12-30 | Ibm | Method for gettering contaminants in monocrystalline silicon |

| US4405864A (en) * | 1981-09-08 | 1983-09-20 | Rca Corporation | Ion implanter end processing station |

| FR2681472B1 (fr) | 1991-09-18 | 1993-10-29 | Commissariat Energie Atomique | Procede de fabrication de films minces de materiau semiconducteur. |

| JPH05326897A (ja) | 1992-05-19 | 1993-12-10 | Rohm Co Ltd | Soi基板の製法 |

| TW299897U (en) * | 1993-11-05 | 1997-03-01 | Semiconductor Energy Lab | A semiconductor integrated circuit |

| JP3528880B2 (ja) | 1995-05-24 | 2004-05-24 | 三菱住友シリコン株式会社 | Soi基板の製造方法 |

| JPH09186306A (ja) | 1996-01-08 | 1997-07-15 | Mitsubishi Materials Corp | Soi基板の製造方法 |

| US6534380B1 (en) * | 1997-07-18 | 2003-03-18 | Denso Corporation | Semiconductor substrate and method of manufacturing the same |

| JPH11191617A (ja) * | 1997-12-26 | 1999-07-13 | Mitsubishi Materials Silicon Corp | Soi基板の製造方法 |

| FR2777115B1 (fr) * | 1998-04-07 | 2001-07-13 | Commissariat Energie Atomique | Procede de traitement de substrats semi-conducteurs et structures obtenues par ce procede |

| JPH11307747A (ja) * | 1998-04-17 | 1999-11-05 | Nec Corp | Soi基板およびその製造方法 |

| JP2000012864A (ja) * | 1998-06-22 | 2000-01-14 | Semiconductor Energy Lab Co Ltd | 半導体装置の作製方法 |

| US6271101B1 (en) * | 1998-07-29 | 2001-08-07 | Semiconductor Energy Laboratory Co., Ltd. | Process for production of SOI substrate and process for production of semiconductor device |

| JP4476390B2 (ja) * | 1998-09-04 | 2010-06-09 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| JP2000124092A (ja) * | 1998-10-16 | 2000-04-28 | Shin Etsu Handotai Co Ltd | 水素イオン注入剥離法によってsoiウエーハを製造する方法およびこの方法で製造されたsoiウエーハ |

| JP2000349266A (ja) * | 1999-03-26 | 2000-12-15 | Canon Inc | 半導体部材の製造方法、半導体基体の利用方法、半導体部材の製造システム、半導体部材の生産管理方法及び堆積膜形成装置の利用方法 |

| JP4379943B2 (ja) | 1999-04-07 | 2009-12-09 | 株式会社デンソー | 半導体基板の製造方法および半導体基板製造装置 |

| US7183177B2 (en) * | 2000-08-11 | 2007-02-27 | Applied Materials, Inc. | Silicon-on-insulator wafer transfer method using surface activation plasma immersion ion implantation for wafer-to-wafer adhesion enhancement |

| JP4794810B2 (ja) * | 2003-03-20 | 2011-10-19 | シャープ株式会社 | 半導体装置の製造方法 |

| US7625808B2 (en) | 2003-09-01 | 2009-12-01 | Sumco Corporation | Method for manufacturing bonded wafer |

| JP5110772B2 (ja) | 2004-02-03 | 2012-12-26 | 株式会社半導体エネルギー研究所 | 半導体薄膜層を有する基板の製造方法 |

| US7560361B2 (en) * | 2004-08-12 | 2009-07-14 | International Business Machines Corporation | Method of forming gate stack for semiconductor electronic device |

| WO2006029651A1 (en) | 2004-09-16 | 2006-03-23 | S.O.I.Tec Silicon On Insulator Technologies | Method of manufacturing a silicon dioxide layer |

| JP2006303201A (ja) * | 2005-04-21 | 2006-11-02 | Sumco Corp | Soi基板の製造方法 |

| EP1760798B1 (en) | 2005-08-31 | 2012-01-11 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and manufacturing method thereof |

| JP5177976B2 (ja) | 2005-08-31 | 2013-04-10 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| CN101278398B (zh) | 2005-09-30 | 2010-09-29 | 株式会社半导体能源研究所 | 半导体器件的制造方法 |

| JP5063066B2 (ja) | 2005-09-30 | 2012-10-31 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| CN101281912B (zh) * | 2007-04-03 | 2013-01-23 | 株式会社半导体能源研究所 | Soi衬底及其制造方法以及半导体装置 |

| EP2140480A4 (en) * | 2007-04-20 | 2015-04-22 | Semiconductor Energy Lab | METHOD FOR PRODUCING AN SOI SUBSTRATE AND SEMICONDUCTOR ARRANGEMENT |

| KR101440930B1 (ko) * | 2007-04-20 | 2014-09-15 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | Soi 기판의 제작방법 |

| CN101669193B (zh) * | 2007-04-27 | 2012-02-15 | 株式会社半导体能源研究所 | Soi衬底及其制造方法和半导体器件 |

| EP1993127B1 (en) * | 2007-05-18 | 2013-04-24 | Semiconductor Energy Laboratory Co., Ltd. | Manufacturing method of SOI substrate |

| US7772054B2 (en) * | 2007-06-15 | 2010-08-10 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing semiconductor device |

| JP5277571B2 (ja) * | 2007-06-18 | 2013-08-28 | セイコーエプソン株式会社 | ノズル基板の製造方法及び液滴吐出ヘッドの製造方法 |

-

2009

- 2009-03-23 JP JP2009069508A patent/JP2009260313A/ja not_active Withdrawn

- 2009-03-25 US US12/410,643 patent/US9633892B2/en not_active Expired - Fee Related

-

2014

- 2014-05-13 JP JP2014099380A patent/JP2014179643A/ja not_active Withdrawn

-

2016

- 2016-02-12 JP JP2016024294A patent/JP6154926B2/ja not_active Expired - Fee Related

Patent Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS5638828A (en) * | 1979-09-07 | 1981-04-14 | Sony Corp | Manufacture of semiconductor device |

| JPS56103425A (en) * | 1980-01-21 | 1981-08-18 | Nippon Telegr & Teleph Corp <Ntt> | Improving method for semiconductor substrate |

| JPH0254532A (ja) * | 1988-08-17 | 1990-02-23 | Sony Corp | Soi基板の製造方法 |

| JPH0456223A (ja) * | 1990-06-25 | 1992-02-24 | Matsushita Electron Corp | シリコン酸化膜の形成方法および薄膜形成装置 |

| JP2000036583A (ja) * | 1998-05-15 | 2000-02-02 | Canon Inc | 半導体基板、半導体薄膜の作製方法および多層構造体 |

| JP2000077287A (ja) * | 1998-08-26 | 2000-03-14 | Nissin Electric Co Ltd | 結晶薄膜基板の製造方法 |

| WO2007142852A2 (en) * | 2006-05-31 | 2007-12-13 | Corning Incorporated | Producing soi structure using ion shower |

Cited By (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2012199762A (ja) * | 2011-03-22 | 2012-10-18 | Murata Mfg Co Ltd | 圧電デバイスの製造方法 |

| KR20210156817A (ko) * | 2018-11-30 | 2021-12-27 | 타이완 세미콘덕터 매뉴팩쳐링 컴퍼니 리미티드 | 무금속 soi 웨이퍼의 제조 방법 |

| KR102407399B1 (ko) | 2018-11-30 | 2022-06-10 | 타이완 세미콘덕터 매뉴팩쳐링 컴퍼니 리미티드 | 무금속 soi 웨이퍼의 제조 방법 |

| JP2022148013A (ja) * | 2021-03-24 | 2022-10-06 | 株式会社東京精密 | シリコンウエハの表面改質方法 |

| JP7596191B2 (ja) | 2021-03-24 | 2024-12-09 | 株式会社東京精密 | シリコンウエハの表面改質方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| US9633892B2 (en) | 2017-04-25 |

| JP2014179643A (ja) | 2014-09-25 |

| JP2016119490A (ja) | 2016-06-30 |

| JP6154926B2 (ja) | 2017-06-28 |

| US20090246936A1 (en) | 2009-10-01 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5654206B2 (ja) | Soi基板の作製方法及び該soi基板を用いた半導体装置 | |

| JP6154926B2 (ja) | Soi基板の作製方法 | |

| US8021958B2 (en) | Method for manufacturing SOI substrate and method for manufacturing semiconductor device | |

| JP5490393B2 (ja) | 半導体基板の製造方法 | |

| JP5917595B2 (ja) | Soi基板の作製方法 | |

| CN101562153B (zh) | 半导体装置及半导体装置的制造方法 | |

| JP5548395B2 (ja) | Soi基板の作製方法 | |

| JP5568260B2 (ja) | Soi基板の作製方法 | |

| TWI494974B (zh) | Soi基板的製造方法 | |

| JP2009212503A (ja) | Soi基板の作製方法 | |

| JP2010109353A (ja) | Soi基板の作製方法 | |

| JP2010114431A (ja) | Soi基板の作製方法 | |

| CN101714519B (zh) | 半导体装置的制造方法 | |

| JP5666794B2 (ja) | Soi基板の作製方法 | |

| JP5667767B2 (ja) | Soi基板の作製方法 | |

| US20100173472A1 (en) | Method for manufacturing soi substrate and method for manufacturing semiconductor device | |

| JP5580010B2 (ja) | 半導体装置の作製方法 | |

| JP2010153811A (ja) | 半導体装置の作製方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120228 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20120228 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20131114 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20131119 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20131211 |

|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20131211 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20140430 |

|

| A761 | Written withdrawal of application |

Free format text: JAPANESE INTERMEDIATE CODE: A761 Effective date: 20140514 |