JP2005294981A - 位相同期回路 - Google Patents

位相同期回路 Download PDFInfo

- Publication number

- JP2005294981A JP2005294981A JP2004103762A JP2004103762A JP2005294981A JP 2005294981 A JP2005294981 A JP 2005294981A JP 2004103762 A JP2004103762 A JP 2004103762A JP 2004103762 A JP2004103762 A JP 2004103762A JP 2005294981 A JP2005294981 A JP 2005294981A

- Authority

- JP

- Japan

- Prior art keywords

- circuit

- phase

- gain

- signal

- output

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Landscapes

- Synchronizing For Television (AREA)

- Stabilization Of Oscillater, Synchronisation, Frequency Synthesizers (AREA)

Abstract

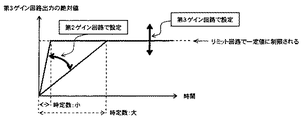

【解決手段】積分回路123の前に設けた第2ゲイン回路122により、積分回路123での積分時定数を小さくすることが出来、外部基準信号と発振回路(VCO)14との位相が一致するまでの時間を短縮することができる。また、第2ゲイン回路122のゲイン値を外部で設定出来るようにした第2ゲイン設定回路127により、この位相制御の速度を希望する値に任意に設定することが出来る。

【選択図】図1

Description

2 TVチューナ

3 複合映像信号を出力するVTR等の映像再生機器

4 切り替え器

11、272、372、41、51 位相検出回路

12、273、373、42、52 フィルタ回路

121、2731、3731、421、521 第1ゲイン回路

122、2732、3732、425、522 第2ゲイン回路

123、2733、3733、423、523 積分回路

124、2734、3734、424、524 リミット回路

125、2735、3735、525 第3ゲイン回路

126、2736、3736、426、526 第1加算回路

528 判定回路

127、2737、3737、527 第2ゲイン設定回路

13、274、374、43、53 第2加算回路

14、375、44、54 発振回路(VCO)

275 発振回路(デジタルVCO)

20 クロック回路

21 AD変換回路

22 サンプル周波数変換回路

23、33 同期分離回路

24、34 YC分離回路

25、35 ACC回路

26、36 色復調回路

27、37 バーストロック回路

271、371 色副搬送波検出回路

28、38 映像信号処理回路

29、39 映像信号表示装置

Claims (6)

- 外部信号に位相同期した信号を作り出す位相同期システムにおける定常的な位相偏差であるオフセットを無くするための位相同期回路であって、外部から入力した信号の位相を検出する位相検出回路と、位相検出回路からの出力にゲインをかける第1ゲイン回路と、位相検出回路からの出力にゲインをかけるもう一つのゲイン回路である第2ゲイン回路と、第2ゲイン回路の出力を積分する積分回路と、積分回路の出力をある一定値で制限するリミット回路と、リミット回路の出力にゲインをかける第3ゲイン回路と、第1ゲイン回路の出力と第3ゲイン回路の出力を加算する第1加算回路と、第1加算回路からの出力にある固定値を加算する第2加算回路と、第2加算回路からの出力で決まる周波数の信号を出力する発振回路(VCO)とを備え、第1ゲイン回路及び、第3ゲイン回路で、位相同期ループが安定に動作するように設定し、第2ゲイン回路の設定で積分回路の収束を速めることにより、位相同期ループの安定を保持したまま高速な位相制御ができるようにしたことを特徴とする位相同期回路。

- 前記位相同期回路において、積分器の前に配置した第2ゲイン回路にかける係数を外部から設定できる第2ゲイン設定回路を設けて、位相制御の速度を外部から任意に設定できるようにしたことを特徴とする請求項1に記載の位相同期回路。

- 前記位相同期回路のVCOからの出力を複合映像信号の色復調処理をするための搬送波に使用することを特徴とする請求項1及び2に記載の位相同期回路。

- 前記位相同期回路において、位相検出回路から出力される位相誤差の値に応じて第2ゲイン回路のゲインを変えるようにしたことを特徴とする請求項1及び2に記載の位相同期回路。

- 前記位相同期回路を用いた色復調回路において、入力した複合映像信号がTV信号である場合、受信波の電界強度に応じて第2ゲイン回路のゲインを変えるようにしたことで、安定性を保持したまま強電界での高速な色同期と弱電界での色同期の安定化が出来ることを特徴とする請求項1及び2に記載の位相同期回路。

- 前記位相同期回路を用いた色復調回路において、入力した複合映像信号が、TV信号のような色副搬送波周波数が正確な信号である場合と、VTR信号等の色副搬送波周波数が正確でない可能性がある信号である場合とで、第2ゲイン回路のゲインを変えるようにしたことで、安定性を保持したまま高速な色同期が出来ることを特徴とする請求項1及び2に記載の位相同期回路。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004103762A JP2005294981A (ja) | 2004-03-31 | 2004-03-31 | 位相同期回路 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004103762A JP2005294981A (ja) | 2004-03-31 | 2004-03-31 | 位相同期回路 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2005294981A true JP2005294981A (ja) | 2005-10-20 |

Family

ID=35327468

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004103762A Pending JP2005294981A (ja) | 2004-03-31 | 2004-03-31 | 位相同期回路 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2005294981A (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2009027581A (ja) * | 2007-07-23 | 2009-02-05 | Renesas Technology Corp | 半導体集積回路 |

Citations (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS62253224A (ja) * | 1986-01-14 | 1987-11-05 | Toshiba Corp | 位相同期回路 |

| JPH02148985A (ja) * | 1988-06-02 | 1990-06-07 | Philips Gloeilampenfab:Nv | ビデオ信号処理回路 |

| JPH04365267A (ja) * | 1991-06-13 | 1992-12-17 | Mitsubishi Electric Corp | 時定数可変型afc回路 |

| JPH05129946A (ja) * | 1991-11-08 | 1993-05-25 | Sony Corp | Pll回路 |

| JP2547563B2 (ja) * | 1986-03-28 | 1996-10-23 | アールシーエー トムソン ライセンシング コーポレーシヨン | 安定化装置 |

| JPH0974499A (ja) * | 1995-06-13 | 1997-03-18 | Texas Instr Inc <Ti> | トラッキングフィルターおよびフィルターを使用した信号処理の方法 |

| JPH10200400A (ja) * | 1997-01-13 | 1998-07-31 | Hitachi Ltd | 位相同期回路 |

| JP2001168712A (ja) * | 1999-12-13 | 2001-06-22 | Matsushita Electric Ind Co Ltd | クロック抽出回路 |

| JP2002111491A (ja) * | 2000-09-27 | 2002-04-12 | Ricoh Co Ltd | 位相同期回路 |

| JP2002152041A (ja) * | 2000-11-08 | 2002-05-24 | Nec Corp | フィードバック制御回路及びpll回路 |

| JP3323824B2 (ja) * | 1999-02-22 | 2002-09-09 | 松下電器産業株式会社 | クロック生成回路 |

-

2004

- 2004-03-31 JP JP2004103762A patent/JP2005294981A/ja active Pending

Patent Citations (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS62253224A (ja) * | 1986-01-14 | 1987-11-05 | Toshiba Corp | 位相同期回路 |

| JP2547563B2 (ja) * | 1986-03-28 | 1996-10-23 | アールシーエー トムソン ライセンシング コーポレーシヨン | 安定化装置 |

| JPH02148985A (ja) * | 1988-06-02 | 1990-06-07 | Philips Gloeilampenfab:Nv | ビデオ信号処理回路 |

| JPH04365267A (ja) * | 1991-06-13 | 1992-12-17 | Mitsubishi Electric Corp | 時定数可変型afc回路 |

| JPH05129946A (ja) * | 1991-11-08 | 1993-05-25 | Sony Corp | Pll回路 |

| JPH0974499A (ja) * | 1995-06-13 | 1997-03-18 | Texas Instr Inc <Ti> | トラッキングフィルターおよびフィルターを使用した信号処理の方法 |

| JPH10200400A (ja) * | 1997-01-13 | 1998-07-31 | Hitachi Ltd | 位相同期回路 |

| JP3323824B2 (ja) * | 1999-02-22 | 2002-09-09 | 松下電器産業株式会社 | クロック生成回路 |

| JP2001168712A (ja) * | 1999-12-13 | 2001-06-22 | Matsushita Electric Ind Co Ltd | クロック抽出回路 |

| JP2002111491A (ja) * | 2000-09-27 | 2002-04-12 | Ricoh Co Ltd | 位相同期回路 |

| JP2002152041A (ja) * | 2000-11-08 | 2002-05-24 | Nec Corp | フィードバック制御回路及びpll回路 |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2009027581A (ja) * | 2007-07-23 | 2009-02-05 | Renesas Technology Corp | 半導体集積回路 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US4933767A (en) | Video intermediate frequency signal processing circuit | |

| JP2005294981A (ja) | 位相同期回路 | |

| JPH09182100A (ja) | Pll回路 | |

| JPH02180473A (ja) | キード型同期検波回路 | |

| JPH0846433A (ja) | ビデオ信号復調回路 | |

| JPH11150735A (ja) | 信号発生回路 | |

| JPS59202736A (ja) | 位相同期回路 | |

| JP2007181046A (ja) | 受信回路、受信装置および受信方法 | |

| JP2001156627A (ja) | 位相検出装置、及び位相検出方法 | |

| JPS5930388A (ja) | 多方式カラ−テレビジヨン受像機 | |

| JP2001169302A (ja) | 色信号処理回路 | |

| JP2641290B2 (ja) | クロック発生装置 | |

| JPH0715216Y2 (ja) | Pll選局装置 | |

| JPH0865152A (ja) | 位相同期ループ回路 | |

| JPH0486079A (ja) | 映像処理装置 | |

| JPS6378676A (ja) | 水平偏向回路 | |

| JPH04189034A (ja) | Afcループ併用位相同期ループ補捉回路 | |

| JPH0638116A (ja) | 位相同期ループ回路 | |

| JPH04192885A (ja) | テレビジョン受像機の水平同期回路 | |

| JPS61202503A (ja) | 位相ロツクドル−プ回路を用いた同期検波装置 | |

| JPH05207496A (ja) | 色副搬送波周波数の判別回路 | |

| JPH02202178A (ja) | テレビジョン信号用同期抽出回路 | |

| JPH04100412A (ja) | 位相同期ループ回路 | |

| JPH09233367A (ja) | フィルタ自動調整回路 | |

| JPH04348616A (ja) | 位相同期ループ回路 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20070116 |

|

| RD01 | Notification of change of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7421 Effective date: 20070214 |

|

| RD01 | Notification of change of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7421 Effective date: 20091120 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100223 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100326 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100817 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100916 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20101026 |