CN101320695A - 带穿通电极的基板的制造方法 - Google Patents

带穿通电极的基板的制造方法 Download PDFInfo

- Publication number

- CN101320695A CN101320695A CNA2008101086822A CN200810108682A CN101320695A CN 101320695 A CN101320695 A CN 101320695A CN A2008101086822 A CNA2008101086822 A CN A2008101086822A CN 200810108682 A CN200810108682 A CN 200810108682A CN 101320695 A CN101320695 A CN 101320695A

- Authority

- CN

- China

- Prior art keywords

- electrode

- substrate

- band

- supporting bracket

- opening portion

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76898—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics formed through a semiconductor substrate

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/02—Apparatus or processes for manufacturing printed circuits in which the conductive material is applied to the surface of the insulating support and is thereafter removed from such areas of the surface which are not intended for current conducting or shielding

- H05K3/06—Apparatus or processes for manufacturing printed circuits in which the conductive material is applied to the surface of the insulating support and is thereafter removed from such areas of the surface which are not intended for current conducting or shielding the conductive material being removed chemically or electrolytically, e.g. by photo-etch process

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/48—Manufacture or treatment of parts, e.g. containers, prior to assembly of the devices, using processes not provided for in a single one of the subgroups H01L21/06 - H01L21/326

- H01L21/4814—Conductive parts

- H01L21/4846—Leads on or in insulating or insulated substrates, e.g. metallisation

- H01L21/486—Via connections through the substrate with or without pins

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/40—Forming printed elements for providing electric connections to or between printed circuits

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/40—Forming printed elements for providing electric connections to or between printed circuits

- H05K3/4038—Through-connections; Vertical interconnect access [VIA] connections

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/40—Forming printed elements for providing electric connections to or between printed circuits

- H05K3/42—Plated through-holes or plated via connections

- H05K3/423—Plated through-holes or plated via connections characterised by electroplating method

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/46—Manufacturing multilayer circuits

- H05K3/4602—Manufacturing multilayer circuits characterized by a special circuit board as base or central core whereon additional circuit layers are built or additional circuit boards are laminated

- H05K3/4605—Manufacturing multilayer circuits characterized by a special circuit board as base or central core whereon additional circuit layers are built or additional circuit boards are laminated made from inorganic insulating material

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/12—Mountings, e.g. non-detachable insulating substrates

- H01L23/14—Mountings, e.g. non-detachable insulating substrates characterised by the material or its electrical properties

- H01L23/147—Semiconductor insulating substrates

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/498—Leads, i.e. metallisations or lead-frames on insulating substrates, e.g. chip carriers

- H01L23/49833—Leads, i.e. metallisations or lead-frames on insulating substrates, e.g. chip carriers the chip support structure consisting of a plurality of insulating substrates

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/0002—Not covered by any one of groups H01L24/00, H01L24/00 and H01L2224/00

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/151—Die mounting substrate

- H01L2924/153—Connection portion

- H01L2924/1531—Connection portion the connection portion being formed only on the surface of the substrate opposite to the die mounting surface

- H01L2924/15311—Connection portion the connection portion being formed only on the surface of the substrate opposite to the die mounting surface being a ball array, e.g. BGA

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/02—Details

- H05K1/03—Use of materials for the substrate

- H05K1/0306—Inorganic insulating substrates, e.g. ceramic, glass

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/09—Shape and layout

- H05K2201/09209—Shape and layout details of conductors

- H05K2201/09654—Shape and layout details of conductors covering at least two types of conductors provided for in H05K2201/09218 - H05K2201/095

- H05K2201/0979—Redundant conductors or connections, i.e. more than one current path between two points

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2203/00—Indexing scheme relating to apparatus or processes for manufacturing printed circuits covered by H05K3/00

- H05K2203/03—Metal processing

- H05K2203/0376—Etching temporary metallic carrier substrate

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2203/00—Indexing scheme relating to apparatus or processes for manufacturing printed circuits covered by H05K3/00

- H05K2203/06—Lamination

- H05K2203/063—Lamination of preperforated insulating layer

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2203/00—Indexing scheme relating to apparatus or processes for manufacturing printed circuits covered by H05K3/00

- H05K2203/07—Treatments involving liquids, e.g. plating, rinsing

- H05K2203/0703—Plating

- H05K2203/0733—Method for plating stud vias, i.e. massive vias formed by plating the bottom of a hole without plating on the walls

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/10—Apparatus or processes for manufacturing printed circuits in which conductive material is applied to the insulating support in such a manner as to form the desired conductive pattern

- H05K3/20—Apparatus or processes for manufacturing printed circuits in which conductive material is applied to the insulating support in such a manner as to form the desired conductive pattern by affixing prefabricated conductor pattern

- H05K3/205—Apparatus or processes for manufacturing printed circuits in which conductive material is applied to the insulating support in such a manner as to form the desired conductive pattern by affixing prefabricated conductor pattern using a pattern electroplated or electroformed on a metallic carrier

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/46—Manufacturing multilayer circuits

- H05K3/4644—Manufacturing multilayer circuits by building the multilayer layer by layer, i.e. build-up multilayer circuits

- H05K3/4647—Manufacturing multilayer circuits by building the multilayer layer by layer, i.e. build-up multilayer circuits by applying an insulating layer around previously made via studs

Abstract

本发明公开了一种带穿通电极的基板的制造方法,所述基板包括具有通孔的基板和接收在通孔中的穿通电极,所述方法包括:穿通电极形成步骤,其用于在支撑板上形成穿通电极;基板形成步骤,其用于形成基板;穿通电极接收步骤,其用于将基板堆叠在所述支撑板(45)上并且将所述穿通电极接收在所述通孔内;树脂填充步骤,其用于利用树脂填充在所述穿通电极的侧表面与所述基板(11)的通孔的内壁之间的间隙;以及支撑板去除步骤,其用于在树脂填充步骤之后去除所述支撑板。

Description

技术领域

本发明涉及带穿通电极的基板的制造方法,具体地说,本发明涉及包括贯穿基板延伸的穿通电极的带穿通电极的基板的制造方法。

背景技术

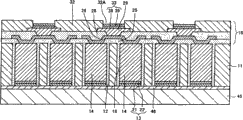

如图1所示的带穿通电极的基板200已经用作将半导体芯片与例如母板等安装基板电连接的插入物。

图1是现有技术的带穿通电极的基板的剖视图。

参考图1,现有技术的带穿通电极的基板200具有基板201、绝缘膜202和穿通电极203。基板201呈板形,并且在基板201中形成通孔205。可以使用例如硅基板作为基板201。绝缘膜202布置成覆盖基板201的上表面201A和基板201的暴露于通孔205的部分的表面。可以使用例如通过CVD方法制成的氧化膜作为绝缘膜202。

穿通电极203布置在上面形成有绝缘膜202的通孔205中。穿通电极203具有种晶层207和镀Cu膜208。种晶层207布置成覆盖形成在通孔205上的绝缘膜202。种晶层207是用于通过电解电镀法形成镀Cu膜208的馈电层。可以使用例如通过金属CVD方法制成的Cu层作为种晶层207。镀Cu膜208布置成填充上面形成有绝缘膜202和种晶层207的通孔205。

按照上述方式构造的穿通电极203的一端与半导体芯片(未示出)连接,另一端与例如母板等安装基板(未示出)连接。

图2至图12是示出现有技术的带穿通电极的基板的制造步骤的视图。在图2至图12中,使用相同的附图标记表示与现有技术的带穿通电极的基板200相同的部件。

首先,在图2所示的步骤中,制备用作前述基板201的基材的基板211。使用比基板201更厚的基板作为基板211。可以使用例如硅基板作为基板211。

接下来,在图3所示的步骤中,在基板211的上表面211A上形成具有多个开口部分212A的抗蚀膜212。开口部分212A使基板211的上表面211A的与通孔205的形成区域相对应的部分露出。

然后,在图4所示的步骤中,通过使用抗蚀膜212作为掩模的非等向性蚀刻,在基板211中形成开口部分214。通过在下述图11所示的步骤中对基板211进行抛光,使开口部分214形成通孔205。因此,开口部分214比通孔205更深。然后,在图5所示的步骤中,去除图4所示的抗蚀膜212。

然后,在图6所示的步骤中,通过CVD方法形成绝缘膜202,使得该绝缘膜覆盖基板211的上表面211A和基板211的形成开口部分214的部分的表面。可以使用例如氧化膜作为绝缘膜202。

然后,在图7所示的步骤中,通过金属CVD方法形成种晶层207,使该种晶层覆盖绝缘膜202。可以使用例如Cu层作为种晶层207。

然后,在图8所示的步骤中,通过使用种晶层207作为馈电层的电解电镀法,在种晶层207上形成镀Cu膜208。镀Cu膜208形成为填充上面形成有绝缘膜202和种晶层207的开口部分214。此时,镀Cu膜208沿着从形成在开口部分214侧面上的种晶层207向开口部分214中心的方向生长。

然后,在图9所示的步骤中,通过CMP设备对多余的镀Cu膜208进行抛光。执行该抛光操作,直到形成在基板211的上表面211A上的绝缘膜202露出为止。然后,在图10所示的步骤中,通过粘合剂216将支撑板217粘在图9所示的结构体的上表面侧。

然后,在图11所示的步骤中,使用背面抛光设备从图10所示的基板211的下表面211B侧对基板211、绝缘膜202、种晶层207和镀Cu膜208进行抛光,并且形成具有通孔205的基板201和形成在通孔205中的穿过绝缘膜202的穿通电极203。从而,在支撑板217下面形成与带穿通电极的基板200对应的结构体。

然后,在图12所示的步骤中,去除图11所示的支撑板217和粘合剂216。从而制成了带穿通电极的基板200(例如,参见日本专利申请公开出版物No.2004-221240)。

然而,在现有技术的带穿通电极的基板200中,使用了处理成本高的CMP设备,因而存在带穿通电极的基板200的制造成本增加的问题。

此外,在现有技术的带穿通电极的基板200中,使用背面抛光设备对不同材料(具体为基板211、绝缘膜202、种晶层207和镀Cu膜208)进行抛光,因而存在穿通电极203中产生裂缝以及穿通电极203折断的问题。

此外,在现有技术的带穿通电极的基板200中,作为穿通电极203的元件之一的镀Cu膜208沿着从形成在开口部分214侧面上的种晶层207向开口部分214的中心的方向生长,因而存在易于在穿通电极203中心出现空洞的问题。

发明内容

本发明的示例性实施例提供了带穿通电极的基板的制造方法,该方法能够防止穿通电极折断,降低带穿通电极的基板的制造成本,并且还防止在穿通电极中出现空洞。

根据本发明的一个方面,提供了带穿通电极的基板的制造方法,其特征在于,所述方法包括:穿通电极形成步骤,其用于在支撑板上形成穿通电极;基板形成步骤,其用于形成具有通孔的基板;穿通电极接收步骤,其用于将基板堆叠在所述支撑板上并且将所述穿通电极接收在所述通孔内;树脂填充步骤,其用于利用树脂填充在所述穿通电极的侧表面与所述基板的通孔的内壁之间的间隙;以及支撑板去除步骤,其用于在树脂填充步骤之后去除所述支撑板。

根据本发明,通过以下方式制成带穿通电极的基板:在支撑板上形成穿通电极,随后将基板堆叠在所述支撑板上并且将所述穿通电极接收在所述通孔内,然后利用树脂填充在所述穿通电极的侧表面与所述基板的通孔的内壁之间的间隙,以及随后去除所述支撑板。因此,不需要在现有技术中所需的使用处理成本高的CMP设备或背面抛光设备进行抛光,因而可以防止穿通电极折断,并且还可以降低带穿通电极的基板的制造成本。

此外,在穿通电极形成步骤中,可以这样构造穿通电极:在所述支撑板上形成具有开口部分的抗蚀膜,然后通过电解电镀法从所述支撑板的暴露于所述开口部分的底部的顶端向开口部分的开口端沉淀电镀膜,并形成穿通电极,并且在形成穿通电极之后去除所述抗蚀膜。如此通过从所述支撑板的暴露于所述开口部分的底部的顶端向开口部分的开口端沉淀电镀膜,可以防止在穿通电极中出现空洞。

根据本发明,可以防止穿通电极折断,可以降低带穿通电极的基板的制造成本,并且还可以防止在穿通电极中出现空洞。

从下面的详细描述、附图和权利要求书中可以清楚地看出其它特征和优点。

附图说明

图1是现有技术的带穿通电极的基板的剖视图。

图2是示出现有技术的带穿通电极的基板的制造步骤的视图(第一步)。

图3是示出现有技术的带穿通电极的基板的制造步骤的视图(第二步)。

图4是示出现有技术的带穿通电极的基板的制造步骤的视图(第三步)。

图5是示出现有技术的带穿通电极的基板的制造步骤的视图(第四步)。

图6是示出现有技术的带穿通电极的基板的制造步骤的视图(第五步)。

图7是示出现有技术的带穿通电极的基板的制造步骤的视图(第六步)。

图8是示出现有技术的带穿通电极的基板的制造步骤的视图(第七步)。

图9是示出现有技术的带穿通电极的基板的制造步骤的视图(第八步)。

图10是示出现有技术的带穿通电极的基板的制造步骤的视图(第九步)。

图11是示出现有技术的带穿通电极的基板的制造步骤的视图(第十步)。

图12是示出现有技术的带穿通电极的基板的制造步骤的视图(第十一步)。

图13是根据本发明第一实施例的带穿通电极的基板的剖视图。

图14是示出根据本发明第一实施例的带穿通电极的基板的制造步骤的视图(第一步)。

图15是示出根据本发明第一实施例的带穿通电极的基板的制造步骤的视图(第二步)。

图16是示出根据本发明第一实施例的带穿通电极的基板的制造步骤的视图(第三步)。

图17是示出根据本发明第一实施例的带穿通电极的基板的制造步骤的视图(第四步)。

图18是示出根据本发明第一实施例的带穿通电极的基板的制造步骤的视图(第五步)。

图19是示出根据本发明第一实施例的带穿通电极的基板的制造步骤的视图(第六步)。

图20是示出根据本发明第一实施例的带穿通电极的基板的制造步骤的视图(第七步)。

图21是示出根据本发明第一实施例的带穿通电极的基板的制造步骤的视图(第八步)。

图22是示出根据本发明第一实施例的带穿通电极的基板的制造步骤的视图(第九步)。

图23是示出根据本发明第一实施例的带穿通电极的基板的制造步骤的视图(第十步)。

图24是示出根据本发明第一实施例的带穿通电极的基板的制造步骤的视图(第十一步)。

图25是示出根据本发明第一实施例的带穿通电极的基板的制造步骤的视图(第十二步)。

图26是示出根据本发明第一实施例的带穿通电极的基板的制造步骤的视图(第十三步)。

图27是示出根据本发明第一实施例的带穿通电极的基板的制造步骤的视图(第十四步)。

图28是示出根据本发明第一实施例的带穿通电极的基板的制造步骤的视图(第十五步)。

图29是示出根据本发明第一实施例的带穿通电极的基板的制造步骤的视图(第十六步)。

图30是根据本发明第二实施例的带穿通电极的基板的剖视图。

图31是根据本发明第三实施例的带穿通电极的基板的剖视图。

具体实施方式

接下来,将基于附图描述本发明的实施例。

(第一实施例)

图13是根据本发明第一实施例的带穿通电极的基板的剖视图。

参考图13,本实施例的带穿通电极的基板10具有基板11、树脂12、防扩散膜13、穿通电极14、积层结构体16(配线层)以及外部连接端子17。

基板11呈板形,并且具有多个通孔18。通孔18的直径R1可以设置为比穿通电极14的直径R2大例如20μm或更多。可以使用例如硅基板或石英玻璃基板作为基板11。基板11的厚度M1设置为大致等于穿通电极14的长度L1加上防扩散膜13的厚度所得到的值。在本实施例中,以使用硅基板作为基板11的情况作为实例进行下面的描述。

布置树脂12,使该树脂填充形成在穿通电极14和防扩散膜13的侧面与基板11的与穿通电极14和防扩散膜13的侧面相对的部分(也就是通孔18的内壁)之间的间隙。树脂12使基板11与防扩散膜13和穿通电极14绝缘。可以使用例如环氧树脂作为树脂12。

防扩散膜13构造成具有Au层21和层叠在Au层21上的Ni层22。防扩散膜13布置在多个通孔18内,使得Au层21的下表面与基板11的下表面11B大致齐平。Au层21的厚度可以设置为例如0.1μm。此外,Ni层22的厚度可以设置为例如2μm。防扩散膜13是用于防止穿通电极14所含的Cu扩散到外部连接端子17内的薄膜。

穿通电极14穿过树脂12并布置在通孔18内。穿通电极14的下端与Ni层22接触。因此,穿通电极14与防扩散膜13电连接。穿通电极14的上表面14A与基板11的上表面11A大致齐平。穿通电极14的直径R2可以设置为例如20μm-150μm。此外,穿通电极14的长度L1可以设置为例如50μm-300μm。可以使用例如Cu作为穿通电极14的材料。

积层结构体16具有树脂层25和28、配线图案26和29、阻焊层32以及防扩散膜33。

树脂层25布置成覆盖穿通电极14的上表面14A的一部分、树脂12的上表面和基板11的上表面11A。树脂层25具有开口部分35,以便露出穿通电极14的上表面14A的一部分。可以使用例如环氧树脂作为树脂层25的材料。

配线图案26布置在树脂层25的上表面25A和开口部分35上,以便例如使两个相邻穿通电极14电连接。可以使用例如Cu作为配线图案26的材料。

树脂层28布置成覆盖配线图案26的一部分和树脂层25的上表面25A。树脂层28具有开口部分37,以便露出配线图案26的设置在树脂层25的上表面25A上的部分的上表面。可以使用例如环氧树脂作为树脂层28的材料。

配线图案29布置成在填充开口部分37的同时从开口部分37延伸到树脂层28的上表面28A。配线图案29与配线图案26电连接。可以使用例如Cu作为配线图案29的材料。配线图案29具有形成防扩散膜33的防扩散膜形成区域。

阻焊层32布置成覆盖树脂层28的上表面28A和配线图案29的一部分。阻焊层32具有开口部分32A,以便露出配线图案29的防扩散膜形成区域。

防扩散膜33布置在配线图案29的暴露于开口部分32A的部分上。防扩散膜33构造成使Ni层38和Au层39顺序地层叠在配线图案29上。Ni层38的厚度可以设置为例如2μm。此外,Au层39的厚度可以设置为例如0.1μm。在防扩散膜33上安装电子元件(例如,半导体芯片)。防扩散膜33是用于安装电子元件的焊盘。

通过布置按照上述方式构造的积层结构体16,就可以通过调节配线图案29的布线并将防扩散膜33布置在任意位置来加宽电子元件安装位置的选择范围。

外部连接端子17布置在Au层21的下表面21A侧。外部连接端子17通过防扩散膜13与穿通电极14电连接。外部连接端子17是连接在例如母板等安装基板(未示出)上的端子。可以使用例如焊料凸点作为外部连接端子17。

图14-图29是示出根据本发明第一实施例的带穿通电极的基板的制造步骤的视图。在图14-图29中,用相同的附图标记表示与第一实施例的带穿通电极的基板10相同的部件。

首先,在图14所示的步骤中,制备呈板形的支撑板45。可以使用硅基板或金属板(例如,Cu板)作为支撑板45。在本实施例中,以使用硅基板作为支撑板45的情况作为实例进行下面的描述。在使用硅基板作为支撑板45的情况下,支撑板45的厚度M2可以设置为例如0.4mm-0.8mm。

接下来,在图15所示的步骤中,形成种晶层46,使该种晶层覆盖支撑板45的上表面45A。可以使用例如Cu层作为种晶层46。当使用Cu层作为种晶层46时,可以通过例如溅射法形成Cu层。另外,当使用金属板作为支撑板45时,金属板可以起到种晶层的作用,因而不需要形成种晶层46。

然后,在图16所示的步骤中,在种晶层46上形成具有多个开口部分48A的抗蚀膜48。开口部分48A的直径大致等于上述穿通电极14的直径R2(见图13)。此外,开口部分48A形成为使种晶层46的上表面露出。

然后,在图17所示的步骤中,通过以下方式形成防扩散膜13:通过使用种晶层46作为馈电层的电解电镀法,在种晶层46的暴露于开口部分48A的部分上顺序沉淀并生长Au层21和Ni层22。

然后,在图18所示的步骤中,通过以下方式形成由电镀膜制成的穿通电极14:通过使用种晶层46作为馈电层的电解电镀法,在Ni层22上沉淀并生长电镀膜(穿通电极形成步骤)。此时,电镀膜从Ni层22的顶端向开口部分48A的开口端(开口部分48A的上端)沉淀并生长。

虽然在现有技术中难以防止出现空洞,但是,通过电解电镀法从Ni层22的顶端向开口部分48A的开口端(开口部分48A的上端)沉淀并生长电镀膜,就可以防止在穿通电极14内部出现空洞。

此外,在穿通电极14的该形成方法中,可以形成穿通电极14,而不用如现有技术的带穿通电极的基板200的制造方法所述,使用较高处理成本的CMP设备对形成穿通电极203的基材(种晶层207和镀Cu层208)进行抛光(见图9),或者使用背面抛光设备对形成穿通电极203的基材(钟晶层207和镀Cu层208)和基板211进行抛光(见图11)。因此,可以防止穿通电极14折断,并且还可以降低带穿通电极的基板10的制造成本。

穿通电极14的直径R2可以设置为例如20μm-150μm。此外,穿通电极14的长度L1可以设置为例如50μm-300μm。

然后,在图19所示的步骤中,去除图18所示的抗蚀膜48。从而可以获得柱形的穿通电极14。然后,在图20所示的步骤中,形成具有多个通孔18的基板11(基板形成步骤)。可以通过例如对基板11进行非等向性蚀刻形成多个通孔18。通孔18形成为其直径R1比穿通电极14的直径R2大例如20μm或更多。可以使用例如硅基板或石英玻璃基板作为基板11。在本实施例中,以硅基板为例。基板11的厚度M1设置为大致等于穿通电极14的长度L1加上防扩散膜13的厚度所得到的值。因此,在下述图21所示的步骤中,穿通电极14的上表面14A与基板11的上表面11A大致齐平。另外,穿通电极14的上表面14A可以相对基板11的上表面11A稍微突出或凹陷。

然后,在图21所示的步骤中,将图20所示的基板11堆叠在图19所示的结构体上,并且将穿通电极14接收在基板11的通孔18内,使得可以在基板11与穿通电极14之间形成间隙(即,可以在通孔18的内壁与穿通电极14的侧表面之间形成间隙)(穿通电极接收步骤)。此时,通过例如夹子等一些夹具将基板11与图19所示的结构体临时固定,使得基板11相对于图19所示的结构体的相对位置不会移位。

然后,在图22所示的步骤中,形成树脂12,使该树脂填充通孔18的内壁与穿通电极14的侧表面之间的间隙并且还覆盖图21所示结构体的上表面(树脂填充步骤)。具体地说,例如通过在粘贴薄膜环氧树脂以便覆盖图21所示结构体的上表面之后,软化环氧树脂来形成树脂12。或者,例如通过利用打印法施加液体环氧树脂并随后固化该环氧树脂来形成树脂12。

此外,在图22所示步骤中形成的树脂12中,通过在下述图23所示的步骤中形成开口部分35,使树脂12的用于覆盖图21所示结构体的上表面的部分形成树脂层25(见图13)的基材,该树脂层是上述积层结构体16的元件之一。

通过在穿通电极14的侧表面与基板11的与穿通电极14的侧表面相对的部分之间形成的间隙中填充树脂12,并同时形成作为积层结构体16的元件之一的树脂层25的基材(树脂12的用于覆盖图21所示结构体的上表面的部分),可以简化带穿通电极的基板10的制造步骤。此外,树脂12可以取代通过现有技术的CVD方法制成的氧化膜(绝缘膜),并且可以降低成本和简化步骤。

然后,在图23所示的步骤中,在树脂12的用于覆盖图21所示结构体的上表面的部分(见图22)中形成用于露出穿通电极14的部分上表面14A的开口部分35。因而,形成了具有多个开口部分35的树脂层25。可以通过例如激光加工形成开口部分35。

然后,在图24所示的步骤中,在图23所示结构体的上表面侧形成用于使两个相邻穿通电极14电连接的配线图案26。具体地说,可以通过例如半加成法形成配线图案26。在使用半加成法的情况下,可以使用例如镀Cu膜作为配线图案26。

然后,在图25所示的步骤中,通过例如半加成法等已知技术在图24所示结构体上顺序地形成树脂层28和配线图案29,其中树脂层28具有用于露出配线图案26的一部分的开口部分37,配线图案29布置成填充开口部分37并且还从开口部分37延伸到树脂层28的上表面28A。可以使用例如环氧树脂作为树脂层28。此外,可以使用例如镀Cu膜作为配线图案29。

然后,在图26所示的步骤中,在树脂层28上形成阻焊层32,该阻焊层具有用于露出配线图案29的上表面的一部分的开口部分32A。

然后,在图27所示的步骤中,通过以下方式形成防扩散膜33:通过使用种晶层46作为馈电层的电解电镀法,在配线图案29的暴露于开口部分32A的部分上顺序地沉淀并生长Ni层38和Au层39。因而,形成了积层结构体16。图22-图27所示的步骤为与积层结构体形成步骤对应的步骤。

通过在其中形成有穿通电极14的基板11上如此形成积层结构体16,就可以通过调节配线图案29的布线并将防扩散膜33布置在任意位置来加宽电子元件的安装位置的选择范围。另外,可以使用非电解电镀法形成Ni层38和Au层39。

然后,在图28所示的步骤中,顺序地去除支撑层45和种晶层46。具体地说,例如,通过蚀刻法去除支撑层45和种晶层46。

然后,在图29所示的步骤中,在Au层21的下表面21A侧形成外部连接端子17。从而制造成出带穿通电极的基板10。可以使用例如焊料凸点作为外部连接端子17。

根据本实施例的带穿通电极的基板的制造方法,可以通过以下方式形成穿通电极14:在支撑板45上形成穿通电极14;将其中形成有通孔18的基板11堆叠在支撑板45上;将穿通电极14接收在通孔18内;然后利用树脂填充在穿通电极14的侧表面与基板11的与穿通电极14的侧表面相对的部分之间形成的间隙,而不用如现有技术的带穿通电极的基板200的制造方法所述,使用CMP设备对形成穿通电极203的基材(种晶层207和镀Cu层208)进行抛光(见图9),或者使用背面抛光设备对形成穿通电极203的基材(种晶层207和镀Cu层208)和基板211进行抛光(见图11)。因此,可以防止穿通电极14折断,并且还可以降低带穿通电极的基板10的制造成本。

此外,通过半加成法形成穿通电极14,因而可以防止在穿通电极14内部出现空洞。

虽然上面已经详细描述了本发明的优选实施例,但是本发明不限于这种具体实施例,而是可以在权利要求书所述的本发明要旨的范围内进行各种修改和变化。

例如,在基板11上可以布置有与穿通电极14电连接的元件(例如,无源元件、有源元件或半导体电路),并且在如此构造的带穿通电极的基板中也可以获得与本实施例的带穿通电极的基板10的制造方法相类似的效果。

另外,使用支撑板和基板进行上述制造步骤,然后去掉该支撑板和基板,从而可以制造出多个带穿通电极的基板10,其中所述支撑板形成多个带穿通电极的基板10的其中形成有多个穿通电极14的元件的一部分,所述基板形成多个带穿通电极的基板10的其中形成有多个通孔18的元件的一部分。

(第二实施例)

图30是根据本发明第二实施例的带穿通电极的基板的剖视图。在图30中,与第一实施例的带穿通电极的基板10相同的部件具有相同的附图标记。

参考图30,以类似于带穿通电极的基板10的方式构造第二实施例的带穿通电极的基板60,不同之处在于:从第一实施例的带穿通电极的基板10的元件中去除树脂层28、配线图案26和29以及阻焊层32,并且防扩散膜33布置在穿通电极14的暴露于在树脂层25中形成的开口部分35的部分上。

可以通过以下方式制造上述构造的第二实施例的带穿通电极的基板60:在第一实施例中描述的图23所示的步骤之后,在穿通电极14的上表面14A上形成防扩散膜33,然后将支撑板45和种晶层46去除。

本实施例的带穿通电极的基板的制造方法可以获得与第一实施例的带穿通电极的基板10的制造方法相类似的效果。

(第三实施例)

图31是根据本发明第三实施例的带穿通电极的基板的剖视图。在图31中,与第一实施例的带穿通电极的基板10相同的部件具有相同的附图标记。

参考图31,通过与带穿通电极的基板10相类似的方式构造第三实施例的带穿通电极的基板70,不同之处在于:布置积层结构体72以代替布置在第一实施例的带穿通电极的基板10中的积层结构体16,还布置导体层71。

导体层71布置为覆盖通孔18的内壁以及基板11的上表面11A和下表面11B。通过将导体层71布置在通孔18的内壁上,可以以同轴结构形成穿通电极14。导体层71是通过与下述配线图案73连接以用作电源电位或接地电位的层。可以由例如通过非电解电镀法形成的镀Cu膜和电解电镀法形成的镀Cu膜构造导体层71。

积层结构体72布置在其中形成有导体层71的基板11上。积层结构体72具有与积层结构体16相类似的构造,不同之处在于:在第一实施例描述的积层结构体16的构造中还布置有配线图案73。例如,配线图案73布置在形成于基板11的上表面11A上的导体层71和开口部分35上,使得两个相邻穿通电极14与导体层71电连接。可以使用例如Cu作为配线图案73的材料。

可以通过与第一实施例的带穿通电极的基板10相类似的技术制造上述构造的第三实施例的带穿通电极的基板70,并且可以获得与第一实施例的带穿通电极的基板10的制造方法相类似的效果。

本发明可以应用于包括贯穿基板延伸的穿通电极的带穿通电极的基板的制造方法。

尽管已经结合有限数量的实施例描述了本发明,但是,从本公开内容中受益的所属领域的技术人员将会认识到,在不偏离在此所披露的本发明的保护范围的情况下,可以设计出其它的实施例。因此,本发明的保护范围应当仅由所附权利要求书限定。

本申请要求2007年6月4日向日本特许厅提交的日本专利申请No.2007-148182的优先权。该日本专利申请No.2007-148182通过引用的方式整体并入本文。

Claims (4)

1.一种带穿通电极的基板的制造方法,包括:

穿通电极形成步骤,其用于在支撑板上形成穿通电极;

基板形成步骤,其用于形成具有通孔的基板;

穿通电极接收步骤,其用于将基板堆叠在所述支撑板上并且将所述穿通电极接收在所述通孔内;

树脂填充步骤,其用于利用树脂填充在所述穿通电极的侧表面与所述基板的通孔的内壁之间的间隙;以及

支撑板去除步骤,其用于在树脂填充步骤之后去除所述支撑板。

2.如权利要求1所述的带穿通电极的基板的制造方法,其中,

在穿通电极形成步骤中,穿通电极是通过电解电镀法形成的。

3.如权利要求2所述的带穿通电极的基板的制造方法,其中,

在穿通电极形成步骤中,在所述支撑板上形成具有开口部分的抗蚀膜,随后通过电解电镀法从所述支撑板的暴露于所述开口部分底部的顶端向开口部分的开口端沉淀电镀膜,并形成穿通电极,并且在形成穿通电极之后去除所述抗蚀膜。

4.如权利要求1-3中任一项所述的带穿通电极的基板的制造方法,还包括:

在树脂填充步骤与支撑板去除步骤之间的配线层形成步骤,其用于在基板的与布置有所述支撑板的一侧相对的一侧的表面上形成配线层,所述配线层与所述穿通电极电连接。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007148182 | 2007-06-04 | ||

| JP2007148182A JP5193503B2 (ja) | 2007-06-04 | 2007-06-04 | 貫通電極付き基板及びその製造方法 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| CN101320695A true CN101320695A (zh) | 2008-12-10 |

Family

ID=39731510

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CNA2008101086822A Pending CN101320695A (zh) | 2007-06-04 | 2008-06-04 | 带穿通电极的基板的制造方法 |

Country Status (6)

| Country | Link |

|---|---|

| US (1) | US8349733B2 (zh) |

| EP (1) | EP2001274A3 (zh) |

| JP (1) | JP5193503B2 (zh) |

| KR (1) | KR20080106844A (zh) |

| CN (1) | CN101320695A (zh) |

| TW (1) | TW200850096A (zh) |

Cited By (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN103299723A (zh) * | 2011-01-14 | 2013-09-11 | 贺利实公司 | 制造具有层叠到互连层堆叠的液晶聚合物焊料掩模的电子装置的方法及相关装置 |

| CN104051369A (zh) * | 2014-07-02 | 2014-09-17 | 上海朕芯微电子科技有限公司 | 一种用于2.5d封装的中间互联层及其制备方法 |

| CN108122835A (zh) * | 2017-12-12 | 2018-06-05 | 华进半导体封装先导技术研发中心有限公司 | 转接板的制造方法及其所制造的转接板 |

| CN113021172A (zh) * | 2021-03-25 | 2021-06-25 | 中国电子科技集团公司第五十四研究所 | 一种带腔ltcc基板的研磨抛光方法 |

Families Citing this family (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8288872B2 (en) * | 2008-08-05 | 2012-10-16 | Taiwan Semiconductor Manufacturing Company, Ltd. | Through silicon via layout |

| US8294240B2 (en) * | 2009-06-08 | 2012-10-23 | Qualcomm Incorporated | Through silicon via with embedded decoupling capacitor |

| KR101095373B1 (ko) * | 2010-04-22 | 2011-12-16 | 재단법인 서울테크노파크 | 장벽층을 갖는 범프를 포함하는 반도체칩 및 그 제조방법 |

| JP5547566B2 (ja) * | 2010-06-29 | 2014-07-16 | 株式会社アドバンテスト | 貫通配線基板の製造方法 |

| JP5485818B2 (ja) * | 2010-06-29 | 2014-05-07 | 株式会社アドバンテスト | 貫通配線基板および製造方法 |

| KR20120012602A (ko) * | 2010-08-02 | 2012-02-10 | 삼성전자주식회사 | 반도체 장치, 그 제조 방법 및 반도체 패키지의 제조 방법 |

| US8472207B2 (en) * | 2011-01-14 | 2013-06-25 | Harris Corporation | Electronic device having liquid crystal polymer solder mask and outer sealing layers, and associated methods |

| JP2012156327A (ja) * | 2011-01-26 | 2012-08-16 | Elpida Memory Inc | 半導体装置、及び積層型半導体装置 |

| KR101806806B1 (ko) | 2011-12-20 | 2017-12-11 | 삼성전자주식회사 | 전자 소자 탑재용 기판의 제조방법 |

| JP5878362B2 (ja) * | 2011-12-22 | 2016-03-08 | 新光電気工業株式会社 | 半導体装置、半導体パッケージ及び半導体装置の製造方法 |

| TWI475623B (zh) * | 2011-12-27 | 2015-03-01 | Ind Tech Res Inst | 堆疊式半導體結構的接合結構及其形成方法 |

| JP2016039512A (ja) | 2014-08-08 | 2016-03-22 | キヤノン株式会社 | 電極が貫通配線と繋がったデバイス、及びその製造方法 |

| US10431533B2 (en) * | 2014-10-31 | 2019-10-01 | Ati Technologies Ulc | Circuit board with constrained solder interconnect pads |

| KR102494336B1 (ko) * | 2015-10-07 | 2023-02-01 | 삼성전기주식회사 | 인쇄회로기판 및 그 제조방법 |

| JP6424297B2 (ja) * | 2016-03-25 | 2018-11-14 | 住友精密工業株式会社 | 充填方法 |

Family Cites Families (23)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH05183019A (ja) | 1991-12-27 | 1993-07-23 | Hitachi Ltd | 半導体装置およびその製造方法 |

| WO2001026147A1 (fr) * | 1999-10-04 | 2001-04-12 | Seiko Epson Corporation | Dispositif a semi-conducteur, son procede de fabrication, carte de circuit imprime et dispositif electronique |

| JP4023076B2 (ja) | 2000-07-27 | 2007-12-19 | 富士通株式会社 | 表裏導通基板及びその製造方法 |

| JP2002314244A (ja) * | 2001-04-11 | 2002-10-25 | Ngk Insulators Ltd | コア基板とその製造方法、該コア基板を用いた複層コア基板の製造方法及び多層積層基板の製造方法 |

| KR100435813B1 (ko) * | 2001-12-06 | 2004-06-12 | 삼성전자주식회사 | 금속 바를 이용하는 멀티 칩 패키지와 그 제조 방법 |

| JP4045143B2 (ja) | 2002-02-18 | 2008-02-13 | テセラ・インターコネクト・マテリアルズ,インコーポレイテッド | 配線膜間接続用部材の製造方法及び多層配線基板の製造方法 |

| JP4213478B2 (ja) | 2003-01-14 | 2009-01-21 | 株式会社ルネサステクノロジ | 半導体装置の製造方法 |

| JP4098673B2 (ja) | 2003-06-19 | 2008-06-11 | 新光電気工業株式会社 | 半導体パッケージの製造方法 |

| JP2005026313A (ja) | 2003-06-30 | 2005-01-27 | Shinko Electric Ind Co Ltd | 配線基板の製造方法 |

| JP3938921B2 (ja) * | 2003-07-30 | 2007-06-27 | Tdk株式会社 | 半導体ic内蔵モジュールの製造方法 |

| US7547975B2 (en) | 2003-07-30 | 2009-06-16 | Tdk Corporation | Module with embedded semiconductor IC and method of fabricating the module |

| JP2005072061A (ja) * | 2003-08-27 | 2005-03-17 | Ngk Spark Plug Co Ltd | 配線基板およびその製造方法 |

| JP2005072064A (ja) * | 2003-08-27 | 2005-03-17 | Ngk Spark Plug Co Ltd | 配線基板およびその製造方法 |

| JP4438389B2 (ja) * | 2003-11-14 | 2010-03-24 | カシオ計算機株式会社 | 半導体装置の製造方法 |

| JP3751625B2 (ja) * | 2004-06-29 | 2006-03-01 | 新光電気工業株式会社 | 貫通電極の製造方法 |

| JP4813035B2 (ja) | 2004-10-01 | 2011-11-09 | 新光電気工業株式会社 | 貫通電極付基板の製造方法 |

| JP3987521B2 (ja) * | 2004-11-08 | 2007-10-10 | 新光電気工業株式会社 | 基板の製造方法 |

| JP2006147873A (ja) * | 2004-11-19 | 2006-06-08 | Sharp Corp | 半導体装置の製造方法 |

| JP2006165112A (ja) * | 2004-12-03 | 2006-06-22 | Sharp Corp | 貫通電極形成方法およびそれを用いる半導体装置の製造方法、ならびに該方法によって得られる半導体装置 |

| JP2007027451A (ja) | 2005-07-19 | 2007-02-01 | Shinko Electric Ind Co Ltd | 回路基板及びその製造方法 |

| JP2007148182A (ja) | 2005-11-30 | 2007-06-14 | Ricoh Co Ltd | 現像装置及び画像形成装置 |

| US7863189B2 (en) * | 2007-01-05 | 2011-01-04 | International Business Machines Corporation | Methods for fabricating silicon carriers with conductive through-vias with low stress and low defect density |

| JP5302522B2 (ja) * | 2007-07-02 | 2013-10-02 | スパンション エルエルシー | 半導体装置及びその製造方法 |

-

2007

- 2007-06-04 JP JP2007148182A patent/JP5193503B2/ja active Active

-

2008

- 2008-06-02 KR KR1020080051603A patent/KR20080106844A/ko not_active Application Discontinuation

- 2008-06-03 TW TW097120562A patent/TW200850096A/zh unknown

- 2008-06-03 US US12/132,187 patent/US8349733B2/en active Active

- 2008-06-04 EP EP08157592A patent/EP2001274A3/en not_active Withdrawn

- 2008-06-04 CN CNA2008101086822A patent/CN101320695A/zh active Pending

Cited By (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN103299723A (zh) * | 2011-01-14 | 2013-09-11 | 贺利实公司 | 制造具有层叠到互连层堆叠的液晶聚合物焊料掩模的电子装置的方法及相关装置 |

| CN103299723B (zh) * | 2011-01-14 | 2015-11-25 | 贺利实公司 | 制造具有层叠到互连层堆叠的液晶聚合物焊料掩模的电子装置的方法及相关装置 |

| CN104051369A (zh) * | 2014-07-02 | 2014-09-17 | 上海朕芯微电子科技有限公司 | 一种用于2.5d封装的中间互联层及其制备方法 |

| CN108122835A (zh) * | 2017-12-12 | 2018-06-05 | 华进半导体封装先导技术研发中心有限公司 | 转接板的制造方法及其所制造的转接板 |

| CN113021172A (zh) * | 2021-03-25 | 2021-06-25 | 中国电子科技集团公司第五十四研究所 | 一种带腔ltcc基板的研磨抛光方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| US20080299768A1 (en) | 2008-12-04 |

| EP2001274A3 (en) | 2009-11-11 |

| JP2008300782A (ja) | 2008-12-11 |

| US8349733B2 (en) | 2013-01-08 |

| EP2001274A2 (en) | 2008-12-10 |

| KR20080106844A (ko) | 2008-12-09 |

| JP5193503B2 (ja) | 2013-05-08 |

| TW200850096A (en) | 2008-12-16 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN101320695A (zh) | 带穿通电极的基板的制造方法 | |

| US7452751B2 (en) | Semiconductor device and method of manufacturing the same | |

| CN100556246C (zh) | 配线基板的制造方法 | |

| US8324513B2 (en) | Wiring substrate and semiconductor apparatus including the wiring substrate | |

| CN101106121B (zh) | 布线基板、半导体器件及其制造方法 | |

| CN101388373B (zh) | 半导体装置及其制造方法 | |

| KR101291289B1 (ko) | 반도체 패키지 및 그 제조 방법 | |

| US20140110858A1 (en) | Embedded chip packages and methods for manufacturing an embedded chip package | |

| US20040224499A1 (en) | Semiconductor device substrate and manufacturing method thereof and semiconductor package | |

| JP2002510148A (ja) | 複数の基板層と少なくとも1つの半導体チップを有する半導体構成素子及び当該半導体構成素子を製造する方法 | |

| KR20090054390A (ko) | 반도체 장치 | |

| TW200807666A (en) | Manufacturing Method of Semiconductor Device | |

| US20020117753A1 (en) | Three dimensional packaging | |

| JP2016152260A (ja) | 電子装置 | |

| WO2012078709A2 (en) | Compliant interconnects in wafers | |

| CN102623427A (zh) | 半导体封装结构及其封装方法 | |

| CN1957465B (zh) | 半导体器件及配线基板 | |

| KR20100082551A (ko) | 인터포저 및 집적회로 칩 내장 인쇄회로기판 | |

| CN101393877A (zh) | 制造半导体器件的方法 | |

| US10354971B2 (en) | Method for producing a chip module | |

| US10643949B2 (en) | Component carrier and method for manufacturing the same | |

| US20040188812A1 (en) | Semiconductor package having angulated interconnect surfaces | |

| US7122400B2 (en) | Method of fabricating an interconnection for chip sandwich arrangements | |

| CN105009279A (zh) | 半导体器件及制造半导体器件的方法 | |

| CN104952858A (zh) | 半导体器件、半导体层叠模块构造、层叠模块构造以及它们的制造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C02 | Deemed withdrawal of patent application after publication (patent law 2001) | ||

| WD01 | Invention patent application deemed withdrawn after publication |

Open date: 20081210 |