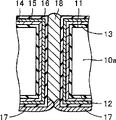

CN100505178C - 贯通基板、内插器以及贯通基板的制造方法 - Google Patents

贯通基板、内插器以及贯通基板的制造方法 Download PDFInfo

- Publication number

- CN100505178C CN100505178C CNB2005800221520A CN200580022152A CN100505178C CN 100505178 C CN100505178 C CN 100505178C CN B2005800221520 A CNB2005800221520 A CN B2005800221520A CN 200580022152 A CN200580022152 A CN 200580022152A CN 100505178 C CN100505178 C CN 100505178C

- Authority

- CN

- China

- Prior art keywords

- substrate

- conductive layer

- layer

- hole

- interposer

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

- Semiconductor Integrated Circuits (AREA)

- Printing Elements For Providing Electric Connections Between Printed Circuits (AREA)

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP199871/2004 | 2004-07-06 | ||

| JP2004199871A JP2006024653A (ja) | 2004-07-06 | 2004-07-06 | 貫通基板および貫通基板の製造方法 |

| JP199872/2004 | 2004-07-06 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN1977365A CN1977365A (zh) | 2007-06-06 |

| CN100505178C true CN100505178C (zh) | 2009-06-24 |

Family

ID=35797731

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CNB2005800221520A Expired - Fee Related CN100505178C (zh) | 2004-07-06 | 2005-07-05 | 贯通基板、内插器以及贯通基板的制造方法 |

Country Status (2)

| Country | Link |

|---|---|

| JP (1) | JP2006024653A (enExample) |

| CN (1) | CN100505178C (enExample) |

Families Citing this family (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4807272B2 (ja) * | 2007-02-05 | 2011-11-02 | パナソニック電工株式会社 | 半導体ウェハへの貫通孔配線の形成方法 |

| KR100916771B1 (ko) * | 2007-10-08 | 2009-09-14 | 성균관대학교산학협력단 | 관통형전극의 형성방법 |

| KR101052870B1 (ko) * | 2008-04-21 | 2011-07-29 | 주식회사 하이닉스반도체 | 관통 전극, 이를 갖는 회로 기판, 이를 갖는 반도체 패키지및 반도체 패키지를 갖는 적층 반도체 패키지 |

| KR101031134B1 (ko) | 2008-09-11 | 2011-04-27 | 주식회사 동부하이텍 | 반도체 소자의 컨택 및 그 제조 방법 |

| JP5246103B2 (ja) * | 2008-10-16 | 2013-07-24 | 大日本印刷株式会社 | 貫通電極基板の製造方法 |

| US8455356B2 (en) * | 2010-01-21 | 2013-06-04 | International Business Machines Corporation | Integrated void fill for through silicon via |

| JP5209075B2 (ja) | 2010-05-21 | 2013-06-12 | 有限会社 ナプラ | 電子デバイス及びその製造方法 |

| TWI449138B (zh) * | 2011-01-19 | 2014-08-11 | 旭德科技股份有限公司 | 封裝載板 |

| JP2013161910A (ja) * | 2012-02-03 | 2013-08-19 | Osaka Prefecture Univ | 半導体装置の製造方法、半導体装置、赤外線センサの製造方法および赤外線センサ |

| JP6056386B2 (ja) * | 2012-11-02 | 2017-01-11 | 凸版印刷株式会社 | 貫通電極付き配線基板及びその製造方法 |

| US9596768B2 (en) * | 2014-03-04 | 2017-03-14 | Qualcomm Incorporated | Substrate with conductive vias |

| CN105390475A (zh) * | 2015-10-20 | 2016-03-09 | 北京大学 | 一种衬底内部的电容集成结构及其制造方法 |

| US10490483B2 (en) * | 2016-03-07 | 2019-11-26 | Micron Technology, Inc. | Low capacitance through substrate via structures |

| JP2017199854A (ja) | 2016-04-28 | 2017-11-02 | Tdk株式会社 | 貫通配線基板 |

| KR102803444B1 (ko) * | 2020-01-06 | 2025-05-07 | 삼성전기주식회사 | 인쇄회로기판 |

Citations (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5003273A (en) * | 1989-12-04 | 1991-03-26 | Itt Corporation | Multilayer printed circuit board with pseudo-coaxial transmission lines |

| US5286926A (en) * | 1991-04-16 | 1994-02-15 | Ngk Spark Plug Co., Ltd. | Integrated circuit package and process for producing same |

| JP2001352017A (ja) * | 2000-06-06 | 2001-12-21 | Fujitsu Ltd | 電子装置実装基板及びその製造方法 |

| US20020017399A1 (en) * | 2000-08-11 | 2002-02-14 | Huey-Ru Chang | Coaxial via hole and process of fabricating the same |

| CN1358331A (zh) * | 1999-06-28 | 2002-07-10 | 英特尔公司 | 内插器及其制造方法 |

| CN1417856A (zh) * | 2001-11-07 | 2003-05-14 | 新光电气工业株式会社 | 半导体封装及其制造方法 |

| JP2004128006A (ja) * | 2002-09-30 | 2004-04-22 | Fujitsu Ltd | 回路基板およびその製造方法 |

| JP2004146445A (ja) * | 2002-10-22 | 2004-05-20 | Fujitsu Ltd | コネクタ基板の製造方法 |

Family Cites Families (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2002009193A (ja) * | 2000-04-18 | 2002-01-11 | Matsushita Electric Ind Co Ltd | 半導体装置 |

| US6498381B2 (en) * | 2001-02-22 | 2002-12-24 | Tru-Si Technologies, Inc. | Semiconductor structures having multiple conductive layers in an opening, and methods for fabricating same |

| JP2004119606A (ja) * | 2002-09-25 | 2004-04-15 | Canon Inc | 半導体基板の貫通孔埋め込み方法および半導体基板 |

| SG111972A1 (en) * | 2002-10-17 | 2005-06-29 | Agency Science Tech & Res | Wafer-level package for micro-electro-mechanical systems |

| JP2006019455A (ja) * | 2004-06-30 | 2006-01-19 | Nec Electronics Corp | 半導体装置およびその製造方法 |

-

2004

- 2004-07-06 JP JP2004199871A patent/JP2006024653A/ja active Pending

-

2005

- 2005-07-05 CN CNB2005800221520A patent/CN100505178C/zh not_active Expired - Fee Related

Patent Citations (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5003273A (en) * | 1989-12-04 | 1991-03-26 | Itt Corporation | Multilayer printed circuit board with pseudo-coaxial transmission lines |

| US5286926A (en) * | 1991-04-16 | 1994-02-15 | Ngk Spark Plug Co., Ltd. | Integrated circuit package and process for producing same |

| CN1358331A (zh) * | 1999-06-28 | 2002-07-10 | 英特尔公司 | 内插器及其制造方法 |

| JP2001352017A (ja) * | 2000-06-06 | 2001-12-21 | Fujitsu Ltd | 電子装置実装基板及びその製造方法 |

| US20020017399A1 (en) * | 2000-08-11 | 2002-02-14 | Huey-Ru Chang | Coaxial via hole and process of fabricating the same |

| CN1417856A (zh) * | 2001-11-07 | 2003-05-14 | 新光电气工业株式会社 | 半导体封装及其制造方法 |

| JP2004128006A (ja) * | 2002-09-30 | 2004-04-22 | Fujitsu Ltd | 回路基板およびその製造方法 |

| JP2004146445A (ja) * | 2002-10-22 | 2004-05-20 | Fujitsu Ltd | コネクタ基板の製造方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| CN1977365A (zh) | 2007-06-06 |

| JP2006024653A (ja) | 2006-01-26 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN100505178C (zh) | 贯通基板、内插器以及贯通基板的制造方法 | |

| US7767913B2 (en) | Electronic devices including conductive vias having two or more conductive elements for providing electrical communication between traces in different planes in a substrate, and accompanying methods | |

| US7924131B2 (en) | Electrical component having an inductor and a method of formation | |

| US7508079B2 (en) | Circuit substrate and method of manufacturing the same | |

| US6239485B1 (en) | Reduced cross-talk noise high density signal interposer with power and ground wrap | |

| CN101593743B (zh) | 集成电路元件 | |

| CN101455129B (zh) | 屏蔽式过孔 | |

| KR100858075B1 (ko) | 인터포저 | |

| CN101142860B (zh) | 印刷线路板 | |

| JP4912992B2 (ja) | キャパシタ内蔵基板及びその製造方法 | |

| US6750403B2 (en) | Reconfigurable multilayer printed circuit board | |

| TWI423753B (zh) | 多層佈線基板 | |

| CN101222824A (zh) | 多层基底及具有该多层基底的电子装置 | |

| CN109962046A (zh) | 半导体封装件和包括其的半导体模块 | |

| US20150282317A1 (en) | Edge contacts of circuit boards, and related apparatus and methods | |

| US9986640B2 (en) | Coil component and method of manufacturing the same | |

| JP5323435B2 (ja) | 差動伝送用多層配線基板 | |

| TWI403251B (zh) | 具有減小穿孔導體棒之高速電路化基板,製造該基板之方法及使用該基板之資料處理系統 | |

| CN103889145A (zh) | 线路板及电子总成 | |

| JP2009135147A (ja) | 配線基板及び電子素子の接続構造及び電子装置 | |

| US20130321104A1 (en) | Multilayer electronic structure with novel transmission lines | |

| JP5051836B2 (ja) | 半導体装置およびその設計方法 | |

| JP2010093018A (ja) | 配線基板 | |

| US20120178217A1 (en) | Method and apparatus for low inductive design pattern | |

| KR100856450B1 (ko) | 관통 기판의 제조 방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C14 | Grant of patent or utility model | ||

| GR01 | Patent grant | ||

| CF01 | Termination of patent right due to non-payment of annual fee |

Granted publication date: 20090624 Termination date: 20150705 |

|

| EXPY | Termination of patent right or utility model |