CN100448026C - 半导体结构及其形成方法 - Google Patents

半导体结构及其形成方法 Download PDFInfo

- Publication number

- CN100448026C CN100448026C CNB2005100998038A CN200510099803A CN100448026C CN 100448026 C CN100448026 C CN 100448026C CN B2005100998038 A CNB2005100998038 A CN B2005100998038A CN 200510099803 A CN200510099803 A CN 200510099803A CN 100448026 C CN100448026 C CN 100448026C

- Authority

- CN

- China

- Prior art keywords

- bury

- source

- regions

- buried

- area

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 60

- 238000000034 method Methods 0.000 title claims abstract description 40

- 230000004888 barrier function Effects 0.000 claims abstract description 83

- 239000000758 substrate Substances 0.000 claims description 49

- 125000006850 spacer group Chemical group 0.000 claims description 24

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 claims description 16

- 239000012212 insulator Substances 0.000 claims description 9

- 230000015572 biosynthetic process Effects 0.000 claims description 8

- 239000000377 silicon dioxide Substances 0.000 claims description 8

- 235000012239 silicon dioxide Nutrition 0.000 claims description 8

- 229910052710 silicon Inorganic materials 0.000 claims description 7

- 239000010703 silicon Substances 0.000 claims description 7

- 239000000463 material Substances 0.000 claims description 6

- 229910021420 polycrystalline silicon Inorganic materials 0.000 claims description 6

- 229920005591 polysilicon Polymers 0.000 claims description 6

- 230000008021 deposition Effects 0.000 claims description 4

- 239000000615 nonconductor Substances 0.000 claims description 3

- 238000009413 insulation Methods 0.000 claims 3

- 239000002019 doping agent Substances 0.000 abstract description 2

- 238000009792 diffusion process Methods 0.000 abstract 1

- 239000010410 layer Substances 0.000 description 28

- 239000012792 core layer Substances 0.000 description 18

- 238000004519 manufacturing process Methods 0.000 description 13

- 239000012535 impurity Substances 0.000 description 7

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical group [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 5

- 238000005530 etching Methods 0.000 description 5

- 229910021421 monocrystalline silicon Inorganic materials 0.000 description 4

- 229910052581 Si3N4 Inorganic materials 0.000 description 3

- 229910004298 SiO 2 Inorganic materials 0.000 description 3

- 150000004767 nitrides Chemical class 0.000 description 3

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 3

- NBIIXXVUZAFLBC-UHFFFAOYSA-N Phosphoric acid Chemical compound OP(O)(O)=O NBIIXXVUZAFLBC-UHFFFAOYSA-N 0.000 description 2

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 2

- 229910052787 antimony Inorganic materials 0.000 description 2

- WATWJIUSRGPENY-UHFFFAOYSA-N antimony atom Chemical compound [Sb] WATWJIUSRGPENY-UHFFFAOYSA-N 0.000 description 2

- 229910052785 arsenic Inorganic materials 0.000 description 2

- RQNWIZPPADIBDY-UHFFFAOYSA-N arsenic atom Chemical compound [As] RQNWIZPPADIBDY-UHFFFAOYSA-N 0.000 description 2

- 238000000151 deposition Methods 0.000 description 2

- 238000005468 ion implantation Methods 0.000 description 2

- 238000012986 modification Methods 0.000 description 2

- 230000004048 modification Effects 0.000 description 2

- 229910052698 phosphorus Inorganic materials 0.000 description 2

- 239000011574 phosphorus Substances 0.000 description 2

- 239000002210 silicon-based material Substances 0.000 description 2

- 239000000126 substance Substances 0.000 description 2

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 1

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 1

- GYHNNYVSQQEPJS-UHFFFAOYSA-N Gallium Chemical compound [Ga] GYHNNYVSQQEPJS-UHFFFAOYSA-N 0.000 description 1

- 230000002411 adverse Effects 0.000 description 1

- 229910000147 aluminium phosphate Inorganic materials 0.000 description 1

- 230000000903 blocking effect Effects 0.000 description 1

- 229910052796 boron Inorganic materials 0.000 description 1

- 229910001873 dinitrogen Inorganic materials 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 229910052733 gallium Inorganic materials 0.000 description 1

- 239000007943 implant Substances 0.000 description 1

- 229910052738 indium Inorganic materials 0.000 description 1

- APFVFJFRJDLVQX-UHFFFAOYSA-N indium atom Chemical compound [In] APFVFJFRJDLVQX-UHFFFAOYSA-N 0.000 description 1

- 230000003647 oxidation Effects 0.000 description 1

- 238000007254 oxidation reaction Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D62/00—Semiconductor bodies, or regions thereof, of devices having potential barriers

- H10D62/10—Shapes, relative sizes or dispositions of the regions of the semiconductor bodies; Shapes of the semiconductor bodies

- H10D62/17—Semiconductor regions connected to electrodes not carrying current to be rectified, amplified or switched, e.g. channel regions

- H10D62/213—Channel regions of field-effect devices

- H10D62/221—Channel regions of field-effect devices of FETs

- H10D62/235—Channel regions of field-effect devices of FETs of IGFETs

- H10D62/314—Channel regions of field-effect devices of FETs of IGFETs having vertical doping variations

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/01—Manufacture or treatment

- H10D30/021—Manufacture or treatment of FETs having insulated gates [IGFET]

- H10D30/027—Manufacture or treatment of FETs having insulated gates [IGFET] of lateral single-gate IGFETs

- H10D30/0275—Manufacture or treatment of FETs having insulated gates [IGFET] of lateral single-gate IGFETs forming single crystalline semiconductor source or drain regions resulting in recessed gates, e.g. forming raised source or drain regions

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/601—Insulated-gate field-effect transistors [IGFET] having lightly-doped drain or source extensions, e.g. LDD IGFETs or DDD IGFETs

- H10D30/608—Insulated-gate field-effect transistors [IGFET] having lightly-doped drain or source extensions, e.g. LDD IGFETs or DDD IGFETs having non-planar bodies, e.g. having recessed gate electrodes

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D62/00—Semiconductor bodies, or regions thereof, of devices having potential barriers

- H10D62/10—Shapes, relative sizes or dispositions of the regions of the semiconductor bodies; Shapes of the semiconductor bodies

- H10D62/113—Isolations within a component, i.e. internal isolations

- H10D62/115—Dielectric isolations, e.g. air gaps

- H10D62/116—Dielectric isolations, e.g. air gaps adjoining the input or output regions of field-effect devices, e.g. adjoining source or drain regions

Landscapes

- Insulated Gate Type Field-Effect Transistor (AREA)

- Thin Film Transistor (AREA)

- Element Separation (AREA)

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US10/711,450 US7271453B2 (en) | 2004-09-20 | 2004-09-20 | Buried biasing wells in FETS |

| US10/711,450 | 2004-09-20 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN1753188A CN1753188A (zh) | 2006-03-29 |

| CN100448026C true CN100448026C (zh) | 2008-12-31 |

Family

ID=36073039

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CNB2005100998038A Expired - Fee Related CN100448026C (zh) | 2004-09-20 | 2005-09-02 | 半导体结构及其形成方法 |

Country Status (3)

| Country | Link |

|---|---|

| US (2) | US7271453B2 (enExample) |

| JP (1) | JP5116224B2 (enExample) |

| CN (1) | CN100448026C (enExample) |

Families Citing this family (16)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7091071B2 (en) * | 2005-01-03 | 2006-08-15 | Freescale Semiconductor, Inc. | Semiconductor fabrication process including recessed source/drain regions in an SOI wafer |

| KR20090004147A (ko) * | 2007-07-06 | 2009-01-12 | 삼성전자주식회사 | 반도체 소자 및 그 형성 방법 |

| CN102254824B (zh) * | 2010-05-20 | 2013-10-02 | 中国科学院微电子研究所 | 半导体器件及其形成方法 |

| CN102479709B (zh) * | 2010-11-24 | 2015-03-11 | 中芯国际集成电路制造(北京)有限公司 | 晶体管及其制作方法 |

| CN102623337B (zh) * | 2011-01-30 | 2014-12-03 | 中芯国际集成电路制造(北京)有限公司 | 晶体管及其制作方法 |

| CN102693915B (zh) * | 2011-03-22 | 2015-02-18 | 中芯国际集成电路制造(上海)有限公司 | 一种mos晶体管的制造方法 |

| JP5915181B2 (ja) * | 2011-04-05 | 2016-05-11 | 富士通セミコンダクター株式会社 | 半導体装置およびその製造方法 |

| US8629016B1 (en) | 2011-07-26 | 2014-01-14 | Suvolta, Inc. | Multiple transistor types formed in a common epitaxial layer by differential out-diffusion from a doped underlayer |

| US9070477B1 (en) | 2012-12-12 | 2015-06-30 | Mie Fujitsu Semiconductor Limited | Bit interleaved low voltage static random access memory (SRAM) and related methods |

| WO2015042049A1 (en) | 2013-09-17 | 2015-03-26 | Wave Semiconductor, Inc. | Multi-threshold circuitry based on silicon-on-insulator technology |

| WO2015152904A1 (en) | 2014-04-01 | 2015-10-08 | Empire Technology Development Llc | Vertical transistor with flashover protection |

| US9406750B2 (en) | 2014-11-19 | 2016-08-02 | Empire Technology Development Llc | Output capacitance reduction in power transistors |

| US11245020B2 (en) * | 2017-01-04 | 2022-02-08 | International Business Machines Corporation | Gate-all-around field effect transistor having multiple threshold voltages |

| US10128347B2 (en) | 2017-01-04 | 2018-11-13 | International Business Machines Corporation | Gate-all-around field effect transistor having multiple threshold voltages |

| CN110911407B (zh) * | 2018-09-18 | 2025-03-28 | 长鑫存储技术有限公司 | 半导体器件及其形成方法 |

| CN117529102B (zh) * | 2024-01-03 | 2024-05-14 | 长鑫新桥存储技术有限公司 | 半导体结构及其制备方法 |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4862232A (en) * | 1986-09-22 | 1989-08-29 | General Motors Corporation | Transistor structure for high temperature logic circuits with insulation around source and drain regions |

| CN1407630A (zh) * | 2001-08-10 | 2003-04-02 | 三洋电机株式会社 | 半导体器件及其制造方法 |

| CN1440071A (zh) * | 2002-02-19 | 2003-09-03 | 精工电子有限公司 | 半导体器件及其制造方法 |

Family Cites Families (22)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0616559B2 (ja) * | 1985-11-18 | 1994-03-02 | 日本電気株式会社 | 半導体装置の製造方法 |

| US4885618A (en) * | 1986-03-24 | 1989-12-05 | General Motors Corporation | Insulated gate FET having a buried insulating barrier |

| JP2537936B2 (ja) * | 1986-04-23 | 1996-09-25 | エイ・ティ・アンド・ティ・コーポレーション | 半導体デバイスの製作プロセス |

| JP2817285B2 (ja) * | 1989-11-29 | 1998-10-30 | 日本電気株式会社 | 電界効果型トランジスタ |

| US5290714A (en) * | 1990-01-12 | 1994-03-01 | Hitachi, Ltd. | Method of forming semiconductor device including a CMOS structure having double-doped channel regions |

| US5250829A (en) * | 1992-01-09 | 1993-10-05 | International Business Machines Corporation | Double well substrate plate trench DRAM cell array |

| KR960008735B1 (en) * | 1993-04-29 | 1996-06-29 | Samsung Electronics Co Ltd | Mos transistor and the manufacturing method thereof |

| US6001676A (en) * | 1995-05-29 | 1999-12-14 | Matsushita Electronics Corporation | Semiconductor integrated circuit apparatus and associated fabrication |

| US5598367A (en) * | 1995-06-07 | 1997-01-28 | International Business Machines Corporation | Trench EPROM |

| US5731619A (en) * | 1996-05-22 | 1998-03-24 | International Business Machines Corporation | CMOS structure with FETS having isolated wells with merged depletions and methods of making same |

| JP3060948B2 (ja) * | 1996-06-03 | 2000-07-10 | 日本電気株式会社 | 半導体装置の製造方法 |

| KR100226794B1 (ko) * | 1996-06-10 | 1999-10-15 | 김영환 | 모스펫 제조방법 |

| US5923067A (en) * | 1997-04-04 | 1999-07-13 | International Business Machines Corporation | 3-D CMOS-on-SOI ESD structure and method |

| JPH118379A (ja) * | 1997-06-16 | 1999-01-12 | Toshiba Corp | 半導体装置及びその製造方法 |

| KR100272527B1 (ko) * | 1998-02-04 | 2000-12-01 | 김영환 | 반도체 소자 및 그 제조방법 |

| US6097242A (en) * | 1998-02-26 | 2000-08-01 | Micron Technology, Inc. | Threshold voltage compensation circuits for low voltage and low power CMOS integrated circuits |

| KR100261170B1 (ko) * | 1998-05-06 | 2000-07-01 | 김영환 | 반도체소자 및 그 제조방법 |

| DE19853268C2 (de) * | 1998-11-18 | 2002-04-11 | Infineon Technologies Ag | Feldeffektgesteuerter Transistor und Verfahren zu dessen Herstellung |

| DE19946201C1 (de) * | 1999-09-27 | 2000-12-14 | Infineon Technologies Ag | Anordnung zur Spannungspufferung bei dynamischen Speichern in CMOS-Technologie |

| JP2001203348A (ja) * | 2000-01-18 | 2001-07-27 | Sharp Corp | 半導体装置及びその製造方法 |

| US6664598B1 (en) * | 2002-09-05 | 2003-12-16 | International Business Machines Corporation | Polysilicon back-gated SOI MOSFET for dynamic threshold voltage control |

| US6867433B2 (en) * | 2003-04-30 | 2005-03-15 | Taiwan Semiconductor Manufacturing Company, Ltd. | Semiconductor-on-insulator chip incorporating strained-channel partially-depleted, fully-depleted, and multiple-gate transistors |

-

2004

- 2004-09-20 US US10/711,450 patent/US7271453B2/en not_active Expired - Fee Related

-

2005

- 2005-09-02 CN CNB2005100998038A patent/CN100448026C/zh not_active Expired - Fee Related

- 2005-09-06 JP JP2005257269A patent/JP5116224B2/ja not_active Expired - Fee Related

-

2007

- 2007-08-27 US US11/845,244 patent/US7732286B2/en not_active Expired - Fee Related

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4862232A (en) * | 1986-09-22 | 1989-08-29 | General Motors Corporation | Transistor structure for high temperature logic circuits with insulation around source and drain regions |

| CN1407630A (zh) * | 2001-08-10 | 2003-04-02 | 三洋电机株式会社 | 半导体器件及其制造方法 |

| CN1440071A (zh) * | 2002-02-19 | 2003-09-03 | 精工电子有限公司 | 半导体器件及其制造方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| US7732286B2 (en) | 2010-06-08 |

| US7271453B2 (en) | 2007-09-18 |

| US20070293010A1 (en) | 2007-12-20 |

| JP5116224B2 (ja) | 2013-01-09 |

| JP2006093694A (ja) | 2006-04-06 |

| US20060060918A1 (en) | 2006-03-23 |

| CN1753188A (zh) | 2006-03-29 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

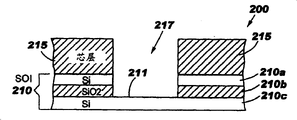

| US7732286B2 (en) | Buried biasing wells in FETs (Field Effect Transistors) | |

| CN100565878C (zh) | 半导体装置 | |

| KR100346617B1 (ko) | 반도체 소자 및 그 제조 방법 | |

| US7704808B2 (en) | Methods of forming semiconductor-on-insulating (SOI) field effect transistors with body contacts | |

| US6579750B1 (en) | Manufacturing method for fully depleted silicon on insulator semiconductor device | |

| CN102386124B (zh) | 直接接触的沟槽结构 | |

| JP3415459B2 (ja) | 半導体装置及びその製造方法 | |

| US6437404B1 (en) | Semiconductor-on-insulator transistor with recessed source and drain | |

| JPH05102296A (ja) | 集積回路において平坦化した浅いトレンチ分離を製造する方法及びそれにより製造された構成体 | |

| US5856700A (en) | Semiconductor device with doped semiconductor and dielectric trench sidewall layers | |

| US9806190B2 (en) | High voltage drain extension on thin buried oxide SOI | |

| US6987052B2 (en) | Method for making enhanced substrate contact for a semiconductor device | |

| US9385051B2 (en) | Method for the formation of a FinFET device having partially dielectric isolated fin structure | |

| US20050085026A1 (en) | Manufacturing method of semiconductor-on-insulator region structures | |

| US6326272B1 (en) | Method for forming self-aligned elevated transistor | |

| JP2004507088A (ja) | トレンチゲート半導体装置の製造方法 | |

| US7482656B2 (en) | Method and structure to form self-aligned selective-SOI | |

| US6566680B1 (en) | Semiconductor-on-insulator (SOI) tunneling junction transistor | |

| US7041561B2 (en) | Enhanced substrate contact for a semiconductor device | |

| US5895243A (en) | Semiconductor processing method of providing electrical isolation between adjacent semiconductor diffusion regions of different field effect transistors and integrated circuitry having adjacent electrically isolated field effect transistors | |

| US8816429B2 (en) | Charge balance semiconductor devices with increased mobility structures | |

| CN1328795C (zh) | 一种源漏下陷型超薄体soimos晶体管及其制作方法 | |

| KR101206628B1 (ko) | 산화물 영역 형성 방법, 반도체 구조체, 집적 회로 및mos 장치 | |

| JP5266738B2 (ja) | トレンチゲート型半導体装置の製造方法 | |

| KR100833594B1 (ko) | 모스펫 소자 및 그 제조방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C14 | Grant of patent or utility model | ||

| GR01 | Patent grant | ||

| CF01 | Termination of patent right due to non-payment of annual fee | ||

| CF01 | Termination of patent right due to non-payment of annual fee |

Granted publication date: 20081231 |