KR930008417B1 - 반도체 메모리 장치의 다중 비트 병렬 테스트방법 - Google Patents

반도체 메모리 장치의 다중 비트 병렬 테스트방법 Download PDFInfo

- Publication number

- KR930008417B1 KR930008417B1 KR1019900008924A KR900008924A KR930008417B1 KR 930008417 B1 KR930008417 B1 KR 930008417B1 KR 1019900008924 A KR1019900008924 A KR 1019900008924A KR 900008924 A KR900008924 A KR 900008924A KR 930008417 B1 KR930008417 B1 KR 930008417B1

- Authority

- KR

- South Korea

- Prior art keywords

- data

- pairs

- pair

- comparator

- input

- Prior art date

Links

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C29/00—Checking stores for correct operation ; Subsequent repair; Testing stores during standby or offline operation

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C7/00—Arrangements for writing information into, or reading information out from, a digital store

- G11C7/10—Input/output [I/O] data interface arrangements, e.g. I/O data control circuits, I/O data buffers

- G11C7/1048—Data bus control circuits, e.g. precharging, presetting, equalising

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C29/00—Checking stores for correct operation ; Subsequent repair; Testing stores during standby or offline operation

- G11C29/04—Detection or location of defective memory elements, e.g. cell constructio details, timing of test signals

- G11C29/08—Functional testing, e.g. testing during refresh, power-on self testing [POST] or distributed testing

- G11C29/12—Built-in arrangements for testing, e.g. built-in self testing [BIST] or interconnection details

- G11C29/18—Address generation devices; Devices for accessing memories, e.g. details of addressing circuits

- G11C29/26—Accessing multiple arrays

- G11C29/28—Dependent multiple arrays, e.g. multi-bit arrays

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C29/00—Checking stores for correct operation ; Subsequent repair; Testing stores during standby or offline operation

- G11C29/04—Detection or location of defective memory elements, e.g. cell constructio details, timing of test signals

- G11C29/08—Functional testing, e.g. testing during refresh, power-on self testing [POST] or distributed testing

- G11C29/12—Built-in arrangements for testing, e.g. built-in self testing [BIST] or interconnection details

- G11C29/18—Address generation devices; Devices for accessing memories, e.g. details of addressing circuits

- G11C29/30—Accessing single arrays

- G11C29/34—Accessing multiple bits simultaneously

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C29/00—Checking stores for correct operation ; Subsequent repair; Testing stores during standby or offline operation

- G11C29/04—Detection or location of defective memory elements, e.g. cell constructio details, timing of test signals

- G11C29/08—Functional testing, e.g. testing during refresh, power-on self testing [POST] or distributed testing

- G11C29/12—Built-in arrangements for testing, e.g. built-in self testing [BIST] or interconnection details

- G11C29/38—Response verification devices

Landscapes

- For Increasing The Reliability Of Semiconductor Memories (AREA)

- Tests Of Electronic Circuits (AREA)

- Dram (AREA)

- Techniques For Improving Reliability Of Storages (AREA)

Abstract

내용 없음.

Description

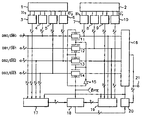

제 1 도는 종래의 방법을 보여주는 회로구성도.

제 2 도는 본 발명에 따른 방법을 보여주는 회로구성도.

제 3 도는 메모리셀블럭과 입출력선간의 연결을 보여주는 회로도.

제 4 도는 입출력선프리차아지회로도.

본 발명은 반도체메모리장치의 테스트방법에 관한 것으로, 특히 작은면적으로 정상동작에 영향을 주지않는 다중비트병렬테스트방법 관한 것이다. 반도체메모리장치는 고집적화됨에 따라 칩면적의 증가로 여러가지 제조경비가 늘어나고 있는 추세이다. 특히 집적도가 높아질수록 메모리장치의 테스트시간 및 경비는 증가된다. 테스트시간과 경비를 줄이기 위한 방법으로 직렬로 데이터를 억세스하는 방법을 사용하지 않고, 여러개의 비트를 동시에 병렬로 테스트하는 방법이 있다.

제 1 도는 종래의 병렬로 테스트를 위한 메모리장치의 구성도로서 8비트의 병렬데이터를 처리하는 경우의 실시예이다. 상기 제 1 도에서는, 두개의 메모리셀군(1) (2)으로부터 각각 내쌍의 입출력선을 통하여 데이터쌍을 입력하는 데이터감지/구동회로(3-10)의 출력이 네개의 데이터버스 쌍에 각각 연결되어 있다. 상기 데이터버스쌍들의 중앙에는 좌측의 데이터감지/구동회로(3-6)와 우측의 데이터감지/구동회로(7-10)에 각각 연결된 데이터버스쌍을 분리 또는 연결하는 네개의 전달게이트(11-14)가 위치하여 있다. 상기 전달게이트(11-14)는 엔모오수 및 피모오스트랜지스터로 구성되어 병렬테스트인에이블신호에 각 트랜지스터들의 게이트가 연결되어 있다. 또한, 상기 데이터버스쌍의 일단에는 데이터출력버퍼(도시되지 않음)와 연결된 데이터선택회로(16)가 연결되어 있으며, 각각 네개의 데이터버스쌍에 입력이 연결되어 제 2 비교기(18)로 하나의 데이터쌍을 출력하는 두개의 제 1 비교기 (17) (19)와, 상기 제 2의비교기(18)와 상기 데이터출력버퍼를 연결하는 스위칭회로(20)가 도시되어 있다.

그리고 상기 제 1 비교기(17) (19)와 데이터선택회로(16) 및 제 2 비교기(18)와 스위칭회로(20)는 상기 전달 게이트(11-15)와 마찬가지로 상기 병렬테스트인에이블 신호에 의해 제어된다. 이러한 구성에 의해 행해지는 8비트 병렬테스트방법은, 먼저 두개의 메모리셀군(1) (2)으로부터 8개의 입출력선쌍을 통하여 8개의 데이터쌍이 출력되면 데이터감지/구동회로(3-10)에 의해 감지증폭 및 드라이빙되어 데이터버스쌍으로 데이터쌍이 보내어진다. 상기 전송된 8개의 데이터쌍들은 각각 네개씩 제 1 비교기(17) (19)로 입력되어 비교되고, 상기 두개의 제 1 비교기(17) (19)는 입력된 각 네쌍의 데이터쌍을 소정의 디코딩처리하여 각각 하나의 데이터쌍을 제 2 비교기(18)로 출력한다. 그러면 상기 제 2 비교기(18)는 두개의 데이터쌍을 입력하여 하나의 데이터쌍으로 만들어 스위칭회로(20)를 통하여 데이터출력버퍼로 보낸다.

여기서 상기 병력테스트인에이블신호는 테스트모드이므로 "하이"상태에 있기 때문에, 노멀모드시에 좌우의 데이터버스쌍을 연결하는 전달게이트들(11-15)은 모두 턴오프상태에 있고, 데이터선택회로(16)도 상기 신호에 의해 동작하지 않는다. 반대로, 노멀모드인 경우, 상기 신호가 "로우"상태이면, 상기 제 1 비교기(17) (19) 및 제 2 비교기(18)와 스위칭회로(20)는 동작하지 않는다. 즉, 노멀모드인 경우에는 메모리셀군(1) (2)-데이터감지/구동회로(3-10 )-데이터버스쌍[물론 전달게이트(11-15)는 턴오프상태임]-데이터 선택회로(16)-데이터 출력버퍼로 되는 데이터 전송경로를 가지고, 데스트모드인 경우에는 메모리셀군(1) (2)-데이타감지 /구동회로(3-10 )-데이터버스쌍[전달게이트(11-15)는 턴오프상태임]-제 1 비교기(17)(19)-제 2 비교기(18)-스위칭회로(20)-데이터 출력버퍼로 되는 데어터 전송경로를 가지게 된다.

상술한 바와 같은 종래의 구성에 있어서는 노멀모드시에 좌측의 메모리셀군 으로부터 선택되어 나오는 데이터가 데이터출력버터로 전송되기 위해서 전달게이트(11-15)를 반드시 거쳐서 하므로 동작속도가 저하되는 문제가 있다. 또한 종래의 테스트방법에 있어서는, 노멀모드시에 공통으로 데이터가 구동회로(데이터감지/구동회로(3-10)에 포함되어 있음)를 통해야 하므로 전력소모가 증대하고, 전달게이트(11-15)의 존재로 인해 데이터버스쌍의 수가 많은 고집적메모리장치에서 면적을 증가시키는 요인이 된다.

따라서 본 발명의 다른 목적은 반도체 메모리 장치의 병렬비트 테스트 방법에 있어서, 전력소모를 줄이고 고집적화에 적합한 방법을 제공한다.

본 발명의 다른 목적은 반도체메몰리장치의 정상동작에 영향을 주지않고 여러게의 병렬비트를 테스트하는 방법을 제공함에 있다.

이하 본 발명을 첨부된 도면을 참조하여 상세히 설명한다.

제 2 도는 본 발명에 따른 다중병렬비트테스트방법을 보여주는 구성도이다.

상기 제 2 도에서는 8개의 비트를 병렬로 테스트하는 경우를 실시예로 하는데, 도시된 바와 같이, 두개의 메모리셀군(100) (101)은 각각 네개의 입출력선쌍을 통하여 각각 네개의 데이터 감지회로(102-105) (106-109)와 연결되어 있으며, 상기 8개의 데이터 감지회로(102-109)는 8개의 드라이버(110-117)와 각각 연결 두개씩 한조를 이루어 4개의 제 1 비교(118-121)와 연결되어 있다.

상기 제 1 비교기(118-121)는 두개의 데이터감지회로의 출력, 즉 두개의 데이터쌍을 직접 입력하도록 되어 있다. 상기 드라이버(110-117)와 제 1 비교기(118-121)의 출력은 모두 하나의 데이터쌍으로 구성되어 네개의 데이터버스쌍에 연결되어 있는데, 드라이버는 두개씩 제 1 비교기는 한개씩 상기 데이터버스쌍의 각각에 접속된다. 상기 네개의 데이터버스쌍들은 하나의 제 2 비교기(122)의 입력단과 연결되고, 상기 제 2 비교기(122)는 데이터출력버퍼(125)와 스위치회로(123)를 통하여 연결되어 있다. 또한 상기 네개의 데이터버스쌍들은 데이터선택회로(124)의 입력단과 연결되어 있다. 그리고 상기 드리이버(110-117) 및 제 1 비교기(118-121)와 제 2 비교기(122) 및 스위치회로(123)와 데이터회로(124)는 병렬테스트인에이블신호(129)에 의해 제어를 받는다.

제 3 도는 상기 좌측의 메모리셀군(1)과 입출력선쌍과의 연결형태를 보여주는 일례를 도시한 것으로서, 상기 입출력선쌍들은 전달트랜지스터(140-155)를 통하여 센스엠프(132-139)와 연결되어 있다. 상기 센스엠프(132-139)는 비트라인쌍을 통하여 메모리셀(도시되지 않음)과 연결되어 있다. 상기 전달트랜지서터(140-155)의 게이트들은 컬럼디코더(130) (131)에 두부분으로 나뉘어 연결되어 컬럼디코더(130) (131)로부터 출력되는 컬럼선택신호에 의해 센스엠프로부터 나오는 데이터를 입출력선쌍으로 전송한다.

제 4 도는 상기 입출력선쌍들을 프리차아지 및 등화시키는 회로이다. 상기 입출력선프리차아지 및 등화회로에서는 프리차아지 및 등화신호에 게이트가 접속된 프리차아지트랜지스터(161-164)와, 상기 신호에 게이트가 접속되어 한쌍의 입출력선을 등화시키는 앤모오스 및 피모오스트랜지스터(165, 166) (169, 170)와, 상기 신호를 반전시켜 상기 등화용 피모오스트랜지스터(169, 170)의 게이트로 인가하는 인버터(167, 168)로 구성되어 있다. 상기 회로에 의한 입출력선쌍의 프리차아지 및 등화레벨은 상기 프리차아지트랜지스터(161-164)의 드레인에 접속된 전원전압이 앤채널트랜지스터의 드레쉬홀드 전압만큼 강하된 값이 될 것이다.

상기한 제 2 도를 중심으로 제 3 도 및 제 4 도를 참조하여 본 발명에 따른 다중비트병렬테스트방법을 설명하면 하기와 같다.

먼저, 제 3 도를 참조하면 메모리셀로부터 독출된 데이터쌍은 비트라인쌍쌍을 통하여 센스앰프(132-139)로 전달되거, 센스앰프에서 증폭된 데이터는 컬럼디코더(130, 131)중 하나로부터 컬럼선택신호가 "하이"상태로 출력되면 턴온된 전달트랜지스터를 통하여 입출력선쌍으로 데이터쌍을 전송한다. 상기 컬럼선택신호의 "하이"상태에 의해 데이터쌍이 입출력선쌍으로 전송되기전에는, 제 4 도의 입출력선프리차아지 및 등화신호는 소정기간동안 "하이" 상태를 유지하여 상기 입출력선쌍이 Vcc-VTN(VTN은 앤채널트랜지스터의 드레쉬홀드전압)의 값으로 프리차아지 및 등화되어 있는 상태이다. 그리고 병렬테스트인에이블신호(127)는 드라이버(110-117)와 데이타선택 회로(124)를 디스에이블상태로 만들고, 제 1 비교기(118-121)와 제 2 비교기(122)및 스위칭회로(123)만을 인에이블상태로 만든다. 그리서 상기 입출력선쌍으로 전송된 데이터쌍은 데이터감지회로(102) (109)로 입력되고, 데이터감지회로는 드라이버(110-117)가 디스에이블 상태이므로 상기 데이터쌍을 증폭한 다음 제 1 비교기(118-121)로 출력한다. 제 1 비교기는 두개의 데이터쌍을 입력하여 선택된 하나의 데이터쌍을 각각 데이터버스쌍으로 출력한다. 그러면 제 2 비교기(122)는 상기 데이터버스쌍에 실린 상기 제 1 비교기(118-121)로부터 공급된 네개의 데이터쌍을 입력한 다음, 소정의 디코딩동작에 의해 선택된 하나의 데이터쌍을 턴온되어 있는 스위칭회로(123)를 통하여 데이터출력 버퍼(125)로 전송한다. 즉, 병렬테스트 모드에서 데이터쌍들이 전송되는 경로는 메모리셀군(100)(101)으로부터 데이터 감지회로(102-109)-제 1 비교기(118-121)-데이터버스쌍-제 2 비교기(122)-스위칭회로(123)을 통하여 데이터 출력회로(125)로 가는 것이 된다.

한편 노멀모드인 경우에는 상기 병렬테스트 인에이블신호(129)가 상기 제 1 비교기(118-121)와 제 2 비교기(122) 및 스위칭회로(123)를 디스에이블 상태로 만들기 때문에, 상기 병렬 테스트에서 데이터 쌍들이 지나간 경로와는 무관하게 데이터 감지회로(102-109)-드라아버(110-117)-데이터버스쌍-데이터선택회로(124)로 이어지는 경로를 통하여 데이터출력버퍼(125)로 전송된다.

상기 본 발명의 실시예서는 8비트의 병렬데이터를 테스트하는 경우만을 실시예로 개시하였으나, N개의 병렬비트를 처리하는 경우하면 상기 제 1 비교기의 갯수는 N/2개로써 한개당 N/4개의 데이터쌍을 처리할 수 있으며, 제 2 비교기는 상기 제 1 비교기로부터 출력되는 전체 N/2개의 데이터쌍을 처리할 수가 있다.

상술한 바와 같이, 본 발명은 반도체메모리장치에서 여러개의 병렬비트를 테스트하는 방법에 있어서, 소정갯수의 제 1 및 제 2 비교기만으로 간단하게 병렬데이터쌍을 처리할 수 있는 방법을 제공함으로써, 테스트에 소모되는 전력과 시간을 줄이는 효과가 있다. 또한 본 발명은 노멀모드에서나 테스트모드에서나 데이터버스의 상태를 일정하게 유지하고 테스트모드에서 데이터쌍들이 불필요한 전송경로를 거치지 않도록 함으로써, 테스트동작 및 노멀동작에서의 동작고속화를 달성하는 이점이 있다.

Claims (4)

- 데이타출력버퍼와 소정갯수의 데이타버스쌍 및 메모리셀군을 구비하는 반도체메모리장치의 다중비트병렬테으스트방법에 있어서, 상기 메로리셀군으로부터 공급되는 데이터쌍을 감지하는 데이터감지부와, 상기 데이터감지부와 상기 소정갯수의 데이터버스쌍들의 사이에 연결된 구동부와, 상기 데이터감지부와 하나의 데이터버스쌍사이에 연결되어 상기 데이터 감지부로부터 출력되는 데이터쌍들의 일군을 입력하여 상기 하나의 데이터버스쌍으로 단일의 데이터쌍을 출력하는 하나의 제 1 비교기와, 상기 데이타감지부와 다른하나의 데이터쌍 사이에 연결되어 데이터감지부로부터 출력되는 데이터쌍들의 타군을 입력하는 상기 다른하나의 데이터쌍으로 단일의 데이터쌍을 출력하는 다른하나의 제 1 비교기와, 상기 데이터버스쌍들에 입력이 연결되고 상기 데이타출력버퍼에 출력이 연결되어 상기 데이타버스쌍들에 있는 소정갯수의 데이터쌍을 입력하여 단일의 데이터쌍을 출력하는 제 2 비교기와, 상기 데이터버스쌍들에 입력이 연결되어 상기 데이터출력버퍼에 출력이 연결되어 상기 데이터버스쌍들에 있는 소정갯수의 데이터쌍을 입력하여 단일의 데이터쌍을 출력하는 데이터선택회로를 구비하여, 상기 데이터감지부가 상기 메모리셀군으로부터 공급되는 복수개의 데이터쌍을 노멀모드에서는 상기 구동부를 통하여 상기 데이터버스쌍들로 보내고 테스트모드에서는 상기 제 1 비교기로 보냄을 특징으로 하는 반도체메모리장치의 다중비트병렬테스트방법.

- 제 1 항에 있어서, 상기 제 1 및 제 2 비교기가 노멀모드에서는 동작하지 않음을 특징으로 하는 반도체메모리장치의 다중비트병렬테스트방법.

- 제 1 항 또는 제 2 항에 있어서, 상기 제 1 비교기가 입력단을 소정레벨로 프리차아지하는 회로를 구비하여, 노멀모드에서 상기 피리차아지회로에 의해 입력이 프리차아지됨을 특징으로 하는 반도체메모리장치의 다중비트병렬테스트방법.

- 제 1 항 또는 제 2 항에 있어서, 상기 제 2 비교기가 출력단에 스위칭회로를 구비하여, 상기 스위칭회로가 노멀모드에서 턴오프됨을 특징으로 하는 반도체 메모리 장치의 다중비트병렬 테스트방법.

Priority Applications (8)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1019900008924A KR930008417B1 (ko) | 1990-06-18 | 1990-06-18 | 반도체 메모리 장치의 다중 비트 병렬 테스트방법 |

| FR9009152A FR2663450B1 (fr) | 1990-06-18 | 1990-07-18 | Procede de test en parallele de bits multiples dans un dispositif memoire a semiconducteur. |

| DE4023015A DE4023015C1 (ko) | 1990-06-18 | 1990-07-19 | |

| US07/559,697 US5077689A (en) | 1990-01-18 | 1990-07-30 | Method for multi-bit parallel test in semiconductor memory device |

| IT48190A IT1241525B (it) | 1990-06-18 | 1990-07-31 | "metodo per collaudo in parallelo su piu' bit in un dispositivo di memoria a semiconduttori". |

| JP02201562A JP3025519B2 (ja) | 1990-06-18 | 1990-07-31 | 半導体記憶素子におけるマルチビツトパラレルテストの方法及びその半導体記憶素子 |

| CN90106619A CN1025077C (zh) | 1990-06-18 | 1990-07-31 | 半导体存储器件及其多位并行测试方法 |

| GB9016763A GB2245393B (en) | 1990-06-18 | 1990-07-31 | Multi-bit parallel testing |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1019900008924A KR930008417B1 (ko) | 1990-06-18 | 1990-06-18 | 반도체 메모리 장치의 다중 비트 병렬 테스트방법 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR920001552A KR920001552A (ko) | 1992-01-30 |

| KR930008417B1 true KR930008417B1 (ko) | 1993-08-31 |

Family

ID=19300202

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1019900008924A KR930008417B1 (ko) | 1990-01-18 | 1990-06-18 | 반도체 메모리 장치의 다중 비트 병렬 테스트방법 |

Country Status (8)

| Country | Link |

|---|---|

| US (1) | US5077689A (ko) |

| JP (1) | JP3025519B2 (ko) |

| KR (1) | KR930008417B1 (ko) |

| CN (1) | CN1025077C (ko) |

| DE (1) | DE4023015C1 (ko) |

| FR (1) | FR2663450B1 (ko) |

| GB (1) | GB2245393B (ko) |

| IT (1) | IT1241525B (ko) |

Families Citing this family (20)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5675544A (en) * | 1990-06-25 | 1997-10-07 | Texas Instruments Incorporated | Method and apparatus for parallel testing of memory circuits |

| KR950001293B1 (ko) * | 1992-04-22 | 1995-02-15 | 삼성전자주식회사 | 반도체 메모리칩의 병렬테스트 회로 |

| JPH06295599A (ja) * | 1993-04-09 | 1994-10-21 | Nec Corp | 半導体記憶装置 |

| KR960008824B1 (en) * | 1993-11-17 | 1996-07-05 | Samsung Electronics Co Ltd | Multi bit test circuit and method of semiconductor memory device |

| KR0137846B1 (ko) * | 1994-03-24 | 1998-06-15 | 문정환 | 반도체 기억장치의 멀티비트 테스트회로 |

| KR0172533B1 (ko) * | 1995-10-18 | 1999-03-30 | 김주용 | 플래쉬 메모리 장치 |

| US5592425A (en) * | 1995-12-20 | 1997-01-07 | Intel Corporation | Method and apparatus for testing a memory where data is passed through the memory for comparison with data read from the memory |

| US5905744A (en) * | 1997-09-30 | 1999-05-18 | Lsi Logic Corporation | Test mode for multifunction PCI device |

| JP3322303B2 (ja) * | 1998-10-28 | 2002-09-09 | 日本電気株式会社 | 半導体記憶装置 |

| KR100339502B1 (ko) | 1999-06-02 | 2002-05-31 | 윤종용 | 다수개의 데이터 라인을 구분되게 테스트하는 통합 데이터 라인 테스트 회로 및 이를 이용하는 테스트 방법 |

| KR100295691B1 (ko) * | 1999-06-04 | 2001-07-12 | 김영환 | 디램의 오픈 테스트용 테스트모드회로 |

| JP3484388B2 (ja) * | 2000-02-08 | 2004-01-06 | 日本電気株式会社 | 半導体記憶装置 |

| KR100346447B1 (ko) * | 2000-06-30 | 2002-07-27 | 주식회사 하이닉스반도체 | 반도체 메모리 소자의 병렬 테스트 장치 |

| KR100546308B1 (ko) * | 2002-12-13 | 2006-01-26 | 삼성전자주식회사 | 데이터 독출 능력이 향상된 반도체 메모리 장치. |

| KR100699827B1 (ko) * | 2004-03-23 | 2007-03-27 | 삼성전자주식회사 | 메모리 모듈 |

| US7480195B2 (en) * | 2005-05-11 | 2009-01-20 | Micron Technology, Inc. | Internal data comparison for memory testing |

| KR100809070B1 (ko) * | 2006-06-08 | 2008-03-03 | 삼성전자주식회사 | 반도체 메모리 장치의 병렬 비트 테스트 회로 및 그 방법 |

| KR101821088B1 (ko) | 2008-07-02 | 2018-01-22 | 뷔흘러 에이지 | 가루 및/또는 세몰리나를 만드는 장치 및 방법 |

| CN101770967A (zh) * | 2009-01-03 | 2010-07-07 | 上海芯豪微电子有限公司 | 一种共用基底集成电路测试方法、装置和系统 |

| KR20150033374A (ko) * | 2013-09-24 | 2015-04-01 | 에스케이하이닉스 주식회사 | 반도체 시스템 및 반도체 장치 |

Family Cites Families (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS60115099A (ja) * | 1983-11-25 | 1985-06-21 | Fujitsu Ltd | 半導体記憶装置 |

| US4686456A (en) * | 1985-06-18 | 1987-08-11 | Kabushiki Kaisha Toshiba | Memory test circuit |

| JP2523586B2 (ja) * | 1987-02-27 | 1996-08-14 | 株式会社日立製作所 | 半導体記憶装置 |

| JPH01286200A (ja) * | 1988-05-12 | 1989-11-17 | Fujitsu Ltd | 半導体メモリ装置 |

| JPH0713858B2 (ja) * | 1988-08-30 | 1995-02-15 | 三菱電機株式会社 | 半導体記憶装置 |

| KR910005306B1 (ko) * | 1988-12-31 | 1991-07-24 | 삼성전자 주식회사 | 고밀도 메모리의 테스트를 위한 병렬리드회로 |

-

1990

- 1990-06-18 KR KR1019900008924A patent/KR930008417B1/ko not_active IP Right Cessation

- 1990-07-18 FR FR9009152A patent/FR2663450B1/fr not_active Expired - Fee Related

- 1990-07-19 DE DE4023015A patent/DE4023015C1/de not_active Expired - Lifetime

- 1990-07-30 US US07/559,697 patent/US5077689A/en not_active Expired - Lifetime

- 1990-07-31 JP JP02201562A patent/JP3025519B2/ja not_active Expired - Lifetime

- 1990-07-31 CN CN90106619A patent/CN1025077C/zh not_active Expired - Fee Related

- 1990-07-31 IT IT48190A patent/IT1241525B/it active IP Right Grant

- 1990-07-31 GB GB9016763A patent/GB2245393B/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| FR2663450B1 (fr) | 1993-10-15 |

| DE4023015C1 (ko) | 1991-12-19 |

| GB2245393B (en) | 1994-02-23 |

| IT1241525B (it) | 1994-01-17 |

| GB9016763D0 (en) | 1990-09-12 |

| CN1025077C (zh) | 1994-06-15 |

| GB2245393A (en) | 1992-01-02 |

| KR920001552A (ko) | 1992-01-30 |

| JP3025519B2 (ja) | 2000-03-27 |

| JPH0448500A (ja) | 1992-02-18 |

| CN1057720A (zh) | 1992-01-08 |

| IT9048190A1 (it) | 1992-01-31 |

| US5077689A (en) | 1991-12-31 |

| FR2663450A1 (fr) | 1991-12-20 |

| IT9048190A0 (it) | 1990-07-31 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR930008417B1 (ko) | 반도체 메모리 장치의 다중 비트 병렬 테스트방법 | |

| US5418737A (en) | DRAM with sub data lines and match lines for test | |

| US4893278A (en) | Semiconductor memory device including precharge/equalization circuitry for the complementary data lines | |

| NL192155C (nl) | Datatransmissieketen. | |

| US7035161B2 (en) | Semiconductor integrated circuit | |

| KR100574181B1 (ko) | 고속기입회복을갖춘메모리장치및그에관련된기입회복방법 | |

| US6661714B2 (en) | Integrated circuit memory devices having sense amplifiers therein that receive nominal and boosted supply voltages when active and methods of operating same | |

| KR100520179B1 (ko) | 반도체 메모리 장치의 입출력 구조 | |

| EP0440206A2 (en) | Semiconductor memory having built-in test circuit | |

| EP0521594A2 (en) | Semiconductor memory device | |

| US5682110A (en) | Low capacitance bus driver | |

| KR930008311B1 (ko) | 센스 앰프의 출력 제어회로 | |

| JPH0456398B2 (ko) | ||

| US4730133A (en) | Decoder circuit of a semiconductor memory device | |

| US4634900A (en) | Sense amplifier | |

| JP2006502516A (ja) | カスコードセンス増幅器及び列選択回路及び動作方法。 | |

| EP0439141B1 (en) | Memory circuit with improved power interconnections | |

| KR0155986B1 (ko) | 반도체 기억장치 | |

| JPH05250872A (ja) | ランダム・アクセス・メモリ | |

| US6188631B1 (en) | Semiconductor memory device column select circuit and method for minimizing load to data input/output lines | |

| US5982692A (en) | Bit line boost amplifier | |

| EP0397986B1 (en) | A non-address transition detection memory with improved access time | |

| US6011739A (en) | Semiconductor memory | |

| US6166964A (en) | Semiconductor memory and method of controlling data therefrom | |

| KR100342595B1 (ko) | 반도체기억장치 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A201 | Request for examination | ||

| G160 | Decision to publish patent application | ||

| E701 | Decision to grant or registration of patent right | ||

| GRNT | Written decision to grant | ||

| FPAY | Annual fee payment |

Payment date: 20090814 Year of fee payment: 17 |

|

| EXPY | Expiration of term |