KR20190032414A - 반도체 장치 - Google Patents

반도체 장치 Download PDFInfo

- Publication number

- KR20190032414A KR20190032414A KR1020197003827A KR20197003827A KR20190032414A KR 20190032414 A KR20190032414 A KR 20190032414A KR 1020197003827 A KR1020197003827 A KR 1020197003827A KR 20197003827 A KR20197003827 A KR 20197003827A KR 20190032414 A KR20190032414 A KR 20190032414A

- Authority

- KR

- South Korea

- Prior art keywords

- insulator

- oxide

- transistor

- barrier layer

- film

- Prior art date

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 268

- 239000012212 insulator Substances 0.000 claims abstract description 611

- 239000004020 conductor Substances 0.000 claims abstract description 376

- 230000004888 barrier function Effects 0.000 claims abstract description 313

- 229910052760 oxygen Inorganic materials 0.000 claims abstract description 236

- 239000001301 oxygen Substances 0.000 claims abstract description 234

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical group [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 claims abstract description 232

- 238000000034 method Methods 0.000 claims description 175

- 239000001257 hydrogen Substances 0.000 claims description 117

- 229910052739 hydrogen Inorganic materials 0.000 claims description 117

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 claims description 93

- 230000006870 function Effects 0.000 claims description 75

- 230000010354 integration Effects 0.000 abstract description 4

- 239000010408 film Substances 0.000 description 479

- 239000010410 layer Substances 0.000 description 235

- 239000000758 substrate Substances 0.000 description 162

- 239000007789 gas Substances 0.000 description 119

- 239000000463 material Substances 0.000 description 87

- TWNQGVIAIRXVLR-UHFFFAOYSA-N oxo(oxoalumanyloxy)alumane Chemical compound O=[Al]O[Al]=O TWNQGVIAIRXVLR-UHFFFAOYSA-N 0.000 description 83

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 82

- 229910052710 silicon Inorganic materials 0.000 description 82

- 239000010703 silicon Substances 0.000 description 82

- 238000004544 sputter deposition Methods 0.000 description 80

- 229910052721 tungsten Inorganic materials 0.000 description 77

- 239000010937 tungsten Substances 0.000 description 77

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 75

- 238000005530 etching Methods 0.000 description 72

- 238000000151 deposition Methods 0.000 description 70

- 230000008021 deposition Effects 0.000 description 68

- 238000010438 heat treatment Methods 0.000 description 67

- 239000012298 atmosphere Substances 0.000 description 63

- 239000012535 impurity Substances 0.000 description 60

- MZLGASXMSKOWSE-UHFFFAOYSA-N tantalum nitride Chemical compound [Ta]#N MZLGASXMSKOWSE-UHFFFAOYSA-N 0.000 description 51

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 50

- 238000000231 atomic layer deposition Methods 0.000 description 50

- 238000004519 manufacturing process Methods 0.000 description 41

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 description 38

- 238000005229 chemical vapour deposition Methods 0.000 description 36

- 229910044991 metal oxide Inorganic materials 0.000 description 35

- 150000004706 metal oxides Chemical class 0.000 description 35

- 238000009792 diffusion process Methods 0.000 description 34

- 239000011701 zinc Substances 0.000 description 28

- 229910052581 Si3N4 Inorganic materials 0.000 description 27

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 27

- 238000011282 treatment Methods 0.000 description 27

- 230000008569 process Effects 0.000 description 26

- 238000012545 processing Methods 0.000 description 26

- 150000002431 hydrogen Chemical class 0.000 description 25

- 229910052751 metal Inorganic materials 0.000 description 25

- 239000002184 metal Substances 0.000 description 25

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 24

- 229910052757 nitrogen Inorganic materials 0.000 description 24

- 229910052814 silicon oxide Inorganic materials 0.000 description 23

- 229910052782 aluminium Inorganic materials 0.000 description 22

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 22

- 125000004429 atom Chemical group 0.000 description 22

- 238000005259 measurement Methods 0.000 description 22

- 206010021143 Hypoxia Diseases 0.000 description 21

- 229910000449 hafnium oxide Inorganic materials 0.000 description 20

- WIHZLLGSGQNAGK-UHFFFAOYSA-N hafnium(4+);oxygen(2-) Chemical compound [O-2].[O-2].[Hf+4] WIHZLLGSGQNAGK-UHFFFAOYSA-N 0.000 description 20

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 20

- 229910001868 water Inorganic materials 0.000 description 20

- 238000001459 lithography Methods 0.000 description 19

- 230000015572 biosynthetic process Effects 0.000 description 17

- 230000007547 defect Effects 0.000 description 17

- 230000003647 oxidation Effects 0.000 description 17

- 238000007254 oxidation reaction Methods 0.000 description 17

- 238000009832 plasma treatment Methods 0.000 description 17

- 238000001312 dry etching Methods 0.000 description 16

- 229910052799 carbon Inorganic materials 0.000 description 15

- 230000035882 stress Effects 0.000 description 15

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 14

- MYMOFIZGZYHOMD-UHFFFAOYSA-N Dioxygen Chemical compound O=O MYMOFIZGZYHOMD-UHFFFAOYSA-N 0.000 description 14

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 14

- 239000010949 copper Substances 0.000 description 14

- 229910001882 dioxygen Inorganic materials 0.000 description 14

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 13

- 230000008859 change Effects 0.000 description 13

- 229910052802 copper Inorganic materials 0.000 description 13

- 239000013078 crystal Substances 0.000 description 13

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 description 13

- 238000004458 analytical method Methods 0.000 description 12

- 238000006243 chemical reaction Methods 0.000 description 12

- 238000005498 polishing Methods 0.000 description 12

- 229910052719 titanium Inorganic materials 0.000 description 12

- 239000010936 titanium Substances 0.000 description 12

- 150000002500 ions Chemical class 0.000 description 11

- 150000004767 nitrides Chemical class 0.000 description 11

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 11

- 238000012360 testing method Methods 0.000 description 11

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 10

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 10

- 239000003990 capacitor Substances 0.000 description 10

- 230000000052 comparative effect Effects 0.000 description 10

- 239000011229 interlayer Substances 0.000 description 10

- 229910052750 molybdenum Inorganic materials 0.000 description 10

- 239000011733 molybdenum Substances 0.000 description 10

- 239000007800 oxidant agent Substances 0.000 description 10

- 238000004140 cleaning Methods 0.000 description 9

- 229910052738 indium Inorganic materials 0.000 description 9

- 239000007787 solid Substances 0.000 description 9

- 238000003860 storage Methods 0.000 description 9

- 229910052715 tantalum Inorganic materials 0.000 description 9

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 9

- OGIDPMRJRNCKJF-UHFFFAOYSA-N titanium oxide Inorganic materials [Ti]=O OGIDPMRJRNCKJF-UHFFFAOYSA-N 0.000 description 9

- XEEYBQQBJWHFJM-UHFFFAOYSA-N Iron Chemical compound [Fe] XEEYBQQBJWHFJM-UHFFFAOYSA-N 0.000 description 8

- 239000000969 carrier Substances 0.000 description 8

- 239000000470 constituent Substances 0.000 description 8

- 238000013461 design Methods 0.000 description 8

- 238000000851 scanning transmission electron micrograph Methods 0.000 description 8

- GQPLMRYTRLFLPF-UHFFFAOYSA-N Nitrous Oxide Chemical compound [O-][N+]#N GQPLMRYTRLFLPF-UHFFFAOYSA-N 0.000 description 7

- GWEVSGVZZGPLCZ-UHFFFAOYSA-N Titan oxide Chemical compound O=[Ti]=O GWEVSGVZZGPLCZ-UHFFFAOYSA-N 0.000 description 7

- 229910052786 argon Inorganic materials 0.000 description 7

- APFVFJFRJDLVQX-UHFFFAOYSA-N indium atom Chemical compound [In] APFVFJFRJDLVQX-UHFFFAOYSA-N 0.000 description 7

- 229910003437 indium oxide Inorganic materials 0.000 description 7

- PJXISJQVUVHSOJ-UHFFFAOYSA-N indium(iii) oxide Chemical compound [O-2].[O-2].[O-2].[In+3].[In+3] PJXISJQVUVHSOJ-UHFFFAOYSA-N 0.000 description 7

- 238000003754 machining Methods 0.000 description 7

- 239000007769 metal material Substances 0.000 description 7

- 238000002488 metal-organic chemical vapour deposition Methods 0.000 description 7

- QGLKJKCYBOYXKC-UHFFFAOYSA-N nonaoxidotritungsten Chemical compound O=[W]1(=O)O[W](=O)(=O)O[W](=O)(=O)O1 QGLKJKCYBOYXKC-UHFFFAOYSA-N 0.000 description 7

- 230000001590 oxidative effect Effects 0.000 description 7

- 239000002356 single layer Substances 0.000 description 7

- 238000012546 transfer Methods 0.000 description 7

- -1 tungsten nitride Chemical class 0.000 description 7

- 229910001930 tungsten oxide Inorganic materials 0.000 description 7

- XLOMVQKBTHCTTD-UHFFFAOYSA-N Zinc monoxide Chemical compound [Zn]=O XLOMVQKBTHCTTD-UHFFFAOYSA-N 0.000 description 6

- 239000000956 alloy Substances 0.000 description 6

- 230000006378 damage Effects 0.000 description 6

- 125000004430 oxygen atom Chemical group O* 0.000 description 6

- BPUBBGLMJRNUCC-UHFFFAOYSA-N oxygen(2-);tantalum(5+) Chemical compound [O-2].[O-2].[O-2].[O-2].[O-2].[Ta+5].[Ta+5] BPUBBGLMJRNUCC-UHFFFAOYSA-N 0.000 description 6

- RVTZCBVAJQQJTK-UHFFFAOYSA-N oxygen(2-);zirconium(4+) Chemical compound [O-2].[O-2].[Zr+4] RVTZCBVAJQQJTK-UHFFFAOYSA-N 0.000 description 6

- 239000011347 resin Substances 0.000 description 6

- 229920005989 resin Polymers 0.000 description 6

- 229910001936 tantalum oxide Inorganic materials 0.000 description 6

- 229910052725 zinc Inorganic materials 0.000 description 6

- 229910001928 zirconium oxide Inorganic materials 0.000 description 6

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 5

- 229910052779 Neodymium Inorganic materials 0.000 description 5

- QCWXUUIWCKQGHC-UHFFFAOYSA-N Zirconium Chemical compound [Zr] QCWXUUIWCKQGHC-UHFFFAOYSA-N 0.000 description 5

- 229910052783 alkali metal Inorganic materials 0.000 description 5

- 150000001340 alkali metals Chemical class 0.000 description 5

- 229910052784 alkaline earth metal Inorganic materials 0.000 description 5

- 150000001342 alkaline earth metals Chemical class 0.000 description 5

- 239000012670 alkaline solution Substances 0.000 description 5

- GPBUGPUPKAGMDK-UHFFFAOYSA-N azanylidynemolybdenum Chemical compound [Mo]#N GPBUGPUPKAGMDK-UHFFFAOYSA-N 0.000 description 5

- 229910052796 boron Inorganic materials 0.000 description 5

- PMHQVHHXPFUNSP-UHFFFAOYSA-M copper(1+);methylsulfanylmethane;bromide Chemical compound Br[Cu].CSC PMHQVHHXPFUNSP-UHFFFAOYSA-M 0.000 description 5

- AJNVQOSZGJRYEI-UHFFFAOYSA-N digallium;oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[Ga+3].[Ga+3] AJNVQOSZGJRYEI-UHFFFAOYSA-N 0.000 description 5

- 229910052733 gallium Inorganic materials 0.000 description 5

- 229910001195 gallium oxide Inorganic materials 0.000 description 5

- 238000005468 ion implantation Methods 0.000 description 5

- 238000013507 mapping Methods 0.000 description 5

- 239000000203 mixture Substances 0.000 description 5

- QEFYFXOXNSNQGX-UHFFFAOYSA-N neodymium atom Chemical compound [Nd] QEFYFXOXNSNQGX-UHFFFAOYSA-N 0.000 description 5

- 229910052759 nickel Inorganic materials 0.000 description 5

- SIWVEOZUMHYXCS-UHFFFAOYSA-N oxo(oxoyttriooxy)yttrium Chemical compound O=[Y]O[Y]=O SIWVEOZUMHYXCS-UHFFFAOYSA-N 0.000 description 5

- 230000003071 parasitic effect Effects 0.000 description 5

- 238000000206 photolithography Methods 0.000 description 5

- 238000001004 secondary ion mass spectrometry Methods 0.000 description 5

- 239000000243 solution Substances 0.000 description 5

- 238000002230 thermal chemical vapour deposition Methods 0.000 description 5

- 238000001039 wet etching Methods 0.000 description 5

- YVTHLONGBIQYBO-UHFFFAOYSA-N zinc indium(3+) oxygen(2-) Chemical compound [O--].[Zn++].[In+3] YVTHLONGBIQYBO-UHFFFAOYSA-N 0.000 description 5

- 229910052726 zirconium Inorganic materials 0.000 description 5

- CURLTUGMZLYLDI-UHFFFAOYSA-N Carbon dioxide Chemical compound O=C=O CURLTUGMZLYLDI-UHFFFAOYSA-N 0.000 description 4

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 4

- HCHKCACWOHOZIP-UHFFFAOYSA-N Zinc Chemical compound [Zn] HCHKCACWOHOZIP-UHFFFAOYSA-N 0.000 description 4

- 239000000460 chlorine Substances 0.000 description 4

- 229910052804 chromium Inorganic materials 0.000 description 4

- 239000011651 chromium Substances 0.000 description 4

- 239000002131 composite material Substances 0.000 description 4

- 230000002950 deficient Effects 0.000 description 4

- 238000010893 electron trap Methods 0.000 description 4

- 238000011049 filling Methods 0.000 description 4

- 229910052732 germanium Inorganic materials 0.000 description 4

- GNPVGFCGXDBREM-UHFFFAOYSA-N germanium atom Chemical compound [Ge] GNPVGFCGXDBREM-UHFFFAOYSA-N 0.000 description 4

- 229910052735 hafnium Inorganic materials 0.000 description 4

- VBJZVLUMGGDVMO-UHFFFAOYSA-N hafnium atom Chemical compound [Hf] VBJZVLUMGGDVMO-UHFFFAOYSA-N 0.000 description 4

- 229910052742 iron Inorganic materials 0.000 description 4

- 239000011159 matrix material Substances 0.000 description 4

- 150000002739 metals Chemical class 0.000 description 4

- 239000002159 nanocrystal Substances 0.000 description 4

- MWUXSHHQAYIFBG-UHFFFAOYSA-N nitrogen oxide Inorganic materials O=[N] MWUXSHHQAYIFBG-UHFFFAOYSA-N 0.000 description 4

- 239000000126 substance Substances 0.000 description 4

- 229910052727 yttrium Inorganic materials 0.000 description 4

- VWQVUPCCIRVNHF-UHFFFAOYSA-N yttrium atom Chemical compound [Y] VWQVUPCCIRVNHF-UHFFFAOYSA-N 0.000 description 4

- JBRZTFJDHDCESZ-UHFFFAOYSA-N AsGa Chemical compound [As]#[Ga] JBRZTFJDHDCESZ-UHFFFAOYSA-N 0.000 description 3

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 3

- 229910052684 Cerium Inorganic materials 0.000 description 3

- GYHNNYVSQQEPJS-UHFFFAOYSA-N Gallium Chemical compound [Ga] GYHNNYVSQQEPJS-UHFFFAOYSA-N 0.000 description 3

- FYYHWMGAXLPEAU-UHFFFAOYSA-N Magnesium Chemical compound [Mg] FYYHWMGAXLPEAU-UHFFFAOYSA-N 0.000 description 3

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 3

- 229910000577 Silicon-germanium Inorganic materials 0.000 description 3

- 230000009471 action Effects 0.000 description 3

- 229910045601 alloy Inorganic materials 0.000 description 3

- MDPILPRLPQYEEN-UHFFFAOYSA-N aluminium arsenide Chemical compound [As]#[Al] MDPILPRLPQYEEN-UHFFFAOYSA-N 0.000 description 3

- 229910000416 bismuth oxide Inorganic materials 0.000 description 3

- ZMIGMASIKSOYAM-UHFFFAOYSA-N cerium Chemical compound [Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce] ZMIGMASIKSOYAM-UHFFFAOYSA-N 0.000 description 3

- 239000003795 chemical substances by application Substances 0.000 description 3

- 150000001875 compounds Chemical class 0.000 description 3

- TYIXMATWDRGMPF-UHFFFAOYSA-N dibismuth;oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[Bi+3].[Bi+3] TYIXMATWDRGMPF-UHFFFAOYSA-N 0.000 description 3

- 230000000694 effects Effects 0.000 description 3

- 238000010894 electron beam technology Methods 0.000 description 3

- 238000000921 elemental analysis Methods 0.000 description 3

- 239000004744 fabric Substances 0.000 description 3

- YBMRDBCBODYGJE-UHFFFAOYSA-N germanium oxide Inorganic materials O=[Ge]=O YBMRDBCBODYGJE-UHFFFAOYSA-N 0.000 description 3

- 238000003475 lamination Methods 0.000 description 3

- 229910052746 lanthanum Inorganic materials 0.000 description 3

- FZLIPJUXYLNCLC-UHFFFAOYSA-N lanthanum atom Chemical compound [La] FZLIPJUXYLNCLC-UHFFFAOYSA-N 0.000 description 3

- 229910052749 magnesium Inorganic materials 0.000 description 3

- 239000011777 magnesium Substances 0.000 description 3

- 229910000484 niobium oxide Inorganic materials 0.000 description 3

- URLJKFSTXLNXLG-UHFFFAOYSA-N niobium(5+);oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[O-2].[O-2].[Nb+5].[Nb+5] URLJKFSTXLNXLG-UHFFFAOYSA-N 0.000 description 3

- 238000005121 nitriding Methods 0.000 description 3

- 239000001272 nitrous oxide Substances 0.000 description 3

- PVADDRMAFCOOPC-UHFFFAOYSA-N oxogermanium Chemical compound [Ge]=O PVADDRMAFCOOPC-UHFFFAOYSA-N 0.000 description 3

- 239000002245 particle Substances 0.000 description 3

- 229910052698 phosphorus Inorganic materials 0.000 description 3

- 239000011574 phosphorus Substances 0.000 description 3

- 238000004549 pulsed laser deposition Methods 0.000 description 3

- 238000009751 slip forming Methods 0.000 description 3

- 238000004611 spectroscopical analysis Methods 0.000 description 3

- 239000011787 zinc oxide Substances 0.000 description 3

- 229910018072 Al 2 O 3 Inorganic materials 0.000 description 2

- ZAMOUSCENKQFHK-UHFFFAOYSA-N Chlorine atom Chemical compound [Cl] ZAMOUSCENKQFHK-UHFFFAOYSA-N 0.000 description 2

- KRHYYFGTRYWZRS-UHFFFAOYSA-N Fluorane Chemical compound F KRHYYFGTRYWZRS-UHFFFAOYSA-N 0.000 description 2

- YCKRFDGAMUMZLT-UHFFFAOYSA-N Fluorine atom Chemical compound [F] YCKRFDGAMUMZLT-UHFFFAOYSA-N 0.000 description 2

- 229910001218 Gallium arsenide Inorganic materials 0.000 description 2

- 229910000530 Gallium indium arsenide Inorganic materials 0.000 description 2

- CBENFWSGALASAD-UHFFFAOYSA-N Ozone Chemical compound [O-][O+]=O CBENFWSGALASAD-UHFFFAOYSA-N 0.000 description 2

- BOTDANWDWHJENH-UHFFFAOYSA-N Tetraethyl orthosilicate Chemical compound CCO[Si](OCC)(OCC)OCC BOTDANWDWHJENH-UHFFFAOYSA-N 0.000 description 2

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 description 2

- LEVVHYCKPQWKOP-UHFFFAOYSA-N [Si].[Ge] Chemical compound [Si].[Ge] LEVVHYCKPQWKOP-UHFFFAOYSA-N 0.000 description 2

- 229910052785 arsenic Inorganic materials 0.000 description 2

- RQNWIZPPADIBDY-UHFFFAOYSA-N arsenic atom Chemical compound [As] RQNWIZPPADIBDY-UHFFFAOYSA-N 0.000 description 2

- 229910052788 barium Inorganic materials 0.000 description 2

- 230000005540 biological transmission Effects 0.000 description 2

- 230000000903 blocking effect Effects 0.000 description 2

- 238000004364 calculation method Methods 0.000 description 2

- 229910002092 carbon dioxide Inorganic materials 0.000 description 2

- 239000001569 carbon dioxide Substances 0.000 description 2

- 229910052801 chlorine Inorganic materials 0.000 description 2

- 238000007796 conventional method Methods 0.000 description 2

- 238000003795 desorption Methods 0.000 description 2

- 230000002542 deteriorative effect Effects 0.000 description 2

- 238000010586 diagram Methods 0.000 description 2

- 229910001873 dinitrogen Inorganic materials 0.000 description 2

- 230000005685 electric field effect Effects 0.000 description 2

- 230000005669 field effect Effects 0.000 description 2

- 229910052731 fluorine Inorganic materials 0.000 description 2

- 239000011737 fluorine Substances 0.000 description 2

- 229910052736 halogen Inorganic materials 0.000 description 2

- 150000002367 halogens Chemical class 0.000 description 2

- 238000007654 immersion Methods 0.000 description 2

- 239000007788 liquid Substances 0.000 description 2

- 238000012986 modification Methods 0.000 description 2

- 230000004048 modification Effects 0.000 description 2

- 238000001451 molecular beam epitaxy Methods 0.000 description 2

- 239000005416 organic matter Substances 0.000 description 2

- 238000000623 plasma-assisted chemical vapour deposition Methods 0.000 description 2

- 238000002360 preparation method Methods 0.000 description 2

- 239000000047 product Substances 0.000 description 2

- 230000001681 protective effect Effects 0.000 description 2

- 238000005001 rutherford backscattering spectroscopy Methods 0.000 description 2

- 229910052706 scandium Inorganic materials 0.000 description 2

- SIXSYDAISGFNSX-UHFFFAOYSA-N scandium atom Chemical compound [Sc] SIXSYDAISGFNSX-UHFFFAOYSA-N 0.000 description 2

- 229910052712 strontium Inorganic materials 0.000 description 2

- VEALVRVVWBQVSL-UHFFFAOYSA-N strontium titanate Chemical compound [Sr+2].[O-][Ti]([O-])=O VEALVRVVWBQVSL-UHFFFAOYSA-N 0.000 description 2

- 239000010409 thin film Substances 0.000 description 2

- 229910052718 tin Inorganic materials 0.000 description 2

- LLZRNZOLAXHGLL-UHFFFAOYSA-J titanic acid Chemical compound O[Ti](O)(O)O LLZRNZOLAXHGLL-UHFFFAOYSA-J 0.000 description 2

- JPJZHBHNQJPGSG-UHFFFAOYSA-N titanium;zirconium;tetrahydrate Chemical compound O.O.O.O.[Ti].[Zr] JPJZHBHNQJPGSG-UHFFFAOYSA-N 0.000 description 2

- 229910052720 vanadium Inorganic materials 0.000 description 2

- MGWGWNFMUOTEHG-UHFFFAOYSA-N 4-(3,5-dimethylphenyl)-1,3-thiazol-2-amine Chemical compound CC1=CC(C)=CC(C=2N=C(N)SC=2)=C1 MGWGWNFMUOTEHG-UHFFFAOYSA-N 0.000 description 1

- 229910000838 Al alloy Inorganic materials 0.000 description 1

- 239000004215 Carbon black (E152) Substances 0.000 description 1

- UGFAIRIUMAVXCW-UHFFFAOYSA-N Carbon monoxide Chemical compound [O+]#[C-] UGFAIRIUMAVXCW-UHFFFAOYSA-N 0.000 description 1

- 206010010144 Completed suicide Diseases 0.000 description 1

- PWHULOQIROXLJO-UHFFFAOYSA-N Manganese Chemical compound [Mn] PWHULOQIROXLJO-UHFFFAOYSA-N 0.000 description 1

- 229910052774 Proactinium Inorganic materials 0.000 description 1

- BLRPTPMANUNPDV-UHFFFAOYSA-N Silane Chemical compound [SiH4] BLRPTPMANUNPDV-UHFFFAOYSA-N 0.000 description 1

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 description 1

- 229910008813 Sn—Si Inorganic materials 0.000 description 1

- 229910002367 SrTiO Inorganic materials 0.000 description 1

- 238000003917 TEM image Methods 0.000 description 1

- KXNLCSXBJCPWGL-UHFFFAOYSA-N [Ga].[As].[In] Chemical compound [Ga].[As].[In] KXNLCSXBJCPWGL-UHFFFAOYSA-N 0.000 description 1

- 239000002253 acid Substances 0.000 description 1

- 239000005407 aluminoborosilicate glass Substances 0.000 description 1

- DSAJWYNOEDNPEQ-UHFFFAOYSA-N barium atom Chemical compound [Ba] DSAJWYNOEDNPEQ-UHFFFAOYSA-N 0.000 description 1

- 229910052790 beryllium Inorganic materials 0.000 description 1

- ATBAMAFKBVZNFJ-UHFFFAOYSA-N beryllium atom Chemical compound [Be] ATBAMAFKBVZNFJ-UHFFFAOYSA-N 0.000 description 1

- 239000005388 borosilicate glass Substances 0.000 description 1

- 229910052800 carbon group element Inorganic materials 0.000 description 1

- 229910002091 carbon monoxide Inorganic materials 0.000 description 1

- 239000000919 ceramic Substances 0.000 description 1

- 238000005352 clarification Methods 0.000 description 1

- 239000011248 coating agent Substances 0.000 description 1

- 238000000576 coating method Methods 0.000 description 1

- 230000000295 complement effect Effects 0.000 description 1

- 238000005520 cutting process Methods 0.000 description 1

- 230000001419 dependent effect Effects 0.000 description 1

- 238000002149 energy-dispersive X-ray emission spectroscopy Methods 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 238000007687 exposure technique Methods 0.000 description 1

- 238000007667 floating Methods 0.000 description 1

- 239000011521 glass Substances 0.000 description 1

- 230000012447 hatching Effects 0.000 description 1

- 229930195733 hydrocarbon Natural products 0.000 description 1

- 150000002430 hydrocarbons Chemical class 0.000 description 1

- 125000004435 hydrogen atom Chemical group [H]* 0.000 description 1

- 238000003384 imaging method Methods 0.000 description 1

- RPQDHPTXJYYUPQ-UHFFFAOYSA-N indium arsenide Chemical compound [In]#[As] RPQDHPTXJYYUPQ-UHFFFAOYSA-N 0.000 description 1

- 239000011810 insulating material Substances 0.000 description 1

- 238000001307 laser spectroscopy Methods 0.000 description 1

- 239000004973 liquid crystal related substance Substances 0.000 description 1

- 238000012423 maintenance Methods 0.000 description 1

- 229910052748 manganese Inorganic materials 0.000 description 1

- 239000011572 manganese Substances 0.000 description 1

- 230000008018 melting Effects 0.000 description 1

- 238000002844 melting Methods 0.000 description 1

- 239000012528 membrane Substances 0.000 description 1

- 239000011156 metal matrix composite Substances 0.000 description 1

- 238000005459 micromachining Methods 0.000 description 1

- WUJISAYEUPRJOG-UHFFFAOYSA-N molybdenum vanadium Chemical compound [V].[Mo] WUJISAYEUPRJOG-UHFFFAOYSA-N 0.000 description 1

- 239000002105 nanoparticle Substances 0.000 description 1

- RUFLMLWJRZAWLJ-UHFFFAOYSA-N nickel silicide Chemical compound [Ni]=[Si]=[Ni] RUFLMLWJRZAWLJ-UHFFFAOYSA-N 0.000 description 1

- 229910021334 nickel silicide Inorganic materials 0.000 description 1

- 239000012299 nitrogen atmosphere Substances 0.000 description 1

- JCXJVPUVTGWSNB-UHFFFAOYSA-N nitrogen dioxide Inorganic materials O=[N]=O JCXJVPUVTGWSNB-UHFFFAOYSA-N 0.000 description 1

- TVMXDCGIABBOFY-UHFFFAOYSA-N octane Chemical compound CCCCCCCC TVMXDCGIABBOFY-UHFFFAOYSA-N 0.000 description 1

- 230000001151 other effect Effects 0.000 description 1

- 230000035515 penetration Effects 0.000 description 1

- 230000000737 periodic effect Effects 0.000 description 1

- 230000035699 permeability Effects 0.000 description 1

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 1

- 238000012805 post-processing Methods 0.000 description 1

- 239000010453 quartz Substances 0.000 description 1

- 239000002994 raw material Substances 0.000 description 1

- 239000011435 rock Substances 0.000 description 1

- 229910052594 sapphire Inorganic materials 0.000 description 1

- 239000010980 sapphire Substances 0.000 description 1

- 238000000926 separation method Methods 0.000 description 1

- 229910000077 silane Inorganic materials 0.000 description 1

- 229910052709 silver Inorganic materials 0.000 description 1

- 239000004332 silver Substances 0.000 description 1

- 239000002002 slurry Substances 0.000 description 1

- 238000004528 spin coating Methods 0.000 description 1

- CIOAGBVUUVVLOB-UHFFFAOYSA-N strontium atom Chemical compound [Sr] CIOAGBVUUVVLOB-UHFFFAOYSA-N 0.000 description 1

- 238000006467 substitution reaction Methods 0.000 description 1

- 239000013589 supplement Substances 0.000 description 1

- 230000008646 thermal stress Effects 0.000 description 1

- XOLBLPGZBRYERU-UHFFFAOYSA-N tin dioxide Chemical compound O=[Sn]=O XOLBLPGZBRYERU-UHFFFAOYSA-N 0.000 description 1

- 229910001887 tin oxide Inorganic materials 0.000 description 1

- 230000009466 transformation Effects 0.000 description 1

- GPPXJZIENCGNKB-UHFFFAOYSA-N vanadium Chemical compound [V]#[V] GPPXJZIENCGNKB-UHFFFAOYSA-N 0.000 description 1

- 238000007740 vapor deposition Methods 0.000 description 1

- 230000008016 vaporization Effects 0.000 description 1

- 230000000007 visual effect Effects 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/7869—Thin film transistors, i.e. transistors with a channel being at least partly a thin film having a semiconductor body comprising an oxide semiconductor material, e.g. zinc oxide, copper aluminium oxide, cadmium stannate

-

- H01L27/1052—

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1203—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body the substrate comprising an insulating body on a semiconductor body, e.g. SOI

- H01L27/1207—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body the substrate comprising an insulating body on a semiconductor body, e.g. SOI combined with devices in contact with the semiconductor body, i.e. bulk/SOI hybrid circuits

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/1222—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs with a particular composition, shape or crystalline structure of the active layer

- H01L27/1225—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs with a particular composition, shape or crystalline structure of the active layer with semiconductor materials not belonging to the group IV of the periodic table, e.g. InGaZnO

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/1248—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs with a particular composition or shape of the interlayer dielectric specially adapted to the circuit arrangement

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/1255—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs integrated with passive devices, e.g. auxiliary capacitors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/43—Electrodes ; Multistep manufacturing processes therefor characterised by the materials of which they are formed

- H01L29/49—Metal-insulator-semiconductor electrodes, e.g. gates of MOSFET

- H01L29/4908—Metal-insulator-semiconductor electrodes, e.g. gates of MOSFET for thin film semiconductor, e.g. gate of TFT

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/43—Electrodes ; Multistep manufacturing processes therefor characterised by the materials of which they are formed

- H01L29/49—Metal-insulator-semiconductor electrodes, e.g. gates of MOSFET

- H01L29/51—Insulating materials associated therewith

- H01L29/511—Insulating materials associated therewith with a compositional variation, e.g. multilayer structures

- H01L29/513—Insulating materials associated therewith with a compositional variation, e.g. multilayer structures the variation being perpendicular to the channel plane

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66969—Multistep manufacturing processes of devices having semiconductor bodies not comprising group 14 or group 13/15 materials

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78645—Thin film transistors, i.e. transistors with a channel being at least partly a thin film with multiple gate

- H01L29/78648—Thin film transistors, i.e. transistors with a channel being at least partly a thin film with multiple gate arranged on opposing sides of the channel

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78696—Thin film transistors, i.e. transistors with a channel being at least partly a thin film characterised by the structure of the channel, e.g. multichannel, transverse or longitudinal shape, length or width, doping structure, or the overlap or alignment between the channel and the gate, the source or the drain, or the contacting structure of the channel

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B99/00—Subject matter not provided for in other groups of this subclass

Abstract

전기 특성이 안정적인 반도체 장치를 제공한다. 또는, 메세화 또는 고집적화에 적합한 신뢰성이 높은 반도체 장치를 제공한다. 반도체 장치는 제 1 배리어층, 제 2 배리어층, 제 3 배리어층, 산화물을 포함하는 트랜지스터, 절연체, 및 도전체를 포함한다. 절연체는 산소 과잉 영역을 포함한다. 절연체 및 산화물은 제 1 배리어층과 제 2 배리어층 사이에 있다. 도전체는 제 3 배리어층을 개재하여, 제 1 배리어층의 개구, 제 2 배리어층의 개구, 및 절연체의 개구에 있다.

Description

본 발명의 일 형태는 반도체 장치 및 그 제작 방법에 관한 것이다. 본 발명의 다른 일 형태는 전자 기기에 관한 것이다.

또한, 본 발명의 일 형태는 상기 기술분야에 한정되지 않는다. 본 명세서 등에 개시(開示)된 발명의 일 형태는 물건, 방법, 또는 제작 방법에 관한 것이다. 또한 본 발명의 일 형태는 공정(process), 기계(machine), 제품(manufacture), 또는 조성물(composition of matter)에 관한 것이다.

본 명세서 등에서 반도체 장치는 일반적으로, 반도체 특성을 이용함으로써 기능할 수 있는 장치를 의미한다. 표시 장치(예를 들어 액정 표시 장치 또는 발광 표시 장치), 투영 장치, 조명 장치, 전기 광학 장치, 축전 장치, 기억 장치, 반도체 회로, 촬상 장치, 및 전자 기기 등은 반도체 장치를 포함할 수 있다.

트랜지스터를 반도체 박막을 사용하여 형성하는 기술이 주목을 받고 있다. 이러한 트랜지스터는 집적 회로(IC) 및 화상 표시 장치(단순히 표시 장치라고도 함) 등의 광범위의 전자 기기에 적용되고 있다. 트랜지스터에 적용 가능한 반도체 박막의 재료로서 실리콘계 반도체 재료가 널리 알려져 있다. 다른 재료로서는 산화물 반도체가 주목을 받고 있다.

예를 들어, 산화물 반도체로서, 활성층이 산화 아연 또는 In-Ga-Zn계 산화물로 이루어지는 트랜지스터를 사용하여 표시 장치를 제작하는 기술이 각각 개시되어 있다(특허문헌 1 및 특허문헌 2 참조).

또한, 근년에 들어, 산화물 반도체를 포함하는 트랜지스터를 사용하여 기억 장치의 집적 회로를 제작하는 기술이 개시되어 있다(특허문헌 3 참조). 또한, 기억 장치뿐만 아니라 연산 장치 또는 그 외의 장치도, 산화물 반도체를 포함하는 트랜지스터를 사용하여 제작되고 있다.

그러나, 활성층으로서 산화물 반도체를 포함하는 트랜지스터는, 산화물 반도체 내의 불순물 및 산소 결손에 의하여 전기 특성이 쉽게 변화되기 때문에 신뢰성이 낮다는 문제를 갖는 것이 알려져 있다. 예를 들어, 바이어스 온도 스트레스 시험(BT 시험) 후에 트랜지스터의 문턱 전압이 변화되는 경우가 있다.

본 발명의 일 형태의 과제는 전기 특성이 양호한 반도체 장치를 제공하는 것이다. 본 발명의 일 형태의 다른 과제는 신뢰성이 높은 반도체 장치를 제공하는 것이다. 본 발명의 일 형태의 다른 과제는 미세화 또는 고집적화가 가능한 반도체 장치를 제공하는 것이다. 본 발명의 일 형태의 다른 과제는 높은 생산성으로 제작할 수 있는 반도체 장치를 제공하는 것이다.

본 발명의 일 형태의 다른 과제는 오랫동안 데이터를 유지할 수 있는 반도체 장치를 제공하는 것이다. 본 발명의 일 형태의 다른 과제는 고속으로 데이터를 기록할 수 있는 반도체 장치를 제공하는 것이다. 본 발명의 일 형태의 다른 과제는 설계의 유연성이 높은 반도체 장치를 제공하는 것이다. 본 발명의 일 형태의 다른 과제는 저전력의 반도체 장치를 제공하는 것이다. 본 발명의 일 형태의 다른 과제는 신규 반도체 장치를 제공하는 것이다.

또한 이들 과제의 기재는 다른 과제의 존재를 방해하지 않는다. 본 발명의 일 형태에서 모든 과제를 달성할 필요는 없다. 다른 과제는 명세서, 도면, 및 청구항 등의 기재로부터 명백해질 것이며 추출될 수 있다.

본 발명의 일 형태에서는, 과잉 산소를 산화물 반도체 근방의 산화물 절연체로부터 산화물 반도체에 공급하여 산화물 반도체 내의 산소 결손을 저감시킨다.

또한, 산화물 반도체 근방의 다른 구성 요소 등으로부터의 물 및 수소 등의 불순물이 산화물 반도체에 들어가는 것을 방지할 수 있다. 외부로부터 산화물 반도체에 수소 등의 불순물이 들어가는 것을 방지하기 위하여, 물 및 수소 등의 불순물에 대한 배리어성을 갖는 절연체가 산화물 반도체를 덮도록 형성된다.

물 및 수소 등의 불순물에 대한 배리어성을 갖는 절연체의 산소 투과성을 낮게 한다. 이에 의하여, 산소의 외부 확산을 방지할 수 있고, 산화물 반도체 및 산화물 반도체 근방의 산화물 절연체에 산소를 효율적으로 공급할 수 있다.

이러한 식으로, 산화물 반도체 및 주위의 산화물 절연체에 포함되는 물 및 수소 등의 불순물을 저감할 수 있고, 산화물 반도체 내의 산소 결손을 저감할 수 있다.

본 발명의 일 형태는 제 1 배리어층, 제 2 배리어층, 제 3 배리어층, 산화물을 포함하는 트랜지스터, 절연체, 및 도전체를 포함한다. 절연체는 산소 과잉 영역을 포함한다. 절연체 및 산화물은 제 1 배리어층과 제 2 배리어층 사이에 있다. 도전체는 제 1 배리어층의 개구, 제 2 배리어층의 개구, 및 절연체의 개구에 있다. 제 3 배리어층은 도전체와, 제 1 배리어층, 제 2 배리어층, 및 절연체와의 사이에 있다.

본 발명의 일 형태는 제 1 배리어층, 제 2 배리어층, 제 3 배리어층, 산화물을 포함하는 트랜지스터, 절연체, 및 트랜지스터에 전기적으로 접속되는 도전체를 포함한다. 절연체는 산소 과잉 영역을 포함한다. 절연체 및 산화물은 제 1 배리어층과 제 2 배리어층 사이에 있다. 도전체는 제 1 배리어층의 개구 및 절연체의 개구에 있다. 제 3 배리어층은 도전체와, 제 1 배리어층 및 절연체와의 사이에 있다.

본 발명의 일 형태는 제 1 배리어층, 제 2 배리어층, 제 3 배리어층, 산화물을 포함하는 트랜지스터, 절연체, 제 1 도전체, 및 제 2 도전체를 포함한다. 절연체는 산소 과잉 영역을 포함한다. 제 2 도전체는 트랜지스터에 전기적으로 접속된다. 절연체 및 산화물은 제 1 배리어층과 제 2 배리어층 사이에 있다. 제 1 도전체는 제 1 배리어층의 개구, 제 2 배리어층의 개구, 및 절연체의 개구에 있다. 제 3 배리어층은 제 1 도전체와, 제 1 배리어층, 제 2 배리어층, 및 절연체와의 사이에 있다. 제 2 도전체는 제 1 배리어층의 개구 및 절연체의 개구에 있다. 제 3 배리어층은 제 2 도전체와, 제 1 배리어층 및 절연체와의 사이에 있다.

상기 구조 중 임의의 것에서, 제 1 배리어층의 개구의 측면 및 제 2 배리어층의 개구의 측면이 제 3 배리어층과 접촉함으로써, 트랜지스터 및 절연체가 제 1 배리어층, 제 2 배리어층, 및 제 3 배리어층에 의하여 밀봉된다.

상기 구조 중 임의의 것에서, 400℃ 이하의 온도에서 TDS에 의하여 측정될 때, 제 1 배리어층, 제 2 배리어층, 또는 제 3 배리어층 아래의 구성 요소로부터의 수소의 방출량은 5.0×1014/cm2 이하이어도 좋다.

상기 구조 중 임의의 것은 개구를 갖는 제 2 절연체 및 개구를 갖는 제 3 절연체를 포함하여도 좋다. 제 2 절연체는 제 2 배리어층 위에 있다. 제 3 절연체는 제 1 배리어층 아래에 있다. 제 2 절연체의 개구의 측면 및 제 3 절연체의 개구의 측면은 각각 제 3 배리어층으로 덮인 영역을 갖는다.

상기 구조 중 임의의 것에서, 제 1 배리어층은 트랜지스터의 게이트 절연막으로서 기능하여도 좋다.

본 발명의 일 형태에 따르면, 산화물 반도체를 포함하며 전기 특성이 안정적인 트랜지스터를 포함하는 반도체 장치를 제공할 수 있다. 본 발명의 일 형태에 따르면, 설계의 유연성이 높은 반도체 장치를 제공할 수 있다.

본 발명의 일 형태에 따르면, 전기 특성이 양호한 반도체 장치를 제공할 수 있다. 본 발명의 일 형태에 따르면, 신뢰성이 높은 반도체 장치를 제공할 수 있다. 본 발명의 일 형태에 따르면, 미세화 또는 고집적화가 가능한 반도체 장치를 제공할 수 있다. 본 발명의 일 형태에 따르면, 높은 생산성으로 제작할 수 있는 반도체 장치를 제공할 수 있다.

본 발명의 일 형태에 따르면, 오랫동안 데이터를 유지할 수 있는 반도체 장치를 제공할 수 있다. 본 발명의 일 형태에 따르면, 고속으로 데이터를 기록할 수 있는 반도체 장치를 제공할 수 있다. 본 발명의 일 형태에 따르면, 저전력의 반도체 장치를 제공할 수 있다. 본 발명의 일 형태에 따르면, 신규 반도체 장치를 제공할 수 있다.

또한 이들 효과의 기재는 다른 과제의 존재를 방해하지 않는다. 본 발명의 일 형태는 모든 효과를 반드시 실현할 필요는 없다. 다른 효과는 명세서, 도면, 및 청구항 등의 기재로부터 명백해질 것이며 추출될 수 있다.

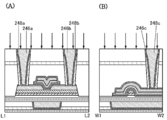

도 1의 (A) 내지 (C)는 본 발명의 일 형태의 반도체 장치의 구조를 도시한 상면도 및 단면도이다.

도 2의 (A) 내지 (J)는 본 발명의 일 형태의 반도체 장치의 제작 방법을 도시한 단면도이다.

도 3의 (A) 내지 (H)는 본 발명의 일 형태의 반도체 장치의 제작 방법을 도시한 단면도이다.

도 4의 (A) 내지 (H)는 본 발명의 일 형태의 반도체 장치의 제작 방법을 도시한 단면도이다.

도 5의 (A) 내지 (F)는 본 발명의 일 형태의 반도체 장치의 제작 방법을 도시한 단면도이다.

도 6의 (A) 내지 (D)는 본 발명의 일 형태의 반도체 장치의 제작 방법을 도시한 단면도이다.

도 7의 (A) 내지 (D)는 본 발명의 일 형태의 반도체 장치의 제작 방법을 도시한 단면도이다.

도 8의 (A) 내지 (D)는 본 발명의 일 형태의 반도체 장치의 제작 방법을 도시한 단면도이다.

도 9의 (A) 및 (B)는 본 발명의 일 형태의 반도체 장치의 제작 방법을 도시한 단면도이다.

도 10의 (A) 내지 (C)는 본 발명의 일 형태의 반도체 장치의 구조를 도시한 상면도 및 단면도이다.

도 11의 (A) 내지 (C)는 본 발명의 일 형태의 반도체 장치의 구조를 도시한 상면도 및 단면도이다.

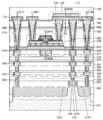

도 12는 본 발명의 일 형태의 반도체 장치의 구조를 도시한 단면도이다.

도 13은 본 발명의 일 형태의 반도체 장치의 구조를 도시한 단면도이다.

도 14는 본 발명의 일 형태의 반도체 장치의 구조를 도시한 단면도이다.

도 15는 본 발명의 일 형태의 반도체 장치의 구조를 도시한 단면도이다.

도 16의 (A) 내지 (C)는 각각 실시예의 구조를 도시한 것이다.

도 17의 (A) 내지 (F)는 실시예의 TDS 결과를 나타낸 것이다.

도 18의 (A) 및 (B)는 각각 실시예의 구조를 도시한 것이다.

도 19의 (A) 내지 (D)는 실시예의 TDS 결과를 나타낸 것이다.

도 20의 (A) 및 (B)는 실시예의 구조의 단면도, 및 STEM 이미지이다.

도 21은 실시예의 I d-V g 특성을 나타낸 것이다.

도 22의 (A) 및 (B)는 실시예의 구조, 및 TDS 결과를 나타낸 것이다.

도 23의 (A) 내지 (D)는 실시예의 구조의 단면도, 및 STEM 이미지이다.

도 24의 (A)는 실시예의 시료의 접촉 저항을 나타낸 것이고, 도 24의 (B) 및 (C)는 EDX 매핑 이미지를 나타낸 것이다.

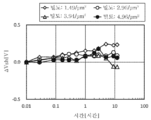

도 25는 실시예의 I d-V g 특성을 나타낸 것이다.

도 26은 실시예의 I d-V g 특성을 나타낸 것이다.

도 27은 실시예의 시료의 접촉 저항을 나타낸 것이다.

도 28은 실시예의 시료의 GBT 스트레스 시험의 결과를 나타낸 것이다.

도 2의 (A) 내지 (J)는 본 발명의 일 형태의 반도체 장치의 제작 방법을 도시한 단면도이다.

도 3의 (A) 내지 (H)는 본 발명의 일 형태의 반도체 장치의 제작 방법을 도시한 단면도이다.

도 4의 (A) 내지 (H)는 본 발명의 일 형태의 반도체 장치의 제작 방법을 도시한 단면도이다.

도 5의 (A) 내지 (F)는 본 발명의 일 형태의 반도체 장치의 제작 방법을 도시한 단면도이다.

도 6의 (A) 내지 (D)는 본 발명의 일 형태의 반도체 장치의 제작 방법을 도시한 단면도이다.

도 7의 (A) 내지 (D)는 본 발명의 일 형태의 반도체 장치의 제작 방법을 도시한 단면도이다.

도 8의 (A) 내지 (D)는 본 발명의 일 형태의 반도체 장치의 제작 방법을 도시한 단면도이다.

도 9의 (A) 및 (B)는 본 발명의 일 형태의 반도체 장치의 제작 방법을 도시한 단면도이다.

도 10의 (A) 내지 (C)는 본 발명의 일 형태의 반도체 장치의 구조를 도시한 상면도 및 단면도이다.

도 11의 (A) 내지 (C)는 본 발명의 일 형태의 반도체 장치의 구조를 도시한 상면도 및 단면도이다.

도 12는 본 발명의 일 형태의 반도체 장치의 구조를 도시한 단면도이다.

도 13은 본 발명의 일 형태의 반도체 장치의 구조를 도시한 단면도이다.

도 14는 본 발명의 일 형태의 반도체 장치의 구조를 도시한 단면도이다.

도 15는 본 발명의 일 형태의 반도체 장치의 구조를 도시한 단면도이다.

도 16의 (A) 내지 (C)는 각각 실시예의 구조를 도시한 것이다.

도 17의 (A) 내지 (F)는 실시예의 TDS 결과를 나타낸 것이다.

도 18의 (A) 및 (B)는 각각 실시예의 구조를 도시한 것이다.

도 19의 (A) 내지 (D)는 실시예의 TDS 결과를 나타낸 것이다.

도 20의 (A) 및 (B)는 실시예의 구조의 단면도, 및 STEM 이미지이다.

도 21은 실시예의 I d-V g 특성을 나타낸 것이다.

도 22의 (A) 및 (B)는 실시예의 구조, 및 TDS 결과를 나타낸 것이다.

도 23의 (A) 내지 (D)는 실시예의 구조의 단면도, 및 STEM 이미지이다.

도 24의 (A)는 실시예의 시료의 접촉 저항을 나타낸 것이고, 도 24의 (B) 및 (C)는 EDX 매핑 이미지를 나타낸 것이다.

도 25는 실시예의 I d-V g 특성을 나타낸 것이다.

도 26은 실시예의 I d-V g 특성을 나타낸 것이다.

도 27은 실시예의 시료의 접촉 저항을 나타낸 것이다.

도 28은 실시예의 시료의 GBT 스트레스 시험의 결과를 나타낸 것이다.

실시형태에 대하여 도면을 참조하여 이하에서 설명한다. 또한 실시형태는 많은 다른 형태로 실행할 수 있다. 본 발명의 취지 및 범위에서 벗어남이 없이 형태 및 자세한 사항이 다양하게 변경될 수 있다는 것은 통상의 기술자에 의하여 쉽게 이해될 것이다. 그러므로, 본 발명은 이하의 실시형태의 설명에 한정되어 해석되지 말아야 한다.

도면에서, 크기, 층의 두께, 또는 영역은 명료화를 위하여 과장되어 있는 경우가 있다. 그러므로, 본 발명의 형태는 이러한 스케일에 한정되지 않는다. 또한, 도면은 이상적인 예를 도시한 모식도이고, 본 발명의 형태는 도면에 도시된 형상 또는 값에 한정되지 않는다. 도면에서, 같은 부분 또는 비슷한 기능을 갖는 부분은 상이한 도면에서 같은 부호로 나타내고, 그 설명은 반복하지 않는다. 또한, 비슷한 기능을 갖는 부분에는 같은 해칭 패턴을 적용하고, 이 부분을 부호로 나타내지 않는 경우가 있다.

또한, 본 명세서 등에서 "제 1" 및 "제 2" 등의 서수는 편의상 사용되며, 공정 순서 또는 층의 적층 순서를 나타내지 않는다. 그러므로, 예를 들어, "제 1"을 "제 2" 또는 "제 3"으로 적절히 바꿔도 설명할 수 있다. 또한, 본 명세서 등에서의 서수는 본 발명의 일 형태를 특정하는 것과 반드시 같을 필요는 없다.

본 명세서에서, "위에" 및 "아래에" 등, 배치를 설명하기 위한 용어는, 도면을 참조하여 구성 요소들 사이의 위치 관계를 설명하기 위하여 편의상 사용된다. 구성 요소들 사이의 위치 관계는 각 구성 요소를 기재하는 방향에 따라 적절히 변화된다. 따라서, 본 명세서에서 사용되는 용어에 대한 한정은 없고, 상황에 따라 적절히 설명할 수 있다.

본 명세서 등에서, 트랜지스터는 게이트, 드레인, 및 소스의 적어도 3개의 단자를 갖는 소자이다. 트랜지스터는 드레인(드레인 단자, 드레인 영역, 또는 드레인 전극)과 소스(소스 단자, 소스 영역, 또는 소스 전극) 사이에 채널 영역을 포함하고, 채널 형성 영역을 통하여 드레인과 소스 사이에 전류를 흘릴 수 있다. 또한, 본 명세서 등에서, 채널 영역이란, 전류가 주로 흐르는 영역을 말한다.

"소스" 및 "드레인'의 기능은 예를 들어 반대 극성의 트랜지스터를 사용할 때 또는 회로 동작에서 전류가 흐르는 방향이 변화될 때, 서로 바뀌는 경우가 있다. 따라서, 본 명세서 등에서 "소스" 및 "드레인"이라는 용어는 서로 바꿀 수 있다.

또한 채널 길이란 예를 들어 트랜지스터의 상면도에서 반도체(또는 트랜지스터가 온일 때 반도체에서 전류가 흐르는 부분)와 게이트 전극이 서로 중첩되는 영역 또는 채널이 형성되는 영역에서의 소스(소스 영역 또는 소스 전극)와 드레인(드레인 영역 또는 드레인 전극) 사이의 거리를 말한다. 하나의 트랜지스터에서, 채널 길이는 모든 영역에서 반드시 같을 필요는 없다. 바꿔 말하면 하나의 트랜지스터의 채널 길이는 하나의 값에 한정되지 않는 경우가 있다. 그러므로, 본 명세서에서 채널 길이는, 채널이 형성되는 영역에서의 어느 하나의 값, 최대값, 최소값, 또는 평균값이다.

채널 폭이란 예를 들어, 반도체(또는 트랜지스터가 온일 때 반도체에서 전류가 흐르는 부분)와 게이트 전극이 서로 중첩되는 영역, 또는 채널이 형성되는 영역에서 소스와 드레인이 서로 대향하는 부분의 길이를 말한다. 하나의 트랜지스터에서, 채널 폭은 모든 영역에서 반드시 같을 필요는 없다. 바꿔 말하면, 하나의 트랜지스터의 채널 폭은 하나의 값으로 고정되지 않는 경우가 있다. 그러므로, 본 명세서에서 채널 폭은, 채널이 형성되는 영역에서의 어느 하나의 값, 최대값, 최소값, 또는 평균값이다.

또한, 트랜지스터 구조에 따라, 실제로 채널이 형성되는 영역에서의 채널 폭(이하, "실효적인 채널 폭"이라고 함)은 트랜지스터의 상면도에 나타낸 채널 폭(이하, "외견상 채널 폭"이라고 함)과 상이한 경우가 있다. 예를 들어, 반도체의 측면을 덮는 게이트 전극을 갖는 트랜지스터에서는 실효적인 채널 폭이 외견상 채널 폭보다 크고, 그 영향을 무시할 수 없는 경우가 있다. 예를 들어 반도체의 측면을 덮는 게이트 전극을 갖는 미세한 트랜지스터에서는 반도체의 측면에 형성되는 채널 형성 영역의 비율이 증가되는 경우가 있다. 이 경우, 실효적인 채널 폭이 외견상 채널 폭보다 크다.

이러한 경우, 실효적인 채널 폭을 측정하기 어려운 경우가 있다. 예를 들어, 설계값으로부터의 실효적인 채널 폭의 추산에는, 반도체의 형상을 알고 있다는 가정이 요구된다. 그러므로 반도체의 형상을 정확하게 모르는 경우에는 실효적인 채널 폭을 정확하게 측정하기 어렵다.

따라서, 본 명세서에서는 외견상 채널 폭을 "SCW(surrounded channel width)"라고 하는 경우가 있다. 또한, 본 명세서에서 단순히 "채널 폭"이라는 용어를 사용하는 경우에는 SCW 또는 외견상 채널 폭을 나타낼 수 있다. 또는, 본 명세서에서 단순히 "채널 폭"이라는 용어를 사용하는 경우에는 실효적인 채널 폭을 나타내는 경우가 있다. 또한 채널 길이, 채널 폭, 실효적인 채널 폭, 외견상 채널 폭, 및 SCW 등의 값은 단면 TEM 이미지 등을 분석함으로써 결정할 수 있다.

또한, 트랜지스터의 전계 효과 이동도 및 채널 폭당 전류값 등을 계산하여 얻는 경우, SCW가 계산에 사용되어도 좋다. 이 경우, 값은 실효적인 채널 폭을 사용하여 계산한 것과 상이한 경우가 있다.

본 명세서 등에서, "전기적으로 접속"이라는 용어는 구성 요소가 "어떠한 전기적 기능을 갖는 물체"를 통하여 접속되어 있는 경우를 포함한다. "어떠한 전기적 기능을 갖는 물체"에는, 그 물체를 통하여 접속된 구성 요소들 사이에서 전기 신호가 송수신될 수 있기만 하면, 특별한 제한은 없다. "어떠한 전기적 기능을 갖는 물체"의 예에는 전극 및 배선뿐만 아니라, 트랜지스터 등의 스위칭 소자, 저항 소자, 인덕터, 용량 소자, 및 다양한 기능을 갖는 소자가 포함된다.

또한 본 명세서 등에서, 질화 산화물이란 산소보다 질소를 더 포함하는 화합물을 말한다. 산화 질화물이란 질소보다 산소를 더 포함하는 화합물을 말한다. 각 원소의 함유량은, 예를 들어 RBS(Rutherford backscattering spectrometry)에 의하여 측정될 수 있다.

본 명세서 등에서 "막" 및 "층"이라는 용어는 서로 바꿀 수 있다. 예를 들어, "도전층"이라는 용어는 "도전막"이라는 용어로 바꿀 수 있는 경우가 있다. 또한, "절연막"이라는 용어를 "절연층"이라는 용어로 바꿀 수 있는 경우가 있다.

본 명세서 등에서, "평행"이란 용어는 2개의 직선 사이에 형성되는 각도가 -10° 이상 10° 이하인 것을 나타내기 때문에, 상기 각도가 -5° 이상 5° 이하인 경우도 포함한다. 또한, "실질적으로 평행"이라는 용어는 2개의 직선 사이에 형성되는 각도가 -30° 이상 30° 이하인 것을 나타낸다. 또한, "수직"이란 용어는 2개의 직선 사이에 형성되는 각도가 80° 이상 100° 이하인 것을 나타내기 때문에 상기 각도가 85° 이상 95° 이하인 경우도 포함한다. 또한 "실질적으로 수직"이라는 용어는 2개의 직선 사이에 형성되는 각도가 60° 이상 120° 이하인 것을 나타낸다.

본 명세서에서, 삼방정계 및 능면체정계(rhombohedral crystal system)는 육방정계에 포함된다.

또한 본 명세서에서, 배리어막이란 산소, 및 수소 등의 불순물의 투과를 억제하는 기능을 갖는 막을 말한다. 도전성을 갖는 배리어막을 도전성 배리어막이라고 할 수 있다.

본 명세서 등에서, 노멀리 온 특성을 갖는 트랜지스터는, 전원에 의하여 전위가 인가되지 않는 경우(0V)에 온이 되는 트랜지스터이다. 예를 들어, 트랜지스터의 노멀리 온 특성은, 트랜지스터의 게이트에 공급되는 전압(V g)이 0V인 경우에 트랜지스터의 문턱 전압이 음이 되는 전기 특성을 의미하는 경우가 있다.

본 명세서 등에서, 금속 산화물은 넓은 의미에서 금속의 산화물을 의미한다. 금속 산화물은 산화물 절연체, 산화물 도전체(투명 산화물 도전체를 포함함), 및 산화물 반도체(단순히 OS라고도 함) 등으로 분류된다. 예를 들어, 트랜지스터의 활성층에 사용한 금속 산화물을 산화물 반도체라고 부르는 경우가 있다. 바꿔 말하면, OS FET는 금속 산화물 또는 산화물 반도체를 포함하는 트랜지스터이다.

(실시형태 1)

본 실시형태에서는, 반도체 장치의 일 형태에 대하여 도 1의 (A) 내지 (C), 도 2의 (A) 내지 (J), 도 3의 (A) 내지 (H), 도 4의 (A) 내지 (H), 도 5의 (A) 내지 (F), 도 6의 (A) 내지 (D), 도 7의 (A) 내지 (D), 도 8의 (A) 내지 (D), 도 9의 (A) 및 (B), 도 10의 (A) 내지 (C), 및 도 11의 (A) 내지 (C)를 참조하여 설명한다.

<반도체 장치의 구조>

이하에서, 본 발명의 일 형태의 반도체 장치의 예에 대하여 설명한다. 도 1의 (A) 내지 (C)는 본 발명의 일 형태의 트랜지스터(200), 및 트랜지스터(200)에 전기적으로 접속되는 플러그를 도시한 상면도 및 단면도이다. 도 1의 (A)는 상면도이고, 도 1의 (B)는 도 1의 (A)에서의 일점쇄선 L1-L2를 따라 취한 단면도이고, 도 1의 (C)는 일점쇄선 W1-W2를 따라 취한 단면도이다. 도면의 명료화를 위하여, 일부의 구성 요소를 도 1의 (A)의 상면도에 도시하지 않았다.

본 발명의 일 형태의 반도체 장치는 트랜지스터(200), 층간막으로서 기능하는 절연체(280, 282, 및 286), 절연체(280 및 282)의 개구의 측면을 덮는 배리어층(276)(배리어층(276a, 276b, 및 276c)), 및 층간막으로서 기능하는 절연체(280, 282, 및 286)의 개구에 제공되는 도전체(246)(도전체(246a, 246b, 및 246c)) 및 도전체(248)(도전체(248a, 248b, 및 248c))를 포함한다. 배리어층(276)은 도전체(246 및 248)와 절연체(280, 282, 및 286) 사이에 있다.

반도체 장치에서, 도전체(246 및 248)는 플러그 또는 배선으로서 기능한다. 또한 본 명세서 등에서, 배선 및 배선에 전기적으로 접속되는 플러그가 하나의 구성 요소이어도 좋다. 즉, 도전체의 일부가 배선으로서 기능하고, 도전체의 다른 부분이 플러그로서 기능하는 경우가 있다.

트랜지스터(200)는, 제 1 게이트 전극으로서 기능하는 도전체(260)(도전체(260a) 및 도전체(260b)를 포함함), 제 2 게이트 전극으로서 기능하는 도전체(205)(도전체(205a) 및 도전체(205b)를 포함함), 도전체(260)와 접촉하는 배리어층(270), 게이트 절연층으로서 기능하는 절연체(220, 222, 및 224) 및 절연체(250), 채널이 형성되는 영역을 포함하는 산화물(230)(산화물(230a), 산화물(230b), 및 산화물(230c)을 포함함), 소스 및 드레인 중 한쪽으로서 기능하는 도전체(240a), 소스 및 드레인 중 다른 쪽으로서 기능하는 도전체(240b), 및 도전체(240)(도전체(240a 및 240b))와 접촉하는 배리어층(244)(배리어층(244a 및 244b))을 포함한다.

트랜지스터(200)에서, 산화물(230)은 산화물 반도체로서 기능하는 금속 산화물(이하, 금속 산화물을 산화물 반도체라고도 함)을 사용하여 형성하는 것이 바람직하다. 산화물 반도체를 사용하여 형성되는 트랜지스터는 오프 상태에서의 누설 전류가 매우 낮기 때문에, 소비전력이 낮은 반도체 장치를 제공할 수 있다. 산화물 반도체는 스퍼터링법 등으로 형성할 수 있기 때문에 고집적화된 반도체 장치에 포함되는 트랜지스터에 사용할 수 있다.

그러나, 산화물 반도체를 사용하여 형성되는 트랜지스터는 산화물 반도체 내의 불순물 및 산소 결손에 의하여 그 전기 특성이 변화되기 쉬워, 그 결과, 신뢰성이 저하되는 경우가 있다. 산화물 반도체에 포함되는 수소는 금속 원자와 결합되는 산소와 반응하여 물이 되기 때문에, 산소 결손을 발생시키는 경우가 있다. 산소 결손에 수소가 들어가는 것으로 인하여, 캐리어로서 기능하는 전자가 생성되는 경우가 있다. 또한, 수소의 일부가 금속 원자와 결합되는 산소와 결합됨으로써, 캐리어로서 기능하는 전자가 생성되는 경우가 있다. 따라서, 수소를 포함한 산화물 반도체를 포함하는 트랜지스터는 노멀리 온이 되기 쉽다. 따라서, 산화물 반도체 내의 수소는 가능한 한 저감되어 있는 것이 바람직하다.

따라서, 트랜지스터(200) 근방에 제공되는 절연막으로서 기능하는 절연체(280)는 산화 실리콘막 또는 산화 질화 실리콘막 등, 산소를 포함하는 절연체인 것이 바람직하다.

절연체(280)는 화학량론적 조성보다 높은 비율로 산소를 포함하는 산화물을 사용하여 형성되는 것이 특히 바람직하다. 즉, 절연체(280)는 화학량론적 조성을 초과하여 산소를 포함하는 영역(이하, 산소 과잉 영역이라고도 함)을 갖는 것이 바람직하다. 특히, 산소 과잉 영역을 갖는 절연체를 트랜지스터(200) 근방의 층간막에 제공하면, 트랜지스터(200)에 포함되는 산화물(230) 내의 산소 결손을 저감할 수 있어, 신뢰성이 향상될 수 있다.

산소 과잉 영역을 포함하는 절연체로서는, 구체적으로 가열에 의하여 산소의 일부가 방출되는 산화물 재료를 사용하는 것이 바람직하다. 가열에 의하여 산소의 일부가 방출되는 산화물은, TDS(thermal desorption spectroscopy) 분석에 있어서 산소 원자로 환산한 산소의 방출량이 1.0×1018atoms/cm3 이상, 바람직하게는 3.0×1020atoms/cm3 이상인 산화물막이다. 또한, TDS 분석에서의 막의 표면 온도는 바람직하게는 100℃ 이상 700℃ 이하, 또는 100℃ 이상 500℃ 이하이다.

예를 들어, 산화 실리콘 또는 산화 질화 실리콘을 포함하는 재료를 사용할 수 있다. 또는, 금속 산화물을 사용할 수 있다. 또한, 본 명세서에서, "산화 질화 실리콘"이란 질소보다 높은 비율로 산소를 포함하는 재료를 말하고, "질화 산화 실리콘"이란 산소보다 높은 비율로 질소를 포함하는 재료를 말한다.

또한, 절연체(280)가 산소 과잉 영역을 포함하는 경우, 절연체(282)는 산소, 수소, 및 물에 대한 배리어성을 갖는 것이 바람직하다. 절연체(282)가 산소에 대한 배리어성을 가지면, 산소 과잉 영역의 산소가 절연체(286) 측으로 확산되지 않고 산화물(230)에 효율적으로 공급된다.

또한, 규정되지 않는 한, 본 명세서에서의 "배리어성"이라는 용어는, 적어도 수소 및 물로 대표되는 불순물의 확산을 억제하는 기능을 말한다. 예를 들어, 수소의 확산은 350℃, 바람직하게는 400℃의 분위기에서 억제된다. 예를 들어 수소를 방출하는 제 1 막, 및 그 위에 적층된 임의의 제 2 막을 포함하는 구조에는 400℃ 이하의 온도에서 TDS 측정이 수행되고, 수소의 방출량이 5.0×1014/cm2 이하인 경우, 제 2 막은 수소에 대한 배리어성을 갖는 것으로 간주된다. 수소의 방출량은 400℃ 이하의 온도에서 3.4×1014/cm2 이하인 것이 바람직하고, 500℃ 이하의 온도에서 7.1×1014/cm2 이하인 것이 더 바람직하고, 600℃ 이하의 온도에서 1.4×1015/cm2 이하인 것이 더욱 바람직하다.

나중에 자세히 설명하는 바와 같이, 절연체(282)와 마찬가지로, 트랜지스터(200)에 포함되는 절연체(222)는 산소, 수소, 및 물에 대한 배리어성을 갖는 것이 바람직하다. 절연체(222)가 산소에 대한 배리어성을 가지면, 산소 과잉 영역의 산소가 절연체(220) 측으로 확산되지 않고, 산화물(230)에 효율적으로 공급될 수 있다.

절연체(282)는 산화 질화 실리콘, 질화 산화 실리콘, 산화 알루미늄, 산화 하프늄, 산화 탄탈럼, 산화 지르코늄, 타이타늄산 지르콘산연(PZT), 타이타늄산 스트론튬(SrTiO3), 또는 (Ba,Sr)TiO3(BST) 등의 소위 high-k 재료를 포함하는 절연체를 사용한 단층 구조 또는 적층 구조를 갖는 것이 바람직하다. 특히, 산소 또는 수소에 대한 배리어성을 갖는 절연막, 예를 들어 산화 알루미늄막 또는 산화 하프늄막을 사용하는 것이 바람직하다. 이러한 재료로 형성된 절연체(282)는, 산화물(230)로부터 산소가 방출되는 것, 및 외부로부터 수소 등의 불순물이 들어가는 것을 방지하는 층으로서 기능한다.

또는, 예를 들어, 상기 절연체에 산화 알루미늄, 산화 비스무트, 산화 저마늄, 산화 나이오븀, 산화 실리콘, 산화 타이타늄, 산화 텅스텐, 산화 이트륨, 또는 산화 지르코늄을 첨가하여도 좋다. 또는 절연체에 질화 처리를 수행하여도 좋다. 상기 절연체 위에 산화 실리콘, 산화 질화 실리콘, 또는 질화 실리콘을 적층하여도 좋다.

또한, 절연체(280, 282, 및 286)는 각각 2층 이상의 적층 구조를 가져도 좋다. 이 경우, 적층은 반드시 같은 재료로 형성될 필요는 없고, 상이한 재료로 형성되어도 좋다. 또한, 트랜지스터(200)를 덮는 절연체(280)는 그 아래의 거칠기를 덮는 평탄화막으로서 기능하여도 좋다.

트랜지스터(200)는, 절연체(280, 282, 및 286)에 제공되는 도전체(246 및 248) 등의 플러그 또는 배선을 통하여, 다른 구성 요소와 전기적으로 접속되는 경우가 있다. 도전체(246 및 248)가 절연체(280)와 접촉되면, 절연체(280)에 포함되는 과잉 산소가 도전체(246 및 248)에 의하여 흡수될 수 있다.

반도체 장치에 제공되는 플러그 또는 배선의 형상, 또는 플러그 또는 배선의 수에 따라서는, 절연체(280)에 포함되는 과잉 산소가 트랜지스터(200)에 포함되는 산화물(230) 내의 산소 결손을 보충하는 데 부족하므로, 반도체 장치의 신뢰성이 저하될 수 있다. 따라서, 절연체(280)의 산소 과잉 영역은 도전체(246 및 248)에 의하여 흡수되는 산소의 양을 고려하여 형성될 필요가 있다.

또한, 트랜지스터(200) 근방에 형성되는 구성 요소에 포함되는 불순물인 수소가, 플러그 또는 배선으로서 사용되는 도전체를 통하여 상기 도전체와 접촉하는 구성 요소로 확산되는 경우가 있다.

따라서, 도전체(246 및 248)와, 산소 과잉 영역을 갖는 절연체(280) 및 배리어성을 갖는 절연체(282)와의 사이에 배리어층(276)을 제공하는 것이 바람직하다. 배리어층(276)은 배리어성을 갖는 절연체(282)와 접촉하여 제공되는 것이 특히 바람직하다. 배리어층(276)은 절연체(282)와 접촉하기 때문에, 절연체(280) 및 트랜지스터(200)는 배리어성을 갖는 절연체, 및 배리어층에 의하여 밀봉될 수 있다. 배리어층(276)은 절연체(286)의 일부와 접촉하는 것도 바람직하다. 배리어층(276)이 절연체(286)와도 접촉되면, 산소 및 불순물의 확산을 더 억제할 수 있다.

즉, 배리어층(276)은 절연체(280)에 포함되는 과잉 산소가 도전체(246 및 248)에 의하여 흡수되는 것을 방지할 수 있다. 따라서, 도전체(246 및 248)에 의하여 과잉 산소가 흡수되기 때문에, 트랜지스터(200)에 포함되는 산화물(230) 내의 산소 결손이 과잉 산소로 보충되지 않음으로써 발생되는, 반도체 장치의 신뢰성의 저하를 방지할 수 있다.

또한, 배리어층(276)은 불순물인 수소의 확산을 억제할 수 있다. 예를 들어, 배리어층(276)은 절연체(282) 위의 구성 요소에 포함되는 수소가 트랜지스터(200)와 접촉하는 절연체(280)로 도전체(246 및 248)를 통하여 확산되는 것을 억제할 수 있다.

또한, 배리어층(276)에 의하여, 반도체 장치에 제공되는 플러그 또는 배선의 형상 또는 위치, 또는 플러그 또는 배선의 수에 상관없이, 절연체(280)는 적절한 양의 과잉 산소를 포함할 수 있다. 수소의 확산을 억제하면 산소 결손이 형성되기 어려워지기 때문에, 캐리어의 생성을 억제할 수 있다. 따라서, 과잉 산소를 트랜지스터(200)에 안정적으로 공급할 수 있어, 트랜지스터(200)가 안정적인 전기 특성을 가질 수 있다. 또한, 반도체 장치의 설계의 유연성을 높일 수 있다.

또한, 배리어층(276)을 사용함으로써, 플러그 또는 배선으로서 사용되는 도전체의 재료 선택의 폭을 넓힐 수 있다. 예를 들어, 산소 흡수성 및 높은 도전성을 갖는 금속 재료를 도전체(246 및 248)에 사용함으로써, 소비전력이 낮은 반도체 장치를 제공할 수 있다. 구체적인 예로서, 텅스텐 또는 알루미늄 등의 내산화성이 낮으며 도전성이 높은 재료, 그리고 쉽게 퇴적 및 가공할 수 있는 도전체를 들 수 있다.

각 도전체(246 및 248)는, 금속 재료, 합금 재료, 금속 질화물 재료, 또는 금속 산화물 재료 등의 도전 재료를 사용하여 단층 구조 또는 적층 구조를 갖도록 형성할 수 있다. 예를 들어, 텅스텐 또는 몰리브데넘 등, 내열성 및 도전성의 양쪽 모두를 갖는 고융점 재료를 사용하는 것이 바람직하다. 또는, 알루미늄 또는 구리 등의 저저항 도전 재료를 사용하는 것이 바람직하다. 저저항 도전 재료를 사용하면 배선의 저항을 저감시킬 수 있다.

도전체(246)에는, 예를 들어 수소 및 산소에 대한 배리어성을 갖는 도전체인 질화 탄탈럼 등을 사용할 수 있다. 또한, 도전성이 높은 텅스텐을 도전체(248)에 사용하면, 배선으로서의 도전성을 유지하면서 외부로부터의 불순물의 확산을 억제할 수 있다.

배리어층(276)에는, 예를 들어 금속 산화물을 사용할 수 있다. 특히, 산소 또는 수소에 대한 배리어성을 갖는 절연막, 예를 들어 산화 알루미늄막, 산화 하프늄막, 또는 산화 갈륨막을 사용하는 것이 바람직하다. 또는 CVD(chemical vapor deposition)법에 의하여 퇴적된 질화 실리콘을 사용하여도 좋다.

상기에 따르면, 전기 특성이 안정적인 반도체 장치를 제공할 수 있다. 상기에 따르면, 신뢰성이 높은 반도체 장치를 제공할 수 있다. 상기에 따르면, 소비전력이 낮은 반도체 장치를 제공할 수 있다. 상기에 따르면, 반도체 장치의 설계의 유연성을 높일 수 있다.

<트랜지스터의 구조 1>

이하에서, 트랜지스터(200)의 예에 대하여 설명한다.

몰리브데넘, 타이타늄, 탄탈럼, 텅스텐, 알루미늄, 구리, 크로뮴, 네오디뮴, 및 스칸듐에서 선택된 원소를 포함하는 금속막; 또는 그 성분으로서 상기 원소 중 임의의 것을 포함하는 금속 질화물막(예를 들어, 질화 탄탈럼막, 질화 타이타늄막, 질화 몰리브데넘막, 또는 질화 텅스텐막) 등을 사용하여 도전체(205)를 형성한다. 특히, 질화 탄탈럼막 등의 금속 질화물막은, 수소 또는 산소에 대한 배리어성을 갖고 산화되기 어렵기 때문에(내산화성이 높기 때문에) 바람직하다. 또는, 인듐 주석 산화물, 산화 텅스텐을 포함하는 인듐 산화물, 산화 텅스텐을 포함하는 인듐 아연 산화물, 산화 타이타늄을 포함하는 인듐 산화물, 산화 타이타늄을 포함하는 인듐 주석 산화물, 인듐 아연 산화물, 또는 산화 실리콘이 첨가된 인듐 주석 산화물 등의 도전 재료를 사용할 수 있다.

예를 들어, 도전체(205a)로서 수소에 대한 배리어성을 갖는 도전체, 예를 들어, 질화 탄탈럼을 사용하고, 그 위에 도전체(205b)로서 도전성이 높은 텅스텐을 적층하는 것이 바람직하다. 이 재료의 조합을 사용하면 배선의 도전성을 지키면서 산화물(230)로의 수소의 확산을 방지할 수 있다. 또한, 도 1의 (A) 내지 (C)에는 도전체(205a 및 205b)의 2층 구조를 도시하였지만, 본 발명의 일 형태는 이에 한정되지 않고, 단층 구조 또는 3층 이상의 적층 구조를 사용하여도 좋다. 예를 들어, 배리어성을 갖는 도전체와 도전성이 높은 도전체 사이에, 배리어성을 갖는 도전체 및 도전성이 높은 도전체에 대한 밀착성이 높은 도전체를 형성하여도 좋다.

절연체(280)와 같이, 절연체(224)는 산화 실리콘막 또는 산화 질화 실리콘막 등, 산소를 포함하는 절연체인 것이 바람직하다. 절연체(224)는 산소 과잉 영역을 갖는 것이 특히 바람직하다. 산화물 반도체를 트랜지스터(200)에 사용하고, 산소 과잉 영역을 갖는 절연체를 트랜지스터(200) 근방의 층간막 등에 제공하면, 트랜지스터(200)에 포함되는 산화물(230) 내의 산소 결손을 저감할 수 있고 신뢰성을 향상시킬 수 있다.

또한, 절연체(224)가 산소 과잉 영역을 포함하는 경우, 절연체(222)는 산소, 수소, 및 물에 대한 배리어성을 갖는 것이 바람직하다. 절연체(222)가 산소에 대한 배리어성을 가지면, 산소 과잉 영역의 산소가 도전체(205a) 측으로 확산되지 않고 산화물(230)에 효율적으로 공급된다. 도전체(205)가 절연체(224)의 산소 과잉 영역의 산소와 반응하는 것을 억제할 수 있다.

절연체(222)는, 산화 질화 실리콘, 질화 산화 실리콘, 산화 알루미늄, 산화 하프늄, 산화 탄탈럼, 산화 지르코늄, 타이타늄산 지르콘산연(PZT), 타이타늄산 스트론튬(SrTiO3), 또는 (Ba,Sr)TiO3(BST) 등의 소위 high-k 재료를 포함하는 절연체를 사용하는 단층 구조 또는 적층 구조를 갖는 것이 바람직하다. 특히, 산소 또는 수소에 대한 배리어성을 갖는 절연막, 예를 들어 산화 알루미늄막 또는 산화 하프늄막을 사용하는 것이 바람직하다. 이러한 재료로 형성된 절연체(222)는, 산화물(230)로부터 산소가 방출되는 것, 및 외부로부터 수소 등의 불순물이 들어가는 것을 방지하는 층으로서 기능한다.

또는, 예를 들어, 상기 절연체에 산화 알루미늄, 산화 비스무트, 산화 저마늄, 산화 나이오븀, 산화 실리콘, 산화 타이타늄, 산화 텅스텐, 산화 이트륨, 또는 산화 지르코늄을 첨가하여도 좋다. 또는, 상기 절연체에 질화 처리를 수행하여도 좋다. 상기 절연체 위에 산화 실리콘, 산화 질화 실리콘, 또는 질화 실리콘을 적층하여도 좋다.

또한, 절연체(220, 222, 및 224)는 각각 2층 이상의 적층 구조를 가져도 좋다. 이 경우, 적층은 반드시 같은 재료로 형성될 필요는 없고, 상이한 재료로 형성되어도 좋다.

high-k 재료를 포함하는 절연체(222)를 절연체(220)와 절연체(224) 사이에 제공하기 때문에, 특정한 조건하에서 전자가 절연체(222)에 트랩되고, 문턱 전압이 증대될 수 있다. 이 결과, 절연체(222)가 음으로 대전되는 경우가 있다.

예를 들어, 절연체(220) 및 절연체(224)를 산화 실리콘을 사용하여 형성하고, 절연체(222)를 산화 하프늄, 산화 알루미늄, 또는 산화 탄탈럼 등의 전자 트랩 준위가 많은 재료를 사용하여 형성하는 경우, 반도체 장치의 동작 온도 또는 보관 온도보다 높은 온도(예를 들어, 125℃ 이상 450℃ 이하, 대표적으로는 150℃ 이상 300℃ 이하)에서, 도전체(205)의 전위가 소스 전극 또는 드레인 전극의 전위보다 높은 상태를 10밀리초 이상, 대표적으로는 1분 이상 유지한다. 이에 의하여, 트랜지스터(200)의 산화물로부터 도전체(205)로 전자가 이동한다. 이때, 이동하는 전자의 일부가 절연체(222)의 전자 트랩 준위에 의하여 트랩된다.

필요한 양의 전자가 절연체(222)의 전자 트랩 준위에 의하여 트랩된 트랜지스터에서는, 문턱 전압이 양의 방향으로 변동된다. 도전체(205)의 전압을 제어함으로써, 트랩될 전자의 양을 제어할 수 있어, 문턱 전압을 제어할 수 있다. 상기 구조를 갖는 트랜지스터(200)는, 게이트 전압이 0V일 때도 비도통 상태(오프 상태라고도 함)에 있는 노멀리 오프 트랜지스터이다.

또한, 전자를 트랩하기 위한 처리를 트랜지스터의 제작 공정에서 수행하여도 좋다. 예를 들어, 트랜지스터의 소스 도전체 또는 드레인 도전체에 접속된 도전체의 형성 후, 전(前)처리(웨이퍼 처리) 후, 웨이퍼 다이싱 단계 후, 또는 패키징 후 등의, 공장 출하 전의 임의의 단계에서 처리가 수행되는 것이 바람직하다.

절연체(220, 222, 및 224)의 두께를 적절히 조정함으로써, 문턱 전압을 제어할 수 있다. 예를 들어, 절연체(220, 222, 및 224)의 총 두께가 얇으면, 도전체(205)로부터 전압이 효율적으로 인가되기 때문에, 트랜지스터의 소비전력이 저감된다. 절연체(220, 222, 및 224)의 총 두께는 65nm 이하, 바람직하게는 20nm 이하이다.

그러므로, 오프 상태에서의 누설 전류가 낮은 트랜지스터를 제공할 수 있다. 전기 특성이 안정적인 트랜지스터를 제공할 수 있다. 온 상태 전류가 높은 트랜지스터를 제공할 수 있다. 서브스레시홀드 스윙값이 작은 트랜지스터를 제공할 수 있다. 신뢰성이 높은 트랜지스터를 제공할 수 있다.

산화물(230)은 산화물(230a), 산화물(230a) 위의 산화물(230b), 및 산화물(230b) 위의 산화물(230c)을 포함한다. 트랜지스터(200)를 온으로 하면, 주로 산화물(230b)에 전류가 흐른다(채널이 형성된다). 한편, 산화물(230b)과 산화물(230a 또는 230c) 사이의 계면 근방(혼합 영역인 경우도 있음)의 영역을 통하여 전류가 흐르는 경우가 있지만, 산화물(230a 및 230c)의 다른 영역은 절연체로서 기능하는 경우가 있다.

도 1의 (C)에 도시된 바와 같이, 산화물(230c)은 산화물(230a 및 230b)의 측면을 덮도록 제공되는 것이 바람직하다. 채널이 형성되는 영역을 포함하는 산화물(230b)과 절연체(280) 사이에 제공되는 산화물(230c)은, 절연체(280)로부터 산화물(230b)로 수소, 물, 및 할로젠 등의 불순물이 확산되는 것을 방지할 수 있다.

In-M-Zn 산화물(원소 M은 알루미늄, 갈륨, 이트륨, 구리, 바나듐, 베릴륨, 붕소, 실리콘, 타이타늄, 철, 니켈, 저마늄, 지르코늄, 몰리브데넘, 란타넘, 세륨, 네오디뮴, 하프늄, 탄탈럼, 텅스텐, 및 마그네슘 등에서 선택된 1종류 이상) 등의 금속 산화물을 사용하여 산화물(230a, 230b, 및 230c)을 형성한다. In-Ga 산화물 또는 In-Zn 산화물을 산화물(230)에 사용하여도 좋다.

[금속 산화물]

본 발명의 일 형태의 산화물(230)에 대하여 이하에서 설명한다. 산화물(230)은, 산화물 반도체로서 기능하는 금속 산화물(이하, 금속 산화물을 산화물 반도체라고도 함)을 사용하여 형성되는 것이 바람직하다.

산화물 반도체는 적어도 인듐 또는 아연을 포함하는 것이 바람직하다. 특히, 인듐 및 아연을 포함하는 것이 바람직하다. 또한, 알루미늄, 갈륨, 이트륨, 또는 주석 등을 포함하는 것이 바람직하다. 또한, 붕소, 실리콘, 타이타늄, 철, 니켈, 저마늄, 지르코늄, 몰리브데넘, 란타넘, 세륨, 네오디뮴, 하프늄, 탄탈럼, 텅스텐, 또는 마그네슘 등에서 선택된 하나 이상의 원소를 포함하여도 좋다.

여기서, 산화물 반도체가 인듐, 원소 M, 및 아연을 포함하는 InMZnO인 경우를 생각한다. 원소 M은 알루미늄, 갈륨, 이트륨, 또는 주석 등이다. 또는, 원소 M은 붕소, 실리콘, 타이타늄, 철, 니켈, 저마늄, 지르코늄, 몰리브데넘, 란타넘, 세륨, 네오디뮴, 하프늄, 탄탈럼, 텅스텐, 또는 마그네슘 등일 수 있다. 또한, 상기 원소 중 2개 이상을 조합하여 원소 M으로서 사용하여도 좋다.

본 명세서 등에서는, 질소를 포함하는 금속 산화물(metal oxide)도 금속 산화물이라고 부르는 경우가 있다. 또한, 질소를 포함하는 금속 산화물을 금속 산질화물(metal oxynitride)이라고 불러도 좋다.

<금속 산화물의 구성>

본 발명의 일 형태에 개시된 트랜지스터에 적용할 수 있는 CAC-OS(cloud-aligned composite oxide semiconductor)의 구성에 대하여 이하에서 설명한다.

본 명세서 등에서, "CAAC(c-axis aligned crystal)" 또는 "CAC(cloud-aligned composite)"라고 말하는 경우가 있다. CAAC는 결정 구조의 예를 말하고, CAC는 기능 또는 재료 구성의 예를 말한다.

CAC-OS 또는 CAC metal oxide는 재료의 일부에서 도전성 기능을 갖고, 재료의 다른 일부에서 절연성 기능을 갖고, 전체로서는 CAC-OS 또는 CAC metal oxide는 반도체의 기능을 갖는다. CAC-OS 또는 CAC metal oxide가 트랜지스터의 활성층에 사용되는 경우, 도전성 기능은 캐리어로서 기능하는 전자(또는 정공)를 흘리게 하기 위한 것이고, 절연성 기능은 캐리어로서 기능하는 전자를 흘리지 않게 하기 위한 것이다. 도전성 기능과 절연성 기능의 상보적인 작용에 의하여, CAC-OS 또는 CAC metal oxide는 스위칭 기능(온/오프 기능)을 가질 수 있다. CAC-OS 또는 CAC metal oxide에서는, 기능을 분리함으로써 각 기능을 최대화시킬 수 있다.

CAC-OS 또는 CAC metal oxide는 도전성 영역 및 절연성 영역을 포함한다. 도전성 영역은 상술한 도전성 기능을 갖고, 절연성 영역은 상술한 절연성 기능을 갖는다. 재료 내의 도전성 영역 및 절연성 영역은 나노 입자 레벨로 분리되어 있는 경우가 있다. 도전성 영역 및 절연성 영역은 재료 내에서 고르지 않게 분포되어 있는 경우가 있다. 도전성 영역은 그 경계가 흐릿해져 클라우드상(cloud-like)으로 연결되어 있는 것이 관찰되는 경우가 있다.

또한 CAC-OS 또는 CAC metal oxide에서, 도전성 영역 및 절연성 영역 각각은 0.5nm 이상 10nm 이하, 바람직하게는 0.5nm 이상 3nm 이하의 크기를 갖고, 재료 내에서 분산되어 있는 경우가 있다.

CAC-OS 또는 CAC metal oxide는 밴드 갭이 상이한 성분을 포함한다. 예를 들어, CAC-OS 또는 CAC metal oxide는 절연성 영역에 기인하는 넓은 갭(wide gap)을 갖는 성분 및 도전성 영역에 기인하는 좁은 갭(narrow gap)을 갖는 성분을 포함한다. 이러한 구성의 경우, 좁은 갭을 갖는 성분에서 캐리어가 주로 흐른다. 좁은 갭을 갖는 성분은 넓은 갭을 갖는 성분을 보완하고, 좁은 갭을 갖는 성분과 연동하여 넓은 갭을 갖는 성분에서도 캐리어가 흐른다. 그러므로, 상술한 CAC-OS 또는 CAC metal oxide를 트랜지스터의 채널 영역에 사용하는 경우, 트랜지스터의 온 상태에서의 높은 전류 구동 능력, 즉 높은 온 상태 전류 및 높은 전계 효과 이동도를 얻을 수 있다.

바꿔 말하면, CAC-OS 또는 CAC-metal oxide를 매트릭스 복합재(matrix composite) 또는 금속 매트릭스 복합재(metal matrix composite)라고 부를 수 있다.

<금속 산화물의 구조>

산화물 반도체는 단결정 산화물 반도체와 비단결정 산화물 반도체로 분류할 수 있다. 비단결정 산화물 반도체의 예에는 CAAC-OS(c-axis-aligned crystalline oxide semiconductor), 다결정 산화물 반도체, nc-OS(nanocrystalline oxide semiconductor), a-like OS(amorphous-like oxide semiconductor), 및 비정질 산화물 반도체가 포함된다.

CAAC-OS는 c축 배향을 갖고, 그 나노 결정들은 a-b면 방향에서 연결되어 있고, 그 결정 구조는 변형을 갖는다. 또한 변형이란, 나노 결정들이 연결된 영역에서, 균일한 격자 배열을 갖는 영역과 균일한 격자 배열을 갖는 다른 영역 사이에서 격자 배열의 방향이 변화되는 부분을 말한다.

나노 결정의 형상은 기본적으로 육각형이지만, 반드시 정육각형인 것은 아니고, 비정육각형인 경우가 있다. 오각형의 격자 배열 또는 칠각형의 격자 배열 등이 변형에 포함되는 경우가 있다. 또한 CAAC-OS의 변형 근방에서도 명확한 결정립계를 관찰할 수 없다. 즉, 격자 배열의 변형으로 인하여 결정립계의 형성이 억제된다. 이는, a-b면 방향에서 산소 원자의 배열의 밀도가 낮은 것, 및 금속 원소의 치환에 의하여 원자간 결합 거리가 변화되는 것 등에 의하여 CAAC-OS가 변형을 허용할 수 있기 때문이라고 생각된다.

CAAC-OS는, 인듐 및 산소를 포함하는 층(이하, In층), 그리고 원소 M, 아연, 및 산소를 포함하는 층(이하, (M, Zn)층)이 적층된 층상 결정 구조(층상 구조라고도 함)를 갖는 경향이 있다. 또한 인듐 및 원소 M은 서로 치환될 수 있고, (M, Zn)층의 원소 M이 인듐으로 치환되는 경우, 상기 층을 (In, M, Zn)층이라고 할 수도 있다. In층의 인듐이 원소 M으로 치환되는 경우, 상기 층을 (In, M)층이라고 할 수도 있다.

CAAC-OS는 결정성이 높은 산화물 반도체이다. 한편, CAAC-OS에서는, 명확한 결정립계를 관찰할 수 없기 때문에, 결정립계에 기인하는 전자 이동도의 저하가 발생되기 어렵다. 불순물의 침입 또는 결함의 형성 등은 산화물 반도체의 결정성을 저하시킬 수 있다. 이는, CAAC-OS는 불순물 및 결함(예를 들어, 산소 결손)의 양이 적다는 것을 의미한다. 따라서 CAAC-OS를 포함하는 산화물 반도체는 물리적으로 안정된다. 그러므로 CAAC-OS를 포함하는 산화물 반도체는 내열성이 있고 신뢰성이 높다.

nc-OS에서, 미소 영역(예를 들어, 크기가 1nm 이상 10nm 이하인 영역, 특히 크기가 1nm 이상 3nm 이하인 영역)은 주기적인 원자 배열을 갖는다. nc-OS에서 상이한 나노 결정들 사이에 결정 배향의 규칙성은 없다. 따라서, 막 전체에서 배향이 관찰되지 않는다. 그러므로, 분석 방법에 따라서는 nc-OS를 a-like OS 또는 비정질 산화물 반도체와 구별할 수 없는 경우가 있다.

a-like OS는 nc-OS와 비정질 산화물 반도체의 중간의 구조를 갖는다. a-like OS는 공동 또는 밀도가 낮은 영역을 갖는다. 즉, a-like OS는 nc-OS 및 CAAC-OS와 비교하여 결정성이 낮다.

산화물 반도체는 다양한 상이한 특성을 나타내는 다양한 구조를 가질 수 있다. 비정질 산화물 반도체, 다결정 산화물 반도체, a-like OS, nc-OS, 및 CAAC-OS 중 2개 이상이 본 발명의 일 형태의 산화물 반도체에 포함되어도 좋다.

[산화물 반도체를 포함하는 트랜지스터]

다음으로, 상기 산화물 반도체를 트랜지스터에 사용하는 경우에 대하여 설명한다.

또한 산화물 반도체를 트랜지스터에 사용하면, 전계 효과 이동도가 높은 트랜지스터로 할 수 있다. 또한, 신뢰성이 높은 트랜지스터로 할 수 있다.

트랜지스터에는 캐리어 밀도가 낮은 산화물 반도체를 사용하는 것이 바람직하다. 산화물 반도체막의 캐리어 밀도를 저감시키기 위해서는, 산화물 반도체막 내의 불순물 농도를 저감시킴으로써 결함 준위의 밀도를 저감시킬 수 있다. 본 명세서 등에서, 불순물 농도가 낮고 결함 준위의 밀도가 낮은 상태를 고순도 진성 또는 실질적으로 고순도 진성 상태라고 한다. 예를 들어, 캐리어 밀도가 8×1011/cm3 미만, 바람직하게는 1×1011/cm3 미만, 더 바람직하게는 1×1010/cm3 미만이고 1×10-9/cm3 이상인 산화물 반도체를 사용한다.

고순도 진성 또는 실질적으로 고순도 진성인 산화물 반도체는 결함 준위의 밀도가 낮기 때문에, 트랩 준위의 밀도가 낮은 경우가 있다.

산화물 반도체 내에서 트랩 준위에 의하여 트랩된 전하는 방출되는 데 긴 시간이 걸리고, 고정 전하처럼 작용될 수 있다. 따라서, 트랩 준위의 밀도가 높은 산화물 반도체에 채널 영역이 형성되는 트랜지스터는 전기 특성이 불안정한 경우가 있다.

트랜지스터의 안정적인 전기 특성을 얻기 위해서는, 산화물 반도체 내의 불순물 농도를 저감시키는 것이 효과적이다. 또한, 산화물 반도체 내의 불순물 농도를 저감시키기 위해서는, 산화물 반도체에 인접한 막 내의 불순물 농도를 저감시키는 것이 바람직하다. 불순물의 예에는 수소, 질소, 알칼리 금속, 알칼리 토금속, 철, 니켈, 및 실리콘이 포함된다.

<불순물>

여기서, 산화물 반도체에서의 불순물의 영향에 대하여 설명한다.

14족 원소 중 하나인 실리콘 또는 탄소가 산화물 반도체에 포함되면, 결함 준위가 형성된다. 따라서, 산화물 반도체에서의, 그리고 산화물 반도체와의 계면 근방에서의 실리콘 또는 탄소의 농도(SIMS(secondary ion mass spectrometry)에 의하여 측정됨)를 2×1018atoms/cm3 이하, 바람직하게는 2×1017atoms/cm3 이하로 한다.

산화물 반도체가 알칼리 금속 또는 알칼리 토금속을 포함하면, 결함 준위가 형성되고 캐리어가 생성되는 경우가 있다. 이에 의하여, 알칼리 금속 또는 알칼리 토금속을 포함하는 산화물 반도체를 포함하는 트랜지스터는 노멀리 온이 되기 쉽다. 그러므로, 산화물 반도체 내의 알칼리 금속 또는 알칼리 토금속의 농도를 저감하는 것이 바람직하다. 구체적으로는, SIMS에 의하여 측정되는 산화물 반도체의 알칼리 금속 또는 알칼리 토금속의 농도는 1×1018atoms/cm3 이하, 바람직하게는 2×1016atoms/cm3 이하이다.

산화물 반도체가 질소를 포함하면, 캐리어로서 기능하는 전자의 생성 및 캐리어 밀도의 증가에 의하여 산화물 반도체가 n형화되기 쉽다. 이에 의하여, 질소를 포함하는 산화물 반도체를 포함하는 트랜지스터는 노멀리 온이 되기 쉽다. 이러한 이유로, 상기 산화물 반도체의 질소는 가능한 한 저감되어 있는 것이 바람직하고, SIMS에 의하여 측정되는 질소 농도를 예를 들어, 5×1019atoms/cm3 미만, 바람직하게는 5×1018atoms/cm3 이하, 더 바람직하게는 1×1018atoms/cm3 이하, 더욱 바람직하게는 5×1017atoms/cm3 이하로 설정한다.

산화물 반도체에 포함되는 수소는 금속 원자와 결합되는 산소와 반응하여 물이 되기 때문에, 산소 결손을 발생시키는 경우가 있다. 산소 결손에 수소가 들어가는 것으로 인하여, 캐리어로서 기능하는 전자가 생성되는 경우가 있다. 또한, 수소의 일부가 금속 원자와 결합되는 산소와 결합됨으로써, 캐리어로서 기능하는 전자가 생성되는 경우가 있다. 따라서, 수소를 포함한 산화물 반도체를 포함하는 트랜지스터는 노멀리 온이 되기 쉽다. 따라서, 산화물 반도체 내의 수소는 가능한 한 저감되어 있는 것이 바람직하다. 구체적으로는, SIMS에 의하여 측정되는 수소 농도를 1×1020atoms/cm3 미만, 바람직하게는 1×1019atoms/cm3 미만, 더 바람직하게는 5×1018atoms/cm3 미만, 더욱 바람직하게는 1×1018atoms/cm3 미만으로 설정한다.

불순물 농도가 충분히 저감된 산화물 반도체를 트랜지스터의 채널 영역에 사용하면, 전기 특성이 안정적인 트랜지스터로 할 수 있다.

절연체(250)로서, 예를 들어 산화 질화 실리콘, 질화 산화 실리콘, 산화 알루미늄, 산화 하프늄, 산화 탄탈럼, 산화 지르코늄, 타이타늄산 지르콘산연(PZT), 타이타늄산 스트론튬(SrTiO3), 또는 (Ba,Sr)TiO3(BST) 등의 소위 high-k 재료를 포함하는 절연체를 사용할 수 있다. 상기 절연체는 단층 구조 또는 적층 구조를 가져도 좋다. 또는, 예를 들어, 상기 절연체에 산화 알루미늄, 산화 비스무트, 산화 저마늄, 산화 나이오븀, 산화 타이타늄, 산화 텅스텐, 산화 이트륨, 또는 산화 지르코늄을 첨가하여도 좋다. 또는 절연체에 질화 처리를 수행하여도 좋다. 상기 절연체 위에 산화 실리콘, 산화 질화 실리콘, 또는 질화 실리콘을 적층하여도 좋다.

예를 들어, 산화 실리콘 및 산화 질화 실리콘은 열적으로 안정적이기 때문에, 비유전율이 높은 절연체와, 산화 실리콘 또는 산화 질화 실리콘을 조합함으로써, 열적으로 안정적이고 비유전율이 높은 적층 구조로 할 수 있다.

절연체(250)로서, 절연체(224)와 같이, 화학량론적 조성보다 산소를 더 포함하는 산화물 절연체가 사용되는 것이 바람직하다. 과잉 산소를 포함하는 이러한 절연체가 산화물(230)과 접촉하여 제공되면, 산화물(230) 내의 산소 결손이 저감될 수 있다.

절연체(250)로서는, 산소 또는 수소에 대하여 배리어성을 갖는, 산화 알루미늄, 산화 질화 알루미늄, 산화 갈륨, 산화 질화 갈륨, 산화 이트륨, 산화 질화 이트륨, 산화 하프늄, 산화 질화 하프늄, 또는 질화 실리콘 등으로 형성된 절연막을 사용할 수 있다. 이러한 재료로 형성된 절연체(250)는, 산화물(230)로부터 산소가 방출되는 것, 및 외부로부터 수소 등의 불순물이 들어가는 것을 방지하는 층으로서 기능한다.

또한, 절연체(250)는 절연체(220), 절연체(222), 및 절연체(224)와 비슷한 적층 구조를 가져도 좋다. 전자 트랩 준위에 의하여 필요한 양의 전자가 트랩된 절연체를 절연체(250)가 포함하면, 트랜지스터(200)의 문턱 전압이 양의 방향으로 변동될 수 있다. 상기 구조를 갖는 트랜지스터(200)는 게이트 전압이 0V일 때도 비도통 상태(오프 상태라고도 함)에 있는 노멀리 오프 트랜지스터이다.

도전체(240a 및 240b) 중 한쪽은 소스 전극으로서 기능하고, 다른 쪽은 드레인 전극으로서 기능한다.

알루미늄, 타이타늄, 크로뮴, 니켈, 구리, 이트륨, 지르코늄, 몰리브데넘, 은, 탄탈럼, 및 텅스텐 등의 금속 중 임의의 것, 또는 상기 금속 중 임의의 것을 주성분으로서 포함하는 합금을 도전체(240a 및 240b) 각각에 사용할 수 있다. 특히, 질화 탄탈럼막 등의 금속 질화물막은 수소 또는 산소에 대한 배리어성을 갖고, 내산화성이 높기 때문에 바람직하다.

도면에는 단층 구조를 도시하였지만, 2층 이상의 적층 구조를 사용하여도 좋다. 예를 들어, 질화 탄탈럼막과 텅스텐막을 적층하여도 좋다. 또는, 타이타늄막과 알루미늄막을 적층하여도 좋다. 다른 예에는, 알루미늄막을 텅스텐막 위에 적층하는 2층 구조, 구리막을 구리-마그네슘-알루미늄 합금막 위에 적층하는 2층 구조, 구리막을 타이타늄막 위에 적층하는 2층 구조, 및 구리막을 텅스텐막 위에 적층하는 2층 구조가 포함된다.

다른 예에는, 타이타늄막 또는 질화 타이타늄막을 형성하고, 이 타이타늄막 또는 질화 타이타늄막 위에 알루미늄막 또는 구리막을 적층하고, 이 알루미늄막 또는 구리막 위에 타이타늄막 또는 질화 타이타늄막을 형성하는 3층 구조; 및 몰리브데넘막 또는 질화 몰리브데넘막을 형성하고, 이 몰리브데넘막 또는 질화 몰리브데넘막 위에 알루미늄막 또는 구리막을 적층하고, 이 알루미늄막 또는 구리막 위에 몰리브데넘막 또는 질화 몰리브데넘막을 형성하는 3층 구조가 포함된다. 또한, 산화 인듐, 산화 주석, 또는 산화 아연을 포함하는 투명 도전 재료를 사용하여도 좋다.

또한, 도전체(240a) 및 도전체(240b) 위에, 배리어층(244a) 및 배리어층(244b)을 제공하여도 좋다. 산소 또는 수소에 대한 배리어성을 갖는 재료가 배리어층(244a) 및 배리어층(244b)에 사용되는 것이 바람직하다. 이 구조에 의하여, 산화물(230c)을 퇴적할 때, 도전체(240a) 및 도전체(240b)가 산화되는 것을 억제할 수 있다. 절연체(280)에서의 산소 과잉 영역의 산소가, 도전체(240a) 및 도전체(240b)와 반응하고, 그들이 산화되는 것을 방지할 수 있다.

예를 들어, 금속 산화물을 배리어층(244a) 및 배리어층(244b)에 사용할 수 있다. 특히, 산소 또는 수소에 대한 배리어성을 갖는 절연막, 예를 들어 산화 알루미늄막, 산화 하프늄막, 또는 산화 갈륨막을 사용하는 것이 바람직하다. 또는 CVD법에 의하여 퇴적된 질화 실리콘을 사용하여도 좋다.

배리어층(244)을 사용함으로써, 도전체(240)의 재료 선택의 폭을 넓힐 수 있다. 도전체(240)에는, 예를 들어 텅스텐 또는 알루미늄 등의 내산화성이 낮으며 도전성이 높은 재료, 또는 쉽게 퇴적 및 가공할 수 있는 도전체를 사용할 수 있다.

또한, 도전체(240)의 산화를 방지할 수 있고, 절연체(224) 및 절연체(280)로부터 방출된 산소를 효율적으로 산화물(230)로 공급할 수 있다. 또한, 도전성이 높은 도전체를 도전체(240)에 사용함으로써, 소비전력이 낮은 트랜지스터(200)를 제공할 수 있다.

게이트 전극으로서 기능하는 도전체(260)는 예를 들어 알루미늄, 크로뮴, 구리, 탄탈럼, 타이타늄, 몰리브데넘, 및 텅스텐에서 선택된 금속, 이들 금속 중 임의의 것을 그 성분으로서 포함하는 합금, 또는 이들 금속 중 임의의 것을 조합하여 포함하는 합금 등을 사용하여 형성될 수 있다. 특히, 질화 탄탈럼막 등의 금속 질화물막은 수소 또는 산소에 대한 배리어성을 갖고, 내산화성이 높기 때문에 바람직하다. 또한, 망가니즈 및 지르코늄 중 한쪽 또는 양쪽이 사용되어도 좋다. 또는, 인 등의 불순물 원소를 도핑한 다결정 실리콘으로 대표되는 반도체, 또는 니켈 실리사이드 등의 실리사이드가 사용되어도 좋다.

예를 들어, 도전체(260a)를 열 CVD법, MOCVD법, 또는 ALD(atomic layer deposition)법에 의하여 형성한다. 특히, 도전체(260a)는 ALD법에 의하여 형성되는 것이 바람직하다. ALD법 등을 채용함으로써, 퇴적 시의 절연체(250)에 대한 대미지를 저감할 수 있다. 또한, 도전체(260a)를 ALD법 등에 의하여 형성하면 피복성을 향상시킬 수 있어 바람직하다. 따라서, 신뢰성이 높은 트랜지스터(200)를 제공할 수 있다.