KR20150027061A - 반도체장치 및 검출 시스템 - Google Patents

반도체장치 및 검출 시스템 Download PDFInfo

- Publication number

- KR20150027061A KR20150027061A KR1020147033189A KR20147033189A KR20150027061A KR 20150027061 A KR20150027061 A KR 20150027061A KR 1020147033189 A KR1020147033189 A KR 1020147033189A KR 20147033189 A KR20147033189 A KR 20147033189A KR 20150027061 A KR20150027061 A KR 20150027061A

- Authority

- KR

- South Korea

- Prior art keywords

- substrate

- processing

- section

- processing unit

- detection

- Prior art date

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 56

- 239000000758 substrate Substances 0.000 claims abstract description 197

- 238000012545 processing Methods 0.000 claims abstract description 96

- 238000001514 detection method Methods 0.000 claims description 49

- 238000000034 method Methods 0.000 claims description 36

- 238000003860 storage Methods 0.000 claims description 25

- 230000008569 process Effects 0.000 claims description 14

- 230000020169 heat generation Effects 0.000 claims description 7

- 238000005516 engineering process Methods 0.000 description 27

- 238000010586 diagram Methods 0.000 description 22

- 239000000470 constituent Substances 0.000 description 5

- 238000004519 manufacturing process Methods 0.000 description 5

- 230000002411 adverse Effects 0.000 description 4

- 238000007781 pre-processing Methods 0.000 description 4

- 230000002950 deficient Effects 0.000 description 3

- 239000011159 matrix material Substances 0.000 description 3

- 230000000295 complement effect Effects 0.000 description 2

- 238000012937 correction Methods 0.000 description 2

- 230000000694 effects Effects 0.000 description 2

- 230000006870 function Effects 0.000 description 2

- 238000003384 imaging method Methods 0.000 description 2

- 230000010354 integration Effects 0.000 description 2

- 238000003475 lamination Methods 0.000 description 2

- 230000008901 benefit Effects 0.000 description 1

- 230000007423 decrease Effects 0.000 description 1

- 230000006866 deterioration Effects 0.000 description 1

- 230000002542 deteriorative effect Effects 0.000 description 1

- 238000010438 heat treatment Methods 0.000 description 1

- 229910044991 metal oxide Inorganic materials 0.000 description 1

- 150000004706 metal oxides Chemical class 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 230000004044 response Effects 0.000 description 1

- 230000011664 signaling Effects 0.000 description 1

- 238000010561 standard procedure Methods 0.000 description 1

- 230000003068 static effect Effects 0.000 description 1

- 230000001629 suppression Effects 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L25/00—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof

- H01L25/16—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof the devices being of types provided for in two or more different main groups of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. forming hybrid circuits

- H01L25/167—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof the devices being of types provided for in two or more different main groups of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. forming hybrid circuits comprising optoelectronic devices, e.g. LED, photodiodes

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14601—Structural or functional details thereof

- H01L27/14609—Pixel-elements with integrated switching, control, storage or amplification elements

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14643—Photodiode arrays; MOS imagers

- H01L27/14649—Infrared imagers

- H01L27/1465—Infrared imagers of the hybrid type

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

- H04N25/60—Noise processing, e.g. detecting, correcting, reducing or removing noise

- H04N25/68—Noise processing, e.g. detecting, correcting, reducing or removing noise applied to defects

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

- H04N25/70—SSIS architectures; Circuits associated therewith

- H04N25/71—Charge-coupled device [CCD] sensors; Charge-transfer registers specially adapted for CCD sensors

- H04N25/75—Circuitry for providing, modifying or processing image signals from the pixel array

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

- H04N25/70—SSIS architectures; Circuits associated therewith

- H04N25/76—Addressed sensors, e.g. MOS or CMOS sensors

- H04N25/78—Readout circuits for addressed sensors, e.g. output amplifiers or A/D converters

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

- H04N25/70—SSIS architectures; Circuits associated therewith

- H04N25/79—Arrangements of circuitry being divided between different or multiple substrates, chips or circuit boards, e.g. stacked image sensors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/0002—Not covered by any one of groups H01L24/00, H01L24/00 and H01L2224/00

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Power Engineering (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Signal Processing (AREA)

- Multimedia (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Electromagnetism (AREA)

- Transforming Light Signals Into Electric Signals (AREA)

- Solid State Image Pick-Up Elements (AREA)

- Semiconductor Integrated Circuits (AREA)

- Measurement Of Length, Angles, Or The Like Using Electric Or Magnetic Means (AREA)

- Investigating Or Analyzing Materials By The Use Of Electric Means (AREA)

Abstract

반도체장치는 : 소정의 정보를 검출하는 검출부를 갖는 제1 기판과 ; 상기 검출부로부터 공급되는 데이터를 처리하는 제1 처리부를 갖는 제2 기판과 ; 상기 제1 기판 또는 상기 제2 기판의 어느 하나로부터 공급되는 데이터를 처리하는 제2 처리부를 갖는 제3 기판을 포함한다.

Description

본 기술은, 반도체장치 및 반도체를 포함하는 검출 시스템에 관한 것으로, 특히 고화질 신호를 취득할 수 있는 반도체장치 및 반도체를 포함하는 검출 시스템에 관한 것이다.

본 기술에 의한 방법을 제안하기 위해, 기존의 반도체장치 및 검출 시스템과, 본 기술에 의한 반도체장치 및 검출 시스템과의 차이에 관해 이하에 설명한다. 이하의 기재에서는, 설명은, 화상 처리 검출 시스템을 예로서 들음에 의해 행하여진다.

도 1은, 기존의 이미지 센서(1)의 구성의 한 예를 도시하는 블록도이다. 기존의 이미지 센서(1)에서는, 기준 전압 발생부(19)가, 필요한 기준 전압을 개개의 구성부분의 각 구성부분에 공급한다. 드라이버(17)는, 복수의 화소가 행렬형상으로 배치된 구성의 화소부(11)를 구동함에 의해, 아날로그 비디오 신호를 화소부(11)로부터 판독한다. AD 변환기(12)는, 이 AD 변환기(12)에 화소부(11)로부터 입력된 아날로그 비디오 신호를, DA 변환기(18)로부터 공급되고 서서히 높아지는 기준 전압과 비교하고, 그리고 AD 변환기(12)의 출력 신호를, 아날로그 비디오 신호의 전위가 기준 전압에 달한 때에 반전시킨다.

카운터(13)는 클록을, AD 변환기(12)로부터의 출력 신호가, 소정의 타이밍에서 온하고나서 반전할 때까지, 소정의 기간에 걸쳐서 카운트한다. 그 결과, 아날로그 비디오 신호의 전위가 디지털 비디오 신호로 변환된다. SRAM(Static Random Access Memory)(14)은, 카운터(13)로부터 출력되는 디지털 비디오 신호를 당해 SRAM에 일시적으로 격납한다.

파이프라인 처리부(15)는, 당해 파이프라인 처리부에 SRAM(14)으로부터 공급되는 디지털 비디오 신호에 여러 가지 종류의 처리를 시행한다. 파이프라인 처리부(15)는, 당해 파이프라인 처리부 내에 SRAM(15A)을 내장하고, 그리고 SRAM(15A)은, 당해 SRAM(15A)에, 전처리가 행하여진 디지털 비디오 신호를 일시적으로 격납한다. SRAM(15A)으로부터 판독된 디지털 비디오 신호는, 외부에 데이터 인터페이스(16)를 통하여 출력된다.

MPU(Micro Processing Unit)(20)는, 개개의 구성부분의 동작을 OTP(On Time Programmable Read Only Memory)(21)에 격납되는 프로그램 및 데이터에 따라 제어한다.

지금까지, 위에 설명한 화소부(11), 및 다른 회로(31)가, 1장의 기판 시트에 배치되는 구성의 이미지 센서가 알려져 있다. 한마디로 말하면, AD 변환기(12), 카운터(13), SRAM(14), 파이프라인 처리부(15), 데이터 인터페이스(16), 드라이버(17), DA 변환기(18), 기준 전압 발생부(19), MPU(20), 및 OTP(21)는, 회로부(31) 내에 배치된다.

집적도 및 잡음 특성을 밸런스시키기 위해, 본 특허출원인은 지금까지, 예를 들면 일본 특허출원 공개 제2011-159958호 명세서에 기재된 방법을 제안하고 있다.

그러나, 화소부(11)의 기판, 및 회로부(31)의 기판이, 서로의 위에 이와 같이 적층되는 구성의 구조인 경우, 회로부(31)에서 발생하는 열이 화소부(11)에 악영향을 미침에 의해, 비디오 신호를 몇 가지의 경우에서 열화시킨다. 그 결과, 비용의 상승을 몇 가지의 경우에서 초래하는 이와 같은 상황을 보완하는 회로를 제공할 필요가 있다. 보완 회로가 생략된 경우, 고화질 이미지 센서를 제공하는 것이 곤란해진다.

본 기술은, 위에 설명한 문제를 해결하기 위해 개발되고, 그리고 고화질 신호의 취득을 가능하게 하는 것이 본 기술의 제1의 목적이다.

본 기술의 제2의 목적은, 노이즈 및 열에 기인한 신호의 열화를 억제하는 것에 있다.

본 기술의 제3의 목적은, 여러 가지 종류의 반도체장치를 최적의 제조 프로세스에 의해 제조할 수 있도록 하는 것에 있다.

본 기술의 제4의 목적은, 전력소비량의 억제를 가능하게 하는 것에 있다.

본 기술의 제5의 목적은, 여러 가지 종류의 신호 방식을 구체적으로 실시할 수 있도록 하는 것에 있다.

본 기술의 제6의 목적은, 검출되는 정보를 부분적으로 출력할 수 있도록 하는 것에 있다.

본 기술의 제7의 목적은, 입력/출력에 관한 인터페이스 속도를 완화할 수 있도록 하는 것에 있다.

본 기술의 제8의 목적은, 전자파의 방사를 억제할 수 있도록 하는 것에 있다.

본 기술의 제9의 목적은, 검출된 여러 가지 종류의 물리 정보에 관한 신호를, 당해 신호에 신호 처리를 시행한 후에 출력할 수 있도록 하는 것에 있다.

본 기술의 제10의 목적은, 여러 가지의 방식을 갖는 신호의 표준화를 기판 내에서 행할 수 있도록 하는 것에 있다.

본 기술에 의하면, 반도체장치가 제공되고, 그 반도체장치는 : 소정의 정보를 검출하는 검출부를 갖는 제1 기판과 ; 검출부로부터 공급되는 데이터를 처리하는 제1 처리부를 갖는 제2 기판과 ; 제1 기판 또는 제2 기판의 어느 하나로부터 공급되는 데이터를 처리하는 제2 처리부를 갖는 제3 기판을 포함한다.

제1 내지 제3 기판은, 서로의 기판의 위에 순차적으로 적층시킬 수 있다.

제3 기판은, 제1 기판 또는 제2 기판의 어느 하나의 기판부터의 데이터를 보존하는 기억 영역부를 가질 수 있다.

제3 기판의 기억 영역부는, 휘발성 기억 영역부 및 불휘발성 기억 영역부의 양쪽을 가질 수 있다.

제1 기판의 검출부, 제2 기판의 제1 처리부, 및 제3 기판의 기억 영역부는, 다른 프로세스에 의해 각각 제조할 수 있다.

제3 기판의 기억 영역부는, 제1 기판의 검출부가 검출한 데이터의 일부를 출력할 수 있다.

제3 기판의 제2 처리부는, 검출부로부터의 데이터를 처리함에 의해 얻어지는 데이터를 외부에 출력하는 인터페이스를 가질 수 있다.

제1 기판은 복수의 검출부를 가질 수 있다.

제2 기판의 제1 처리부의 발열량은, 제3 기판의 제2 처리부의 발열량보다도 적게 할 수 있다.

제3 기판의 제2 처리부는, 발열량이 가장 많은 회로 블록을 포함할 수 있다.

반도체장치는 이미지 센서로 할 수 있다.

제2 기판의 제1 처리부는 아날로그 회로를 포함할 수 있다.

제2 기판의 제1 처리부는 DRAM을 포함할 수 있다.

제2 기판의 제1 처리부는, 드라이버, 기준 전압 발생부, DA 변환기, AD 변환기, 및 OTP로 이루어지는 적어도 하나의 회로 블록을 포함할 수 있다.

제3 기판의 제2 처리부는 논리 회로를 포함할 수 있다.

제3 기판의 제2 처리부는, 파이프라인 처리부, 카운터, SRAM, MPU, 어레이 컨트롤러, 및 DRAM 컨트롤러로 이루어지는 적어도 하나의 회로 블록을 포함할 수 있다.

본 기술에 의하면, 검출 시스템을 제공할 수 있고, 그 검출 시스템은 : 소정의 정보를 검출하는 검출 장치를 포함하고, 그 검출 장치는, 소정의 정보를 검출하는 검출부를 갖는 제1 기판과, 검출부로부터 공급되는 데이터를 처리하는 제1 처리부를 갖는 제2 기판과, 제1 기판 또는 제2 기판의 어느 하나로부터 공급되는 데이터를 처리하는 제2 처리부를 갖는 제3 기판을 포함한다.

검출 시스템은, 복수의 검출 장치로부터의 데이터를 처리하는 MPU를 구비할 수 있다.

도 1은 기존의 이미지 센서의 구성의 한 예를 도시하는 블록도.

도 2는 본 기술의 하나의 실시 형태에 의한 반도체장치의 구성례를 도시하는 블록도.

도 3은 격납된 비디오 신호의 처리를 행하는 예를 도시하는 일련의 도면.

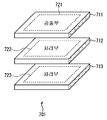

도 4는 본 기술에 의한 반도체장치의 적층 구조의 한 예를 도시하는 일련의 도면.

도 5는 화소 기판의 평면 구조를 도시하는 도면.

도 6은 아날로그부의 기판의 평면 구조를 도시하는 도면.

도 7은 로직부의 기판의 평면 구조를 도시하는 도면.

도 8은 기판에서의 블록군 사이의 접속의 관계를 도시하는 도면.

도 9는 본 기술의 하나의 실시 형태에 의한 검출 시스템의 구성의 한 예를 도시하는 도면.

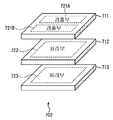

도 10은 본 기술의 다른 실시 형태에 의한 반도체장치의 구조의 한 예를 도시하는 도면.

도 11은 본 기술의 또 다른 실시 형태에 의한 반도체장치의 구조의 한 예를 도시하는 도면.

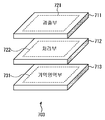

도 12는 본 기술의 또 다른 실시 형태에 의한 반도체장치의 구조의 한 예를 도시하는 도면.

도 13은 본 기술의 다른 실시 형태에 의한 반도체장치의 구조의 한 예를 도시하는 도면.

도 14는 본 기술의 또 다른 실시 형태에 의한 반도체장치의 구조의 한 예를 도시하는 도면.

도 15는 본 기술의 하나의 실시 형태에 의한 반도체장치에 대한 처리를 설명하는 도면.

도 16은 본 기술의 다른 실시 형태에 의한 검출 시스템의 구성의 한 예를 도시하는 도면.

도 2는 본 기술의 하나의 실시 형태에 의한 반도체장치의 구성례를 도시하는 블록도.

도 3은 격납된 비디오 신호의 처리를 행하는 예를 도시하는 일련의 도면.

도 4는 본 기술에 의한 반도체장치의 적층 구조의 한 예를 도시하는 일련의 도면.

도 5는 화소 기판의 평면 구조를 도시하는 도면.

도 6은 아날로그부의 기판의 평면 구조를 도시하는 도면.

도 7은 로직부의 기판의 평면 구조를 도시하는 도면.

도 8은 기판에서의 블록군 사이의 접속의 관계를 도시하는 도면.

도 9는 본 기술의 하나의 실시 형태에 의한 검출 시스템의 구성의 한 예를 도시하는 도면.

도 10은 본 기술의 다른 실시 형태에 의한 반도체장치의 구조의 한 예를 도시하는 도면.

도 11은 본 기술의 또 다른 실시 형태에 의한 반도체장치의 구조의 한 예를 도시하는 도면.

도 12는 본 기술의 또 다른 실시 형태에 의한 반도체장치의 구조의 한 예를 도시하는 도면.

도 13은 본 기술의 다른 실시 형태에 의한 반도체장치의 구조의 한 예를 도시하는 도면.

도 14는 본 기술의 또 다른 실시 형태에 의한 반도체장치의 구조의 한 예를 도시하는 도면.

도 15는 본 기술의 하나의 실시 형태에 의한 반도체장치에 대한 처리를 설명하는 도면.

도 16은 본 기술의 다른 실시 형태에 의한 검출 시스템의 구성의 한 예를 도시하는 도면.

도 2는, 본 기술의 하나의 실시 형태에 의한 반도체장치를 도시하는 블록도이다. 예를 들면, 디지털 카메라에 사용되는 CMOS 이미지 센서(상보형 금속 산화물 반도체 이미지 센서(Complementary Metal Oxide Semiconductor Image Sensor))로서 사용할 수 있는 반도체장치(101)는 화소부(111)를 포함한다. 피사체로부터의 광을 검출하는 복수의 화소는, n×m의 행렬형상으로 화소부(111)에 배치된다. 편의상, 화소를 도 2에 2개만 도시하고 있다.

화소군의 각 화소는, 트랜지스터(151 내지 153), 및 포토 다이오드(154)로 이루어진다. 포토 다이오드(154)는, 피사체로부터의 광을 광전 변환함에 의해 얻어지는 비디오 신호를 출력한다. 트랜지스터(152)는, 포토 다이오드(154)로부터의 당해 비디오 신호를 트랜지스터(153)에 전송한다. 트랜지스터(153)는, 당해 트랜지스터(153)에 포토 다이오드(154)로부터 트랜지스터(152)를 통하여 공급되는 당해 비디오 신호를 증폭하고, 그리고 결과적으로 얻어지는 비디오 신호를 배선(155)에 출력한다. 트랜지스터(151)는, 구동되어야 할 포토 다이오드(154)를 선택한다.

트랜지스터(151)의 게이트에 접속되는 배선(156), 트랜지스터(152)의 게이트에 접속되는 배선(157), 및 트랜지스터(153)의 게이트에 접속되는 배선(158)은 전부, 드라이버(112)에 비어(via)군(171)을 각각 통하여 접속된다. 또한, 배선(155)은, 트랜지스터(116), 및 AD 변환기(115)의 일방의 입력단자에 비어(171)를 통하여 접속된다. DA 변환기(114)로부터 출력된 기준 전압은, AD 변환기(115)의 타방의 입력단자에 공급된다. 기준 전압 발생부(113)는, 소정의 기준 전압을 발생하고, 이 기준 전압이 이번에는, AD 변환기(115) 이외의 개개의 구성부분의 각 구성부분에 공급된다.

어레이 컨트롤러(117)는, 드라이버(112), DA 변환기(114), 및 기준 전압 발생부(113)에 각각의 비어(172)를 통하여 접속되고, 그리고 드라이버(112), DA 변환기(114), 및 기준 전압 발생부(113)의 동작을 제어한다. AD 변환기(115)의 출력은, 카운터(118)에 비어(172)를 통하여 접속된다. 카운터(118)는, 당해 카운터에 회로(도시 생략)로부터 공급되는 클록을 카운트한다. 카운터(118)의 카운트 동작은, AD 변환기(115)로부터의 디지털 출력 신호에 응하여 제어되고, 이에 의해 카운트값이 아날로그 비디오 신호의 전위에 일치하도록 된다. 즉, 카운터(118)의 카운트값이 디지털 비디오 신호가 된다. 카운터(118)로부터의 출력 신호는, 버퍼로서 기능하는 SRAM(121)에 공급되고, 그리고 SRAM(121)에 일시적으로 격납된다. 본 개시된 방법에서 제안되는 구성을 사용하는 경우, DRAM(124)을 SRAM(121)에 대신하여 이용할 수 있음에 유의하기를 바란다. 그 결과, 칩 사이즈를 작게 할 수 있다.

칼럼 인터페이스로서 기능하는 SRAM(121)으로부터 판독된 비디오 신호는, 파이프라인 처리부(122)에 공급되고, 그리고 다음에, 당해 비디오 신호에 전처리가 시행된다. 파이프라인 처리부(122)에서 전처리가 시행된 당해 비디오 신호는, DRAM(Dynamic Random Access Memory) 컨트롤러(123)가 판독하고, 그리고 다음에, DRAM(124)에 비어(172)를 통하여 공급되고, DRAM(124)에 격납된다.

DRAM(124)에 격납되는 비디오 신호는, 소정의 타이밍에서, DRAM 컨트롤러(123)에 의해 판독되고, 그리고 다음에, 파이프라인 처리부(122)에 전송된다. 파이프라인 처리부(122)에 전송되는 비디오 신호는, 파이프라인 처리부(122)에 내장되는 SRAM(122A)에 일시적으로 격납된다. SRAM(122A)에 일시적으로 격납되는 비디오 신호는, 데이터 인터페이스(125)에 공급되고, 그리고 다음에, 데이터 인터페이스(125)로부터 외부에 출력된다.

MPU(119)는, OTP(120)에 비어(172)를 통하여 접속되고, 그리고 어레이 컨트롤러(117) 외에, SRAM(121), 파이프라인 처리부(122), 및 DRAM 컨트롤러(123)의 동작을, OTP(120)에 격납되는 프로그램 및 데이터에 따라 제어한다.

다음에, 반도체장치(101)의 동작에 관해 설명하기로 한다. 드라이버(112)는, 어레이 컨트롤러(117)에 의해 제어되어, 소정의 배선에 속하는 화소군을 소정의 타이밍에서 선택한다. 이와 같이 하여 선택되는 화소의 포토 다이오드(154)에 축적하고 있는 전하량에 대응하는 비디오 신호는, 트랜지스터(153)에 트랜지스터(152)를 통하여 전송되고, 그리고 다음에, 트랜지스터(153)에 의해 증폭됨에 의해, 배선(155)에 판독된다. 이와 같이 하여 판독되는 비디오 신호는, AD 변환기(115)의 일방의 입력단자에 공급된다.

DA 변환기(114)는, 어레이 컨트롤러(117)에 의해 제어되어, 소정의 타이밍에서 서서히 커지는 기준 전압을 발생시키고, 그리고 이와 같이 하여 발생시킨 기준 전압을 AD 변환기(115)의 타방의 입력단자에 공급한다. 카운터(118)는, 동작을 시작하여, 소정의 타이밍에서 온하고 나서의 클록을 카운트한다. DA 변환기(114)로부터 출력되는 기준 전압의 전위가, 비디오 신호의 전위와 동등하게 되면, AD 변환기(115)로부터의 출력이 반전한다. AD 변환기(115)로부터의 출력이 반전하면, 카운터(118)는, 카운트값을 당해 카운터에, 해당하는 시점까지 래치하고, 그리고 당해 카운트값을 SRAM(121)에 공급한다. 당해 카운트값은, 비디오 신호의 전위가 높아짐에 따라 커진다. 즉, 당해 카운트값은, 아날로그 비디오 신호를 디지털 비디오 신호로 변환함에 의해 얻어지는 값이 된다.

SRAM(121)에 일시적으로 유지되어 있는 비디오 신호에는 전처리가, 파이프라인 처리부(122)에 의해 시행된다. 예를 들면, 결함 화소군에 관한 데이터는, OTP(120)에 격납되고, 그리고 결함을 갖는 화소로부터의 화소 신호는, 격납되어 있는 결함 데이터에 의거하여 보정된다. 또한, 비디오 신호에는, 클램프 처리가 시행된다.

전처리가 시행된 비디오 신호는, DRAM(124)에 DRAM 컨트롤러(123)를 통하여 공급되고, 그리고 다음에, DRAM(124)에 격납된다. MPU(119)는, DRAM 컨트롤러(123)를 필요에 응하여 제어하여, 소정의 처리를 DRAM(124)에 격납되는 비디오 신호에 대해 실행한다.

도 3은, DRAM(124)에 격납되는 비디오 신호에 대해 행하여지는 처리의 예를 도시하는 일련의 도면이다. 이 경우, 1프레임에 대응하는 비디오 신호군은, DRAM(124) 내의 소정의 어드레스군에 각각 격납된다고 생각된다. 도 3의 A에 도시하는 바와 같이, 프레임(501)에 대응하는 비디오 신호군은, 좌상측부터 우하측을 향하는 방향으로 연속적으로 판독된다. 또한, 도 3의 B에 도시하는 바와 같이, 프레임(501)의 소정 영역 내의 비디오 신호군도, 우상측부터 좌하측을 향하는 방향으로 연속적으로 판독할 수 있다. 그에 더하여, 도 3의 C에 도시하는 바와 같이, 프레임(501A)에 대응하는 비디오 신호군과, 프레임(501A)에 대응하는 비디오 신호군의 전 또는 후의 프레임(501B)에 대응하는 비디오 신호군과의 차(差)는, 수치 연산할 수 있다.

이와 같은 여러 가지 종류의 처리를 실행하면, 손떨림 보정, 노이즈 보정, 움직임 검출, ToF(비행시간(Time of Flight)) 검출, 고속 AF(Autofocus), 화소수를 늘리는 또는 줄이는 고해상도의 스칼라장(場)의 처리, 및 디지털 줌과 같은 기능을 실현할 수 있다. DRAM(124)은, 반도체장치(101)에 이와 같이 하여 내장됨에 의해, 이미지 센서로부터 출력되는 비디오 신호를 외부 DSP(Digital Signal Processor)로 처리하는 경우와 비교하여, 고속 처리가 가능해진다.

DRAM(124)에 격납되는 비디오 신호군이, DRAM 컨트롤러(123)에 의해 행하여지는 제어에 따라 판독되어, 파이프라인 처리부(122)의 SRAM(122A)에 일시적으로 격납된 후, 관계되는 비디오 신호군은 또한, 외부에 데이터 인터페이스(125)를 통하여 출력된다.

다음에, 반도체장치(101)의 구조에 관해 설명하기로 한다. 도 4는, 반도체장치(101)의 적층 구조의 한 예를 도시하는 일련의 도면이다. 도 4에 도시하는 바와 같이, 반도체장치(101)는, 3층 : 최하층의 기판(401) ; 기판(401)에 적층된 기판(301) ; 및 기판(301)에 적층된 기판(201)으로 이루어진다. 한마디로 말하면, 기판(201), 기판(301), 및 기판(401)을 적층하여 1칩형상으로 형성한다. 도 4의 A는, 기판(201), 기판(301), 및 기판(401)을 순차적으로 적층한 상태를 도시하고 있다. 또한, 도 4의 B는, 기판(201), 기판(301), 및 기판(401)을 순차적으로 적층하기 전의 상태를 나타내고 있다. 도 4에서는, 화살표로 도시하는 바와 같이, 피사체로부터 방출된 광의 입사가, 상측부터 최상층의 기판(201)을 향하여 행하여진다.

도 5는, 화소군을 형성한 기판(201)의 평면 구조를 도시하는 도면이다. 이 도 에 도시하는 바와 같이, 화소부(111)는, 기판(201)의 개략 중심에 형성된다. 위에 설명한 바와 같이, 이들의 화소는, n×m의 행렬형상으로 화소부(111)에 배치된다. 이 도면에서는, 비어군(211)은, 화소부(111)의 상측 및 하측, 및 우측에 각각 형성된다. 이들의 비어(211)는, 도 2의 비어군(171)을 각각 형성한다.

도 6은, 아날로그부를 형성한 기판(301)의 평면 구조를 도시하는 도면이다. 기판(301)은, 제1 회로부(331)를 포함하고, 제1 회로부(331)는, 당해 제1 회로부에 화소부(111)로부터 공급되는 신호군을 처리한다. 즉, 이 도면에 도시하는 바와 같이, 3개의 DRAM(124)이, 기판(301)의 개략 중심의 우측 및 좌측의 각 측에 배치되는, 즉 합계 6개의 DRAM(124)이, 기판(301)의 개략 중심에 배치된다. OTP(120)는, 기판(301)의 좌측에 배치된다. 기준 전압 발생부(113) 및 DA 변환기(114)의 양쪽은, 기판(301)의 우측에 배치된다. 또한, 드라이버(112)는, 기판(301)의 기준 전압 발생부(113) 및 DA 변환기(114)의 양쪽의 우측에 배치된다.

각 AD 변환기가 이 도면의 수평 방향으로 연재하는 구성의 AD 변환기군(115)은, 기판(301)의 상측 및 하측에 각각 배치된다. 비어군(312)은, AD 변환기군(115)의 내측에 형성된다. 또한, 3개의 비어(312)가 또한 배치되고, 이 도면의 길이 방향으로, 우측 DRAM(124) 및 좌측 DRAM(124)의 내측부터 연재되어 있다. 이들의 3개의 비어(312)는, 도 2의 비어군(172)을 각각 형성하고 있다.

도 2에 도시하는 비어군(171)을 각각 형성하는 비어군(311)은, 상측 AD 변환기(115) 및 하측 AD 변환기(115)의 외측에, 그리고 기판(301)의 드라이버(112)의 우측에 각각 형성된다. 비어군(311)은, 도 5에 도시하는 기판(201)의 비어군(211)에 각각 대응하는 위치에 형성된다. 따라서, 기판(201)이, 기판(301)에 적층된 경우, 기판(301)의 비어군(311)은, 기판(201)의 비어군(211)에 접속됨에 의해, 도 2에 도시하는 비어군(171)을 각각 형성한다.

이와 같이 하여, 본 실시 형태에서는, 아날로그 회로 블록 및 DRAM군(124)은 기판(301)에 매입된다. 한마디로 말하면, 기판(301)의 제1 회로부(331)는, 드라이버(112), 기준 전압 발생부(113), DA 변환기(114), 및 AD 변환기(115)로 이루어지는 아날로그 회로 블록에 더하여, OTP(120), DRAM군(124) 등으로 이루어지는 회로 블록에 의해 구성된다.

도 7은, 로직부를 형성한 기판(401)의 평면 구조를 도시하는 도면이다. 기판(401)은, 제2 회로부(431)를 포함하고, 제2 회로부(431)는, 당해 제2 회로부에 화소부(111)로부터 공급되는 신호군을 처리한다. 즉, 기판(401)에서는, 파이프라인 처리부(122)는, 개략 중심의 좌측에 배치된다. 또한, 데이터 인터페이스(125)는, 이 도면의 길이 방향으로, 파이프라인 처리부(122)의 좌측으로 연재되도록 배치된다. DRAM 컨트롤러(123)는, 기판(401)의 개략 중심의 우측에 배치된다. 또한, MPU(119) 및 어레이 컨트롤러(117)의 양쪽은, 이 도면의 길이 방향으로 DRAM 컨트롤러(123)의 우측으로 연재되도록 배치된다.

각 SRAM이 칼럼 인터페이스로서 기능하는 구성의 SRAM군(121)은, 이 도면의 수평 방향으로, 기판(401)의 상측 및 하측부터 각각 연재되도록 배치된다. 또한, 카운터군(118)은, 이 도면의 수평 방향으로, SRAM군(121)의 내측부터 연재되도록 배치된다.

비어군(411)은, 이 도면의 수평 방향으로, 카운터군(118)의 내측부터 각각 연재되도록 배치된다. 또한, 3개의 비어(411)은, 파이프라인 처리부(122)와 DRAM 컨트롤러(123)와의 사이에 배치되고, 이 도면의 길이 방향으로 연재되어 있다.

기판(401)의 비어군(411)은, 도 6에 도시하는 기판(301)의 비어군(312)에 각각 대응하는 위치에 형성된다. 따라서, 기판(301)이, 기판(401)에 적층된 경우, 기판(401)의 비어군(411)은, 기판(301)의 비어군(311)에 접속됨에 의해, 도 2에 도시하는 비어군(172)을 각각 형성한다.

이와 같이 하여, 기판(401)의 제2 회로부(431)는, 어레이 컨트롤러(117), 카운터군(118), MPU(119), SRAM군(121), 파이프라인 처리부(122), DRAM 컨트롤러(123), 데이터 인터페이스(125) 등으로 이루어지는 회로 블록에 의해 구성된다. 도 8에는 도시되어 있지 않지만, 도 7에 도시하는 바와 같이, 어레이 컨트롤러(117) 및 DRAM 컨트롤러(123)의 양쪽이 또한, 기판(401)의 제2 회로부(431)에 포함되는 것에 유의하기를 바란다.

도 8은, 이들 기판의 블록군 사이의 접속의 관계를 도시하는 도면이다. 기판(201)의 화소부(111)로부터의 출력은, 기판(301)의 AD 변환기(115)에 공급된다. AD 변환기(115)로부터의 출력은, 기판(401)의 카운터(118)에 공급되고, 그리고 당해 출력을 사용하여, 카운터(118)의 카운트 동작을 제어한다. 카운터(118)의 카운트값에 소정의 전처리를, 기판(401)의 파이프라인 처리부(122)에 의해, 기판(401)의 SRAM(121)을 통하여 행한 후, 결과로서 얻어지는 카운트값을 기판(301)의 DRAM(124)에 공급하여, DRAM(124)에 격납한다. 파이프라인 처리부(122)의 동작은, 기판(401)의 MPU(119)에 의해 제어된다.

MPU(119)의 프로그램 및 데이터의 양쪽은, 기판(301)의 OTP(120)에 격납된다. 드라이버(112), DA 변환기(114), 및 기준 전압 발생부(113)가 또한, 기판(301)에 배치된다.

기판(301)의 DRAM(124)에 격납되어 있는 비디오 신호군은, 기판(401)의 데이터 인터페이스(125)에, 기판(401)의 파이프라인 처리부(122)의 SRAM(122A)을 통하여 공급되고, 그리고 또한, 데이터 인터페이스(125)로부터 외부에 출력된다. 데이터 인터페이스(125)는, 예를 들면 CSI2(카메라 시리얼 인터페이스 2) 규격에 준거할 수 있다.

3개의 기판을 마련하면, 발열량이 많은 논리 회로를 기판(401)에 배치할 수 있고, 그리고 발열량이 적은 회로 블록을 기판(301)에 배치할 수 있다. 한마디로 말하면, 드라이버(112), 기준 전압 발생 회로(113), DA 변환기(114), 및 AD 변환기(115)로 이루어지는 아날로그 회로 블록 외에, OTP(120), DRAM(124) 등으로 이루어지는 발열량이 적은 회로 블록을 기판(301)에 배치할 수 있다. 그 결과, 기판(201)의 화소부(111)의 노이즈 발생량을 억제할 수 있다. 또한, 고집적도를 갖는 기판은, 기판(401)으로서 사용할 수 있다.

한마디로 말하면, 기판(301)은, 기판(401)과 기판(201)과의 사이에 배치된다. 그 결과, 화소부(111)를 갖는 기판(201)은, 기판(401)으로부터 멀리할 수 있다. 회로 블록의 발열량은, 동작 주파수가 높아짐에 따라 많아진다. 따라서, 발열량이 비교적 많은 논리 회로 블록은, 기판(401)에 배치된다. 다른 표현을 하면, 열을 발생하지 않는, 또는 발열량이, 발열하는 경우에도 상대적이면서 비교적 적은 아날로그 회로 블록은, 기판(301)에 배치된다. 그 결과, 기판(401)에 발생하는 노이즈 및 열이, 악영향을 기판(201)의 화소부(111)에 미침에 의해, 비디오 신호를 열화시키는 것을 방지할 수 있다. 또한, 기판(401)은, 가장 외측에 배치되기 때문에, 기판(401)은, 열을 외부에 방산하기 쉽게 되기 때문에, 반도체장치(101)의 온도의 상승을 억제할 수 있다.

기판(301)의 발열량이 기판(401)의 발열량보다도 적어짐(다른 표현을 하면, 기판(401)의 발열량이 기판(301)의 발열량보다도 많아짐)에 의해, 발열에 의해 화소부(111)에 미치는 악영향을 억제할 수 있다. 한마디로 말하면, 회로 블록군의 전부가, 기판(301) 및 기판(401)에, 기판(301)의 제1 회로부(331)의 발열량이 기판(401)의 제2 회로부(431)의 발열량보다도 적어지도록 분산 배치된다.

또는, 예를 들면 배치될 예정의 회로 블록군 중, 발열량이 가장 많은 회로 블록이, 기판(301)에 배치되는 것이 아니라, 기판(401)에 배치되는 경우에도, 같은 효과를 실현할 수도 있다.

비교되는 발열량은, 반도체장치(101)가, 열을 가장 발생하기 쉬운 방법을 이용함에 의해 소정의 시간 길이에 걸쳐서만 사용되는 경우의 발열량으로서, 또는 반도체장치(101)가, 표준적인 방법을 이용함에 의해 표준적인 시간 길이에 걸쳐서만 사용되는 경우의 발열량으로서 채용할 수 있는 것에 유의하기를 바란다. 가장 가혹한 조건이 설정되는 경우, 전자의 쪽의 발열량을 채용할 수 있다.

위의 설명으로부터, 고화질 비디오 신호는, 반도체장치(101)를 이용하여 얻어진다.

위에 설명한 반도체장치(101)는, 예를 들면 디지털 카메라와 같은 촬상 시스템의 이미지 센서에 적용할 수 있다. 도 9는, 본 기술의 하나의 실시 형태에 의한 검출 시스템의 구성의 한 예를 도시하는 도면이다. 도 9에 도시하는 예에서는, 검출 시스템은, 화상 촬영 시스템에 적용된다. 설명을 알기 쉽게 하기 위해, 촬상 시스템(601)의 구성을 간략화하고 있다. 촬상 시스템(601)은, 렌즈(611), 위에 설명하는 실시 형태의 반도체장치(101)로 이루어지는 이미지 센서(101A), 신호 처리부(612), 메모리(613), 및 표시부(614)를 포함한다.

피사체로부터 방출되는 광을 수속(收束)시켜서 이미지 센서(101A)에 입사시킨다. 이미지 센서(101A)는, 피사체에 대응하는 비디오 신호를, 피사체로부터 방출되는 광량에 응하여 출력한다. 신호 처리부(612)는, 당해 신호 처리부에 이미지 센서(101A)로부터 공급되는 비디오 신호를 처리하고, 그리고 변조함에 의해 기록 신호를 생성하고, 그리고 결과적으로 얻어지는 기록 신호를 메모리(613)에 공급하여 메모리(613)에 격납한다. 메모리(613)는, 하드디스크, 고체 메모리 등으로 이루어진다. 신호 처리부(612)는, 비디오 신호를 외부에 필요에 응하여 출력한다.

신호 처리부(612)는, 메모리(613)에 격납되어 있는 비디오 신호를, 소정의 타이밍에서 판독하고, 이와 같이 하여 판독한 비디오 신호를 변조하고, 그리고 결과적으로 얻어지는 비디오 신호를 표시부(614)에 공급한다. 그 결과, 피사체의 화상이 표시부(614)에 표시된다.

위에 설명한 바와 같이, 이미지 센서(101A)가 열에 의한 악영향을 받는 것을 억제할 수 있다. 따라서, 고화질의 화상을 취득할 수 있다.

본 기술은, 화상 정보를 출력하는 촬상 시스템에 적용할 수 있을 뿐만 아니라, 음성 정보, 위치 정보, 속도 정보 등에 관한 대용량의 고정밀 신호를 출력할 필요가 있는 구성의 여러 가지 종류의 검출 시스템에도 적용할 수 있다. 도 10은, 본 기술의 다른 실시 형태에 의한 반도체장치의 구조의 한 예를 도시하는 도면이다.

도 10에 도시하는 반도체장치(701)는, 검출부(721), 처리부(722), 및 처리부(723)로 이루어진다. 검출부(721)는, 기판(711)에 형성되고, 처리부(722)는 기판(712)에 형성되고, 그리고 처리부(723)는 기판(713)에 형성된다. 기판(712)은 기판(713)에 적층되고, 그리고 기판(711)은 기판(712)에 적층된다. 기판(711)에 형성되는 검출부(721)는, 음성 정보, 위치 정보, 속도 정보 등을 검출한다. 기판(712)에 형성되는 처리부(722)는, 검출부(721)가 검출하는 데이터를 처리한다. 기판(713)에 형성되는 처리부(723)는, 검출부(721)가 검출하는 데이터(당해 데이터가 기판(712)의 처리부(722)에 의해 처리되는 경우의 데이터를 포함한다)를 처리한다.

도 10에 도시하는 반도체장치(701)에서의 기판(711)상의 검출부(721), 기판(712)상의 처리부(722), 및 기판(713)상의 처리부(723)는, 도 4에 도시하는 반도체장치(101)에서의 기판(201)상의 화소부(111), 기판(301)상의 제1 회로부(331), 및 기판(401)상의 제2 회로부(431)에 각각 대응하고 있다.

도 10에 도시하는 실시 형태의 경우에서도, 처리부(722 및 723)는, 기판(711)에 접촉한 기판(712)의 발열량이, 기판(713)의 발열량보다도 적어지도록 기판(712) 및 기판(713)에 분산 배치된다. 3개의 기판(711, 712, 및 713)은, 적층 구조를 갖도록 1칩형상으로 형성된다. 그 결과, 고화질 출력 신호를 취득할 수 있다.

4층 또는 그보다도 많은 층수를 갖는 적층 구조를 채용하는 경우에도 또한, 발열량이 가장 큰 회로 블록이, 최하층의 기판(기판(711)에 형성되는 검출부(721)를 갖는 당해 기판(711)으로부터 가장 멀게 떨어진 위치에 적층된 기판)에 배치되어 있는 것에 주목하기 바란다.

도 11은, 본 기술의 또 다른 실시 형태에 의한 반도체장치의 구조의 한 예를 도시하는 도면이다. 본 실시 형태의 반도체장치(702)에서는, 복수의 검출부가 기판(711)에 형성된다. 도 11에 도시하는 예에서는, 2개의 검출부(721A 및 721B)가 기판(711)에 형성된다. 2개의 검출부(721A 및 721B)는, 같은 종류의 정보, 또는 다른 정보의 어느 정보도 검출한다. 기판(712 및 713)에 각각 형성된 처리부(722 및 723)는, 검출부(721A 및 721B)로부터의 출력 신호군의 어느 한쪽의 출력 신호, 또는 양쪽의 출력 신호를 처리한다. 반도체장치(702)의 다른 구조는, 도 10에 도시하는 반도체장치 구조와 같다.

도 12는, 본 기술의 또 다른 실시 형태에 의한 반도체장치의 구조의 한 예를 도시하는 도면이다. 본 실시 형태의 반도체장치(703)에서는, 기억 영역부(731)는, 도 10에 도시하는 기판(713)의 처리부(723)로서 형성된다. 물론, 처리부(723) 전체에서가 아니라, 처리부(723)의 일부에서, 기억 영역부(731)를 형성하여도 좋다. 기판(713)의 기억 영역부(731)는, 기판(711)의 검출부(721)로부터 출력되는 데이터(당해 데이터가 기판(712)의 처리부(722)에서 처리되는 경우의 데이터를 포함한다)를 당해 기억 영역부(731)에 보존한다. 반도체장치(703)의 다른 구조는, 도 10 또는 도 11에 도시하는 반도체장치 구조와 같다.

처리부(723)는, 최하층의 기판(713)에 형성할 수도 있고, 그리고 기억 영역부(731)는, 중간의 기판(712)에 형성할 수도 있음에 유의하기를 바란다.

도 13은, 본 기술의 다른 실시 형태에 의한 반도체장치의 구조의 한 예를 도시하는 도면이다. 본 실시 형태의 반도체장치(704)에서는, 휘발성 기억 영역부(731A) 및 불휘발성 기억 영역부(731B)의 양쪽이, 기판(713)의 기억 영역부(731)로서 형성된다. 전원의 오프 상태의 위상에 있어서 소거할 필요가 있는 정보는, 휘발성 기억 영역부(731A)에 보존된다. 이와는 달리, 전원의 오프 상태의 위상에서도 소거하면 안되는 정보는, 불휘발성 기억 영역부(731B)에 보존된다. 다른 구조는, 도 12에 도시하는 경우에서의 구조와 같다.

도 14는, 본 기술의 또 다른 실시 형태에 의한 반도체장치의 구조의 한 예를 도시하는 도면이다. 본 실시 형태의 반도체장치(705)는, 도 12에 도시하는 반도체장치(703)와 구조가 기본적으로 같다. 그러나, 반도체장치(705)에서는, 기판(711A)의 검출부(721P)는, 제조 프로세스 A에 의해 제조되고, 기판(712A)의 처리부(722P)는, 제조 프로세스 B에 의해 제조되고, 그리고 기판(713A)의 기억 영역부(731P)는, 제조 프로세스 C에 의해 제조된다.

반도체장치(705)가, 다층 구조형상으로 형성되는 경우, 개개의 층은, 최적의 제조 프로세스에 의해 각각 제조됨에 의해, 전력소비량을 줄일 수 있다.

도 15는, 본 기술의 하나의 실시 형태에 의한 반도체장치의 처리를 설명하는 도면이다. 도 15에 도시하는 반도체장치(706)에서는, 기판(711)의 검출부(721)가 검출한 데이터는, 기판(712)의 처리부(722)에서 처리되고, 그리고 다음에, 기판(713)의 기억 영역부(731)에 보존된다. 또한, 기판(713)의 기억 영역부(731)에 보존된 소정수의 데이터 중, 이들 데이터의 불과 일부만이 외부에 출력된다. 즉, 검출부(721)가 검출한 소정수의 데이터의 불과 일부만이, 외부에 출력된다.

기억 영역부(731)를 이와 같이 하여 마련하면, 정보를 시간축 방향으로 보존할 수 있기 때문에, 여러 가지 종류의 신호 방식을 구체적으로 실시할 수 있도록 된다. 또한, 검출된 데이터는, 기억 영역부(731)에 보존할 수 있기 때문에, 검출되는 소정수의 데이터의 일부를 출력단에 출력할 수 있다. 한마디로 말하면, 입력/출력에 관한 인터페이스 속도를 내리도록 작용할 수 있다. 또한, 입력/출력에 관한 인터페이스 속도를 내리는 아울러, 전자파의 방사를 억제할 수 있다.

도 16은, 본 기술의 다른 실시 형태에 의한 검출 시스템의 구성의 한 예를 도시하는 도면이다. 도 16에 도시하는 검출 시스템(801)은, 검출 장치(811 내지 814), 및 MPU(815)로 이루어진다. 검출 장치(811 내지 814)는, 도 4에 도시하는 반도체장치(101), 도 10 내지 도 15에 각각 도시하는 반도체장치(701 내지 706) 등에 의해 구성된다.

검출 장치(811 내지 814)는, 예를 들면 화상 정보, 오토 포커스 정보, 위치 정보, 및 속도 정보에 부가되는 음성 정보 및 다른 정보와 같은, 검출 시스템(801)의 기능에 대응하는 여러 가지 종류의 정보에 관한 데이터를 개개로 검출한다. MPU(815)는, 검출 장치(811 내지 814)가 검출하는 소정수의 데이터를 처리한다.

검출 장치(811 내지 814)는, 검출 장치(811 내지 814)에 의해 각각 검출된 여러 가지 종류의 물리 정보에 관한 소정수의 데이터를, 신호 처리까지의 처리가 행하여진 후에 출력할 수 있다. 따라서, 여러 가지 종류의 방식을 갖는 신호(화상 정보, 음성 정보, 위치 정보, 및 속도 정보와 같은)가 준거하는 규격을 표준화할 수 있다. 한마디로 말하면, 이미 규정되어 있는 소정의 규격에 준거하는 이들의 신호는, 검출 장치(811 내지 814) 등이 각각 갖는 검출부(721)로부터 출력된 신호의 방식에 관계없이, 최종적으로 검출 장치(811 내지 814) 등으로부터 출력할 수 있다. 그 결과, 예를 들면 임의의 제조업자에 의해 제조된 검출부(721)를 채용할 수 있도록 된다. 이와 같이 하여, 자유도가 높아진다.

또한, 본 기술의 이들의 실시 형태는, 위에 설명한 실시 형태에 결코 한정되는 일이 없고, 따라서 여러 가지의 변경을 본 기술의 주제로부터 일탈하는 일 없이 행할 수 있음에 유의하기를 바란다.

예를 들면, 각각의 기판에 배치된 구체적인 회로 블록은, 위에 설명한 실시 형태에서 기재된 회로 블록에 결코 한정되지 않는다.

[관련 출원의 상호 참조]

본 출원은, 2012년 6월 4일에 출원된 미국 가(假)특허출원 제61/655237호의 우선권의 이익을 주장하는 것이고, 이 가특허출원의 내용 전체는, 참조에 의해 본 명세서에 편입된다.

Claims (18)

- 소정의 정보를 검출하는 검출부를 갖는 제1 기판과,

상기 검출부로부터 공급되는 데이터를 처리하는 제1 처리부를 갖는 제2 기판과,

상기 제1 기판 또는 상기 제2 기판의 어느 하나로부터 공급되는 데이터를 처리하는 제2 처리부를 갖는 제3 기판을 구비하는 것을 특징으로 하는 반도체장치. - 제1항에 있어서,

상기 제1 내지 제3 기판은, 서로의 기판의 위에 순차적으로 적층되는 것을 특징으로 하는 반도체장치. - 제2항에 있어서,

상기 제3 기판은, 상기 제1 기판 또는 상기 제2 기판의 어느 하나부터의 상기 데이터를 보존하는 기억 영역부를 갖는 것을 특징으로 하는 반도체장치. - 제3항에 있어서,

상기 제3 기판의 상기 기억 영역부는, 휘발성 기억 영역 및 불휘발성 기억 영역의 양쪽을 갖는 것을 특징으로 하는 반도체장치. - 제3항에 있어서,

상기 제1 기판의 상기 검출부, 상기 제2 기판의 상기 제1 처리부, 및 상기 제3 기판의 상기 기억 영역부는, 다른 프로세스에 의해 각각 제조되는 것을 특징으로 하는 반도체장치. - 제2항에 있어서,

상기 제3 기판의 상기 기억 영역부는, 상기 제1 기판의 상기 검출부가 검출하는 상기 데이터의 일부를 출력하는 것을 특징으로 하는 반도체장치. - 제2항에 있어서,

상기 제3 기판의 상기 제2 처리부는, 상기 검출부로부터의 상기 데이터를 처리함에 의해 얻어지는 데이터를 외부에 출력하는 인터페이스를 갖는 것을 특징으로 하는 반도체장치. - 제2항에 있어서,

상기 제1 기판은 복수의 검출부를 갖는 것을 특징으로 하는 반도체장치. - 제2항에 있어서,

상기 제2 기판의 상기 제1 처리부의 발열량은, 상기 제3 기판의 상기 제2 처리부의 발열량보다도 적은 것을 특징으로 하는 반도체장치. - 제9항에 있어서,

상기 제3 기판의 상기 제2 처리부는, 발열량이 가장 많은 회로 블록을 포함하는 것을 특징으로 하는 반도체장치. - 제2항에 있어서,

상기 반도체장치는 이미지 센서인 것을 특징으로 하는 반도체장치. - 제11항에 있어서,

상기 제2 기판의 상기 제1 처리부는 아날로그 회로를 포함하는 것을 특징으로 하는 반도체장치. - 제11항에 있어서,

상기 제2 기판의 상기 제1 처리부는 DRAM을 포함하는 것을 특징으로 하는 반도체장치. - 제11항에 있어서,

상기 제2 기판의 상기 제1 처리부는, 드라이버, 기준 전압 발생부, DA 변환기, AD 변환기, OTP로 이루어지는 적어도 하나의 회로 블록을 포함하는 것을 특징으로 하는 반도체장치. - 제11항에 있어서,

상기 제3 기판의 상기 제2 처리부는 논리 회로를 포함하는 것을 특징으로 하는 반도체장치. - 제11항에 있어서,

상기 제3 기판의 상기 제2 처리부는, 파이프라인 처리부, 카운터, SRAM, MPU, 어레이 컨트롤러, 및 DRAM 컨트롤러로 이루어지는 적어도 하나의 회로 블록을 포함하는 것을 특징으로 하는 반도체장치. - 소정의 정보를 검출하는 검출 장치를 구비하고,

상기 검출 장치는,

소정의 정보를 검출하는 검출부를 갖는 제1 기판과,

상기 검출부로부터 공급되는 데이터를 처리하는 제1 처리부를 갖는 제2 기판과,

상기 제1 기판 또는 상기 제2 기판의 어느 하나로부터 공급되는 데이터를 처리하는 제2 처리부를 갖는 제3 기판을 포함하는 것을 특징으로 하는 검출 시스템. - 제17항에 있어서,

복수의 상기 검출 장치로부터의 데이터를 처리하는 MPU를 더 구비하는 것을 특징으로 하는 검출 시스템.

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US201261655237P | 2012-06-04 | 2012-06-04 | |

| US61/655,237 | 2012-06-04 | ||

| PCT/JP2013/003440 WO2013183266A2 (en) | 2012-06-04 | 2013-05-31 | Semiconductor device and sensing system |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| KR20150027061A true KR20150027061A (ko) | 2015-03-11 |

Family

ID=48614093

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020147033189A KR20150027061A (ko) | 2012-06-04 | 2013-05-31 | 반도체장치 및 검출 시스템 |

Country Status (7)

| Country | Link |

|---|---|

| US (1) | US9607971B2 (ko) |

| EP (1) | EP2856750A2 (ko) |

| JP (1) | JP2015521390A (ko) |

| KR (1) | KR20150027061A (ko) |

| CN (1) | CN104471925B (ko) |

| TW (1) | TWI599015B (ko) |

| WO (1) | WO2013183266A2 (ko) |

Families Citing this family (29)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9478579B2 (en) * | 2012-10-16 | 2016-10-25 | Omnivision Technologies, Inc. | Stacked chip image sensor with light-sensitive circuit elements on the bottom chip |

| JP6494263B2 (ja) * | 2014-02-19 | 2019-04-03 | キヤノン株式会社 | 撮像素子及び電子機器 |

| TWI648986B (zh) | 2014-04-15 | 2019-01-21 | 日商新力股份有限公司 | 攝像元件、電子機器 |

| JP6539987B2 (ja) * | 2014-11-10 | 2019-07-10 | 株式会社ニコン | 撮像素子および撮像装置 |

| US10070088B2 (en) * | 2015-01-05 | 2018-09-04 | Canon Kabushiki Kaisha | Image sensor and image capturing apparatus for simultaneously performing focus detection and image generation |

| JP6218799B2 (ja) * | 2015-01-05 | 2017-10-25 | キヤノン株式会社 | 撮像素子及び撮像装置 |

| US10145942B2 (en) * | 2015-03-27 | 2018-12-04 | Intel Corporation | Techniques for spatio-temporal compressed time of flight imaging |

| JP6272387B2 (ja) | 2015-05-29 | 2018-01-31 | キヤノン株式会社 | 撮像素子および撮像装置 |

| JP6652285B2 (ja) * | 2015-08-03 | 2020-02-19 | キヤノン株式会社 | 固体撮像装置 |

| JP6265962B2 (ja) * | 2015-11-27 | 2018-01-24 | キヤノン株式会社 | 撮像素子及び撮像装置 |

| KR102464716B1 (ko) | 2015-12-16 | 2022-11-07 | 삼성전자주식회사 | 반도체 장치 및 그 제조 방법 |

| JP2017175004A (ja) * | 2016-03-24 | 2017-09-28 | ソニー株式会社 | チップサイズパッケージ、製造方法、電子機器、および内視鏡 |

| JP2017174994A (ja) * | 2016-03-24 | 2017-09-28 | ソニー株式会社 | 撮像装置、電子機器 |

| US10998367B2 (en) | 2016-03-29 | 2021-05-04 | Nikon Corporation | Image sensor and image-capturing apparatus |

| JP6919154B2 (ja) * | 2016-03-31 | 2021-08-18 | ソニーグループ株式会社 | 固体撮像素子、撮像装置、および電子機器 |

| JP6779825B2 (ja) * | 2017-03-30 | 2020-11-04 | キヤノン株式会社 | 半導体装置および機器 |

| KR102275684B1 (ko) | 2017-04-18 | 2021-07-13 | 삼성전자주식회사 | 반도체 패키지 |

| JP7278209B2 (ja) * | 2017-04-25 | 2023-05-19 | ヌヴォトンテクノロジージャパン株式会社 | 固体撮像装置および撮像装置 |

| KR102477352B1 (ko) * | 2017-09-29 | 2022-12-15 | 삼성전자주식회사 | 반도체 패키지 및 이미지 센서 |

| JP6708620B2 (ja) * | 2017-12-15 | 2020-06-10 | キヤノン株式会社 | 撮像素子及び撮像装置 |

| JP7527755B2 (ja) * | 2018-02-09 | 2024-08-05 | キヤノン株式会社 | 光電変換装置および撮像システム |

| KR102598041B1 (ko) | 2018-02-28 | 2023-11-07 | 삼성전자주식회사 | 이미지 센서 칩 |

| KR20200097841A (ko) * | 2019-02-08 | 2020-08-20 | 삼성전자주식회사 | 이미지 센서 장치 |

| KR102661820B1 (ko) | 2019-02-11 | 2024-05-02 | 삼성전자주식회사 | 이미지 센서 및 그것의 구동 방법 |

| US10672101B1 (en) * | 2019-03-04 | 2020-06-02 | Omnivision Technologies, Inc. | DRAM with simultaneous read and write for multiwafer image sensors |

| KR20220134538A (ko) * | 2020-01-31 | 2022-10-05 | 소니 세미컨덕터 솔루션즈 가부시키가이샤 | 촬상 장치 및 촬상 방법 |

| KR20230074476A (ko) * | 2020-09-25 | 2023-05-30 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 촬상 장치 및 전자 기기 |

| CN117397253A (zh) * | 2021-05-24 | 2024-01-12 | 株式会社尼康 | 摄像元件以及摄像装置 |

| TW202308372A (zh) * | 2021-06-22 | 2023-02-16 | 美商元平台技術有限公司 | 多層堆疊的相機影像感測電路 |

Family Cites Families (25)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| DE19732755A1 (de) | 1997-07-30 | 1998-02-05 | Sika Werke Gmbh | Mehrstufig reaktive Heißklebefolie zur Herstellung von flexiblen oder starren Mehrlagenschaltungen |

| US6177333B1 (en) * | 1999-01-14 | 2001-01-23 | Micron Technology, Inc. | Method for making a trench isolation for semiconductor devices |

| US6984571B1 (en) * | 1999-10-01 | 2006-01-10 | Ziptronix, Inc. | Three dimensional device integration method and integrated device |

| JP2001127302A (ja) * | 1999-10-28 | 2001-05-11 | Hitachi Ltd | 半導体薄膜基板、半導体装置、半導体装置の製造方法および電子装置 |

| JP2001251610A (ja) | 2000-03-06 | 2001-09-14 | Canon Inc | 撮像システム、画像処理装置及び方法並びに記憶媒体 |

| RU2190251C2 (ru) | 2000-03-21 | 2002-09-27 | Леонтьев Владимир Васильевич | Устройство накопления и обработки информации |

| US7170049B2 (en) * | 2003-12-30 | 2007-01-30 | Dxray, Inc. | Pixelated cadmium zinc telluride based photon counting mode detector |

| JP2005235825A (ja) * | 2004-02-17 | 2005-09-02 | Renesas Technology Corp | 電子回路モジュール |

| TW201101476A (en) * | 2005-06-02 | 2011-01-01 | Sony Corp | Semiconductor image sensor module and method of manufacturing the same |

| US7362583B2 (en) * | 2005-12-30 | 2008-04-22 | Ati Technologies Inc. | Thermal management device for multiple heat producing devices |

| JP4289377B2 (ja) * | 2006-08-21 | 2009-07-01 | ソニー株式会社 | 物理量検出装置及び撮像装置 |

| US7400505B2 (en) * | 2006-10-10 | 2008-07-15 | International Business Machines Corporation | Hybrid cooling system and method for a multi-component electronics system |

| US7408776B2 (en) * | 2006-10-10 | 2008-08-05 | International Business Machines Corporation | Conductive heat transport cooling system and method for a multi-component electronics system |

| JP2008193359A (ja) | 2007-02-02 | 2008-08-21 | Olympus Imaging Corp | 撮像モジュール及び撮像素子パッケージ |

| JP2009005262A (ja) | 2007-06-25 | 2009-01-08 | Olympus Imaging Corp | 半導体装置および撮像装置 |

| US7884457B2 (en) | 2007-06-26 | 2011-02-08 | Stats Chippac Ltd. | Integrated circuit package system with dual side connection |

| JP2009134828A (ja) | 2007-11-30 | 2009-06-18 | Toshiba Corp | 半導体装置 |

| JP2010283787A (ja) | 2009-06-08 | 2010-12-16 | Panasonic Corp | 撮像装置 |

| JP5685898B2 (ja) | 2010-01-08 | 2015-03-18 | ソニー株式会社 | 半導体装置、固体撮像装置、およびカメラシステム |

| KR20110124065A (ko) | 2010-05-10 | 2011-11-16 | 하나 마이크론(주) | 적층형 반도체 패키지 |

| JP5974425B2 (ja) * | 2010-05-20 | 2016-08-23 | ソニー株式会社 | 固体撮像装置及びその製造方法並びに電子機器 |

| JP5633323B2 (ja) * | 2010-11-11 | 2014-12-03 | ソニー株式会社 | 固体撮像装置及び電子機器 |

| CN102158787B (zh) * | 2011-03-15 | 2015-01-28 | 迈尔森电子(天津)有限公司 | Mems麦克风与压力集成传感器及其制作方法 |

| JP5907687B2 (ja) * | 2011-09-14 | 2016-04-26 | オリンパス株式会社 | 撮像装置および信号転送装置 |

| US8890047B2 (en) * | 2011-09-21 | 2014-11-18 | Aptina Imaging Corporation | Stacked-chip imaging systems |

-

2013

- 2013-05-24 US US13/901,953 patent/US9607971B2/en active Active

- 2013-05-28 TW TW102118830A patent/TWI599015B/zh not_active IP Right Cessation

- 2013-05-31 KR KR1020147033189A patent/KR20150027061A/ko not_active Application Discontinuation

- 2013-05-31 CN CN201380027835.XA patent/CN104471925B/zh not_active Expired - Fee Related

- 2013-05-31 EP EP13728539.1A patent/EP2856750A2/en not_active Ceased

- 2013-05-31 JP JP2014552415A patent/JP2015521390A/ja active Pending

- 2013-05-31 WO PCT/JP2013/003440 patent/WO2013183266A2/en active Application Filing

Also Published As

| Publication number | Publication date |

|---|---|

| US9607971B2 (en) | 2017-03-28 |

| EP2856750A2 (en) | 2015-04-08 |

| JP2015521390A (ja) | 2015-07-27 |

| WO2013183266A2 (en) | 2013-12-12 |

| CN104471925A (zh) | 2015-03-25 |

| WO2013183266A3 (en) | 2014-02-27 |

| TWI599015B (zh) | 2017-09-11 |

| CN104471925B (zh) | 2017-12-15 |

| TW201351607A (zh) | 2013-12-16 |

| US20130320197A1 (en) | 2013-12-05 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR20150027061A (ko) | 반도체장치 및 검출 시스템 | |

| US10375334B2 (en) | Image sensor and electronic apparatus including multiple substrates | |

| US9237285B2 (en) | Solid-state image pickup device and camera system | |

| WO2014007004A1 (ja) | 固体撮像装置及び固体撮像装置の駆動方法、並びに、電子機器 | |

| US9099367B2 (en) | Image sensor and image processing device including the same | |

| US9924122B2 (en) | Solid-state imaging device, method of driving the solid-state imaging device, and electronic device | |

| US20140240565A1 (en) | Solid-state imaging device and electronic apparatus | |

| US9621830B2 (en) | Image sensor, image capturing apparatus, and cellular phone | |

| CN113286103A (zh) | 实施堆叠芯片高动态范围图像传感器的方法及系统 | |

| JP6274904B2 (ja) | 固体撮像装置及び撮像システム | |

| JP2020162111A (ja) | イメージ処理システム、イメージセンサ、イメージセンサの駆動方法 | |

| KR20150139822A (ko) | 고체 촬상 소자, 구동 방법 및 전자 기기 | |

| US9699374B2 (en) | Image device and method for memory-to-memory image processing | |

| KR20150110261A (ko) | 고체 촬상 장치 | |

| JP4661212B2 (ja) | 物理情報取得方法および物理情報取得装置並びに半導体装置 | |

| US10002892B2 (en) | Solid-state imaging device and electronic device | |

| JP7458746B2 (ja) | 光電変換装置、撮像システム及び移動体 | |

| JP5177198B2 (ja) | 物理情報取得方法および物理情報取得装置 | |

| JP2020102816A (ja) | 撮像装置および撮像装置の制御方法 | |

| JP2018057048A (ja) | 固体撮像装置及び撮像システム | |

| EP3809693B1 (en) | Image sensor having reduced parasitic capacitance | |

| US20230011827A1 (en) | Image sensor using transfer gate signal having three voltage levels, and method of operating the same | |

| US20240323563A1 (en) | Photoelectric conversion device, photoelectric conversion system, movable object and equipment |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A201 | Request for examination | ||

| E902 | Notification of reason for refusal | ||

| E902 | Notification of reason for refusal | ||

| E601 | Decision to refuse application |