KR20130020582A - 반도체 장치 - Google Patents

반도체 장치 Download PDFInfo

- Publication number

- KR20130020582A KR20130020582A KR1020120088767A KR20120088767A KR20130020582A KR 20130020582 A KR20130020582 A KR 20130020582A KR 1020120088767 A KR1020120088767 A KR 1020120088767A KR 20120088767 A KR20120088767 A KR 20120088767A KR 20130020582 A KR20130020582 A KR 20130020582A

- Authority

- KR

- South Korea

- Prior art keywords

- oxide semiconductor

- semiconductor layer

- electrode

- insulating film

- oxide

- Prior art date

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 160

- 229910003437 indium oxide Inorganic materials 0.000 claims abstract description 37

- PJXISJQVUVHSOJ-UHFFFAOYSA-N indium(iii) oxide Chemical compound [O-2].[O-2].[O-2].[In+3].[In+3] PJXISJQVUVHSOJ-UHFFFAOYSA-N 0.000 claims abstract description 37

- 239000002245 particle Substances 0.000 claims abstract description 33

- 229910052738 indium Inorganic materials 0.000 claims abstract description 13

- APFVFJFRJDLVQX-UHFFFAOYSA-N indium atom Chemical compound [In] APFVFJFRJDLVQX-UHFFFAOYSA-N 0.000 claims abstract description 13

- 239000011701 zinc Substances 0.000 claims abstract description 13

- GYHNNYVSQQEPJS-UHFFFAOYSA-N Gallium Chemical compound [Ga] GYHNNYVSQQEPJS-UHFFFAOYSA-N 0.000 claims abstract description 12

- HCHKCACWOHOZIP-UHFFFAOYSA-N Zinc Chemical compound [Zn] HCHKCACWOHOZIP-UHFFFAOYSA-N 0.000 claims abstract description 12

- 229910052733 gallium Inorganic materials 0.000 claims abstract description 12

- 229910052725 zinc Inorganic materials 0.000 claims abstract description 10

- 239000000758 substrate Substances 0.000 claims description 16

- 238000000034 method Methods 0.000 claims description 14

- 230000015572 biosynthetic process Effects 0.000 claims description 13

- XLOMVQKBTHCTTD-UHFFFAOYSA-N zinc oxide Inorganic materials [Zn]=O XLOMVQKBTHCTTD-UHFFFAOYSA-N 0.000 claims description 2

- 230000002708 enhancing effect Effects 0.000 abstract 1

- 238000009413 insulation Methods 0.000 abstract 1

- 239000010410 layer Substances 0.000 description 74

- 239000010408 film Substances 0.000 description 60

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 10

- 229910052760 oxygen Inorganic materials 0.000 description 10

- 239000001301 oxygen Substances 0.000 description 10

- 238000010586 diagram Methods 0.000 description 9

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 6

- 239000012212 insulator Substances 0.000 description 6

- 239000013078 crystal Substances 0.000 description 5

- 229910052581 Si3N4 Inorganic materials 0.000 description 3

- 239000012298 atmosphere Substances 0.000 description 3

- 238000005259 measurement Methods 0.000 description 3

- 229910052757 nitrogen Inorganic materials 0.000 description 3

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 3

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 2

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 2

- 238000000151 deposition Methods 0.000 description 2

- 230000008021 deposition Effects 0.000 description 2

- 238000009826 distribution Methods 0.000 description 2

- 239000012299 nitrogen atmosphere Substances 0.000 description 2

- 239000010936 titanium Substances 0.000 description 2

- 229910052719 titanium Inorganic materials 0.000 description 2

- 239000004925 Acrylic resin Substances 0.000 description 1

- 229920000178 Acrylic resin Polymers 0.000 description 1

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 1

- 229910052782 aluminium Inorganic materials 0.000 description 1

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 1

- 229910052786 argon Inorganic materials 0.000 description 1

- 230000005540 biological transmission Effects 0.000 description 1

- 238000005530 etching Methods 0.000 description 1

- 230000002349 favourable effect Effects 0.000 description 1

- 239000011229 interlayer Substances 0.000 description 1

- 238000004519 manufacturing process Methods 0.000 description 1

- 230000003287 optical effect Effects 0.000 description 1

- 230000001681 protective effect Effects 0.000 description 1

- 229910052814 silicon oxide Inorganic materials 0.000 description 1

- 238000004544 sputter deposition Methods 0.000 description 1

- 239000010409 thin film Substances 0.000 description 1

- 230000001131 transforming effect Effects 0.000 description 1

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 1

- 229910052721 tungsten Inorganic materials 0.000 description 1

- 239000010937 tungsten Substances 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/7869—Thin film transistors, i.e. transistors with a channel being at least partly a thin film having a semiconductor body comprising an oxide semiconductor material, e.g. zinc oxide, copper aluminium oxide, cadmium stannate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02518—Deposited layers

- H01L21/02521—Materials

- H01L21/02565—Oxide semiconducting materials not being Group 12/16 materials, e.g. ternary compounds

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Ceramic Engineering (AREA)

- Manufacturing & Machinery (AREA)

- Thin Film Transistor (AREA)

Abstract

본 발명은 도전성이 높은 산화물 반도체층을 포함한 산화물 반도체 트랜지스터를 제공한다.

인듐, 갈륨, 및 아연을 함유한 산화물(IGZO) 및 산화인듐의 입자를 포함한 산화물 반도체층과, 상기 산화물 반도체층의 채널 형성 영역과, 게이트 절연막을 개재하여 중첩된 게이트 전극과, 상기 산화물 반도체층의 소스 영역 및 드레인 영역과 중첩된 소스 전극 및 드레인 전극을 포함한 반도체 장치에 관한 것이다. 상기 반도체 장치는 톱 게이트형 산화물 반도체 트랜지스터 및 보텀 게이트형 산화물 반도체 트랜지스터 중 어느 쪽이라도 좋다. 또한, 상기 산화물 반도체층은 소스 전극 및 드레인 전극 위에 형성되어 있어도 좋고, 소스 전극 및 드레인 전극 아래에 형성되어 있어도 좋다.

인듐, 갈륨, 및 아연을 함유한 산화물(IGZO) 및 산화인듐의 입자를 포함한 산화물 반도체층과, 상기 산화물 반도체층의 채널 형성 영역과, 게이트 절연막을 개재하여 중첩된 게이트 전극과, 상기 산화물 반도체층의 소스 영역 및 드레인 영역과 중첩된 소스 전극 및 드레인 전극을 포함한 반도체 장치에 관한 것이다. 상기 반도체 장치는 톱 게이트형 산화물 반도체 트랜지스터 및 보텀 게이트형 산화물 반도체 트랜지스터 중 어느 쪽이라도 좋다. 또한, 상기 산화물 반도체층은 소스 전극 및 드레인 전극 위에 형성되어 있어도 좋고, 소스 전극 및 드레인 전극 아래에 형성되어 있어도 좋다.

Description

기재되는 발명의 일 형태는 반도체 장치에 관한 것이다.

최근, 산화물 반도체를 사용하여 트랜지스터를 제작하고 전자 디바이스나 광 디바이스에 응용하는 기술이 주목을 받고 있다. 예를 들어, 특허 문헌 1 및 특허 문헌 2에는 산화물 반도체로서 In(인듐), Ga(갈륨), Zn(아연)을 함유한 산화물(이하에서 ‘IGZO’라고 부름)을 사용하여 형성한 트랜지스터를 사용하여 표시 장치를 제작하는 기술이 기재되어 있다.

IGZO는 도전성이 낮으므로 활성층에 IGZO를 사용한 산화물 반도체 트랜지스터는 예를 들어 온 전류가 낮다는 점이 우려된다.

기재되는 발명의 일 형태에서는 상술한 점을 감안하여 도전성이 높은 산화물 반도체층을 포함한 산화물 반도체 트랜지스터를 제공하는 것을 과제 중 하나로 한다.

기재되는 발명의 일 형태는 인듐, 갈륨, 및 아연을 함유한 산화물(IGZO) 및 산화인듐의 입자를 포함한 산화물 반도체층과, 게이트 절연막을 개재(介在)하여 상기 산화물 반도체층의 채널 형성 영역과 중첩된 게이트 전극과, 상기 산화물 반도체층의 소스 영역 및 드레인 영역과 중첩된 소스 전극 및 드레인 전극을 포함한 것을 특징으로 하는 반도체 장치에 관한 것이다.

기재되는 발명의 일 형태에서 산화물 반도체층은 IGZO를 구성하는 일부의 인듐과 산소가 결합함으로써 IGZO 내에 산화인듐(In2O3)의 결정체가 입자로서 존재하는 산화물 반도체층이다.

산화인듐은 에너지 갭이 2.8eV이며 절연체에 가까운 반도체다. IGZO를 구성하는 일부의 인듐과 산소가 결합하여 절연체에 가까운 산화인듐의 입자가 형성되면, 상기 IGZO에서 전하 분포가 불균일하게 된다. 즉 IGZO에서 산화인듐의 입자는 절연체에 가깝고, 산화인듐의 입자를 형성하기 위하여 인듐과 산소가 뽑아진 부분은 다른 부분보다 도전성이 높다. 또한, 산화인듐의 입자는 산화물 반도체층 내에 흩어져 있으므로 캐리어의 이동을 방해하지 않는다. 상술한 이유로 산화인듐의 입자가 IGZO 내에 존재하는 산화물 반도체층은 높은 도전성을 갖는다.

따라서, 이러한 높은 도전성을 갖는 산화물 반도체층을 산화물 반도체 트랜지스터의 산화물 반도체층으로서 사용하면 캐리어의 이동도가 향상되어 산화물 반도체 트랜지스터의 온 전류가 높게 된다.

기재되는 발명의 일 형태는 게이트 전극과, 상기 게이트 전극을 덮는 게이트 절연막과, 상기 게이트 절연막을 개재하여 상기 게이트 전극과 중첩되며 인듐, 갈륨, 및 아연을 함유한 산화물 및 산화인듐의 입자를 포함한 산화물 반도체층과, 상기 산화물 반도체층의 소스 영역 및 드레인 영역 위에 제공된 소스 전극 및 드레인 전극을 포함한 것을 특징으로 하는 반도체 장치에 관한 것이다.

기재되는 발명의 일 형태는 게이트 전극과, 상기 게이트 전극을 덮는 게이트 절연막과, 상기 게이트 절연막 위에 형성된 소스 전극 및 드레인 전극과, 상기 게이트 절연막을 개재하여 상기 게이트 전극 위 및 상기 소스 전극 및 드레인 전극 위에 형성된 인듐, 갈륨, 및 아연을 함유한 산화물 및 산화인듐의 입자를 포함한 산화물 반도체층을 포함한 것을 특징으로 하는 반도체 장치에 관한 것이다.

기재되는 발명의 일 형태는 인듐, 갈륨, 및 아연을 함유한 산화물 및 산화인듐의 입자를 포함한 산화물 반도체층과, 상기 산화물 반도체층의 소스 영역 및 드레인 영역 위에 형성된 소스 전극 및 드레인 전극과, 상기 산화물 반도체층 및 상기 소스 전극 및 드레인 전극을 덮는 게이트 절연막과, 상기 게이트 절연막을 개재하여 상기 산화물 반도체층의 채널 형성 영역 위에 형성된 게이트 전극을 포함한 것을 특징으로 하는 반도체 장치에 관한 것이다.

기재되는 발명의 일 형태는 소스 전극 및 드레인 전극과, 상기 소스 전극 및 드레인 전극 위에 소스 영역 및 드레인 영역이 중첩되도록 형성되며 인듐, 갈륨, 및 아연을 함유한 산화물 및 산화인듐의 입자를 포함한 산화물 반도체층과, 상기 산화물 반도체층을 덮는 게이트 절연막과, 상기 게이트 절연막을 개재하여 상기 산화물 반도체층의 채널 형성 영역 위에 형성된 게이트 전극을 포함한 것을 특징으로 하는 반도체 장치에 관한 것이다.

기재되는 발명의 일 형태에 의하여 도전성이 높은 산화물 반도체층을 포함한 산화물 반도체 트랜지스터를 제공할 수 있다.

도 1a 및 도 1b는 반도체 장치의 단면도.

도 2a 및 도 2b는 반도체 장치의 단면도.

도 3은 산화물 반도체층의 단면 TEM 사진.

도 4는 산화물 반도체층을 TEM-FFT로 해석한 결과를 도시한 도면.

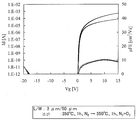

도 5는 산화물 반도체 트랜지스터의 드레인 전류(Id) 및 게이트 전압(Vg)의 관계를 도시한 도면.

도 6은 산화물 반도체 트랜지스터의 드레인 전류(Id) 및 게이트 전압(Vg)의 관계를 도시한 도면.

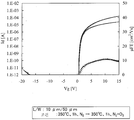

도 7은 산화물 반도체 트랜지스터의 드레인 전류(Id) 및 게이트 전압(Vg)의 관계를 도시한 도면.

도 8은 산화물 반도체 트랜지스터의 드레인 전류(Id) 및 게이트 전압(Vg)의 관계를 도시한 도면.

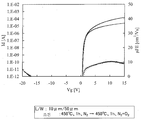

도 9는 산화물 반도체 트랜지스터의 드레인 전류(Id) 및 게이트 전압(Vg)의 관계를 도시한 도면.

도 10은 산화물 반도체 트랜지스터의 드레인 전류(Id) 및 게이트 전압(Vg)의 관계를 도시한 도면.

도 11은 산화물 반도체 트랜지스터의 드레인 전류(Id) 및 게이트 전압(Vg)의 관계를 도시한 도면.

도 12는 산화물 반도체 트랜지스터의 드레인 전류(Id) 및 게이트 전압(Vg)의 관계를 도시한 도면.

도 2a 및 도 2b는 반도체 장치의 단면도.

도 3은 산화물 반도체층의 단면 TEM 사진.

도 4는 산화물 반도체층을 TEM-FFT로 해석한 결과를 도시한 도면.

도 5는 산화물 반도체 트랜지스터의 드레인 전류(Id) 및 게이트 전압(Vg)의 관계를 도시한 도면.

도 6은 산화물 반도체 트랜지스터의 드레인 전류(Id) 및 게이트 전압(Vg)의 관계를 도시한 도면.

도 7은 산화물 반도체 트랜지스터의 드레인 전류(Id) 및 게이트 전압(Vg)의 관계를 도시한 도면.

도 8은 산화물 반도체 트랜지스터의 드레인 전류(Id) 및 게이트 전압(Vg)의 관계를 도시한 도면.

도 9는 산화물 반도체 트랜지스터의 드레인 전류(Id) 및 게이트 전압(Vg)의 관계를 도시한 도면.

도 10은 산화물 반도체 트랜지스터의 드레인 전류(Id) 및 게이트 전압(Vg)의 관계를 도시한 도면.

도 11은 산화물 반도체 트랜지스터의 드레인 전류(Id) 및 게이트 전압(Vg)의 관계를 도시한 도면.

도 12는 산화물 반도체 트랜지스터의 드레인 전류(Id) 및 게이트 전압(Vg)의 관계를 도시한 도면.

본 명세서에 기재되는 발명의 실시형태에 대하여 도면을 참조하여 이하에 설명한다. 다만, 본 명세서에 기재되는 발명은 많은 상이한 형태로 실시할 수 있고, 본 명세서에 기재된 발명의 취지 및 그 범위에서 벗어남이 없이 그 형태 및 상세한 내용을 다양하게 변경할 수 있다는 것은 당업자라면 용이하게 이해할 수 있다. 따라서, 본 실시형태의 기재 내용에 한정하여 해석되는 것은 아니다. 또한, 이하에 도시된 도면에서 동일 부분 또는 같은 기능을 갖는 부분에는 동일 부호를 붙이고 반복 설명은 생략한다.

또한, 본 명세서에 기재된 발명에서 반도체 장치란 반도체를 이용함으로써 기능하는 소자 및 장치 전반을 가리키고, 전자 회로, 표시 장치, 및 발광 장치 등을 포함한 전기 장치 및 그 전기 장치를 탑재한 전자 기기를 그 범주에 포함한다.

또한, 도면 등에 도시된 각 구성의 위치, 크기, 및 범위 등은 설명의 편의상 실제 위치, 실제 크기, 및 실제 범위 등을 나타낸 것이 아닌 경우가 있다. 따라서, 기재하는 발명은 반드시 도면 등에 기재된 위치, 크기, 및 범위 등에 한정되지 않는다.

또한, 본 명세서 등에 기재된 “제 1” “제 2” “제 3” 등의 서수사는 구성 요소의 혼동을 피하기 위하여 붙이는 것이고, 개수를 한정하는 것이 아닌 것을 부기한다.

도 1a 내지 도 2b에 본 실시형태의 산화물 반도체 트랜지스터의 구성을 도시하였다.

도 1a에 도시된 산화물 반도체 트랜지스터(101)는 기판(100) 위에 하지 절연막(102)이 형성되어 있고, 하지 절연막(102) 위에 형성된 게이트 전극(103)과, 하지 절연막(102) 및 게이트 전극(103)을 덮는 게이트 절연막(104)과, 게이트 절연막(104)을 개재하여 게이트 전극(103)과 중첩되며 활성층으로서 기능하는 산화물 반도체층(105)과, 산화물 반도체층(105)의 소스 영역 및 드레인 영역 위에 형성된 소스 전극 및 드레인 전극으로서 기능하는 전극(106a) 및 전극(106b)을 포함한다.

도 1a에 도시된 산화물 반도체 트랜지스터(101)는 게이트 전극(103)이 산화물 반도체층(105) 아래에 형성된 보텀 게이트형이며 또 소스 전극 및 드레인 전극으로서 기능하는 전극(106a) 및 전극(106b)이 산화물 반도체층(105) 위에 형성된 톱 콘택트형이다.

또한, 도 1a에 도시된 산화물 반도체 트랜지스터(101)는 산화물 반도체층(105)의 게이트 전극(103)과 중첩된 영역(즉 채널 형성 영역)의 막 두께가 에칭 등에 의하여 다른 영역의 막 두께보다 얇다. 이와 같이 채널 형성 영역의 막 두께가 얇은 트랜지스터를 채널 에치형 트랜지스터라고 부르기로 한다. 도 1a에 도시된 산화물 반도체 트랜지스터(101)는 채널 에치형 트랜지스터에 한정되지 않고 채널 형성 영역 위에 보호 절연막이 형성된 채널 보호형 트랜지스터라도 좋다.

도 1b에 도시된 산화물 반도체 트랜지스터(111)는 기판(110) 위에 하지 절연막(112)이 형성되어 있고, 하지 절연막(112) 위에 형성된 게이트 전극(113)과, 하지 절연막(112) 및 게이트 전극(113)을 덮는 게이트 절연막(114)과, 게이트 절연막(114) 위에 형성된 소스 전극 및 드레인 전극으로서 기능하는 전극(116a) 및 전극(116b)과, 게이트 절연막(114)을 개재하여 게이트 전극(113) 위 및 소스 전극 및 드레인 전극으로서 기능하는 전극(116a) 및 전극(116b) 위에 형성되며 활성층으로서 기능하는 산화물 반도체층(115)을 포함한다.

또한, 도 1b에서 소스 전극 및 드레인 전극으로서 기능하는 전극(116a) 및 전극(116b)은 게이트 전극(113)과 중첩되어 있지 않지만, 필요에 따라 전극(116a)의 일부 및 전극(116b)의 일부는 각각 게이트 절연막(114)을 개재하여 게이트 전극(113)과 중첩되어 있어도 좋다.

도 1b에 도시된 산화물 반도체 트랜지스터(111)는 게이트 전극(113)이 산화물 반도체층(115) 아래에 형성되어 있는 보텀 게이트형이며 또 소스 전극 및 드레인 전극으로서 기능하는 전극(116a) 및 전극(116b)이 산화물 반도체층(115)의 일부 아래에 형성된 보텀 콘택트형이다.

도 2a에 도시된 산화물 반도체 트랜지스터(201)는 기판(200) 위에 하지 절연막(202)이 형성되어 있고, 하지 절연막(202) 위에 형성되며 활성층으로서 기능하는 산화물 반도체층(203)과, 산화물 반도체층(203) 위에 형성된 소스 전극 및 드레인 전극으로서 기능하는 전극(204a) 및 전극(204b)과, 산화물 반도체층(203), 전극(204a) 및 전극(204b) 위의 게이트 절연막(206)과, 게이트 절연막(206)을 개재하여 산화물 반도체층(203)의 채널 형성 영역(209)과 중첩되는 위치에 형성된 게이트 전극(207)을 포함한다.

도 2a에 도시된 산화물 반도체 트랜지스터(201)는 게이트 전극(207)이 산화물 반도체층(203) 위에 형성되어 있는 톱 게이트형이며 또 소스 전극 및 드레인 전극으로서 기능하는 전극(204a) 및 전극(204b)이 산화물 반도체층(203) 위에 형성되어 있는 톱 콘택트형이다.

산화물 반도체층(203)에서 전극(204a) 및 전극(204b)과 중첩된 영역(208a) 및 영역(208b)은 소스 영역 및 드레인 영역으로서 기능한다.

또한, 채널 형성 영역(209) 및 영역(208a) 사이에는 영역(211a)이 형성되어 있고, 채널 형성 영역(209) 및 영역(208b) 사이에는 영역(211b)이 형성되어 있고, 오프셋 영역으로서 기능한다.

도 2b에 도시된 산화물 반도체 트랜지스터(221)는 기판(220) 위에 하지 절연막(222)이 형성되어 있고, 하지 절연막(222) 위에 형성되며 소스 전극 및 드레인 전극으로서 기능하는 전극(224a) 및 전극(224b)과, 활성층으로서 기능하며 전극(224a) 및 전극(224b) 위에 각각 소스 영역 및 드레인 영역이 중첩되도록 형성된 산화물 반도체층(223)과, 산화물 반도체층(223), 전극(224a) 및 전극(224b) 위의 게이트 절연막(226)과, 게이트 절연막(226)을 개재하여 산화물 반도체층(223)의 채널 형성 영역(229)과 중첩된 위치에 형성된 게이트 전극(227)을 포함한다.

또한, 도 2b에서 소스 전극 및 드레인 전극으로서 기능하는 전극(224a) 및 전극(224b)은 게이트 전극(227)과 중첩되어 있지 않지만, 필요에 따라 전극(224a)의 일부 및 전극(224b)의 일부는 각각 산화물 반도체층(223) 및 게이트 절연막(226)을 개재하여 게이트 전극(227)과 중첩되어 있어도 좋다.

도 2b에 도시된 산화물 반도체 트랜지스터(221)는 게이트 전극(227)이 산화물 반도체층(223) 위에 형성되어 있는 톱 게이트형이며 또 소스 전극 및 드레인 전극으로서 기능하는 전극(224a) 및 전극(224b)이 산화물 반도체층(223) 아래에 형성된 보텀 콘택트형이다.

산화물 반도체층(223)에서 전극(224a) 및 전극(224b) 각각과 중첩된 영역(228a) 및 영역(228b)은 소스 영역 및 드레인 영역으로서 기능한다.

또한, 채널 형성 영역(229) 및 영역(228a) 사이에는 영역(231a)이 형성되어 있고, 채널 형성 영역(229) 및 영역(228b) 사이에는 영역(231b)이 형성되어 있고, 오프셋 영역으로서 기능한다.

도 1a의 산화물 반도체 트랜지스터(101)의 산화물 반도체층(105), 도 1b의 산화물 반도체 트랜지스터(111)의 산화물 반도체층(115), 도 2a의 산화물 반도체 트랜지스터(201)의 산화물 반도체층(203), 도 2b의 산화물 반도체 트랜지스터(221)의 산화물 반도체층(223)은 IGZO 및 산화인듐의 입자를 포함한 산화물 반도체층이다.

상술한 바와 같이, IGZO 및 산화인듐의 입자를 포함한 산화물 반도체층이란 IGZO를 구성하는 일부의 인듐과 산소가 결합하여 산화인듐(In2O3)의 결정체가 입자로서 IGZO 내에 존재하는 산화물 반도체층이다.

산화인듐은 에너지 갭이 2.8eV이며 절연체에 가까운 반도체다. IGZO를 구성하는 일부의 인듐과 산소가 결합하여 절연체에 가까운 산화인듐의 입자가 형성되면, 상기 IGZO에서 전하 분포가 불균일하게 된다. 즉 IGZO에서 산화인듐의 입자는 절연체에 가깝고, 산화인듐의 입자를 형성하기 위하여 인듐과 산소가 뽑아진 부분은 다른 부분보다 도전성이 높다. 또한, 산화인듐의 입자는 산화물 반도체층 내에 흩어져 있으므로 캐리어의 이동을 방해하지 않는다. 상술한 이유로 산화인듐의 입자가 IGZO 내에 존재하는 산화물 반도체층은 높은 도전성을 갖는다.

따라서, IGZO 및 산화인듐의 입자를 포함한 산화물 반도체층을 포함한 산화물 반도체 트랜지스터는 도전성이 높다. 도전성이 높은 산화물 반도체 트랜지스터는 예를 들어 온 전류가 높다는 이점을 갖는다.

도 3은 본 실시형태에 사용하는 IGZO 및 입자를 포함한 산화물 반도체층의 단면 TEM 사진이다.

도 3에 나타낸 IGZO 및 입자를 포함한 산화물 반도체층은 기판 온도 250℃로 스퍼터링법을 사용하여 형성하였다.

입자를 푸리에 변환 투과 전자 현미경(Transmission Electron Microscopy-Fast Fourier Transform: TEM-FFT)으로 해석한 결과, 입자가 산화인듐인 것이 확인되었다. 입자가 산화인듐인 것을 이하에 설명한다.

TEM-FFT에서는 얻어진 격자상 패턴을 푸리에 변환함으로써 패턴의 스폿 위치를 해석할 수 있다. 이로써, 결정 면 간격이나 결정 면 방위를 해석할 수 있다.

본 실시형태에서는 산화물 반도체층 내의 입자를 TEM-FFT로 해석한 결과, 결정 면 간격을 얻었다. 산화물 반도체층 내의 입자의 d값은 A:0.501nm, B:0.265nm, C:0.302nm이었다(도 4 참조). 산화인듐(In2O3)의 d값은 A:0.506nm, B:0.270nm, C:0.320nm이므로 입자 성분이 산화인듐(In2O3)인 것이 시사되었다.

도 5 내지 도 12에 본 실시형태의 산화물 반도체층을 사용한 산화물 반도체 트랜지스터의 드레인 전류(Id) 및 게이트 전압(Vg)의 관계를 도시하였다.

도 5 내지 도 12의 측정에서 사용한 산화물 반도체 트랜지스터는 도 1a에서 도시한 보텀 게이트·톱 콘택트형 산화물 반도체 트랜지스터(101)다. 도 5의 측정에서 사용한 산화물 반도체 트랜지스터(101)에서 하지 절연막(102)으로서 막 두께가 100nm인 질화실리콘막에 막 두께가 150nm인 산질화실리콘막을 적층한 것을 사용하였다. 게이트 전극(103)으로서는 막 두께가 100nm인 텅스텐(W)을 사용하였다. 게이트 절연막(104)으로서는 막 두께가 100nm인 산소 함유 질화실리콘막을 사용하였다.

산화물 반도체층(105)은 성막 압력 0.3Pa, 성막 파워 9kW(AC), 아르곤에 대한 산소(O2) 유량비 50%, 기판 온도 150℃의 조건으로 막 두께가 35nm가 되도록 형성하였다. 또한, 상기 조건으로 성막한 후, 질소 분위기하에서 350℃로 1시간 소성하고 나서 질소 및 산소 분위기하에서 350℃로 1시간 소성한 산화물 반도체층(도 5, 도 7, 도 9, 도 11) 및 질소 분위기하에서 450℃로 1시간 소성하고 나서 질소 및 산소 분위기하에서 450℃로 1시간 소성한 산화물 반도체층(도 6, 도 8, 도 10, 도 12)을 산화물 반도체층(105)으로서 사용하였다.

전극(106a) 및 전극(106b)은 막 두께가 100nm인 티타늄막, 막 두께가 400nm인 알루미늄막, 및 막 두께가 100nm인 티타늄막을 적층한 적층막을 사용하여 형성하였다.

또한, 채널 길이 L 및 채널 폭 W가 3μm 및 3μm(도 5 및 도 6), 3μm 및 50μm(도 7 및 도 8), 6μm 및 50μm(도 9 및 도 10), 및 10μm 및 50μm(도 11 및 도 12)의 산화물 반도체 트랜지스터를 제작하였다.

층간 절연막(도시하지 않았음)은 막 두께가 400nm인 산화실리콘막 및 막 두께가 1500nm인 감광성 아크릴 수지막을 사용하여 산화물 반도체 트랜지스터(101)를 덮도록 형성하였다.

또한, 마지막에 질소 분위기하에서 250℃로 1시간 소성하였다.

도 5 내지 도 12에 도시한 바와 같이, 도 5 내지 도 12의 측정에서 사용한 산화물 반도체 트랜지스터는 온 전류의 값에 약간 차이가 있지만 모두 높은 온 전류를 나타냈다. 따라서, 본 실시형태에 의하여 온 전류가 높은 양호한 산화물 반도체 트랜지스터를 얻을 수 있었다.

100: 기판 101: 산화물 반도체 트랜지스터

102: 하지 절연막 103: 게이트 전극

104: 게이트 절연막 105: 산화물 반도체층

106a: 전극 106b: 전극

110: 기판 111: 산화물 반도체 트랜지스터

112: 하지 절연막 113: 게이트 전극

114: 게이트 절연막 115: 산화물 반도체층

116a: 전극 116b: 전극

200: 기판 201: 산화물 반도체 트랜지스터

202: 하지 절연막 203: 산화물 반도체층

204a: 전극 204b: 전극

206: 게이트 절연막 207: 게이트 전극

208a: 영역 208b: 영역

209: 채널 형성 영역 211a: 영역

211b: 영역 220: 기판

221: 산화물 반도체 트랜지스터 222: 하지 절연막

223: 산화물 반도체층 224a: 전극

224b: 전극 226: 게이트 절연막

227: 게이트 전극 228a: 영역

228b: 영역 229: 채널 형성 영역

231a: 영역 231b: 영역

102: 하지 절연막 103: 게이트 전극

104: 게이트 절연막 105: 산화물 반도체층

106a: 전극 106b: 전극

110: 기판 111: 산화물 반도체 트랜지스터

112: 하지 절연막 113: 게이트 전극

114: 게이트 절연막 115: 산화물 반도체층

116a: 전극 116b: 전극

200: 기판 201: 산화물 반도체 트랜지스터

202: 하지 절연막 203: 산화물 반도체층

204a: 전극 204b: 전극

206: 게이트 절연막 207: 게이트 전극

208a: 영역 208b: 영역

209: 채널 형성 영역 211a: 영역

211b: 영역 220: 기판

221: 산화물 반도체 트랜지스터 222: 하지 절연막

223: 산화물 반도체층 224a: 전극

224b: 전극 226: 게이트 절연막

227: 게이트 전극 228a: 영역

228b: 영역 229: 채널 형성 영역

231a: 영역 231b: 영역

Claims (17)

- 반도체 장치에 있어서,

인듐, 갈륨, 및 아연을 함유한 산화물 및 산화인듐의 입자를 포함하는 산화물 반도체층과;

게이트 절연막을 개재하여 상기 산화물 반도체층의 채널 형성 영역과 중첩된 게이트 전극과;

상기 산화물 반도체층의 소스 영역 및 드레인 영역과 중첩된 소스 전극 및 드레인 전극을 포함하는, 반도체 장치. - 제 1 항에 있어서,

상기 산화물 반도체층은 상기 채널 형성 영역에 인접된 오프셋 영역을 포함하는, 반도체 장치. - 제 1 항에 있어서,

상기 산화물 반도체층 아래에 기판과 하지 절연막을 더 포함하는, 반도체 장치. - 반도체 장치에 있어서,

게이트 전극과;

상기 게이트 전극을 덮는 게이트 절연막과;

인듐, 갈륨, 및 아연을 함유한 산화물 및 산화인듐의 입자를 포함하고 상기 게이트 절연막을 개재하여 상기 게이트 전극과 중첩되는 산화물 반도체층과;

상기 산화물 반도체층의 소스 영역 및 드레인 영역 위의 소스 전극 및 드레인 전극을 포함하는, 반도체 장치. - 제 4 항에 있어서,

상기 산화물 반도체층은 채널 에치형 트랜지스터에 포함되는, 반도체 장치. - 제 4 항에 있어서,

상기 산화물 반도체층은 채널 보호형 트랜지스터에 포함되는, 반도체 장치. - 제 4 항에 있어서,

상기 게이트 전극 아래에 기판과 하지 절연막을 더 포함하는, 반도체 장치. - 반도체 장치에 있어서,

게이트 전극과;

상기 게이트 전극을 덮는 게이트 절연막과;

상기 게이트 절연막 위의 소스 전극 및 드레인 전극과;

인듐, 갈륨, 및 아연을 함유한 산화물 및 산화인듐의 입자를 포함하고 상기 게이트 절연막을 개재하여 상기 게이트 전극 위에 위치하고 상기 소스 전극 및 상기 드레인 전극 위에 위치하는 산화물 반도체층을 포함하는, 반도체 장치. - 제 8 항에 있어서,

상기 산화물 반도체층은 채널 에치형 트랜지스터에 포함되는, 반도체 장치. - 제 8 항에 있어서,

상기 산화물 반도체층은 채널 보호형 트랜지스터에 포함되는, 반도체 장치. - 제 8 항에 있어서,

상기 게이트 전극 아래에 기판과 하지 절연막을 더 포함하는, 반도체 장치. - 반도체 장치에 있어서,

인듐, 갈륨, 및 아연을 함유한 산화물 및 산화인듐의 입자를 포함하는 산화물 반도체층과;

상기 산화물 반도체층의 소스 영역 및 드레인 영역 위의 소스 전극 및 드레인 전극과;

상기 산화물 반도체층, 상기 소스 전극, 상기 드레인 전극을 덮는 게이트 절연막과;

상기 게이트 절연막을 개재하여 상기 산화물 반도체층의 채널 형성 영역 위의 게이트 전극을 포함하는, 반도체 장치. - 제 12 항에 있어서,

상기 산화물 반도체층은 상기 채널 형성 영역에 인접된 오프셋 영역을 포함하는, 반도체 장치. - 제 12 항에 있어서,

상기 산화물 반도체층 아래에 기판과 하지 절연막을 더 포함하는, 반도체 장치. - 반도체 장치에 있어서,

소스 전극 및 드레인 전극과;

상기 소스 전극 및 상기 드레인 전극 위의 산화물 반도체층으로서, 인듐, 갈륨, 및 아연을 함유한 산화물 및 산화인듐의 입자를 포함하고 상기 소스 전극 및 상기 드레인 전극과 중첩되는 소스 영역 및 드레인 영역을 포함하는, 상기 산화물 반도체층과;

상기 산화물 반도체층을 덮는 게이트 절연막과;

상기 게이트 절연막을 개재하여 상기 산화물 반도체층의 채널 형성 영역 위의 게이트 전극을 포함하는, 반도체 장치. - 제 15 항에 있어서,

상기 산화물 반도체층은 상기 채널 형성 영역에 인접된 오프셋 영역을 포함하는, 반도체 장치. - 제 15 항에 있어서,

상기 산화물 반도체층 아래에 기판과 하지 절연막을 더 포함하는, 반도체 장치.

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JPJP-P-2011-178799 | 2011-08-18 | ||

| JP2011178799 | 2011-08-18 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| KR20130020582A true KR20130020582A (ko) | 2013-02-27 |

Family

ID=47711996

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020120088767A KR20130020582A (ko) | 2011-08-18 | 2012-08-14 | 반도체 장치 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US9614095B2 (ko) |

| JP (2) | JP6006572B2 (ko) |

| KR (1) | KR20130020582A (ko) |

Families Citing this family (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| TWI686874B (zh) | 2014-12-26 | 2020-03-01 | 日商半導體能源研究所股份有限公司 | 半導體裝置、顯示裝置、顯示模組、電子裝置、氧化物及氧化物的製造方法 |

| CN106158857B (zh) * | 2015-04-21 | 2020-12-22 | 联华电子股份有限公司 | 半导体元件及其制作方法 |

| CN106558538B (zh) * | 2015-09-18 | 2019-09-13 | 鸿富锦精密工业(深圳)有限公司 | 阵列基板、显示装置及阵列基板的制备方法 |

Family Cites Families (111)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS60198861A (ja) | 1984-03-23 | 1985-10-08 | Fujitsu Ltd | 薄膜トランジスタ |

| JPH0244256B2 (ja) | 1987-01-28 | 1990-10-03 | Kagaku Gijutsucho Mukizaishitsu Kenkyushocho | Ingazn2o5deshimesarerurotsuhoshokeinosojokozoojusurukagobutsuoyobisonoseizoho |

| JPH0244258B2 (ja) | 1987-02-24 | 1990-10-03 | Kagaku Gijutsucho Mukizaishitsu Kenkyushocho | Ingazn3o6deshimesarerurotsuhoshokeinosojokozoojusurukagobutsuoyobisonoseizoho |

| JPS63210023A (ja) | 1987-02-24 | 1988-08-31 | Natl Inst For Res In Inorg Mater | InGaZn↓4O↓7で示される六方晶系の層状構造を有する化合物およびその製造法 |

| JPH0244260B2 (ja) | 1987-02-24 | 1990-10-03 | Kagaku Gijutsucho Mukizaishitsu Kenkyushocho | Ingazn5o8deshimesarerurotsuhoshokeinosojokozoojusurukagobutsuoyobisonoseizoho |

| JPH0244262B2 (ja) | 1987-02-27 | 1990-10-03 | Kagaku Gijutsucho Mukizaishitsu Kenkyushocho | Ingazn6o9deshimesarerurotsuhoshokeinosojokozoojusurukagobutsuoyobisonoseizoho |

| JPH0244263B2 (ja) | 1987-04-22 | 1990-10-03 | Kagaku Gijutsucho Mukizaishitsu Kenkyushocho | Ingazn7o10deshimesarerurotsuhoshokeinosojokozoojusurukagobutsuoyobisonoseizoho |

| JPH05251705A (ja) | 1992-03-04 | 1993-09-28 | Fuji Xerox Co Ltd | 薄膜トランジスタ |

| JP3479375B2 (ja) | 1995-03-27 | 2003-12-15 | 科学技術振興事業団 | 亜酸化銅等の金属酸化物半導体による薄膜トランジスタとpn接合を形成した金属酸化物半導体装置およびそれらの製造方法 |

| DE69635107D1 (de) | 1995-08-03 | 2005-09-29 | Koninkl Philips Electronics Nv | Halbleiteranordnung mit einem transparenten schaltungselement |

| JP3625598B2 (ja) | 1995-12-30 | 2005-03-02 | 三星電子株式会社 | 液晶表示装置の製造方法 |

| JP4170454B2 (ja) | 1998-07-24 | 2008-10-22 | Hoya株式会社 | 透明導電性酸化物薄膜を有する物品及びその製造方法 |

| JP2000150861A (ja) | 1998-11-16 | 2000-05-30 | Tdk Corp | 酸化物薄膜 |

| JP3276930B2 (ja) | 1998-11-17 | 2002-04-22 | 科学技術振興事業団 | トランジスタ及び半導体装置 |

| TW460731B (en) | 1999-09-03 | 2001-10-21 | Ind Tech Res Inst | Electrode structure and production method of wide viewing angle LCD |

| JP4089858B2 (ja) | 2000-09-01 | 2008-05-28 | 国立大学法人東北大学 | 半導体デバイス |

| KR20020038482A (ko) | 2000-11-15 | 2002-05-23 | 모리시타 요이찌 | 박막 트랜지스터 어레이, 그 제조방법 및 그것을 이용한표시패널 |

| JP3997731B2 (ja) | 2001-03-19 | 2007-10-24 | 富士ゼロックス株式会社 | 基材上に結晶性半導体薄膜を形成する方法 |

| JP2002289859A (ja) | 2001-03-23 | 2002-10-04 | Minolta Co Ltd | 薄膜トランジスタ |

| JP3925839B2 (ja) | 2001-09-10 | 2007-06-06 | シャープ株式会社 | 半導体記憶装置およびその試験方法 |

| JP4090716B2 (ja) | 2001-09-10 | 2008-05-28 | 雅司 川崎 | 薄膜トランジスタおよびマトリクス表示装置 |

| JP4164562B2 (ja) | 2002-09-11 | 2008-10-15 | 独立行政法人科学技術振興機構 | ホモロガス薄膜を活性層として用いる透明薄膜電界効果型トランジスタ |

| EP1443130B1 (en) | 2001-11-05 | 2011-09-28 | Japan Science and Technology Agency | Natural superlattice homologous single crystal thin film, method for preparation thereof, and device using said single crystal thin film |

| JP4083486B2 (ja) | 2002-02-21 | 2008-04-30 | 独立行政法人科学技術振興機構 | LnCuO(S,Se,Te)単結晶薄膜の製造方法 |

| US7049190B2 (en) | 2002-03-15 | 2006-05-23 | Sanyo Electric Co., Ltd. | Method for forming ZnO film, method for forming ZnO semiconductor layer, method for fabricating semiconductor device, and semiconductor device |

| JP3933591B2 (ja) | 2002-03-26 | 2007-06-20 | 淳二 城戸 | 有機エレクトロルミネッセント素子 |

| US7339187B2 (en) | 2002-05-21 | 2008-03-04 | State Of Oregon Acting By And Through The Oregon State Board Of Higher Education On Behalf Of Oregon State University | Transistor structures |

| JP2004022625A (ja) | 2002-06-13 | 2004-01-22 | Murata Mfg Co Ltd | 半導体デバイス及び該半導体デバイスの製造方法 |

| US7105868B2 (en) | 2002-06-24 | 2006-09-12 | Cermet, Inc. | High-electron mobility transistor with zinc oxide |

| US7067843B2 (en) | 2002-10-11 | 2006-06-27 | E. I. Du Pont De Nemours And Company | Transparent oxide semiconductor thin film transistors |

| JP4166105B2 (ja) | 2003-03-06 | 2008-10-15 | シャープ株式会社 | 半導体装置およびその製造方法 |

| JP2004273732A (ja) | 2003-03-07 | 2004-09-30 | Sharp Corp | アクティブマトリクス基板およびその製造方法 |

| JP4108633B2 (ja) | 2003-06-20 | 2008-06-25 | シャープ株式会社 | 薄膜トランジスタおよびその製造方法ならびに電子デバイス |

| US7262463B2 (en) | 2003-07-25 | 2007-08-28 | Hewlett-Packard Development Company, L.P. | Transistor including a deposited channel region having a doped portion |

| US7282782B2 (en) | 2004-03-12 | 2007-10-16 | Hewlett-Packard Development Company, L.P. | Combined binary oxide semiconductor device |

| US7297977B2 (en) | 2004-03-12 | 2007-11-20 | Hewlett-Packard Development Company, L.P. | Semiconductor device |

| US7145174B2 (en) | 2004-03-12 | 2006-12-05 | Hewlett-Packard Development Company, Lp. | Semiconductor device |

| EP2246894B2 (en) | 2004-03-12 | 2018-10-10 | Japan Science and Technology Agency | Method for fabricating a thin film transistor having an amorphous oxide as a channel layer |

| US7211825B2 (en) | 2004-06-14 | 2007-05-01 | Yi-Chi Shih | Indium oxide-based thin film transistors and circuits |

| JP2006100760A (ja) | 2004-09-02 | 2006-04-13 | Casio Comput Co Ltd | 薄膜トランジスタおよびその製造方法 |

| US7285501B2 (en) | 2004-09-17 | 2007-10-23 | Hewlett-Packard Development Company, L.P. | Method of forming a solution processed device |

| US7298084B2 (en) | 2004-11-02 | 2007-11-20 | 3M Innovative Properties Company | Methods and displays utilizing integrated zinc oxide row and column drivers in conjunction with organic light emitting diodes |

| JP5118812B2 (ja) | 2004-11-10 | 2013-01-16 | キヤノン株式会社 | 電界効果型トランジスタ |

| US7453065B2 (en) | 2004-11-10 | 2008-11-18 | Canon Kabushiki Kaisha | Sensor and image pickup device |

| RU2358354C2 (ru) | 2004-11-10 | 2009-06-10 | Кэнон Кабусики Кайся | Светоизлучающее устройство |

| US7829444B2 (en) | 2004-11-10 | 2010-11-09 | Canon Kabushiki Kaisha | Field effect transistor manufacturing method |

| KR100998527B1 (ko) | 2004-11-10 | 2010-12-07 | 고쿠리츠다이가쿠호진 토쿄고교 다이가꾸 | 비정질 산화물 및 전계 효과 트랜지스터 |

| US7791072B2 (en) | 2004-11-10 | 2010-09-07 | Canon Kabushiki Kaisha | Display |

| US7863611B2 (en) | 2004-11-10 | 2011-01-04 | Canon Kabushiki Kaisha | Integrated circuits utilizing amorphous oxides |

| US7579224B2 (en) | 2005-01-21 | 2009-08-25 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing a thin film semiconductor device |

| US7608531B2 (en) | 2005-01-28 | 2009-10-27 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device, electronic device, and method of manufacturing semiconductor device |

| TWI562380B (en) | 2005-01-28 | 2016-12-11 | Semiconductor Energy Lab Co Ltd | Semiconductor device, electronic device, and method of manufacturing semiconductor device |

| US7858451B2 (en) | 2005-02-03 | 2010-12-28 | Semiconductor Energy Laboratory Co., Ltd. | Electronic device, semiconductor device and manufacturing method thereof |

| US7948171B2 (en) | 2005-02-18 | 2011-05-24 | Semiconductor Energy Laboratory Co., Ltd. | Light emitting device |

| US20060197092A1 (en) | 2005-03-03 | 2006-09-07 | Randy Hoffman | System and method for forming conductive material on a substrate |

| US8681077B2 (en) | 2005-03-18 | 2014-03-25 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device, and display device, driving method and electronic apparatus thereof |

| WO2006105077A2 (en) | 2005-03-28 | 2006-10-05 | Massachusetts Institute Of Technology | Low voltage thin film transistor with high-k dielectric material |

| US7645478B2 (en) | 2005-03-31 | 2010-01-12 | 3M Innovative Properties Company | Methods of making displays |

| US8300031B2 (en) | 2005-04-20 | 2012-10-30 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device comprising transistor having gate and drain connected through a current-voltage conversion element |

| JP2006344849A (ja) | 2005-06-10 | 2006-12-21 | Casio Comput Co Ltd | 薄膜トランジスタ |

| US7691666B2 (en) | 2005-06-16 | 2010-04-06 | Eastman Kodak Company | Methods of making thin film transistors comprising zinc-oxide-based semiconductor materials and transistors made thereby |

| US7402506B2 (en) | 2005-06-16 | 2008-07-22 | Eastman Kodak Company | Methods of making thin film transistors comprising zinc-oxide-based semiconductor materials and transistors made thereby |

| US7507618B2 (en) | 2005-06-27 | 2009-03-24 | 3M Innovative Properties Company | Method for making electronic devices using metal oxide nanoparticles |

| KR100711890B1 (ko) | 2005-07-28 | 2007-04-25 | 삼성에스디아이 주식회사 | 유기 발광표시장치 및 그의 제조방법 |

| JP2007059128A (ja) | 2005-08-23 | 2007-03-08 | Canon Inc | 有機el表示装置およびその製造方法 |

| JP5116225B2 (ja) | 2005-09-06 | 2013-01-09 | キヤノン株式会社 | 酸化物半導体デバイスの製造方法 |

| JP2007073705A (ja) | 2005-09-06 | 2007-03-22 | Canon Inc | 酸化物半導体チャネル薄膜トランジスタおよびその製造方法 |

| JP4280736B2 (ja) | 2005-09-06 | 2009-06-17 | キヤノン株式会社 | 半導体素子 |

| JP4850457B2 (ja) | 2005-09-06 | 2012-01-11 | キヤノン株式会社 | 薄膜トランジスタ及び薄膜ダイオード |

| JP5078246B2 (ja) | 2005-09-29 | 2012-11-21 | 株式会社半導体エネルギー研究所 | 半導体装置、及び半導体装置の作製方法 |

| JP5064747B2 (ja) | 2005-09-29 | 2012-10-31 | 株式会社半導体エネルギー研究所 | 半導体装置、電気泳動表示装置、表示モジュール、電子機器、及び半導体装置の作製方法 |

| EP1998375A3 (en) | 2005-09-29 | 2012-01-18 | Semiconductor Energy Laboratory Co, Ltd. | Semiconductor device having oxide semiconductor layer and manufacturing method |

| JP5037808B2 (ja) | 2005-10-20 | 2012-10-03 | キヤノン株式会社 | アモルファス酸化物を用いた電界効果型トランジスタ、及び該トランジスタを用いた表示装置 |

| JP4560505B2 (ja) | 2005-11-08 | 2010-10-13 | キヤノン株式会社 | 電界効果型トランジスタ |

| KR101358954B1 (ko) | 2005-11-15 | 2014-02-06 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 다이오드 및 액티브 매트릭스 표시장치 |

| US7998372B2 (en) * | 2005-11-18 | 2011-08-16 | Idemitsu Kosan Co., Ltd. | Semiconductor thin film, method for manufacturing the same, thin film transistor, and active-matrix-driven display panel |

| TWI292281B (en) | 2005-12-29 | 2008-01-01 | Ind Tech Res Inst | Pixel structure of active organic light emitting diode and method of fabricating the same |

| US7867636B2 (en) | 2006-01-11 | 2011-01-11 | Murata Manufacturing Co., Ltd. | Transparent conductive film and method for manufacturing the same |

| JP4977478B2 (ja) | 2006-01-21 | 2012-07-18 | 三星電子株式会社 | ZnOフィルム及びこれを用いたTFTの製造方法 |

| US7576394B2 (en) | 2006-02-02 | 2009-08-18 | Kochi Industrial Promotion Center | Thin film transistor including low resistance conductive thin films and manufacturing method thereof |

| US7977169B2 (en) | 2006-02-15 | 2011-07-12 | Kochi Industrial Promotion Center | Semiconductor device including active layer made of zinc oxide with controlled orientations and manufacturing method thereof |

| KR20070101595A (ko) | 2006-04-11 | 2007-10-17 | 삼성전자주식회사 | ZnO TFT |

| US20070252928A1 (en) | 2006-04-28 | 2007-11-01 | Toppan Printing Co., Ltd. | Structure, transmission type liquid crystal display, reflection type display and manufacturing method thereof |

| JP5028033B2 (ja) | 2006-06-13 | 2012-09-19 | キヤノン株式会社 | 酸化物半導体膜のドライエッチング方法 |

| JP4999400B2 (ja) | 2006-08-09 | 2012-08-15 | キヤノン株式会社 | 酸化物半導体膜のドライエッチング方法 |

| JP4609797B2 (ja) | 2006-08-09 | 2011-01-12 | Nec液晶テクノロジー株式会社 | 薄膜デバイス及びその製造方法 |

| JP4332545B2 (ja) | 2006-09-15 | 2009-09-16 | キヤノン株式会社 | 電界効果型トランジスタ及びその製造方法 |

| JP4274219B2 (ja) | 2006-09-27 | 2009-06-03 | セイコーエプソン株式会社 | 電子デバイス、有機エレクトロルミネッセンス装置、有機薄膜半導体装置 |

| JP5164357B2 (ja) | 2006-09-27 | 2013-03-21 | キヤノン株式会社 | 半導体装置及び半導体装置の製造方法 |

| US7622371B2 (en) | 2006-10-10 | 2009-11-24 | Hewlett-Packard Development Company, L.P. | Fused nanocrystal thin film semiconductor and method |

| US7772021B2 (en) | 2006-11-29 | 2010-08-10 | Samsung Electronics Co., Ltd. | Flat panel displays comprising a thin-film transistor having a semiconductive oxide in its channel and methods of fabricating the same for use in flat panel displays |

| JP2008140684A (ja) | 2006-12-04 | 2008-06-19 | Toppan Printing Co Ltd | カラーelディスプレイおよびその製造方法 |

| KR101303578B1 (ko) | 2007-01-05 | 2013-09-09 | 삼성전자주식회사 | 박막 식각 방법 |

| US8207063B2 (en) | 2007-01-26 | 2012-06-26 | Eastman Kodak Company | Process for atomic layer deposition |

| KR100851215B1 (ko) | 2007-03-14 | 2008-08-07 | 삼성에스디아이 주식회사 | 박막 트랜지스터 및 이를 이용한 유기 전계 발광표시장치 |

| US7795613B2 (en) | 2007-04-17 | 2010-09-14 | Toppan Printing Co., Ltd. | Structure with transistor |

| KR101325053B1 (ko) | 2007-04-18 | 2013-11-05 | 삼성디스플레이 주식회사 | 박막 트랜지스터 기판 및 이의 제조 방법 |

| KR20080094300A (ko) | 2007-04-19 | 2008-10-23 | 삼성전자주식회사 | 박막 트랜지스터 및 그 제조 방법과 박막 트랜지스터를포함하는 평판 디스플레이 |

| KR101334181B1 (ko) | 2007-04-20 | 2013-11-28 | 삼성전자주식회사 | 선택적으로 결정화된 채널층을 갖는 박막 트랜지스터 및 그제조 방법 |

| CN101663762B (zh) | 2007-04-25 | 2011-09-21 | 佳能株式会社 | 氧氮化物半导体 |

| KR101345376B1 (ko) | 2007-05-29 | 2013-12-24 | 삼성전자주식회사 | ZnO 계 박막 트랜지스터 및 그 제조방법 |

| JP5213421B2 (ja) | 2007-12-04 | 2013-06-19 | キヤノン株式会社 | 酸化物半導体薄膜トランジスタ |

| US8202365B2 (en) | 2007-12-17 | 2012-06-19 | Fujifilm Corporation | Process for producing oriented inorganic crystalline film, and semiconductor device using the oriented inorganic crystalline film |

| WO2010029865A1 (en) * | 2008-09-12 | 2010-03-18 | Semiconductor Energy Laboratory Co., Ltd. | Display device |

| JP4623179B2 (ja) | 2008-09-18 | 2011-02-02 | ソニー株式会社 | 薄膜トランジスタおよびその製造方法 |

| JP5451280B2 (ja) | 2008-10-09 | 2014-03-26 | キヤノン株式会社 | ウルツ鉱型結晶成長用基板およびその製造方法ならびに半導体装置 |

| JP2010153802A (ja) | 2008-11-20 | 2010-07-08 | Semiconductor Energy Lab Co Ltd | 半導体装置及び半導体装置の作製方法 |

| KR101658256B1 (ko) * | 2008-12-15 | 2016-09-20 | 이데미쓰 고산 가부시키가이샤 | 복합 산화물 소결체 및 그것으로 이루어지는 스퍼터링 타겟 |

| US8330156B2 (en) | 2008-12-26 | 2012-12-11 | Semiconductor Energy Laboratory Co., Ltd. | Thin film transistor with a plurality of oxide clusters over the gate insulating layer |

| JP5328414B2 (ja) | 2009-02-25 | 2013-10-30 | 富士フイルム株式会社 | トップゲート型の電界効果型トランジスタ及びその製造方法並びにそれを備えた表示装置 |

| JP2011139052A (ja) * | 2009-12-04 | 2011-07-14 | Semiconductor Energy Lab Co Ltd | 半導体記憶装置 |

-

2012

- 2012-07-26 JP JP2012165293A patent/JP6006572B2/ja active Active

- 2012-08-07 US US13/568,451 patent/US9614095B2/en active Active

- 2012-08-14 KR KR1020120088767A patent/KR20130020582A/ko not_active Application Discontinuation

-

2016

- 2016-09-09 JP JP2016176490A patent/JP6219468B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| US20130043465A1 (en) | 2013-02-21 |

| JP6006572B2 (ja) | 2016-10-12 |

| JP2017011292A (ja) | 2017-01-12 |

| JP2013058738A (ja) | 2013-03-28 |

| US9614095B2 (en) | 2017-04-04 |

| JP6219468B2 (ja) | 2017-10-25 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US10686064B2 (en) | Nitride semiconductor device and fabrication method therefor | |

| US8354715B2 (en) | Semiconductor device and method of fabricating the same | |

| JP4737471B2 (ja) | 半導体装置およびその製造方法 | |

| US9570565B2 (en) | Field effect power transistor metalization having a comb structure with contact fingers | |

| JP6401053B2 (ja) | 半導体装置および半導体装置の製造方法 | |

| US10439060B2 (en) | Semiconductor device and method of manufacturing semiconductor device | |

| WO2016104264A1 (ja) | 半導体装置 | |

| US10396149B2 (en) | Semiconductor device and method of manufacturing semiconductor device | |

| JP6705155B2 (ja) | 半導体装置および半導体装置の製造方法 | |

| US20180350900A1 (en) | Silicon carbide semiconductor device and method of manufacturing silicon carbide semiconductor device | |

| US8420421B2 (en) | Method for fabricating a GaN-based thin film transistor | |

| US10249725B2 (en) | Transistor with a gate metal layer having varying width | |

| JP2018157100A (ja) | 窒化物半導体装置 | |

| JP6219468B2 (ja) | 半導体装置 | |

| JP2013065612A (ja) | 窒化物半導体装置およびその製造方法 | |

| TW201947766A (zh) | 高電子遷移率電晶體 | |

| Huang et al. | Enhancement-mode InAlN/GaN power MOSHEMT on silicon with Schottky tri-drain extension | |

| US8841708B2 (en) | Method and system for a GAN vertical JFET with self-aligned source metallization | |

| US10381471B2 (en) | Semiconductor device and manufacturing method | |

| TWI556430B (zh) | 非對稱閘極的穿隧式電晶體 | |

| JP2023133798A (ja) | 窒化物半導体デバイス | |

| WO2020062275A1 (zh) | 栅控二极管及芯片 | |

| WO2019116464A1 (ja) | 半導体装置及び半導体装置の製造方法 | |

| WO2017086253A1 (ja) | ダイヤモンド電子素子 | |

| KR20140039772A (ko) | 질화물계 반도체 소자 및 그 제조 방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A201 | Request for examination | ||

| E902 | Notification of reason for refusal | ||

| E601 | Decision to refuse application |