KR20100038148A - 배선 기판 및 그 제조 방법 - Google Patents

배선 기판 및 그 제조 방법 Download PDFInfo

- Publication number

- KR20100038148A KR20100038148A KR1020090092778A KR20090092778A KR20100038148A KR 20100038148 A KR20100038148 A KR 20100038148A KR 1020090092778 A KR1020090092778 A KR 1020090092778A KR 20090092778 A KR20090092778 A KR 20090092778A KR 20100038148 A KR20100038148 A KR 20100038148A

- Authority

- KR

- South Korea

- Prior art keywords

- electrode pad

- metal layer

- metal

- forming

- layer

- Prior art date

Links

Images

Classifications

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/10—Apparatus or processes for manufacturing printed circuits in which conductive material is applied to the insulating support in such a manner as to form the desired conductive pattern

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/46—Manufacturing multilayer circuits

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/48—Manufacture or treatment of parts, e.g. containers, prior to assembly of the devices, using processes not provided for in a single one of the subgroups H01L21/06 - H01L21/326

- H01L21/4814—Conductive parts

- H01L21/4846—Leads on or in insulating or insulated substrates, e.g. metallisation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/12—Mountings, e.g. non-detachable insulating substrates

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/498—Leads, i.e. metallisations or lead-frames on insulating substrates, e.g. chip carriers

- H01L23/49811—Additional leads joined to the metallisation on the insulating substrate, e.g. pins, bumps, wires, flat leads

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/498—Leads, i.e. metallisations or lead-frames on insulating substrates, e.g. chip carriers

- H01L23/49822—Multilayer substrates

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/498—Leads, i.e. metallisations or lead-frames on insulating substrates, e.g. chip carriers

- H01L23/49827—Via connections through the substrates, e.g. pins going through the substrate, coaxial cables

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/02—Details

- H05K1/11—Printed elements for providing electric connections to or between printed circuits

- H05K1/111—Pads for surface mounting, e.g. lay-out

- H05K1/112—Pads for surface mounting, e.g. lay-out directly combined with via connections

- H05K1/113—Via provided in pad; Pad over filled via

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/46—Manufacturing multilayer circuits

- H05K3/4644—Manufacturing multilayer circuits by building the multilayer layer by layer, i.e. build-up multilayer circuits

- H05K3/4682—Manufacture of core-less build-up multilayer circuits on a temporary carrier or on a metal foil

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L2224/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

- H01L2224/161—Disposition

- H01L2224/16151—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/16221—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/16225—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L2224/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

- H01L2224/161—Disposition

- H01L2224/16151—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/16221—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/16225—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

- H01L2224/16235—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation the bump connector connecting to a via metallisation of the item

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/00011—Not relevant to the scope of the group, the symbol of which is combined with the symbol of this group

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/00014—Technical content checked by a classifier the subject-matter covered by the group, the symbol of which is combined with the symbol of this group, being disclosed without further technical details

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01046—Palladium [Pd]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01079—Gold [Au]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/151—Die mounting substrate

- H01L2924/1517—Multilayer substrate

- H01L2924/15172—Fan-out arrangement of the internal vias

- H01L2924/15174—Fan-out arrangement of the internal vias in different layers of the multilayer substrate

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/03—Conductive materials

- H05K2201/0332—Structure of the conductor

- H05K2201/0335—Layered conductors or foils

- H05K2201/0338—Layered conductor, e.g. layered metal substrate, layered finish layer, layered thin film adhesion layer

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/03—Conductive materials

- H05K2201/0332—Structure of the conductor

- H05K2201/0335—Layered conductors or foils

- H05K2201/0341—Intermediate metal, e.g. before reinforcing of conductors by plating

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/09—Shape and layout

- H05K2201/09209—Shape and layout details of conductors

- H05K2201/09372—Pads and lands

- H05K2201/09472—Recessed pad for surface mounting; Recessed electrode of component

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/10—Details of components or other objects attached to or integrated in a printed circuit board

- H05K2201/10613—Details of electrical connections of non-printed components, e.g. special leads

- H05K2201/10621—Components characterised by their electrical contacts

- H05K2201/10674—Flip chip

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2203/00—Indexing scheme relating to apparatus or processes for manufacturing printed circuits covered by H05K3/00

- H05K2203/03—Metal processing

- H05K2203/0353—Making conductive layer thin, e.g. by etching

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2203/00—Indexing scheme relating to apparatus or processes for manufacturing printed circuits covered by H05K3/00

- H05K2203/03—Metal processing

- H05K2203/0361—Stripping a part of an upper metal layer to expose a lower metal layer, e.g. by etching or using a laser

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2203/00—Indexing scheme relating to apparatus or processes for manufacturing printed circuits covered by H05K3/00

- H05K2203/03—Metal processing

- H05K2203/0369—Etching selective parts of a metal substrate through part of its thickness, e.g. using etch resist

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2203/00—Indexing scheme relating to apparatus or processes for manufacturing printed circuits covered by H05K3/00

- H05K2203/03—Metal processing

- H05K2203/0376—Etching temporary metallic carrier substrate

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2203/00—Indexing scheme relating to apparatus or processes for manufacturing printed circuits covered by H05K3/00

- H05K2203/11—Treatments characterised by their effect, e.g. heating, cooling, roughening

- H05K2203/1184—Underetching, e.g. etching of substrate under conductors or etching of conductor under dielectrics; Means for allowing or controlling underetching

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/10—Apparatus or processes for manufacturing printed circuits in which conductive material is applied to the insulating support in such a manner as to form the desired conductive pattern

- H05K3/20—Apparatus or processes for manufacturing printed circuits in which conductive material is applied to the insulating support in such a manner as to form the desired conductive pattern by affixing prefabricated conductor pattern

- H05K3/205—Apparatus or processes for manufacturing printed circuits in which conductive material is applied to the insulating support in such a manner as to form the desired conductive pattern by affixing prefabricated conductor pattern using a pattern electroplated or electroformed on a metallic carrier

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10T—TECHNICAL SUBJECTS COVERED BY FORMER US CLASSIFICATION

- Y10T29/00—Metal working

- Y10T29/49—Method of mechanical manufacture

- Y10T29/49002—Electrical device making

- Y10T29/49117—Conductor or circuit manufacturing

- Y10T29/49124—On flat or curved insulated base, e.g., printed circuit, etc.

- Y10T29/49155—Manufacturing circuit on or in base

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Power Engineering (AREA)

- Manufacturing & Machinery (AREA)

- Ceramic Engineering (AREA)

- Production Of Multi-Layered Print Wiring Board (AREA)

- Electric Connection Of Electric Components To Printed Circuits (AREA)

- Wire Bonding (AREA)

Abstract

Description

본 발명은 전극 패드, 전극 패드에 접속되는 도전 패턴 및 전극과 도전 패턴이 매설되는 절연층을 갖는 배선 기판 및 그러한 배선 기판을 제조하는 방법에 관한 것이다.

반도체 칩 등의 전자 제품을 실장하기 위해 다양한 형상 및 구조의 배선 기판이 제시되었다. 최근, 반도체 칩의 박형화 및 소형화에 따라, 반도체 칩이 실장되는 배선 기판의 박형화 및 소형화에 대한 요구도 증가하고 있다.

박형의 배선 기판을 형성하는 방법으로서, 예를 들어 소위 빌드업(build-up) 방법이 공지되어 있다. 빌드업 방법은, 예를 들어 배선의 층간 절연체를 형성하기 위해, 에폭시 수지 재료로 이루어진 빌드업 층을 코어 기판에 적층함으로써 멀티레벨(또는 다층) 배선 기판을 제조한다.

코어 기판은 프리프레그 재료 등으로 이루어지고, 배선 기판의 제조 공정 도중에, 경화 전에 연성 빌드업 층을 지지하며, 빌드업 층의 경화에 의해 야기되는 휨을 억제한다. 그러나, 배선 기판의 기부를 형성하는 코어 기판의 두께는 빌드업 방법을 이용하여 제조되는 배선 기판의 추가적인 두께 감소를 저해한다.

빌드업 방법을 이용하여 제조되는 배선 기판의 두께를 박형화하기 위한 방법으로서, 빌드업 방법에 의해 지지판 상에 배선 기판을 형성한 후에 배선 기판(또는 빌드업 층)을 지지하는 지지판을 제거하는 방법이, 예를 들어 일본국 공개특허 제2005-5742호 공보에 개시되어 있다.

도 1은 종래의 배선 기판의 일례를 도시하는 단면도이다. 도 1에 도시된 바와 같이, 전극 패드(1)는, 예를 들어 에칭에 의해 제거되는 지지판(도시 생략) 상에 형성되고, 수지 재료로 이루어진 절연층(2)은 전극 패드(1)의 주변을 피복하도록 형성된다. 전극 패드(1)는 비아 플러그 등의 도전 패턴(3)에 접속된다. 전극 패드(1)는, 예를 들어 Au 층(1A) 및 Ni 층(1B)으로 이루어진 적층 구조로 형성될 수 있다.

빌드업 방법을 이용하여 지지판 상에 배선 기판을 형성하는 경우에, 절연층(2)의 면(2A)과 전극 패드(1)의 면(1C)은 동일 평면 상에 형성된다. 이 때문에, 도 1에 A로 지시한 부분에서, 전극 패드(1)의 측면과 절연층(2) 사이의 경계면에서 박리(delamination)가 발생한다.

상술한 박리에 대한 대응책으로서, 예를 들어 일본국 공개특허 제2005-244108호 공보에는, 전극 패드의 형상을 변경함으로써 전극 패드의 노출된 면으로부터 그 노출된 면의 반대측을 향해 연장되는 벽부를 형성하는 구조가 제안되어 있다. 그러나, 이렇게 제안된 전극 패드 구조의 경우와 같이 전극 패드의 형상이 복잡해지면, 전극 패드를 형성하는데 필요한 공정 수가 증가하게 되어, 배선 기판의 제조 비용이 증가한다.

한편, 예를 들어 일본국 공개특허 제2004-64082호 및 제2003-229512호 공보에는, 전극 패드가 절연층에 매설되는 구조가 제안되어 있다. 그러나, 이렇게 제안된 구조에 따르면, 전극 패드와 절연층 사이의 경계면에서의 박리가 충분히 억제될 수 없고, 박리로 인한 배선 기판의 신뢰성 저하를 방지하기 어렵다.

따라서, 상술한 문제점들을 억제하는, 새롭고 유용한 배선 기판 및 그 제조 방법을 제공하는 것이 본 발명의 주된 목적이다.

본 발명의 다른 목적은, 전극 패드의 측면과 절연층의 측면 사이에서의 박리 발생을 억제하여, 배선 기판의 신뢰성을 향상시키는, 배선 기판 및 그 제조 방법을 제공하는 것이다.

본 발명의 일 양태에 따르면, 제 1 면 및 상기 제 1 면과는 반대측에 위치되는 제 2 면을 가지는 전극 패드; 상기 전극 패드의 제 1 면에 접속되는 도전 패턴; 및 상기 전극 패드 및 상기 도전 패턴이 매설되는 절연층을 포함하는 배선 기판이 제공되고, 상기 절연층은 상기 전극 패드의 상기 제 2 면의 외주부를 덮는다.

본 발명의 일 양태에 따르면, 제 1 금속으로 이루어지는 지지판 상에 전극 패드를 형성하는 전극 패드 형성 단계; 상기 전극 패드와 대향하는 부분의 상기 지지판 상에, 상기 지지판을 에칭하여, 상기 지지판과 대향하는 측의 상기 전극 패드의 면을 노출하고 상기 전극 패드에 접촉하는 돌출부를 형성하는 돌출부 형성 단계; 상기 전극 패드, 상기 돌출부, 및 상기 돌출부가 형성된 상기 지지판의 면을 덮는 절연층을 형성하는 절연층 형성 단계; 상기 절연층에, 상기 전극 패드에 접속되는 도전 패턴을 형성하는 도전 패턴 형성 단계; 및 상기 도전 패턴 형성 단계 후에, 에칭에 의해 상기 돌출부가 형성된 상기 지지판을 제거함으로써, 상기 지지판과 대향하는 측의 상기 전극 패드의 면의 일부를 노출하고 상기 절연층에 상기 돌출부의 형상에 대응하는 형상을 가지는 개구부를 형성하는 지지판 제거 단계를 포함하는 배선 기판의 제조 방법이 제공된다.

본 발명의 일 양태에 따르면, 제 1 금속으로 이루어지는 지지판 상에 금속층을 형성하는 제 1 금속층 형성 단계; 상기 제 1 금속층 상에 전극 패드를 형성하는 전극 패드 형성 단계; 상기 금속층을 에칭하여, 돌출부를 형성하고 상기 돌출부와 접촉하는 상기 전극 패드의 면의 외주부를 노출하는 돌출부 형성 단계; 상기 돌출부 형성 단계 후에, 상기 돌출부, 상기 전극 패드, 및 상기 돌출부가 형성된 상기 지지판의 면을 덮도록 절연층을 형성하는 절연층 형성 단계; 상기 절연층 상에, 상기 전극 패드에 접속된 도전 패턴을 형성하는 도전 패턴 형성 단계; 상기 도전 패 턴 형성 단계 후에, 에칭에 의해 상기 지지판을 제거하는 지지판 제거 단계; 및 상기 도전 패턴 형성 단계 후에, 상기 돌출부를 제거함으로써, 상기 절연층에, 상기 돌출부와 접촉하는 상기 전극 패드의 면의 일부를 노출하고 상기 돌출부의 형상에 대응하는 형상을 가지는 개구부를 형성하는 돌출부 제거 단계를 포함하는 배선 기판의 제조 방법이 제공된다.

본 발명의 또 다른 목적 및 추가적인 특징은 첨부도면을 참조로 하기의 상세한 설명으로부터 분명해질 것이다.

본 발명에 따르면, 전극 패드의 측면과 절연층의 측면 사이에서의 박리 발생을 억제하여, 배선 기판의 신뢰성을 향상시킬 수 있다.

도 2 내지 도 63을 참조하여, 본 발명의 각 실시예를 설명한다.

(제 1 실시예)

도 2는 본 발명의 제 1 실시예에서의 반도체 장치를 도시하는 단면도이다. 본 발명에 따른 반도체 장치는 반도체 패키지라고도 명해진다.

이 제 1 실시예의 반도체 장치(10)는 배선 기판(11) 및 전자 부품(13)을 포함한다. 배선 기판(11)은 적층된 절연층(21, 22, 23), 전극 패드(25), 도전 패턴(27, 28), 비아(31), 외부 접속용 패드(32), 및 솔더 레지스트 층(34)을 포함한다.

절연층(21)은 절연층(22)의 면(22A) 상에 적층된다. 전극 패드(25)와 비아 부(44)는 절연층(21)에 매설되고, 비아부(44)는 도전 패턴(27)의 구성 요소를 형성한다. 절연층(21)은 개구부(37, 38)를 포함한다. 개구부(37)는 절연층(22)의 면(22A)과 접촉하는 절연층(21)의 부분과 반대측에 있는 절연층(21)의 부분에 형성된다. 개구부(37)는 금속층(41)의 면(41A)의 일부를 노출시키고, 여기에 전자 부품(13)에 전기적으로 접속하는 외부 접속 단자(12)가 설치된다. 금속층(41)은 전극 패드(25)를 형성하고, 면(41A)은 전극 패드(25)의 제 2 면을 형성한다. 전극 패드(25)의 제 1 면은 후술한다. 배선 기판(11)을 전자 부품(13)에 전기적으로 접속하는 단자(12)는, 예를 들어 솔더 또는 Au 범프에 의해 개구부(37) 내에 설치된다. 절연층(21)은 금속층(41)의 면(41A)의 외주부를 피복하도록 설치된다.

단자(12)가 제공되는 측에 배치된 전극 패드(25)의 면의 외주부를 덮음으로써, 즉, 금속층(41)의 면(41A)의 외주부를 덮음으로써, 전극 패드(25)의 측면과 절연층(21)의 측면 사이에서의 박리 발생을 억제할 수 있게 된다. 결과적으로, 배선 기판(11)의 신뢰성이 향상될 수 있다.

예를 들어, 절연층(21)에 의해 덮인 금속층(41)의 면(41A)의 외주부의 폭은 0.1㎛ 내지 6㎛인 것이 바람직하며, 1㎛ 내지 3㎛인 것이 더 바람직하다.

개구부(37)는 전극 패드(25)로부터 전자 부품(13)을 향해 폭이 넓어지는 형상을 갖는다. 개구부(37)의 형상이 전극 패드(25)로부터 전자 부품(13)을 향해, 즉 절연층(21)의 면(21A)을 향해 폭이 넓어지기 때문에, 단자(12)를 개구부(37) 내에 설치하는 것이 용이해진다.

금속층(41)의 직경이 100㎛인 경우에, 금속층(41)에 접속하는 부분에서의 개 구부(37)의 직경은 80㎛ 내지 90㎛로 될 수 있다. 예를 들어, 개구부(37)의 깊이는 1㎛ 내지 30㎛인 것이 바람직하고, 20㎛인 것이 더 바람직하다.

개구부(38)는 절연층(22)과 접촉하는 절연층(21)의 부분에 설치된다. 개구부(38)는 전극 패드(25)를 형성하는 금속층(42)의 면(42A)을 노출시킨다. 금속층(42)의 면(42A)은 전극 패드(25)의 제 1 면을 형성한다.

절연층(22)은 절연층(21)과 절연층(23) 사이에 제공된다. 절연층(22)은 절연층(21)의 면(21B)과 절연층(23)의 면(23A)에 접촉한다. 도전 패턴(27)을 형성하는 배선부(45)와 도전 패턴(28)을 형성하는 비아부(48)는 절연층(22)에 매설된다. 절연층(22)은 배선부(45)의 부분들을 노출시키는 개구부(47)를 갖는다.

절연층(23)은 절연층(22)의 면(22B)에 제공된다. 배선부(49)와 비아(31)는 절연층(23)에 매설된다. 절연층(23)은 배선부(49)의 일부를 노출시키는 개구부(52)를 갖는다.

예를 들어, 절연층(21, 22, 23)은 수지 재료로 이루어질 수 있다. 예를 들어, 수지 재료는 에폭시 수지, 폴리이미드 수지 등을 포함한다. 절연층(21, 22, 23)은 동일한 재료로 이루어지거나, 또는 절연층(21, 22, 23)의 적어도 두 층은 서로 다른 재료로 이루어질 수 있다.

전극 패드(25)는 단자(12)에 접속된 제 1 금속층(41) 및 도전 패턴(27)에 접속된 제 2 금속층(42)에 의해 형성된 적층 구조를 갖는다. 예를 들어, 금속층(41)은 0.005㎛ 이상의 두께, 바람직하게는 0.04㎛의 두께를 갖는 Au 층으로 형성될 수 있다. 예를 들어, 금속층(42)은 1㎛ 내지 10㎛의 두께, 바람직하게는 5㎛의 두께 를 갖는 Ni 층으로 형성될 수 있다. 금속층(41)이 Au 층으로 형성되고 금속층(42)이 Ni 층으로 형성되면, 금속층(41)과 금속층(42) 사이에는, 예를 들어 0.005㎛ 이상의 두께를 갖는 Pd 층(도시 생략)이 설치될 수 있다. 배선 기판(11) 상에 전자 부품(13)을 실장하기 위해 전극 패드(25)를 사용하면, 전극 패드(25)는 예를 들어 50㎛ 내지 150㎛의 직경을 가질 수 있다.

도전 패턴(27)은 비아부(44)와, 그 비아부(44) 상에 일체로 형성되는 배선부(45)를 포함한다. 비아부(44)는 개구부(38) 내에 설치된다. 비아부(44)는 금속층(42)에 접속된다. 배선부(45)는 절연층(21)의 면(21B) 상에 설치된다. 예를 들어, 도전 패턴(27)을 형성하는 금속 재료로서 Cu가 사용될 수 있다.

도전 패턴(28)은 비아부(48)와, 그 비아부(48) 상에 일체로 형성되는 배선부(49)를 포함한다. 비아부(48)는 개구부(47) 내에 설치된다. 비아부(48)는 배선부(45)에 접속된다. 배선부(49)는 절연층(22)의 면(22B) 상에 설치된다. 예를 들어, 도전 패턴(28)을 형성하는 금속 재료로서 Cu가 사용될 수 있다.

비아(31)는 개구부(52) 내에 설치된다. 비아(31)는 배선부(49)에 접속된다. 비아(31)는 패드(32) 상에 일체로 형성된다.

패드(32)는 절연층(23)의 면(23B) 상에 설치되며, 비아(31)에 접속된다. 패드(32)는 접속 면(32A)을 갖는다. 예를 들어, 패드(32)는 마더 보드 등의 회로 기판(도시 생략)에 전기적으로 접속된다. 회로 기판에의 전기적인 접속을 위해 패드(32)를 사용하면, 패드(32)는 예를 들어, 200㎛ 내지 1,000㎛의 직경을 가질 수 있다.

예를 들어, 비아(31) 및 패드(32)를 형성하는 재료로서 Cu가 사용될 수 있다.

솔더 레지스트 층(34)은 절연층(23)의 면(23B) 상에 설치된다. 솔더 레지스트 층(34)은 패드(32)의 접속 면(32A)을 노출시키는 개구부(34A)를 갖는다.

전자 부품(13)은 단자(12) 및 전극 패드(25)를 통해 배선 기판(11) 상에 실장된다. 예를 들어, 전자 부품(13)은 반도체 칩에 의해 형성될 수 있다.

이러한 제 1 실시예의 배선 기판에 따르면, 절연층(21)은 단자(12)가 제공되는 측의 전극 패드(24)의 면, 즉 금속층(41)의 면(41A)의 외주부를 피복한다. 따라서, 전극 패드(25)의 측면과 절연층(21)의 측면 사이에서의 박리의 발생을 억제할 수 있고, 배선 기판(11)의 신뢰성이 향상될 수 있다.

또한, 이러한 제 1 실시예의 반도체 장치에 따르면, 상술한 구조를 갖는 배선 기판(11)으로 인해, 배선 기판(11)과 전자 부품(13) 사이의 전기 접속의 신뢰성이 향상될 수 있다.

도 3 내지 도 12는 본 발명의 제 1 실시예에서의 반도체 장치의 제조 공정을 설명하는 단면도이다. 도 3 내지 도 12에서, 도 2에 도시된 반도체 장치(10)의 상응하는 부분들과 동일한 부분들은 동일한 참조 번호로 지시된다.

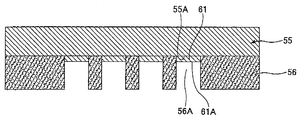

이제, 도 3 내지 도 12를 참조하여, 제 1 실시예의 반도체 장치(10)를 제조하는 방법을 설명한다. 먼저, 도 3에 도시된 제조 공정 또는 단계(이하에서는, 단순히 공정이라고 칭함)에서, 개구부(56A)를 갖는 레지스트 층(56)이 제 1 금속으로 이루어진 지지판(55)의 면(55A) 상에 형성된다. 개구부(56A)는 전극 패드(25)가 형성되는 영역에 대응하는 부분에 있는 지지판(55)의 면(55A)을 노출시키도록 형성된다. 예를 들어, 지지판(55)는 금속박, 금속판 등으로 형성될 수 있다. 제 1 금속은, 예를 들어 Cu일 수 있다. 제 1 금속에 Cu가 사용되면, 지지판(55)의 두께는, 예를 들어 35㎛ 내지 250㎛일 수 있다.

다음으로, 도 4에 도시된 전극 패드 형성 공정에서, 제 1 금속층(41) 및 제 2 금속층(42)은, 지지판(55)를 급전층(feed layer)으로 사용하는 전기 도금에 의해, 개구부(56A)에서 노출되는 지지판(55)의 면(55A) 상에 순차적으로 적층되어, 전극 패드(25)를 형성하게 된다. 금속층(41)은 제 1 금속층 형성 공정에 의해 형성되고, 금속층(42)은 제 2 금속층 형성 공정에 의해 형성된다.

예를 들어, 금속층(41)은 0.005㎛ 이상의 두께를 갖는 Au 층에 의해 형성될 수 있다. 금속층(41)에 Au 층이 사용되면, 금속층(42)은, 예를 들어 1㎛ 내지 10㎛의 두께를 갖는 Ni 층에 의해 형성될 수 있다.

배선 기판(11)상에 전극 패드(25)를 사용하여 전자 부품(13)을 실장할 때, 전극 패드(25)는, 예를 들어 50㎛ 내지 150㎛의 직경을 가질 수 있다. 금속층(41)이 Au 층에 의해 형성되고 금속층(42)이 Ni 층에 의해 형성되면, 금속층(41)과 금속층(42) 사이에는, 예를 들어 0.005㎛ 이상의 두께, 바람직하게는 0.02㎛의 두께를 갖는 Pd 층(도시 생략)이 전기 도금에 의해 형성될 수 있다.

도 5에 도시된 공정에서는, 도 4에서의 레지스트 층(56)이 제거된다. 그리고, 도 6에 도시된 돌출부 형성 공정에서는, 전극 패드(25)가 형성된 측에 위치된 도 5의 지지판(55)의 부분이 에칭되어, 지지판(55)의 면(55A)을 에칭하고 금속층의 면(41A)과 접촉하는 돌출부(58)를 형성하며, 금속층의 면(41A)의 외주부를 노출시킨다. 특히, 제 1 금속으로 이루어진 지지판(55)는 금속층(41, 42)을 에칭시키지 않는 에칭액(etchant)를 사용하여 선택적으로 에칭된다.

전극 패드(25)를 마스크로 사용하는 등방성 습식 에칭을 수행함으로써, 에칭액에 의해 달성되는 지지판(55)에 대한 사이드 에칭 및 언더컷(undercut)을 이용하여, 돌출부(58)로부터 금속층(41)의 면(41A)의 외주부를 노출시킬 수 있다. 또한, 지지판(55)를 선택적으로 에칭함으로써, 전극 패드(25)가 에칭되는 것을 방지할 수 있다.

돌출부(58)는 전극 패드(25)로부터 지지판(55)를 향해 폭이 넓어지는 형상을 갖는다. 예를 들어, 돌출부(58)는 원추대 형상을 가질 수 있다. 이 경우에, 단면도에서는, 원추대 형상을 갖는 돌출부(58)의 측면은 원추대 형상의 중심 축선에 대하여 걸-윙(gull-wing) 형상으로 내향 만곡될 수 있다. 돌출부(58)의 형상은 도 2와 관련하여 상술한 개구부(37)의 형상과 거의 동일하다.

금속층(41)의 직경이 100㎛인 경우에, 금속층(41)과 접촉하는 부분에 있는 돌출부(58)의 직경은, 예를 들어 80㎛ 내지 90㎛일 수 있다. 이 경우에, 층들이 적층되는 방향에서의 돌출부(58)의 높이는 1㎛ 내지 30㎛일 수 있다.

다음으로, 도 7에 도시된 절연층 형성 공정에서, 개구부(38)를 갖는 절연층(21)이 형성되어 전극 패드(25), 돌출부(58), 및 지지판(55)의 면(55A)을 피복한다. 절연층(21)은 에폭시 수지, 폴리이미드 수지 등으로 이루어진 수지 필름을 적층하여 형성되거나, 또는 수지를 코팅하여 형성될 수 있다.

결과적으로, 단자(12)가 제공되는 측에 위치된 전극 패드(25)의 면, 즉 금속층(41)의 면(41A)의 외주부는 절연층(21)에 의해 피복된다. 이 때문에, 전극 패드(25)의 측면과 절연층(21)의 측면 사이에서의 박리 발생을 억제할 수 있어, 배선 기판(11)의 신뢰성이 향상될 수 있다.

절연층(21)에 의해 피복된 금속층(41)의 면(41A)의 외주부의 폭은, 예를 들어 0.1㎛ 내지 6㎛일 수 있으며, 바람직하게는 1㎛ 내지 3㎛일 수 있다.

금속층(42)의 면(42A)에 대향하는 절연층(21)의 부분에는 개구부(38)가 형성되어, 금속층(42)의 면(42A)을 노출시킨다. 예를 들어, 개구부(38)는 레이저 빔 가공에 의해 형성될 수 있다. 지지판(55)의 면(55A)상에 제공된 절연층(21) 부분의 두께는, 예를 들어 55㎛ 내지 60㎛일 수 있다.

다음으로, 도 8에 도시된 도전 패턴 형성 공정에서, 도전 패턴(27)은 개구부(38) 내에 및 절연층(21)의 면(21B)상에 세미애디티브법에 의해 형성된다. 따라서, 개구부(38) 내에 형성된 비아부(44)는 제 2 금속층(42)에 접속된다. 비아부(44)는 돌출부(58)가 형성되지 않는 측에서 전극(25)에 대향하는 절연층(21)의 부분을 관통한다. 예를 들어, 도전 패턴(27)을 형성하는 재료로서는 Cu가 사용될 수 있다.

다음으로, 도 9에 도시된 공정에서, 도 7 및 도 8과 관련하여 상술된 공정과 동일한 공정이 절연층(22, 23), 도전 패턴(28), 비아(31), 및 패드(32)를 형성하기 위해 반복된다. 예를 들어, 각각의 절연층(22, 23)은 수지 재료로 형성될 수 있다. 이 경우에, 수지 재료는, 예를 들어 에폭시 수지, 폴리이미드 수지 등일 수 있다. 절연층(22, 23)이 수지로 제조되면, 각각의 절연층(22, 23)의 두께는, 예를 들어 25㎛ 내지 40㎛일 수 있다. 예를 들어, 도전 패턴(28), 비아(31), 및 패드(32)에는 Cu가 사용될 수 있다. 패드(32)의 평면 형상이 원형일 경우에는, 패드(32)의 직경은, 예를 들어 200㎛ 내지 1,000㎛일 수 있다.

다음으로, 도 10에 도시된 공정에서, 패드(32)의 접속 면(32A)을 노출시키는 개구부(34A)를 갖는 솔더 레지스트 층(34)은 공지된 방법에 의해 절연층(23)의 면(23B)에 형성된다. 따라서, 배선 기판(11)에 상응하는 구조가 지지판(55) 상에 형성된다.

도 11에 도시된 지지판 제거 공정에서, 도 10에 도시된 돌출부(58)가 형성된 지지판(55)은 에칭에 의해 제거된다. 그 결과, 금속층(41)의 면(41A)이 노출되고, 돌출부(58)의 형상에 대응하는 형상을 갖는 개구부(37)가 형성된다. 더욱 상세하게는, 돌출부(58)가 형성된 지지판(55)은 지지판(55)을 선택적으로 에칭하지만 전극 패드(25)는 에칭하지 않는 에칭액을 사용하여 제거된다. 그 결과, 이 제 1 실시예의 배선 기판(11)이 제조된다. 개구부(37)의 깊이는 1㎛ 내지 30㎛이어도 되고, 예를 들면, 20㎛가 바람직하다.

다음에, 도 12에 도시된 공정에서, 전자 부품(13)은 단자(12)와 전극 패드(25)(또는 금속층(41))를 통하여 배선 기판(11) 상에 실장된다. 따라서, 전자 부품(13)과 배선 기판(11)이 설치된 이 제 1 실시예의 반도체 장치(10)가 제조된다.

이 제 1 실시예의 배선 기판의 제조 방법에 따르면, 전극 패드(25)와 대면하 는 지지판(55)의 일부에, 지지판과 대면하는 쪽에 전극 패드(25)의 면(금속층(41)의 면(41A))의 외주부를 노출시키는 돌출부(58)를 형성하도록 지지판(55)이 에칭된다. 그 후, 절연층(21)이 전극 패드(25), 돌출부(58), 및 상기 전극 패드(25)가 형성된 쪽의 지지판(55)의 면(55A)을 덮도록 형성된다. 따라서, 절연층(21)이 지지판(55)과 대향하는 쪽의 전극 패드(25)의 면(금속층(41)의 면(41A)) 상에 형성되어, 전극 패드(25)의 측면과 절연층(21)의 측면 사이의 박리(delamination)의 발생을 억제하고, 그에 의해 배선 기판(11)의 신뢰성이 향상된다.

도 13 내지 도 16은 본 발명의 제 1 실시예의 반도체 장치의 다른 제조 공정을 설명하기 위한 단면도로서, 제 1 실시예의 반도체 장치의 제조에 사용될 수 있다. 도 13 내지 도 16에서, 도 4에 도시된 구조와 도 2에 도시된 제 1 실시예의 반도체 장치(10)의 대응 부분과 동일한 부분은 동일한 참조 번호를 부여한다.

도 13 내지 도 16을 참조하여, 제 1 실시예의 반도체 장치(10)를 제조하는데 사용될 수 있는 다른 제조 공정을 설명한다. 먼저, 도 3과 관련하여 상기 설명한 제 1 실시예의 공정과 동일한 공정을 수행하여, 도 3에 도시된 구조를 형성한다.

다음으로, 도 13에 도시된 높이 조정층 형성 공정에서, 제 1 금속(지지판(55)을 형성하는 금속)으로 이루어진 높이 조정층(61)이, 전극 패드(25)를 형성하기 전에, 전극 패드(25)가 형성되는 영역에 대응하는 부분에 지지판(55)의 면(55A) 상에 형성된다. 높이 조정층(61)이 급전층으로서 지지판(55)을 사용하여 전기 도금에 의해 형성될 수 있다. 예를 들면, Cu는 제 1 금속으로 사용될 수 있다. Cu가 제 1 금속으로 사용될 때, 높이 조정층(61)을 형성하는 Cu층은, 예를 들 면, 5㎛ 내지 15㎛의 두께를 가질 수 있다.

다음에, 도 14에 도시된 공정에서, 도 4와 관련하여 상기 설명한 공정과 동일한 공정이 실행되어 상기 높이 조정층(61)의 면(61A) 상에 금속층(41)과 금속층(42)을 순차적으로 형성한다.

다음에, 도 15에 도시된 공정에서, 도 14에서의 레지스트 층(56)이 제거된다. 다음에, 도 16에 도시된 돌출부 형성 공정에서, 전극 패드(25)가 형성된 쪽에 위치한 지지판(55)과 높이 조정층(61)의 일부가 에칭되어, 지지판(55)의 면(55A)과 높이 조정층(61)의 측벽이 에칭된다. 그 결과, 금속층(41)의 면(41A)과 접촉하고 금속층(41)의 면(41A)의 외주부를 노출시키는 돌출부(62)가 형성된다. 돌출부(62)는 지지판(55)의 일부와 에칭 후에 남아있는 높이 조정층(61)으로 구성된다. 더욱 상세하게는, 돌출부 형성 공정에서, 각각 제 1 금속으로 이루어진 지지판(55)과 높이 조정부(61)를 선택적으로 에칭하고 금속층(41, 42)을 에칭하지 않는 에칭액이, 지지판(55)과 높이 조정층(61)을 에칭하는데 사용된다.

그 후, 도 7 내지 도 12와 관련하여 상기 설명한 공정과 동일한 공정이 실행되어, 이 제 1 실시예의 반도체 장치(10)를 제조한다.

다른 제조 공정을 이용한 이 제 1 실시예의 반도체 장치의 제조 방법에 따르면, 제 1 금속으로 이루어진 높이 조정층(61)이 지지판(55) 상에 형성되어 높이 조정층(61)이 지지판(55)과 그 후에 형성되는 전극 패드(25) 사이에 삽입되고, 다음에 전극 패드(25)가 높이 조정층(61) 상에 형성된다. 또한, 돌출부(62)를 형성하는데 필요한 에칭량이나 에칭 시간을 줄이기 위하여, 전극 패드(25)가 형성되는 지 지판(55)과 높이 조정층(61)의 일부가 에칭된다. 따라서, 높이 조정층(61)이 형성되지 않은 경우와 비교하여, 배선 기판(11)의 제조 비용을 감소시킬 수 있다.

도 17은 본 발명의 제 1 실시예의 변형에서의 반도체 장치를 도시한 단면도이다. 도 17에서, 도 2에 도시된 제 1 실시예의 반도체 장치(10)의 대응 부분과 동일한 부분은 동일한 참조 번호를 부여한다.

도 17에 도시된 바와 같이, 제 1 실시예의 변형에서의 반도체 장치(65)는 제 1 실시예의 반도체 장치(10)에 설치된 배선 기판(11) 대신에, 배선 기판(66)이 설치된다. 그 외에, 반도체 장치(65)의 구조는 반도체 장치(10)의 구조와 기본적으로 동일하다.

배선 기판(66)은 배선 기판(66) 상의 전자 부품(13)을 실장하는데 사용되는 패드(32)와, 마더보드 등의 회로 기판(도시되지 않음)에 전기적 접속을 행하는데 사용되는 전극 패드(25)를 포함한다. 이 경우, 패드(32)의 직경은, 예를 들면, 50㎛ 내지 150㎛가 될 수 있다. 또한, 전극 패드(25)의 직경은, 예를 들면, 200㎛ 내지 1,000㎛가 될 수 있다.

제 1 실시예의 변형의 배선 기판(66)은 제 1 실시예의 배선 기판(11)에 의해 얻을 수 있는 것과 동일한 효과를 얻을 수 있다. 또한, 배선 기판(66)은 배선 기판(11)을 제조하는데 사용되는 것과 동일한 공정에 의해 제조될 수 있고, 배선 기판(66)의 제조 공정에 의해 얻을 수 있는 효과는 배선 기판(11)의 제조 공정에 의해 얻을 수 있는 효과와 동일하다.

반도체 장치(10, 65)는 회로판(도시되지 않음)에 접속되는 쪽의 패드 자체가 외부 접속용 단자로서 기능하는 랜드 그리드 어레이(Land Grid Array(LGA)) 구조를 갖는다. 그러나, 반도체 장치(10, 65)는 패드가 솔더 볼에 접속되는 볼 그리드 어레이(Ball Grid Array(BGA)) 구조 또는, 패드가 핀에 접속되는 핀 그리드 어레이(Pin Grid Array(PGA)) 구조를 가져도 된다.

(제 2 실시예)

도 18은 본 발명의 제 2 실시예의 반도체 장치를 도시한 단면도이다. 도 18에서, 도 2에 도시된 제 1 실시예의 반도체 장치(10)의 대응 부분과 동일한 부분은 동일한 참조 번호를 부여한다.

도 18에 도시된 바와 같이, 이 제 2 실시예의 반도체 장치(70)는 제 1 실시예의 반도체 장치(10)에 설치된 배선 기판(11) 대신에, 배선 기판(71)이 설치된다. 그 외에, 반도체 장치(70)의 구조는 반도체 장치(10)의 구조와 기본적으로 동일하다.

배선 기판(11)에 설치된 전극 패드(25) 대신에, 배선 기판(71)에 전극 패드(73)가 설치된다. 그 외에, 배선 기판(71)의 구조는 배선 기판(11)의 구조와 기본적으로 동일하다.

전극 패드(73)는 전극 패드(25)의 구조에 더하여, 제 2 금속층(42)의 면(42A)을 덮는 제 3 금속층(75)을 포함한다. 그 외에, 전극 패드(73)의 구조는 전극 패드(25)의 구조와 기본적으로 동일하다.

금속층(42)에 접속되는 면과 대향하는 면 상에 위치한 금속층(75)의 면(75A)은 절연층(21) 내에 형성된 개구부(38)에서 노출된다. 금속층(75)은 개구부(38) 내에 설치된 도전 패턴(27), 즉, 비어부(44)에 접속된다. 따라서, 전극 패드(73)는 전자 부품(13)과 도전 패턴(27)을 전기적으로 접속한다.

금속층(75)은 도전 패턴(27)과 동일한 금속, 즉, 제 1 실시예에서 사용된 제 1 금속으로 이루어진다. 바람직하게는, 금속층(75)은 금속층(42)을 형성하는 금속보다 산화되기 어려운 금속으로 이루어진다. Cu가 도전 패턴(27)을 형성하는 금속으로 사용되는 경우, 예를 들면, Cu는 금속층(75)을 형성하는 금속 재료로서 사용될 수 있다. Cu가 금속층(75)을 형성하는 금속 재료로서 사용될 때, 금속층(75)의 두께는 10㎛ 내지 20㎛가 될 수 있고, 예를 들면, 15㎛가 바람직하다. Cu는 Ni보다 산화되기 어렵다.

따라서, 금속층(42)보다 산화되기 어려운 금속층(75)을 금속층(42)의 면(42A) 상에 설치하고, 상기 금속층(75)과 도전 패턴(27)을 형성하는 비어부(44)를 접속함으로써, 전극 패드(73)와 도전 패턴(27) 사이의 전기적 접속의 신뢰성을 향상시킬 수 있다.

또한, 도전 패턴(27)을 형성하는 금속 재료가 Cu인 경우, 금속층(75)을 형성하는 금속 재료로 Cu를 사용함으로써 비어부(44)와 금속층(75) 사이의 밀착성을 향상시킬 수 있다. 그 결과, 이 경우의 전극 패드(73)와 도전 패턴(27) 사이의 전기적인 접속의 신뢰성을 더욱 향상시킬 수 있다.

전극 패드(73)가 배선 기판(71) 상에 전자 부품(13)을 실장하는데 사용될 때, 전극 패드(73)의 직경은, 예를 들면, 50㎛ 내지 150㎛가 될 수 있다. 이 경우, 상기 패드(32)는 마더보드 등의 회로 기판(도시되지 않음)에 접속되고, 상기 패드(32)의 직경은, 예를 들면, 200㎛ 내지 1,000㎛가 될 수 있다.

또한, 전극 패드(73)가 마더보드 등의 회로판(도시되지 않음)에 접속하는데 사용될 때, 전극 패드(73)의 직경은, 예를 들면, 200㎛ 내지 1,000㎛가 될 수 있다. 이 경우, 전자 부품(13)이 상기 패드(32) 상에 실장되고, 상기 패드(32)의 직경은, 예를 들면, 50㎛ 내지 150㎛가 될 수 있다.

이 제 2 실시예의 배선 기판(71)에 따르면, 금속층(42)보다 산화되기 어려운 금속층(75)은 금속층(42)의 면(42A) 상에 설치되고, 금속층(75)은 도전 패턴을 형성하는 비어부(44)에 접속된다. 따라서, 전극 패드(73)와 도전 패턴(27) 사이의 전기적인 접속의 신뢰성을 향상시킬 수 있다.

금속층(41)이 Au층에 의해 형성되고 금속층(42)이 Ni층에 의해 형성되는 경우, Pd층(도시되지 않음)은 금속층(41)과 금속층(42) 사이에 설치될 수 있다. 이 경우, Pd층의 두께는 0.005㎛ 이상이 될 수 있고, 예를 들면, 0.02㎛가 바람직하다.

도 19 내지 도 25는 본 발명의 이 제 2 실시예의 반도체 장치의 제조 공정을 설명하기 위한 단면도이다. 도 19 내지 도 25에서, 도 18에 도시된 반도체 장치(70)의 대응 부분과 동일한 부분은 동일한 참조 번호를 부여한다.

여기에서는, 도 19 내지 도 25를 참조하여, 이 제 2 실시예의 반도체 장치(70)를 제조하는 방법을 설명한다. 우선, 제 1 실시예의 도 3 및 도 4와 함께 상술한 공정과 동일한 제 1 금속층 형성 공정 및 제 2 금속층 형성 공정을 수행하여, 도 4에 도시된 구조체를 형성한다.

이어서, 도 19에 도시된 제 3 금속층 형성 공정에서, 제 1 금속으로 이루어진 지지판(55)을 급전층으로 이용하여 전해 도금함으로써, 금속층(42)의 면(42A)에 금속층(42)보다 산화되기 어려운 제 1 금속으로 이루어진 제 3 금속층(75)을 형성한다.

제 3 금속층 형성 공정에서는 도 18에 도시된 금속층(75)의 두께보다 두꺼운 금속층(75)을 형성하여, 금속층(75)은 도 21과 함께 후술하는 돌출부 형성 공정 후에 금속층(42)의 면(42A)을 덮기에 충분한 두께를 가진다. 즉, 금속층(75)은, 도 18에 도시된 금속층(75)과 돌출부 형성 공정에서 이루어지는 에칭량을 고려하여, 돌출부 형성 공정 동안에 에칭될 금속층(75)의 양 또는 두께의 합의 두께로 형성된다. 예를 들면, 제 1 금속이 Cu인 경우에, 제 1 금속층(75)은 30 ㎛ 내지 50 ㎛의 두께를 가질 수 있다.

돌출부 형성 공정에서 에칭되는 금속층(75)의 양을 고려하여, 도 18에 도시된 금속층(75)보다 두꺼운 금속층(75)을 형성함으로써, 금속층(75)과 도전 패턴(27)의 비아부(44)를 확실하게 접속할 수 있다. 결과적으로, 금속층(75)과 도전 패턴(27) 사이의 전기적 접속의 신뢰성이 향상될 수 있다.

또한, 도전 패턴(27) 및 금속층(75)을 형성하는 금속 재료로 Cu를 사용함으로써, 금속층(75)과 도전 패턴(27) 사이의 전기적인 접속의 신뢰성을 더 향상시킬 수 있다.

이어서, 도 20에 도시된 공정에서, 도 19의 레지스트 층(56)을 제거한다. 이어서, 도 21에 도시된 돌출부 형성 공정에서, 도 6과 함께 상술한 제 1 실시예의 공정과 동일한 공정을 수행하여서, 도 20의 전극 패드(73)가 형성된 측에 위치된 지지판(55)의 일부를 에칭하여, 지지판(55)의 면(55A)이 에칭된다. 그러므로, 금속층(41)의 면(41A)과 접촉하고 금속층(41)의 면(41A)의 외주부를 노출하는 돌출부(58)가 형성된다. 또한, 이 상태에서, 지지판(55)을 형성하는 제 1 금속으로 이루어지는 금속층(75)이 에칭된다. 그러나, 금속층(75)의 두께는 돌출부 형성 공정에서 에칭될 금속층(75)의 양을 고려하여, 도 19와 함께 상술한 공정에서 미리 설정되어 있다. 이 때문에, 돌출부 형성 공정에서의 금속층(75)의 에칭은 금속층(42)의 면(42A)이 노출되게 하지 않는다.

또한, 돌출부 형성 공정에서 수행되는 에칭에 의해 금속층(75)의 두께가 줄어듬으로써, 금속층(41, 42, 75)을 이루는 전극 패드(73)가 형성된다. 도 4 및 도 19 내지 도 21에 도시된 공정은 전극 패드 형성 공정에 대응한다.

예를 들면, 금속층(75)을 형성하는 금속 재료로 Cu를 이용하는 경우, 돌출부 형성 공정 후의 금속층(75)의 두께는 10 ㎛ 내지 20 ㎛일 수 있고, 15 ㎛인 것이 바람직하다.

이어서, 도 22에 도시된 절연층 형성 공정에서, 전극 패드(73), 돌출부(58), 및 돌출부(58)가 형성된 측에 위치된 지지판(55)의 면(55A)을 덮도록, 개구부(38)를 가지는 절연층(21)을 형성한다.

그러므로, 단자(12)가 설치된 측의 전극 패드(73)의 면의 외주부, 즉 금속층(41)의 면(41A)은 절연층(21)으로 덮인다. 결과적으로, 전극 패드(73)의 측면과 절열층(21)의 측면 사이의 박리의 발생을 억제하고, 배선 기판(71)의 신뢰성을 향 상시킬 수 있다.

예를 들면, 지지판(55)의 면(55A)에 설치된 절연층(21)의 두께는 65 ㎛ 내지 75 ㎛일 수 있다.

이어서, 도 23에 도시된 공정에서, 도전 패턴 형성 공정을 포함하는, 도 8 내지 도 10과 함께 상술한 제 1 실시예의 공정과 동일한 공정을 수행하여, 도전 패턴(27, 28), 비아(31), 패드(32), 및 솔더 레지스트 층(34)을 형성한다. 그러므로, 배선 기판(71)에 대응하는 구조체가 지지판(55) 상에 형성된다.

이어서, 도 24에 도시된 지지판 제거 공정에서, 도 11과 함께 상술한 제 1 실시예의 공정과 동일한 공정에 의해, 돌출부(58)가 형성된 지지판(58)을 제거한다. 그러므로, 금속층(41)의 면(41A)을 노출하고 돌출부(58)의 형태에 대응하는 형상을 가지는 개구부(37)가 절연층(21)에 형성된다. 결과적으로, 이 제 2 실시예의 배선 기판(71)이 제조된다.

이어서, 도 25에 도시된 공정에서, 단자(12) 및 전극 패드(73)(또는 금속층(41))를 통해 배선 기판(71)에, 전자 부품(13)이 실장된다. 따라서, 전자 부품(13) 및 배선 기판(71)을 포함하는 이 제 2 실시예의 반도체 장치(70)가 제조된다.

이 제 2 실시예의 배선 기판(71)을 제조하는 방법에 따르면, 제 1 금속과는 상이한 금속으로 이루어진 금속층(41)이 지지판(55) 상에 형성되고, 제 1 금속과는 상이한 금속으로 이루어진 금속층(42)이 금속층(42) 상에 형성되고, 금속층(75)이 금속층(42)의 면(42A)에 형성된다. 이 금속층(75)은 금속층(42)보다 산화되기 어 려운 제 1 금속으로 이루어진다. 또한, 이 금속층(75)은 돌출부 형성 공정 후에, 금속층(75)이 금속층(42)의 면(42A)을 덮을 수 있는 충분한 두께를 가진다. 따라서, 전자 패드(73)의 구성 요소인 금속층(75)은 도전 패턴(27)에 접속될 수 있으므로, 전극 패드(73)와 도전 패턴(27) 사이의 전기적인 접속의 신뢰성을 향상시킬 수 있다.

도 26 내지 도 31은 제 2 실시예의 반도체 장치를 제조하는데 이용될 수 있는, 본 발명의 이 제 2 실시예의 반도체 장치의 다른 제조 공정을 설명하기 위한 단면도이다. 도 26 내지 도 31에서, 도 18에 도시된 제 2 실시예의 반도체 장치(70)의 해당 부품과 동일한 부품에는 동일한 부호를 부여한다.

도 26 내지 도 31을 참조하여, 이 제 2 실시예의 반도체 장치(70)를 제조하는데 이용될 수 있는 다른 제조 공정을 설명한다. 우선, 제 1 금속층 형성 공정 및 제 2 금속층 형성 공정을 포함하는 도 3 및 도 4와 함께 상술한 제 1 실시예의 공정과 동일한 공정을 수행하여, 도 4에 도시된 구조체를 형성한다.

이어서, 도 26에 도시된 공정에서, 제 1 금속으로 이루어진 지지판(55)을 급전층으로 이용하여 전해 도금함으로써, 금속층(42)보다 산화되기 어려운 제 1 금속으로 이루어진 제 3 금속층(75)을 금속층(42)의 면(42A)에 형성한다. 그러므로, 금속층(41, 42, 75)으로 이루어진 전극 패드(73)는 지지판(55)의 면(55A)에 형성된다. 도 4 및 도 26에 도시된 공정은 전극 패드 형성 공정에 대응한다.

예를 들면, 제 1 금속으로 Cu가 이용될 수 있다. 예를 들면, 금속층(75)을 형성하는 금속 재료로 Cu를 이용하는 경우, 금속층(75)의 두께는 10 ㎛ 내지 20 ㎛ 일 수 있고, 15 ㎛인 것이 바람직하다.

이어서, 도 27에 도시된 보호층 형성 공정에서, 금속층의 면(75A)에 보호층(78)을 형성한다. 이 보호층(78)은 도 29와 함께 후술하는 돌출부 형성 공정에서 지지판을 에칭할 때, 금속층(75)이 에칭되는 것을 방지한다.

보호층(78)은 지지판(55)을 급전층으로 이용하는 전해 도금에 의해 형성될 수 있다. 보호층(78)은 제 1 금속과는 상이한 금속 재료로 이루어진다. 예를 들면, 전해 도금에 의해 형성된 Sn층, Sn-Pb층 등을 보호층(78)으로 이용할 수 있다. 예를 들면, 이 경우에, 보호층(78)의 두께는 1 ㎛ 내지 5 ㎛일 수 있다.

이어서, 도 28에 도시된 공정에서, 도 27의 보호층(56)을 제거한다. 이어서, 도 29에 도시된 돌출부 형성 공정에서, 도 28의 전극 패드(73)가 형성된 측의 지지판(55)의 부분을 에칭하여, 지지판(55)의 면(55A)을 에칭한다. 결과적으로, 금속층(41)의 면(41A)과 접촉하고 금속층(41)의 면(41A)의 외주부를 노출하는 돌출부(58)가 형성된다. 더욱 상세하게는, 제 1 금속으로 이루어진 지지판(55)을 선택적으로 에칭하지만 금속층(41, 42) 및 보호층(78)을 에칭하지 않는 에칭액을 이용하여, 지지판(55)을 에칭한다.

전극 패드(73)를 마스크로 이용하여 등방성 습식 에칭을 수행함으로써, 에칭액에 의해 도달된 지지판(55)에 대하여 사이드 에칭 및 언더컷을 이용하여, 돌출부(58)로부터 금속층(41)의 면(41A)의 외주부를 노출할 수 있다.

또한, 제 1 금속과는 상이한 금속으로 이루어지는 보호층(78)은 지지판(55)을 형성하는 제 1 금속으로 이루어지는 금속층(75)의 면(75A)에 형성되고, 돌출 부(58)는 지지판(55)을 에칭함으로써 지지판(55) 상에 형성된다. 이 때문에, 돌출부 형성 공정에서 금속층(75)이 에칭되는 것을 방지할 수 있다.

이어서, 도 30에 도시된 보호층 제거 공정에서, 과산화수소계(hydrogen-peroxide system) 에칭액 등의 도 29에서 보호층(78)만을 제거하는 에칭액을 이용하여 보호층(78)을 제거한다. 결과적으로, 금속층(75)의 면(75A)이 노출된다.

이어서, 도 31에 도시된 절연층 형성 공정에서, 전극 패드(73), 돌출부(58), 및 돌출부(58)가 형성된 측의 지지판(55)의 면(55A)을 덮도록, 개구부(38)를 가지는 절연층(21)을 형성한다.

따라서, 단자(12)가 설치되는 측의 전극 패드(73)의 면의 외주부, 즉 금속층(41)의 면(41A)은 절연층(21)으로 덮인다. 이 때문에, 전극 패드(73)의 측면과 절연층(21)의 측면 사이의 박리를 억제하고, 배선 기판(71)의 신뢰성을 향상시킬 수 있다.

예를 들면, 지지판(55)의 면(55A)에 설치된 절연층(21) 상에 설치된 절연층(21)의 두께는 65 ㎛ 내지 75 ㎛일 수 있다.

이 제 2 실시예의 반도체 장치(70)는 절연층 형성 공정 후에, 도 23 내지 도 25와 함께 상술한 공정과 동일한 공정을 수행함으로써 제조된다.

다른 제조 공정을 이용하여 이 제 2 실시예의 반도체 장치를 제조하는 방법에 따르면, 제 1 금속과는 상이한 금속으로 이루어진 보호층(78)은 지지판(55)을 형성하는 제 1 금속으로 이루어진 금속층의 면(75A)에 형성된다. 그 후, 지지판(55)을 에칭함으로써, 돌출부(58)를 지지판(55) 상에 형성한다. 그러므로, 돌출 부 형성 공정에서 금속층(75)이 에칭되는 것을 방지할 수 있다.

다른 제조 공정을 이용하여 이 제 2 실시예의 반도체 장치를 제조하는 방법에 따르면, 도 19 내지 도 25와 함께 상술한 제조 공정에 의해 얻어질 수 있는 효과와 동일한 효과를 얻을 수 있다.

도 32 내지 도 39는 제 2 실시예서 반도체 장치를 제조하는데 이용될 수 있는 본 발명의 제 2 실시예의 반도체 장치의 또 다른 제조 공정을 설명하는 단면도이다. 도 32 내지 도 39에서, 도 18에 도시된 제 2 실시예의 반도체 장치(70)의 해당 부품과 동일한 부품에는 동일한 참조 번호를 부여한다.

도 32 내지 도 39를 참조하여, 이 제 2 실시예의 반도체 장치(70)를 제조하는데 이용될 수 있는 이 또 다른 제조 공정을 설명한다. 우선, 도 3과 함께 상술한 제 1 실시예의 공정과 동일한 공정을 수행하여, 도 3에 도시된 구조체를 형성한다.

이어서, 도 32에 도시된 돌출부를 형성하기 위한 금속층 형성 공정에서, 돌출부를 형성하기 위한 금속층(81)은 개구부(56A)에 의해 노출된 부분의 지지판(55)의 면(55A)에 형성된다. 더욱 상세하게는, 금속층(81)은 지지판(55)을 급전층으로 이용하여 전해 도금함으로써 형성된다. 예를 들면, 전해 도금에 의해 형성된 Sn층, Sn-Pb층 등이 금속층(81)으로 이용될 수 있다. 예를 들면, 이 경우에 금속층(81)의 높이는 1 ㎛ 내지 30 ㎛일 수 있고, 바람직하게는 20 ㎛일 수 있다.

이어서, 도 33에 도시된 전극 패드 형성 공정에서, 도 4 및 도 26과 함께 상술한 공정과 동일한 공정에 의해 금속층(41), 금속층(42) 및 금속층(75)을 순차적 으로 적층함으로써, 전극 패드(73)를 형성할 수 있다.

이어서, 도 34에 도시된 공정에서, 도 33의 레지스트 층(56)을 제거한다. 이어서, 도 35에 도시된 돌출부 형성 공정에서, 금속층(81)을 에칭하여, 금속층(81)과 접촉하는 측에 형성된 금속층(41)의 면(41A)의 외주부를 노출하는 돌출부(81-1)를 형성한다. 더욱 상세하게는, 돌출부(81-1)는 과산화수소계 에칭액 등의 금속층(81)만을 제거하는 에칭액을 이용함으로써 형성된다.

전극 패드(73)를 마스크로 이용하여 등방성 습식 에칭을 수행함으로써, 에칭액에 의해 도달된 금속층(81)에 대하여 사이드 에칭 및 언더컷을 이용하여, 돌출부(81-1)로부터 금속층(41)의 면(41A)의 외주부를 노출시킬 수 있다.

예를 들면, 돌출부(81-1)는 원추대(truncated cone) 형상을 가질 수 있다. 이 경우에, 단면도에서, 원추대 형상을 가지는 돌출부(81-1)의 측면은 원추대 형상의 중심축에 대해 걸-윙 형상으로 내향 만곡될 수 있다.

금속층(81)만을 에칭하는 에칭액을 이용하여, 전극 패드(73)가 에칭되는 것을 방지할 수 있다.

예를 들면, 금속층(41)의 직경이 100 ㎛인 경우에, 금속층(41)과 접촉하는 부분의 돌출부(81-1)의 직경은 80 ㎛ 내지 90 ㎛일 수 있다.

이어서, 도 36에 도시된 절연층 형성 공정에서, 에칭된 돌출부(81-1), 전극부(73), 및 돌출부(81-1)가 형성된 측의 지지판(55)의 면(55A)을 덮도록, 개구부(38)를 가지는 절연층(21)을 형성할 수 있다.

이어서, 도 37에 도시된 공정에서, 도전 패턴 형성 공정을 포함하는 도 23과 함께 상술한 공정과 동일한 공정을 수행하여, 도전 패턴(27, 28), 비아(31), 패드(32), 및 솔더 레지스트 층(34)을 형성한다. 결과적으로, 배선 기판(71)에 대응하는 구조체가 지지판(55) 상에 형성된다.

이어서, 도 38에 도시된 지지판 제거 공정에서, 도 24와 함께 상술한 공정과 동일한 공정을 수행하여, 지지판(55)을 제거한다. 결과적으로, 돌출부(81-1)가 노출된다.

이어서, 도 39에 도시된 돌출부 제거 공정에서, 돌출부(81-1)를 제거하여, 돌출부(81-1)와 접촉하는 측의 전극 패드(73)의 면(금속층(41)의 면(41A))의 일부를 노출하고, 돌출부(81-1)의 형상에 대응하는 형상을 가지는 개구부(37)를 절연층(21)에 형성한다. 결과적으로, 배선 기판(71)이 제조된다.

돌출부 제거 공정 후에, 도 25와 함께 상술한 공정과 동일한 공정을 수행하여, 이 제 2 실시예의 반도체 장치(70)를 제조한다.

또 다른 제조 공정을 이용하는 이 제 2 실시예의 반도체 장치를 제조하는 방법에 따르면, 금속층(81)이 지지판(55)과 그 후에 형성된 전극 패드(73) 사이에 개재되도록, 금속층(81)을 형성한다. 전극 패드 형성 공정에 의해 전극 패드(73)를 형성한 후에, 금속층(81)을 에칭하여, 금속층(41)의 면(41A)의 외주부를 노출하는 돌출부(81-1)를 형성한다. 그 후, 돌출부(81-1), 전극 패드(73), 및 돌출부(81-1)가 형성된 측의 지지판(55)의 면(55A)을 덮도록, 절연층(21)을 형성한다. 이 때문에, 지지판(55)을 에칭하여 개구부(37)를 형성하는 경우에 비해, 형성되는 개구부(37)의 깊이에 불일치를 저감할 수 있다.

또한, 또 다른 제조 공정을 이용하는 이 제 실시예의 반도체 장치를 제조하는 방법에 따르면, 도 19 내지 도 25와 함께 상술한 제조 공정에 의해 얻어질 수 있는 효과와 동일한 효과를 얻을 수 있다.

(제 3 실시예)

도 40은 본 발명의 제 3 실시예의 반도체 장치를 도시하는 단면도이다. 도 40에서, 도 18에 도시된 제 2 실시예의 반도체 장치(70)의 해당 부품과 동일한 부품에는 동일한 참조 번호를 부여한다.

도 40에 도시된 바와 같이, 이 제 3 실시예의 반도체 장치(85)에는 제 2 실시예의 반도체 장치(70)의 배선 기판(71)을 대신하여 배선 기판(86)이 설치된다. 그 외는, 반도체 장치(85)의 구조는 반도체 장치(70)의 구조와 기본적으로 동일하다.

배선 기판(86)은 배선 기판(71)의 전극 패드(73)를 대신하여 전극 패드(88)를 가진다. 그 외는, 배선 기판(86)의 구조는 배선 기판(71)의 구조와 기본적으로 동일하다.

전극 패드(88)에서, (제 1 및 제 3)금속층(41, 75)의 외주 측면에 비해, 내측에 (제 2)금속층(42)의 외주 측면이 배치된다. 그 외는, 전극 패드(88)는 전극 패드(73)와 동일하게 형성된다.

금속층(42)의 외주 측면이 금속층(41, 75)의 외주 측면에 비해 내측에 배치되므로, 절연층(21)이 충전된 오목부(89)가 전극 패드(88)에 형성된다. 이 때문에, 전극 패드(88)의 위치는 오목부(89) 내의 절연층(21)에 의해 규제되어, 전극 패드(88)는 절연층(21)에 더 확실하게 매설된다.

또한, 절연층(21)과 전극 패드(88) 사이의 접촉 영역은 오목부(89)의 설치에 의해 증가되고, 절연층(21)과 전극 패드(88) 사이의 본딩을 향상시킬 수 있다.

예를 들면, 금속층(42)의 외주 측면으로부터 금속층(41, 75)의 외주 측면까지의 거리(B)는 5 ㎛ 내지 20 ㎛일 수 있다.

이 제 3 실시예의 와이어 기판(86)에 따르면, 금속층(42)의 외주 측면은 금속층(41, 75)의 외주 측면에 비해 내측에 배치되고, 절연층(21)이 충전된 오목부(89)가 전극 패드(88)에 형성된다. 이 때문에, 전극 패드(88)의 위치는 오목부(89) 내의 절연층(21)에 의해 규제되고, 전극 패드(88)는 절연층(21) 내에 더 확실하게 매설된다. 또한, 절연층(21)과 전극 패드(88) 사이의 접촉 영역은 오목부(89)의 설치에 의해 확장되므로, 절연층(21)과 전극 패드(88) 사이의 본딩을 향상시킬 수 있다.

도 41 내지 도 49는 본 발명의 제 3 실시예의 반도체 장치의 제조 공정을 설명하는 단면도이다. 도 41 내지 도 49에서, 도 40에 도시된 제 3 실시예의 반도체 장치(85)의 해당 부분과 동일한 부분에는 동일한 참조 번호를 부여한다.

도 41 내지 도 49를 참조하여, 이 제 3 실시예의 반도체 장치(85)를 제조하는 방법을 설명한다. 우선, 도 3과 함께 상술한 제 1 실시예의 공정과 동일한 공정을 수행하여, 도 3에 도시된 구조체를 형성한다.

이어서, 도 41에 도시된 돌출부를 형성하는 금속층 형성 공정에서, 금속층(42)과 동일한 금속으로 이루어진 돌출부를 형성하는 금속층(91)을 개구부(56A) 에 의해 노출된 부분의 지지판(55)의 면(55A)에 형성한다. 더욱 상세하게는, 지지판(55)을 급전층으로 이용하여 전해 도금함으로써, 금속층(91)을 형성한다. 예를 들면, 금속층(42)을 Ni층에 의해 형성하는 경우에, 금속층(91)을 Ni층에 의해 형성할 수 있다. 예를 들면, 금속층(91)의 두께는 1 ㎛ 내지 30 ㎛일 수 있고, 바람직하게는 20 ㎛일 수 있다.

이어서, 도 42에 도시된 공정에서, 도 33과 함께 상술한 제 2 실시예의 공정과 동일한 공정을 수행하여서, 금속층(91)의 면(91A)에 금속층(41), 금속층(91)과 동일한 금속 재료로 이루어진 금속층(42), 및 금속층(75)을 순차적으로 적층하여, 전극 패드(88)를 형성한다. 이 단계에서, 전극 패드(88)에는 오목부(89)가 아직 형성되어 있지 않다.

이어서, 도 43에 도시된 공정에서, 레지스트 층(56)을 제거한다. 이어서, 도 44에 도시된 돌출부 형성 공정에서, 금속층(91)만을 에칭하고 금속층(41), 금속층(75) 및 지지판(55)을 에칭하지 않는 에칭액을 이용하여, 금속층(91)을 에칭한다. 결과적으로, 금속층(41)의 면(41A)의 외주부를 노출하는 돌출부(91-1)를 형성한다.

전극 패드(88)를 마스크로 이용하는 등방성 습식 에칭을 수행함으로써, 에칭액이 도달되는 금속층(91)에 대해 사이드 에칭 및 언더컷을 이용하여, 돌출부(91-1)로부터 금속층(41)의 면(41A)의 외주부를 노출할 수 있다.

예를 들면, 돌출부(91-1)는 원추대 형상을 가질 수 있다. 이 경우에, 단면도에서, 원추대 형상을 가지는 돌출부(91-1)의 측면은 원추대 형상의 중심축에 대 해 걸-윙 형상으로 내향 만곡될 수 있다.

또한, 돌출부 형성 공정에서, 금속층(91)과 동일한 금속 재료로 이루어진 금속층(42)의 측벽이 에칭되므로, 오목부(89)가 형성된다. 그러므로, 전극 패드 형성 공정에 의해 오목부(89)를 가지는 전극 패드(88)가 형성된다.

따라서, 금속층(91)과 금속층(42)은 동일한 금속 재료로 이루어지므로, 단일 에칭 공정에 의해, 오목부(89) 및 금속층(41)의 면(41A)의 외주부를 노출하는 돌출부(91-1)를 동시에 형성할 수 있다. 그러므로, 배선 기판(86)의 제조 비용을 절감할 수 있다.

이어서, 도 45에 도시된 절연층 형성 공정에서, 돌출부(91-1), 전극 패드(88), 및 돌출부(91-1)가 형성된 측의 지지판(55)의 면(55A)을 덮도록, 절연층(21)을 형성한다. 또한, 금속층(75)의 면(75A)에 대향하는 부분의 절연층(21)에, 금속층(75)의 면(75A)을 노출하도록 개구부(38)를 형성한다.

따라서, 절연층(21)은 단자(12)가 설치된 측의 전극 패드(88)의 면(금속층(41)의 면(41A))의 외주부를 덮는다. 결과적으로, 전극 패드(88)의 측면과 절연층(21)의 측면 사이의 박리의 발생을 억제할 수 있고, 배선 기판(86)의 신뢰성을 향상시킬 수 있다.

또한, 예를 들면, 절연층(21)에 의해 덮인 금속층(41)의 면(41A)의 외주부의 폭은 0.1 ㎛ 내지 6 ㎛일 수 있고, 바람직하게는 1 ㎛ 내지 3 ㎛일 수 있다.

이어서, 도 46에 도시된 공정에서, 도전 패턴 형성 공정을 포함하는 도 23과 함께 상술한 제 2 실시예의 공정과 동일한 공정을 수행하여, 도전 패턴(27, 28), 비아(31), 패드(32), 및 솔더 레지스트 층(34)을 형성한다. 그러므로, 배선 기판(86)에 대응하는 구조체가 지지판(55) 상에 형성된다.

이어서, 도 47에 도시된 지지판 제거 공정에서, 도 24와 함께 설명한 제 2 실시예의 공정과 동일한 공정에 의해 도 46의 지지판(55)을 제거한다.

이어서, 도 48에 도시된 돌출부 제거 공정에서, 돌출부(91-1)만을 제거하는 에칭액을 이용하여, 도 47의 돌출부(91-1)를 제거한다.

이어서, 도 49에 도시된 공정에서, 도 25와 함께 상술한 제 2 실시예의 공정과 동일한 공정을 수행하여, 이 제 3 실시예의 반도체 장치(85)를 제조한다.

이 제 3 실시예의 배선 기판(86)을 제조하는 방법에 따르면, 금속층(91) 및 금속층(42)은 동일한 금속 재료로 이루어지므로, 단일 에칭 공정에 의해, 금속층(41)의 면(41A)의 외주부를 노출하는 오목부(89) 및 돌출부(91-1)를 동시에 형성할 수 있다. 그러므로, 배선 기판(86)의 제조 비용을 절감할 수 있다.

또한, 금속층(41)의 면(41A)의 외주부를 노출하고 전극 패드(88)에 오목부(89)를 형성한 후에, 절연층(21)에 의해 오목부(89)를 충전하도록, 돌출부(91-1), 전극 패드(88), 및 돌출부(91-1)가 형성된 측의 지지판(55)의 면(55A)을 덮도록, 절연층(21)을 형성한다. 결과적으로, 전극 패드(88)와 절연층(21) 사이의 본딩은 향상되고, 전극 패드(88)의 위치는 절연층(21) 내에 규제된다.

(제 4 실시예)

도 50은 본 발명의 제 4 실시예의 반도체 장치를 도시하는 단면도이다. 도 50에서, 도 2에 도시된 제 1 실시예의 반도체 장치(10)의 해당 부품과 동일한 부품 에는 동일한 참조 번호를 부여한다.

도 50에 도시된 바와 같이, 이 제 4 실시예의 반도체 장치(95)에는, 제 1 실시예의 반도체 장치(10)에 설치된 배선 기판(11)을 대신하여, 배선 기판(96)이 설치된다. 그 외는, 반도체 장치(95)의 구조는 반도체 장치(10)의 구조와 기본적으로 동일하다.

배선 기판(96)에는 배선 기판(11)에 설치된 전극 패드(25)를 대신하여, 단일 금속층에 의해 형성된 전극 패드(98)가 설치된다. 그 외는, 배선 기판(96)의 구조는 배선 기판(11)의 구조와 기본적으로 동일하다.

전극 패드(98)는 절연층(21) 내에 매설된다. 전극 패드(98)의 면(98A)의 일부는 개구부(38)에서 노출된다. 개구부(38)에 의해 노출된 전극 패드(98)의 부분은 도전 패턴(27)에 접속된다.

단자(12)가 형성된 측의 전극 패드(98)의 면(98B)의 중심부는 개구부(37)에서 노출된다. 전극 패드(98)의 면(98B)의 외주부는 절연층(21)에 의해 덮인다.

절연층(21)에 의해, 단자(12)가 형성된 측의 전극 패드(98)의 면(98B)의 외주부를 덮음으로써, 전극 패드(98)의 측면과 절연층(21)의 측면 사이의 박리의 발생을 억제할 수 있다. 그러므로, 배선 기판(96)의 신뢰성을 향상시킬 수 있다.

개구부(37)에 노출된 전극 패드(98)의 부분은 단자(12)를 통해 전자 부품(13)에 전기적으로 접속된다.

예를 들면, Cu를 전극 패드(98)로 이용할 수 있다. 이 경우에, 전극 패드(98)의 두께는 10 ㎛ 내지 20 ㎛일 수 있고, 더 바람직하게는 15 ㎛일 수 있다.

Cu를 전극 패드(98)로 이용하고, 도전 패턴(27)을 형성하는 금속 재료가 또한 Cu인 경우, 전극 패드(98)와 도전 패턴(27) 사이의 본딩을 향상시킬 수 있다. 결과적으로, 전극 패드(98)와 도전 패턴(27) 사이의 전기적인 접속의 신뢰성을 향상시킬 수 있다.

예를 들면, 배선 기판(96) 상에 전자 부품(13)을 실장하는데 전자 패드(98)를 이용하는 경우에, 전자 패드(98)의 직경은 50 ㎛ 내지 150 ㎛일 수 있다. 또한, 예를 들면 배선 기판(96) 상에 전자 부품(13)을 실장하는데 패드(32)를 이용하고 배선 기판(98)을 회로 기판(도시 생략)에 접속하는데 전극 패드(98)를 이용하는 경우, 전극 패드(98)의 직경은 200 ㎛ 내지 1000 ㎛일 수 있다.

이 제 4 실시예의 반도체 장치(95)에 따르면, 단자(12)가 형성된 측의 전극 패드(98)의 면(98B)의 외주부는 절연층(21)에 의해 덮인다. 이 때문에, 전극 패드(98)의 측면과 절연층(21)의 측면 사이의 박리의 발생을 억제할 수 있어, 배선 기판(96)의 신뢰성을 향상시킬 수 있다.

또한, Cu를 전극 패드(98)를 형성하는데 이용하고, 도전 패턴(27)을 형성하는 금속 재료가 또한 Cu인 경우에, 전극 패드(98)와 도전 패턴(27) 사이의 본딩을 향상시킬 수 있다. 결과적으로, 전극 패드(98)와 도전 패턴(27) 사이의 전기적인 접속의 신뢰성을 향상시킬 수 있다.

또한, 단일 금속층에 의해 전극 패드(98)를 형성함으로써, 배선 기판(96)의 비용을 절감할 수 있다.

도 51 내지 59는 본 발명의 제 4 실시예의 반도체 장치의 제조 공정을 설명 하는 단면도이다. 도 51 내지 59에서, 도 50에 도시된 제 4 실시예의 반도체 장치(95)의 해당 부품과 동일한 부품에는 동일한 참조 번호를 부여한다.

도 51 내지 도 59를 참조하여, 이 제 4 실시예의 반도체 장치(95)를 제조하는 방법을 설명한다. 우선, 도 3과 함께 상술한 제 1 실시예의 공정과 동일한 공정을 수행하여, 도 3에 도시된 구조체를 형성한다.

이어서, 도 51에 도시된 돌출부를 위한 금속층 형성 공정에서, 제 1 금속과 상이한 금속으로 이루어진 돌출부를 형성하는 금속층(101)을 개구부(56A)에 의해 노출된 위치의 지지판(55)의 면(55A)에 형성한다. 더욱 상세하게는, 예를 들면 지지판(55)을 급전층으로 이용하여 전해 도금함으로써, 금속층(101)을 형성한다. 예를 들면, 금속층(101)은 Ni층, Sn층, Sn-Pb층 등에 의해 형성될 수 있다. 이 경우에, 예를 들면 금속층(101)의 두께는 1 ㎛ 내지 30 ㎛일 수 있고, 20 ㎛인 것이 바람직하다.

이어서, 도 52에 도시된 전극 패드 형성 공정에서, 제 1 금속(예를 들면, Cu)으로 이루어진 전극 패드(98)를 금속층(101)의 면(101A)에 형성한다. 더욱 상세하게는, 예를 들면 전극 패드(98)를 형성하기 위해, 지지판(55)을 급전층으로 이용하여 전해 도금함으로써, Cu층을 형성할 수 있다.

이어서, 도 53에 도시된 공정에서, 레지스트 층(56)을 제거한다. 이어서, 도 54에 도시된 돌출부 형성 공정에서, 금속층(101)만을 에칭하는 에칭액을 이용하여 금속층(101)을 에칭하여, 금속층(101)과 접촉하는 측의 전극 패드(98)의 면(98B)의 외주부를 노출하는 돌출부(101-1)를 형성한다.

전극 패드(98)를 마스크로 이용하는 등방성 습식 에칭을 수행함으로써, 에칭액에 의해 도달되는 금속층(101)에 대하여 사이드 에칭 및 언더컷을 이용하여, 돌출부(101-1)로부터 금속층(98)의 면(98B)의 외주부를 노출시킬 수 있다.

예를 들면, 돌출부(101-1)는 원추대 형상을 가질 수 있다. 이 경우에, 단면도에서, 원추대 형상을 가지는 돌출부(101-1)의 측면은 원추대 형상의 중심축에 대해 걸-윙 형상으로 내향 만곡될 수 있다.

이어서, 도 55에 도시된 절연층 형성 공정에서, 돌출부 형성 공정 후에 돌출부(101-1), 전극 패드(98), 및 돌출부(101-1)가 형성된 측의 지지판(55)의 면(55A)을 덮도록, 개구부(38)를 가지는 절연층(21)을 형성한다.

단자(12)가 형성된 측의 전극 패드(98)의 면(98B)의 외주부를 덮도록 절연층(21)을 형성함으로써, 전극 패드(98)의 측면과 절연층(21)의 측면 사이의 박리의 발생을 억제할 수 있다. 결과적으로, 배선 기판(96)의 신뢰성을 향상시킬 수 있다.

예를 들면, 절연층(21)에 의해 덮인 부분의 전극 패드(98)의 면(98B)의 외주부의 폭은 0.1 ㎛ 내지 6 ㎛일 수 있고, 1 ㎛ 내지 3 ㎛인 것이 바람직하다.

이어서, 도 56에 도시된 공정에서, 도 46과 함께 상술한 제 3 실시예의 공정과 동일한 공정을 수행하여, 도전 패턴(27, 28), 비아(31), 패드(32), 및 솔더 레지스트 층(34)을 형성한다. 결과적으로, 배선 기판(96)에 대응하는 구조체가 지지판(55) 상에 형성된다.

이어서, 도 57에 도시된 지지판 제거 공정에서, 도 47과 함께 상술한 제 3 실시예의 공정과 동일한 공정에 의해, 지지판(55)을 제거한다.

이어서, 도 58에 도시된 돌출부 제거 공정에서, 돌출부(101-1)만을 에칭하는 에칭액을 이용하여 돌출부(101-1)를 제거한다. 그러므로, 돌출부(101-1)와 접촉하는 측의 전극 패드(98)의 면(98B)의 일부가 노출됨으로써, 에칭된 돌출부(101-1)의 형상에 대응하는 형상을 가지는 개구부(37)를 형성한다. 결과적으로, 제 4 실시예의 배선 기판(96)이 제조된다.

이 제 4 실시예의 배선 기판(96)을 제조하는 방법에 따르면, 단자(12)가 형성된 측의 전극 패드(98)의 면(98B)의 외주부를 덮도록, 절연층(21)을 형성한다. 이 때문에, 전극 패드(98)의 측면과 절연층(21)의 측면 사이의 박리를 억제할 수 있어, 배선 기판(96)의 신뢰성을 향상시킬 수 있다.

또한, 전극 패드 형성 공정에서 단일 금속층만을 형성하여 전극 패드(98)를 형성함으로써, 배선 기판(96)의 제조 비용을 절감할 수 있다.

도 60은 다른 배선 기판의 예를 도시하는 단면도이다. 도 60에서, 도 50에 도시된 제 4 실시예의 배선 기판(96)과 동일한 부품에는 동일한 참조 번호를 부여한다.

제 4 실시예의 반도체 장치(95)에 설치된 배선 기판(96)을 대신하여, 도 60에 도시된 배선 기판(110)을 이용할 수 있다.

도 60에 도시된 바와 같이, 배선 기판(110)은 전극 패드(98)의 면(98B)에 설치된 유기 솔더 보존(Organic Solderbility Preservative)(OSP)층(111)을 가진다. 그 외는, 배선 기판(110)의 구조는 배선 기판(96)의 구조와 기본적으로 동일하다.

상술한 구조를 가지는 배선 기판(110)을 반도체 장치(95)에 이용하는 경우, 단자(12)로 솔더를 사용할 경우, 전극 패드(98)와 솔더 사이에 충분한 젖음성(wetting)을 확보할 수 있다. 또한, 전극 패드(98)의 면(98B)의 산화를 방지할 수 있다.

전극 패드(98)의 면(98B)을 OSP에 의해 처리하여, 도 58에 도시된 돌출부 제거 공정과 도 59에 도시된 공정 사이에 수행되는 OSP층 형성 공정에서 개구부(37)에 의해 노출된 부분의 전극 패드(98)의 면(98B)에 OSP층(111)을 형성한다. 그 외는, 제 4 실시예의 배선 기판(96)을 제조하는데 이용되는 공정과 동일한 공정에 의해, 배선 기판(110)을 제조할 수 있다.

도 61은 본 발명의 제 2 실시예의 변형의 반도체 장치를 도시하는 단면도이다. 이 제 2 실시예의 변형의 반도체 장치에서, 전자 부품(13)은 패드(32)에 접속된다. 그 외는, 반도체 장치(120)의 구조는 제 2 실시예의 반도체 장치(70)의 구조와 기본적으로 동일하다. 반도체 장치(120)에 따르면, 반도체 장치(70)에서 얻을 수 있는 효과와 동일한 효과를 얻을 수 있다.

도 62는 본 발명의 제 3 실시예의 변형의 반도체 장치를 도시하는 단면도이다. 이 제 3 실시예의 변형의 반도체 장치(130)에서, 전자 부품(13)은 패드(32)에 접속된다. 그 외는, 반도체 장치(130)의 구조는 제 3 실시예의 반도체 장치(85)의 구조와 기본적으로 동일하다. 반도체 장치(130)에 따르면, 반도체 장치(85)에서 얻을 수 있는 효과와 동일한 효과를 얻을 수 있다.

도 63은 본 발명의 제 4 실시예의 변형의 반도체 장치를 도시하는 단면도이 다. 이 제 4 실시예의 변형의 반도체 장치(140)에서, 전자 부품(13)은 패드(32)에 접속된다. 그 외는, 반도체 장치(140)의 구조는 제 4 실시예의 반도체 장치(95)의 구조와 기본적으로 동일하다. 반도체 장치(140)에 따르면, 반도체 장치(95)에서 얻을 수 있는 효과와 동일한 효과를 얻을 수 있다.

본 발명의 실시예와 변형 각각에서, 돌출부를 형성하는 금속층은 제 1 금속과는 상이한 도전성을 가질 수 있다.

또한, 본 발명의 실시예와 변형 각각에서, 언더필 수지가 전자 부품과 배선 기판 사이에 설치될 수 있다.

본 발명의 실시예와 변형은 전극 패드를 가지는 배선 기판, 전극 패드에 접속된 도전 패턴, 전극 패드 및 도전 패턴이 매설된 절연층, 및 이 배선 기판을 제조하는 방법에 적용 가능하다.

또한, 본 발명은 이들 실시예에 한정되는 것은 아니고, 본 발명의 사상에서 일탈하지 않고 다양한 변형 및 변경이 이루어질 수 있다.

도 1은 종래의 배선 기판의 일례를 도시하는 단면도.

도 2는 본 발명의 제 1 실시예에서의 반도체 장치를 도시하는 단면도.

도 3 내지 도 12는 본 발명의 제 1 실시예에서의 반도체 장치의 제조 공정을 설명하는 단면도.

도 13 내지 도 16은 본 발명의 제 1 실시예에서의 반도체 장치의 다른 제조 공정을 설명하는 단면도.

도 17은 본 발명의 제 1 실시예의 반도체 장치의 변형을 도시하는 단면도.

도 18은 본 발명의 제 2 실시예에서의 반도체 장치를 도시하는 단면도.

도 19 내지 도 25는 본 발명의 제 2 실시예에서의 반도체 장치의 제조 공정을 설명하는 단면도.

도 26 내지 도 31은 본 발명의 제 2 실시예에서의 반도체 장치의 다른 제조 공정을 설명하는 단면도.

도 32 내지 도 39는 본 발명의 제 2 실시예에서의 반도체 장치의 또 다른 제조 공정을 설명하는 단면도.

도 40은 본 발명의 제 3 실시예에서의 반도체 장치를 도시하는 단면도.

도 41 내지 도 49는 본 발명의 제 3 실시예에서의 반도체 장치의 제조 공정을 설명하는 단면도.

도 50은 본 발명의 제 4 실시예에서의 반도체 장치를 도시하는 단면도.

도 51 내지 도 59는 본 발명의 제 4 실시예에서의 반도체 장치의 제조 공정 을 설명하는 단면도.

도 60은 다른 배선 기판의 일례를 도시하는 단면도.

도 61은 본 발명의 제 2 실시예의 반도체 장치의 변형을 도시하는 단면도.

도 62는 본 발명의 제 3 실시예의 반도체 장치의 변형을 도시하는 단면도.

도 63은 본 발명의 제 4 실시예의 반도체 장치의 변형을 도시하는 단면도.

* 도면의 주요 부분에 대한 부호의 설명 *

10 : 반도체 장치 11 : 배선 기판

13 : 전자 부품 21, 22, 23 : 절연층

25 : 전극 패드 27, 28 : 도전 패턴

31 : 비아 32 : 외부 접속용 패드

34 : 솔더 레지스트 층

Claims (17)

- 제 1 면 및 상기 제 1 면과는 반대측에 위치되는 제 2 면을 가지는 전극 패드;상기 전극 패드의 제 1 면에 접속되는 도전 패턴; 및상기 전극 패드 및 상기 도전 패턴이 매설되는 절연층을 포함하고,상기 절연층은 상기 전극 패드의 상기 제 2 면의 외주부를 덮는 배선 기판.

- 제 1 항에 있어서,상기 절연층은 상기 제 2 면의 일부를 노출하는 개구부를 가지고,상기 개구부는 상기 전극 패드로부터 이간(離間)하는 방향으로 폭이 넓어지는 형상을 가지는 배선 기판.

- 제 1 항에 있어서,상기 전극 패드는 상기 개구부에서 노출되고 상기 도전 패턴을 형성하는 금속과는 상이한 금속으로 이루어진 제 1 금속층, 상기 제 1 금속층 상에 설치되고 상기 도전 패턴을 형성하는 상기 금속과는 상이한 금속으로 이루어진 제 2 금속층, 및 상기 제 2 금속층 상에 설치되고 상기 도전 패턴을 형성하는 상기 금속으로 이루어진 제 3 금속층을 포함하고;상기 제 3 금속층은 상기 도전 패턴에 접속되는 배선 기판.

- 제 3 항에 있어서,상기 제 2 금속층의 외주 측면은 상기 제 1 금속층 및 상기 제 3 금속층 각각의 외주 측면에 비해 내측에 배치되는 배선 기판.

- 제 1 항에 있어서,상기 전극 패드는 상기 도전 패턴을 형성하는 금속으로 이루어지고,상기 개구부에서 노출된 부분에서 상기 전극 패드의 상기 제 2 면을 덮는 유기 솔더 보존(Organic Solderbility Preservative)(OSP)층을 더 포함하는 배선 기판.

- 제 1 금속으로 이루어지는 지지판 상에 전극 패드를 형성하는 전극 패드 형성 단계;상기 전극 패드와 대향하는 부분의 상기 지지판 상에, 상기 지지판을 에칭하여, 상기 지지판과 대향하는 측의 상기 전극 패드의 면을 노출하고 상기 전극 패드에 접촉하는 돌출부를 형성하는 돌출부 형성 단계;상기 전극 패드, 상기 돌출부, 및 상기 돌출부가 형성된 상기 지지판의 면을 덮는 절연층을 형성하는 절연층 형성 단계;상기 절연층에, 상기 전극 패드에 접속되는 도전 패턴을 형성하는 도전 패턴 형성 단계; 및상기 도전 패턴 형성 단계 후에, 에칭에 의해 상기 돌출부가 형성된 상기 지지판을 제거함으로써, 상기 지지판과 대향하는 측의 상기 전극 패드의 면의 일부를 노출하고 상기 절연층에 상기 돌출부의 형상에 대응하는 형상을 가지는 개구부를 형성하는 지지판 제거 단계를 포함하는 배선 기판의 제조 방법.

- 제 6 항에 있어서,상기 돌출부 형성 단계는 상기 돌출부가 상기 전극 패드로부터 상기 지지판을 향해 폭이 넓어지는 형상으로 되도록 상기 지지판을 에칭하는 배선 기판의 제조 방법.

- 제 6 항에 있어서,상기 전극 패드 형성 단계는,상기 제 1 금속과는 상이한 금속으로 이루어지는 제 1 금속층을 형성하는 제 1 금속층 형성 단계; 및상기 제 1 금속층 상에, 상기 제 1 금속과는 상이한 금속으로 이루어지는 제 2 금속층을 형성하는 제 2 금속층 형성 단계를 포함하고,상기 돌출부 형성 단계는 상기 전극 패드를 마스크로 이용하고 상기 제 1 금속을 선택적으로 에칭하는 에칭액을 이용하여 상기 지지판을 에칭하는 배선 기판의 제조 방법.

- 제 8 항에 있어서,상기 전극 패드 형성 단계는,상기 제 2 금속층 형성 단계 후에, 상기 제 2 금속층의 면에, 상기 제 1 금속으로 이루어지는 제 3 금속층을 형성하는 제 3 금속층 형성 단계를 더 포함하고,상기 제 3 금속층 형성 단계는 상기 돌출부 형성 단계를 수행한 후에 상기 제 2 금속층의 면을 덮기에 충분한 두께로 상기 제 3 금속층을 형성하는 배선 기판의 제조 방법.

- 제 8 항에 있어서,상기 전극 패드 형성 단계는,상기 제 2 금속층 형성 단계 후에, 상기 제 2 금속층의 면에, 상기 제 1 금속으로 이루어지는 제 3 금속층을 형성하는 제 3 금속층 형성 단계; 및상기 제 3 금속층 상에, 상기 돌출부 형성 단계에서 상기 지지판을 에칭할 때, 상기 제 3 금속층의 에칭을 방지하는 보호층을 형성하는 보호층 형성 단계를 더 포함하고,상기 돌출부 형성 단계와 상기 절연층 형성 단계 사이에서, 상기 보호층을 제거하는 보호층 제거 단계를 더 포함하는 배선 기판의 제조 방법.

- 제 6 항에 있어서,상기 전극 패드 형성 단계에 앞서, 상기 전극 패드가 형성되는 영역에 대응 하는 상기 지지판의 부분에 상기 제 1 금속으로 이루어지는 높이 조정층을 형성하는 높이 조정층 형성 단계를 더 포함하고,상기 지지판 제거 단계는 상기 제 1 금속을 선택적으로 에칭하는 상기 에칭액을 이용하여 상기 지지판과 함께 상기 높이 조정층을 제거하는 배선 기판의 제조 방법.

- 제 1 금속으로 이루어지는 지지판 상에 금속층을 형성하는 금속층 형성 단계;상기 금속층 상에 전극 패드를 형성하는 전극 패드 형성 단계;상기 금속층을 에칭하고, 상기 돌출부와 접촉하는 상기 전극 패드의 면의 외주부를 노출함으로써, 돌출부를 형성하는 돌출부 형성 단계;상기 돌출부 형성 단계 후에, 상기 돌출부, 상기 전극 패드, 및 상기 돌출부가 형성된 상기 지지판의 면을 덮도록 절연층을 형성하는 절연층 형성 단계;상기 절연층 상에, 상기 전극 패드에 접속된 도전 패턴을 형성하는 도전 패턴 형성 단계;상기 도전 패턴 형성 단계 후에, 에칭에 의해 상기 지지판을 제거하는 지지판 제거 단계; 및상기 도전 패턴 형성 단계 후에, 상기 돌출부를 제거함으로써, 상기 절연층에, 상기 돌출부와 접촉하는 상기 전극 패드의 면의 일부를 노출하고 상기 돌출부의 형상에 대응하는 형상을 가지는 개구부를 형성하는 돌출부 제거 단계를 포함하 는 배선 기판의 제조 방법.

- 제 12 항에 있어서,상기 금속층은 상기 제 1 금속과는 상이한 도전성을 가지는 재료로 이루어지는 배선 기판의 제조 방법.

- 제 12 항에 있어서,상기 전극 패드는 상기 제 1 금속으로 이루어지는 배선 기판의 제조 방법.

- 제 12 항에 있어서,상기 전극 패드 형성 단계는 상기 금속층 상에, 상기 제 1 금속과는 상이한 금속으로 이루어지는 제 1 금속층, 상기 제 1 금속과는 상이한 금속으로 이루어지는 제 2 금속층, 및 상기 제 1 금속으로 이루어지는 제 3 금속층을 순차적으로 적층함으로써, 상기 전극 패드를 형성하는 배선 기판의 제조 방법.

- 제 15 항에 있어서,상기 전극 패드 형성 단계는 상기 금속층을 형성하는 금속을 이용하여 상기 제 2 금속층을 형성하는 배선 기판의 제조 방법.

- 제 12 항에 있어서,유기 솔더 보존(OSP) 공정을 수행함으로써, 상기 절연층으로부터 노출된 상기 전극 패드의 부분에 유기 솔더 보존(OSP) 층을 형성하는 단계를 더 포함하는 배선 기판의 제조 방법.

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008259016A JP5101451B2 (ja) | 2008-10-03 | 2008-10-03 | 配線基板及びその製造方法 |

| JPJP-P-2008-259016 | 2008-10-03 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| KR20100038148A true KR20100038148A (ko) | 2010-04-13 |

Family

ID=42074889

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020090092778A KR20100038148A (ko) | 2008-10-03 | 2009-09-30 | 배선 기판 및 그 제조 방법 |

Country Status (3)

| Country | Link |

|---|---|

| US (3) | US20100084163A1 (ko) |

| JP (1) | JP5101451B2 (ko) |

| KR (1) | KR20100038148A (ko) |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20180019226A (ko) * | 2015-08-18 | 2018-02-23 | 미쓰비시덴키 가부시키가이샤 | 반도체 장치 |

| KR20190136240A (ko) * | 2018-05-30 | 2019-12-10 | 삼성전기주식회사 | 패키지 기판 및 그 제조방법 |

Families Citing this family (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN102237287A (zh) * | 2010-04-27 | 2011-11-09 | 中国砂轮企业股份有限公司 | 基板的制作方法及其结构 |

| JP5711472B2 (ja) * | 2010-06-09 | 2015-04-30 | 新光電気工業株式会社 | 配線基板及びその製造方法並びに半導体装置 |

| US9502336B2 (en) * | 2013-03-13 | 2016-11-22 | Intel Corporation | Coreless substrate with passive device pads |

| KR20140134479A (ko) * | 2013-05-14 | 2014-11-24 | 삼성전기주식회사 | 인쇄회로기판 |

| JP2015195305A (ja) * | 2014-03-31 | 2015-11-05 | イビデン株式会社 | 導体ポストを有するプリント配線板の製造方法ならびに導体ポストを有するプリント配線板 |

| US9686862B2 (en) * | 2014-09-23 | 2017-06-20 | Finisar Corporation | Capacitors for multilayer printed circuit boards |

| TWI554174B (zh) * | 2014-11-04 | 2016-10-11 | 上海兆芯集成電路有限公司 | 線路基板和半導體封裝結構 |

| WO2017073622A1 (ja) * | 2015-10-28 | 2017-05-04 | 京セラ株式会社 | センサ基板および検出モジュール |

| US10249561B2 (en) * | 2016-04-28 | 2019-04-02 | Ibiden Co., Ltd. | Printed wiring board having embedded pads and method for manufacturing the same |

| JP6594264B2 (ja) | 2016-06-07 | 2019-10-23 | 新光電気工業株式会社 | 配線基板及び半導体装置、並びにそれらの製造方法 |

| TWI712344B (zh) * | 2017-08-18 | 2020-12-01 | 景碩科技股份有限公司 | 可做電性測試的多層電路板及其製法 |

| US11257745B2 (en) * | 2017-09-29 | 2022-02-22 | Intel Corporation | Electroless metal-defined thin pad first level interconnects for lithographically defined vias |

| US10950531B2 (en) | 2019-05-30 | 2021-03-16 | Advanced Semiconductor Engineering, Inc. | Semiconductor device package and method of manufacturing the same |

Family Cites Families (23)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CA2059020C (en) * | 1991-01-09 | 1998-08-18 | Kohji Kimbara | Polyimide multilayer wiring board and method of producing same |

| US6281446B1 (en) * | 1998-02-16 | 2001-08-28 | Matsushita Electric Industrial Co., Ltd. | Multi-layered circuit board and method of manufacturing the same |

| JP3635219B2 (ja) * | 1999-03-11 | 2005-04-06 | 新光電気工業株式会社 | 半導体装置用多層基板及びその製造方法 |

| JP2000357873A (ja) * | 1999-06-17 | 2000-12-26 | Hitachi Ltd | 多層配線基板及びその製造方法 |

| JP3916348B2 (ja) * | 1999-09-20 | 2007-05-16 | 松下電器産業株式会社 | 半導体装置及びその製造方法 |

| JP4819304B2 (ja) | 2000-10-18 | 2011-11-24 | 日本電気株式会社 | 半導体パッケージ |

| JP4087080B2 (ja) * | 2001-05-17 | 2008-05-14 | 株式会社日立製作所 | 配線基板の製造方法およびマルチップモジュールの製造方法 |

| JP3840921B2 (ja) * | 2001-06-13 | 2006-11-01 | 株式会社デンソー | プリント基板のおよびその製造方法 |

| US6861757B2 (en) * | 2001-09-03 | 2005-03-01 | Nec Corporation | Interconnecting substrate for carrying semiconductor device, method of producing thereof and package of semiconductor device |

| JP3664720B2 (ja) | 2001-10-31 | 2005-06-29 | 新光電気工業株式会社 | 半導体装置用多層回路基板の製造方法 |

| JP3891838B2 (ja) * | 2001-12-26 | 2007-03-14 | 株式会社ルネサステクノロジ | 半導体装置およびその製造方法 |

| JP2003209366A (ja) * | 2002-01-15 | 2003-07-25 | Sony Corp | フレキシブル多層配線基板およびその製造方法 |

| JP3666591B2 (ja) | 2002-02-01 | 2005-06-29 | 株式会社トッパンNecサーキットソリューションズ | 半導体チップ搭載用基板の製造方法 |

| JP4445777B2 (ja) | 2004-02-27 | 2010-04-07 | 日本特殊陶業株式会社 | 配線基板、及び配線基板の製造方法 |

| US7626829B2 (en) * | 2004-10-27 | 2009-12-01 | Ibiden Co., Ltd. | Multilayer printed wiring board and manufacturing method of the multilayer printed wiring board |

| JP4819471B2 (ja) * | 2005-10-12 | 2011-11-24 | 日本電気株式会社 | 配線基板及び配線基板を用いた半導体装置並びにその製造方法 |

| KR100704919B1 (ko) * | 2005-10-14 | 2007-04-09 | 삼성전기주식회사 | 코어층이 없는 기판 및 그 제조 방법 |

| JP4334005B2 (ja) * | 2005-12-07 | 2009-09-16 | 新光電気工業株式会社 | 配線基板の製造方法及び電子部品実装構造体の製造方法 |

| JP2008124107A (ja) * | 2006-11-09 | 2008-05-29 | Fujitsu Ltd | 配線基板、半導体部品及び配線基板の製造方法 |

| TWI331388B (en) * | 2007-01-25 | 2010-10-01 | Advanced Semiconductor Eng | Package substrate, method of fabricating the same and chip package |

| JP4800253B2 (ja) * | 2007-04-04 | 2011-10-26 | 新光電気工業株式会社 | 配線基板の製造方法 |

| US8502398B2 (en) * | 2007-10-05 | 2013-08-06 | Shinko Electric Industries Co., Ltd. | Wiring board, semiconductor apparatus and method of manufacturing them |

| JP5306789B2 (ja) * | 2008-12-03 | 2013-10-02 | 日本特殊陶業株式会社 | 多層配線基板及びその製造方法 |

-

2008

- 2008-10-03 JP JP2008259016A patent/JP5101451B2/ja active Active

-

2009

- 2009-09-25 US US12/566,764 patent/US20100084163A1/en not_active Abandoned

- 2009-09-30 KR KR1020090092778A patent/KR20100038148A/ko not_active Application Discontinuation

-

2013

- 2013-01-16 US US13/742,681 patent/US9089041B2/en active Active

-

2015

- 2015-06-17 US US14/741,545 patent/US9345143B2/en active Active

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20180019226A (ko) * | 2015-08-18 | 2018-02-23 | 미쓰비시덴키 가부시키가이샤 | 반도체 장치 |

| KR20190136240A (ko) * | 2018-05-30 | 2019-12-10 | 삼성전기주식회사 | 패키지 기판 및 그 제조방법 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP2010092943A (ja) | 2010-04-22 |

| JP5101451B2 (ja) | 2012-12-19 |

| US20100084163A1 (en) | 2010-04-08 |

| US9345143B2 (en) | 2016-05-17 |

| US9089041B2 (en) | 2015-07-21 |

| US20130134127A1 (en) | 2013-05-30 |

| US20150289380A1 (en) | 2015-10-08 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR20100038148A (ko) | 배선 기판 및 그 제조 방법 | |

| US9247644B2 (en) | Wiring board and method for manufacturing the same | |

| US9515018B2 (en) | Wiring substrate and method for manufacturing wiring substrate | |

| KR101344800B1 (ko) | 배선 기판 및 반도체 장치 | |

| JP5607086B2 (ja) | 半導体パッケージの製造方法 | |

| US20080245549A1 (en) | Wiring board and method of manufacturing the same | |

| KR20080088403A (ko) | 배선 기판의 제조 방법, 반도체 장치의 제조 방법 및 배선기판 | |

| JP4980295B2 (ja) | 配線基板の製造方法、及び半導体装置の製造方法 | |

| US9247654B2 (en) | Carrier substrate and manufacturing method thereof | |

| US7698813B2 (en) | Method for fabricating conductive blind via of circuit substrate | |

| KR20170009128A (ko) | 회로 기판 및 그 제조 방법 | |

| US8322596B2 (en) | Wiring substrate manufacturing method | |

| KR100803960B1 (ko) | 패키지 온 패키지 기판 및 그 제조방법 | |

| KR102141102B1 (ko) | 반도체 패키지 기판 제조방법 및 이를 이용하여 제조된 반도체 패키지 기판 | |

| KR101158213B1 (ko) | 전자부품 내장형 인쇄회로기판 및 이의 제조 방법 | |

| US11749596B2 (en) | Wiring substrate | |

| KR102535353B1 (ko) | 반도체 패키지 기판, 이의 제조방법, 반도체 패키지 및 이의 제조방법 | |

| US20220285251A1 (en) | Semiconductor package substrate and method of manufacturing the same, and semiconductor package and method of manufacturing the same | |

| KR100694668B1 (ko) | 도금 인입선 없는 패키지 기판 제조방법 | |

| KR100749141B1 (ko) | 패키지 온 패키지 기판 및 그 제조방법 | |

| TW201812929A (zh) | 封裝基板及其製作方法、封裝結構 | |

| JP2007324232A (ja) | Bga型多層配線板及びbga型半導体パッケージ | |

| KR101617023B1 (ko) | 금속 포스트를 구비하는 인쇄회로기판 및 이의 제조 방법 | |

| JP5468572B2 (ja) | 配線基板 | |

| KR20110081628A (ko) | 기판의 제조 방법 및 이를 이용한 기판 및 반도체 패키지 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| WITN | Application deemed withdrawn, e.g. because no request for examination was filed or no examination fee was paid |