KR102047553B1 - 프로그래머블 lsi - Google Patents

프로그래머블 lsi Download PDFInfo

- Publication number

- KR102047553B1 KR102047553B1 KR1020130045208A KR20130045208A KR102047553B1 KR 102047553 B1 KR102047553 B1 KR 102047553B1 KR 1020130045208 A KR1020130045208 A KR 1020130045208A KR 20130045208 A KR20130045208 A KR 20130045208A KR 102047553 B1 KR102047553 B1 KR 102047553B1

- Authority

- KR

- South Korea

- Prior art keywords

- source

- drain

- transistor

- electrically connected

- configuration data

- Prior art date

Links

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K19/00—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits

- H03K19/02—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits using specified components

- H03K19/173—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits using specified components using elementary logic circuits as components

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K19/00—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits

- H03K19/0008—Arrangements for reducing power consumption

- H03K19/0013—Arrangements for reducing power consumption in field effect transistor circuits

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K19/00—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits

- H03K19/02—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits using specified components

- H03K19/173—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits using specified components using elementary logic circuits as components

- H03K19/177—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits using specified components using elementary logic circuits as components arranged in matrix form

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K19/00—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits

- H03K19/02—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits using specified components

- H03K19/173—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits using specified components using elementary logic circuits as components

- H03K19/177—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits using specified components using elementary logic circuits as components arranged in matrix form

- H03K19/1778—Structural details for adapting physical parameters

- H03K19/17784—Structural details for adapting physical parameters for supply voltage

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K19/00—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits

- H03K19/02—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits using specified components

- H03K19/173—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits using specified components using elementary logic circuits as components

- H03K19/177—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits using specified components using elementary logic circuits as components arranged in matrix form

- H03K19/1778—Structural details for adapting physical parameters

- H03K19/17792—Structural details for adapting physical parameters for operating speed

Abstract

본 발명은, 프로그래머블 LSI에서의 동작 지연의 억제 및 소비 전력의 저감의 양립을 도모한다.

컴파일러가 프로그래머블 LSI에서 필요하게 될 컨피규레이션 데이터와, 그 데이터가 프로그래머블 LSI에서 사용되는 타이밍(컨피규레이션 메모리에 있어서 보유되게 되는 타이밍) 및 그 데이터를 사용하기 전에 프로그래머블 LSI 내에 저장하는 타이밍을 나타내는 타임 스케줄을 소스 코드로부터 생성한다. 그리고, 상기 타임 스케줄에 의거하여 외부로부터 프로그래머블 LSI로의 새로운 컨피규레이션 데이터의 공급(새로운 컨피규레이션 데이터의 저장)과, 프로그래머블 LSI 내에서의 컨피규레이션 메모리의 데이터의 재기록(회로의 재구성)을 독립적으로 또 병행적으로 행한다.

컴파일러가 프로그래머블 LSI에서 필요하게 될 컨피규레이션 데이터와, 그 데이터가 프로그래머블 LSI에서 사용되는 타이밍(컨피규레이션 메모리에 있어서 보유되게 되는 타이밍) 및 그 데이터를 사용하기 전에 프로그래머블 LSI 내에 저장하는 타이밍을 나타내는 타임 스케줄을 소스 코드로부터 생성한다. 그리고, 상기 타임 스케줄에 의거하여 외부로부터 프로그래머블 LSI로의 새로운 컨피규레이션 데이터의 공급(새로운 컨피규레이션 데이터의 저장)과, 프로그래머블 LSI 내에서의 컨피규레이션 메모리의 데이터의 재기록(회로의 재구성)을 독립적으로 또 병행적으로 행한다.

Description

본 발명은 프로그래머블(programmable) LSI에 관한 것이다. 또한, 상기 프로그래머블 LSI를 갖는 반도체 장치에 관한 것이다. 또한, 본 명세서에 있어서 반도체 장치란, 반도체 특성을 이용함으로써 기능할 수 있는 장치 전반을 가리킨다. 예를 들어, 전기 광학 장치, 반도체 회로, 및 전자 기기는 반도체 장치이다.

회로의 재구성(reconfigurable)을 행할 수 있는 프로그래머블 LSI는, 종래의 ASIC(Application Specific Integrated Circuit)나 게이트 어레이 등과 비하여, 개발 기간의 단축이나 설계 사양의 변경에 대한 유연성 등의 이점이 있고, 반도체 장치로의 이용이 진행되고 있다.

구체적으로 기재하면, 프로그래머블 LSI에서는, 회로 구성을 설정하기 위한 데이터(컨피규레이션(configuration) 데이터)를 보유하는 메모리(컨피규레이션 메모리)가 제공되어 있다. 그리고, 상기 메모리에 보유되는 데이터에 기초하여 회로의 구성이 결정된다. 그래서, 컨피규레이션 메모리에 보유되는 컨피규레이션 데이터를 재기록함으로써 회로의 재구성을 행할 수 있게 된다. 이와 같이 회로의 재구성을 행하는 방법은 2개로 대별된다.

첫 번째 방법은, 프로그래머블 LSI의 동작이 정지되어 있는 상태에 있어서 회로를 재구성하는 방법(정적(靜的) 재구성)이다. 예를 들어, 상기 상태에 있어서 외부로부터 입력되는 컨피규레이션 데이터에 의하여 컨피규레이션 메모리의 데이터를 재기록함으로써 회로의 재구성을 행할 수 있다.

다만, 정적 재구성에서는, 프로그래머블 LSI의 동작 지연이 필연적으로 발생하게 된다. 또한, 외부로부터 입력되는 컨피규레이션 데이터에 의하여 컨피규레이션 메모리의 데이터를 재기록하는 경우, 프로그래머블 LSI의 동작을 계속시키는 것은 어렵다. 이것은, 프로그래머블 LSI에 대하여 외부로부터 데이터를 공급하는 버스의 폭을 충분히 넓게 하는 것이 설계상 어렵다(컨피규레이션 메모리의 데이터의 재기록에 필요한 시간을 충분히 짧게 하는 것이 어렵다)는 것에 기인한다.

두 번째 방법은, 프로그래머블 LSI의 동작이 계속되는(동작이 정지되는 기간이 매우 짧은) 상태에서 회로를 재구성하는 방법(동적(動的) 재구성)이다. 예를 들어, 특허문헌 1에 기재된 프로그래머블 LSI에서는, 프로그래머블 LSI 내부에 컨피규레이션 메모리와는 별도로 DRAM(Dynamic Random Access Memory)을 제공함으로써 동적 재구성을 가능하게 한다. 구체적으로는, 상기 DRAM에 미리 저장되어 있는 복수의 컨피규레이션 데이터 중 하나를 컨피규레이션 메모리에 보유되어 있는 데이터와 치환(컨피규레이션 데이터를 재기록)함으로써 회로의 재구성을 행한다.

특허문헌 1에 기재되는 프로그래머블 LSI에서는, 프로그래머블 LSI의 동작 지연의 억제를 도모할 수 있다. 다만, 상기 프로그래머블 LSI에서는, 필연적으로 소비 전력의 증가가 수반된다. 이것은, 복수의 컨피규레이션 데이터를 미리 DRAM에 저장할 필요가 있다는 것, 및 그들을 보유하기 위하여 정기적으로 리프레쉬 동작을 행할 필요가 있다는 것에 기인한다. 또한, DRAM에 저장되어 있는 컨피규레이션 데이터 이외의 컨피규레이션 데이터가 필요한 경우에는, 정적 재구성을 행할 수밖에 없게 된다. 또한, 가령 DRAM의 용량을 증가시킴으로써 필요하게 될 가능성이 있는 컨피규레이션 데이터 모두를 DRAM에 저장할 경우에는, 추가적인 소비 전력의 증가 및 회로 면적의 확대라는 문제가 생기게 된다.

상술한 점을 감안하여, 본 발명의 일 형태는 프로그래머블 LSI에서의 동작 지연의 억제 및 소비 전력 저감의 양립(兩立)을 도모하는 것을 목적 중 하나로 한다.

본 발명의 일 형태에서는, 컴파일러(compiler)가 프로그래머블 LSI에서 필요하게 될 컨피규레이션 데이터와, 그 데이터가 프로그래머블 LSI에서 사용되는 타이밍(컨피규레이션 메모리에 있어서 보유되게 되는 타이밍) 및 그 데이터를 사용하기 전에 프로그래머블 LSI 내에 저장하는 타이밍을 나타내는 타임 스케줄을 소스 코드로부터 생성한다. 그리고, 상기 타임 스케줄에 의거하여 외부로부터 프로그래머블 LSI로의 새로운 컨피규레이션 데이터의 공급(새로운 컨피규레이션 데이터의 저장)과, 프로그래머블 LSI 내에서의 컨피규레이션 메모리의 데이터의 재기록(회로의 재구성)을 독립적으로 또 병행적으로 행하는 것을 요지로 한다.

예를 들어, 본 발명의 일 형태는, 컴파일러에 의하여 소스 코드로부터 생성되는 복수의 컨피규레이션 데이터 각각에 의거하여, 기능의 변경이 가능한 논리 회로부를 구성하는 프로그래머블 LSI이며, 컴파일러가 소스 코드로부터 생성하는 타임 스케줄에 의거하여 컨피규레이션 데이터의 저장과 논리 회로부의 재구성을 독립적으로 또 병행적으로 행하는 것을 특징으로 하는 프로그래머블 LSI이다.

본 발명의 일 형태의 프로그래머블 LSI에서는, 소스 코드로부터 생성되는 타임 스케줄에 의거하여 컨피규레이션 데이터의 저장과 논리 회로부의 재구성을 독립적으로 또 병행적으로 행한다. 이로써, 논리 회로부의 재구성을 행할 때 필요하게 되는 컨피규레이션 데이터를 프로그래머블 LSI 내에 미리 저장해 둠으로써 순식간에 컨피규레이션 메모리의 데이터의 재기록을 행할 수 있다. 따라서, 상기 프로그래머블 LSI의 동작 지연을 억제할 수 있다.

본 발명의 일 형태의 프로그래머블 LSI에서는, 필요한 컨피규레이션 데이터는 수시 외부로부터 공급된다. 즉, 다수의 컨피규레이션 데이터를 항상 프로그래머블 LSI 내에서 저장할 필요는 없다. 따라서, 상기 프로그래머블 LSI에서의 소비 전력의 증가 및 회로 면적의 확대를 억제할 수 있다.

즉, 본 발명의 일 형태의 프로그래머블 LSI에서는 동작 지연의 억제 및 소비 전력 저감의 양립을 도모할 수 있다.

도 1a는 프로그래머블 LSI의 구조예를 도시한 도면이고, 도 1b는 타이밍 차트의 일례를 도시한 도면이고, 도 1c 내지 도 1f는 프로그래머블 LSI의 상태의 일례를 도시한 도면.

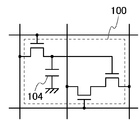

도 2a는 뱅크군의 구성예를 도시한 도면이고, 도 2b 내지 도 2e는 메모리 셀의 구성예를 도시한 도면.

도 3a 내지 도 3c는 메모리 셀의 구조예를 도시한 단면도.

도 4a 내지 도 4c는 메모리 셀의 구조예를 도시한 단면도.

도 5a 내지 도 5c는 메모리 셀의 구조예를 도시한 단면도.

도 6은 메모리 셀의 구성예를 도시한 단면도.

도 7은 휴대용 전자 기기의 블록도.

도 8은 전자 서적의 블록도.

도 9는 논리 회로부의 구성예를 설명하는 회로도.

도 2a는 뱅크군의 구성예를 도시한 도면이고, 도 2b 내지 도 2e는 메모리 셀의 구성예를 도시한 도면.

도 3a 내지 도 3c는 메모리 셀의 구조예를 도시한 단면도.

도 4a 내지 도 4c는 메모리 셀의 구조예를 도시한 단면도.

도 5a 내지 도 5c는 메모리 셀의 구조예를 도시한 단면도.

도 6은 메모리 셀의 구성예를 도시한 단면도.

도 7은 휴대용 전자 기기의 블록도.

도 8은 전자 서적의 블록도.

도 9는 논리 회로부의 구성예를 설명하는 회로도.

본 발명의 일 형태에 대하여 이하에 자세히 설명한다. 다만, 본 발명은 이하의 설명에 한정되지 않고, 본 발명의 취지 및 그 범위에서 벗어남이 없이 그 형태를 다양하게 변경할 수 있다. 따라서, 본 발명은 이하의 기재 내용에 한정하여 해석되는 것은 아니다.

<프로그래머블 LSI의 구성예>

도 1a는 본 발명의 일 형태에 따른 프로그래머블 LSI(1)의 구성예를 도시한 도면이다. 프로그래머블 LSI(1)는 컨피규레이션 데이터(CD_x)를 보유할 수 있는 컨피규레이션 메모리(11)와, 컨피규레이션 메모리(11)에 보유되는 컨피규레이션 데이터(CD_x)에 의거하여 회로 구성(LC(CD_x))이 결정되는 논리 회로부(12)를 갖는다. 또한, 프로그래머블 LSI(1)는 각각에 있어서 컨피규레이션 데이터(CD)를 저장할 수 있는 복수의 뱅크(Bank_1 내지 Bank_n)(뱅크군(10)이라고도 함)를 갖는다.

또한, 프로그래머블 LSI(1)에는 컴파일러(2)에 의하여 소스 코드(SC)로부터 생성되는 컨피규레이션 데이터(CD) 및 타임 스케줄(TS)이 공급되어 있다. 또한, 타임 스케줄(TS)은 프로그래머블 LSI(1)에서 뱅크군(10)에 대하여 행해지는 컨피규레이션 데이터(CD)의 저장의 타이밍과, 컨피규레이션 메모리(11)에 보유되어 있는 기존의 컨피규레이션 데이터(CD)를 뱅크군(10)에 저장되어 있는 복수의 컨피규레이션 데이터(CD) 중 어느 하나로 재기록하는(논리 회로부(12)의 재구성을 행하는) 타이밍을 나타내는 것이다. 바꿔 말하면, 타임 스케줄(TS)은 논리 회로부(12)의 경시적인 재구성의 예정 및 상기 재구성을 실현하기 위하여 필요한 컨피규레이션 데이터(CD)를 뱅크군(10)에 저장할 예정을 나타내는 것이다.

이하, 도 1b 내지 도 1f를 참조하여 프로그래머블 LSI(1)의 동작예에 대하여 설명한다. 또한, 도 1b는 프로그래머블 LSI(1)에 공급되는 타임 스케줄(TS)의 일례를 도시한 도면이고, 도 1c 내지 도 1f는 각 타이밍(T1 내지 T4)에 있어서의 프로그래머블 LSI(1)의 상태를 도시한 도면이다.

타이밍(T0)에 있어서 프로그래머블 LSI(1)에는 도 1b에 도시된 타이밍(T0) 이후의 타임 스케줄(TS)이 공급된다. 또한, 타이밍(T0)에 있어서 복수의 뱅크(Bank_1 내지 Bank_n)에는 컨피규레이션 데이터(CD_1 내지 CD_n)가 저장되어 있는 것으로 한다. 또한, 복수의 뱅크(Bank_1 내지 Bank_n) 중 적어도 하나에 컨피규레이션 데이터가 저장되어 있지 않은 상태라도 이하의 동작을 행할 수 있다. 즉, 본 명세서에 기재된 프로그래머블 LSI에 있어서 복수의 뱅크(Bank_1 내지 Bank_n) 모두에 항상 어떠한 컨피규레이션 데이터가 꼭 저장되어 있어야 한다는 것이 아니다.

타이밍(T1)에 있어서 타임 스케줄(TS)에 의거하여 컨피규레이션 메모리(11)의 데이터가 컨피규레이션 데이터(CD_1)로부터 컨피규레이션 데이터(CD_2)로 재기록된다. 또한, 이에 따라 논리 회로부(12)가 회로 구성(LC(CD_1))으로부터 회로 구성(LC(CD_2))으로 재구성된다(도 1c 참조).

그리고, 컨피규레이션 메모리(11)는 타이밍(T2)까지 컨피규레이션 데이터(CD_2)를 보유한다. 즉, 논리 회로부(12)는 타이밍(T2)까지 회로 구성(LC(CD_2))을 유지한다. 타임 스케줄(TS)에 의거하여 타이밍(T1)에서 타이밍(T2)까지의 기간에 있어서 뱅크(Bank_1)에 있어서의 컨피규레이션 데이터(CD_n+1)의 저장이 시작된다.

타이밍(T2)에 있어서 타임 스케줄(TS)에 의거하여 컨피규레이션 메모리(11)의 데이터가 컨피규레이션 데이터(CD_2)로부터 컨피규레이션 데이터(CD_3)로 재기록된다. 또한, 이에 따라 논리 회로부(12)가 회로 구성(LC(CD_2))으로부터 회로 구성(LC(CD_3))으로 재구성된다. 또한, 타이밍(T2)에 있어서는 뱅크(Bank_1)에 있어서의 컨피규레이션 데이터(CD_n+1)의 저장이 계속하여 행해진다(도 1d 참조).

타이밍(T3)에 있어서 뱅크(Bank_1)에 있어서의 컨피규레이션 데이터(CD_n+1)의 저장이 완료된다. 또한, 타이밍(T3)에 있어서는 컨피규레이션 메모리(11)가 컨피규레이션 데이터(CD_4)를 보유한다. 즉, 논리 회로부(12)는 회로 구성(LC(CD_4))을 유지한다(도 1e 참조).

그리고, 타임 스케줄(TS)에 의거하여 타이밍(T3)에서 타이밍(T4)까지의 기간에 있어서 뱅크(Bank_2)에서의 컨피규레이션 데이터(CD_n+2)의 저장이 시작된다.

타이밍(T4)에 있어서 타임 스케줄(TS)에 의거하여 컨피규레이션 메모리(11)의 데이터가 컨피규레이션 데이터(CD_4)로부터 컨피규레이션 데이터(CD_n+1)로 재기록된다. 또한, 이에 따라 논리 회로부(12)가 회로 구성(LC(CD_4))으로부터 회로 구성(LC(CD_n+1))에 재구성된다. 또한, 타이밍(T4)에 있어서는, 뱅크(Bank_2)에서의 컨피규레이션 데이터(CD_n+2)의 저장이 계속하여 행해진다(도 1f 참조).

이상이 도 1a에 도시된 프로그래머블 LSI의 동작의 일례이다.

상술한 프로그래머블 LSI(1)의 동작에서는, 타임 스케줄(TS)에 의거하여 외부로부터 프로그래머블 LSI(1)로의 새로운 컨피규레이션 데이터(CD)의 공급(새로운 컨피규레이션 데이터(CD)의 저장)과, 프로그래머블 LSI(1) 내에서의 컨피규레이션 메모리의 데이터의 재기록(회로의 재구성)을 독립적으로 또 병행적으로 행할 수 있다.

이로써 필요한 컨피규레이션 데이터(CD)를 수시 외부로부터 뱅크군(10)에 대하여 공급할 수 있게 되는 것과 함께 순식간에 컨피규레이션 메모리의 데이터의 재기록을 행할 수 있게 된다. 따라서, 상술한 프로그래머블 LSI(1)에서는 동작 지연의 억제 및 소비 전력 저감의 양립을 도모할 수 있다.

<뱅크군(10)의 구성예>

도 2a는 도 1a에 도시된 뱅크군(10)의 구성예를 도시한 도면이다. 도 2a에 도시된 뱅크군(10)은 매트릭스 형상으로 배치된 복수의 메모리 셀(100)과, 각각이 특정한 일렬로 배치된 메모리 셀(100) 모두에 전기적으로 접속되어 있는 복수의 입력 비트선(110)과, 각각이 특정한 일렬로 배치된 메모리 셀(100) 모두에 전기적으로 접속되어 있는 복수의 출력 비트선(120)과, 각각이 특정한 일행으로 배치된 메모리 셀(100) 모두에 전기적으로 접속되어 있는 복수의 입력 워드선(130)과, 각각이 특정한 일행으로 배치된 메모리 셀(100) 모두에 전기적으로 접속되어 있는 복수의 출력 워드선(140)을 갖는다.

또한, 복수의 뱅크(Bank_1 내지 Bank_n) 각각은 특정한 일행으로 배치된 복수의 메모리 셀(100)로 구성되어 있다. 즉, 입력 비트선(110) 및 출력 비트선(120)은 각각 복수의 뱅크(Bank_1 내지 Bank_n)가 갖는 복수의 메모리 셀(100) 중 어느 하나에 전기적으로 접속되어 있다. 또한, 입력 워드선(130) 및 출력 워드선(140)은 각각 복수의 뱅크(Bank_1 내지 Bank_n) 중 어느 하나가 갖는 메모리 셀(100) 모두에 전기적으로 접속되어 있다.

도 2a에 도시된 뱅크군(10)에 있어서는, 복수의 입력 비트선(110) 모두에 의하여 입력 버스가 구성되고, 복수의 출력 비트선(120) 모두에 의하여 출력 버스가 구성되어 있다.

또한, 도 2a에 도시된 뱅크군(10)에 있어서는, 복수의 입력 워드선(130) 중 어느 하나에 선택 신호가 공급되는 경우에 상기 입력 워드선(130)에 전기적으로 접속되어 있는 복수의 메모리 셀(100)을 갖는 뱅크에 대한 새로운 컨피규레이션 데이터의 저장이 행해지고, 상기 입력 워드선(130)에 비선택 신호가 공급되는 경우에 상기 뱅크에서 저장된 컨피규레이션 데이터가 유지된다.

또한, 도 2a에 도시된 뱅크군(10)에 있어서는, 복수의 출력 워드선(140) 중 어느 하나에 선택 신호가 공급되는 경우에 상기 출력 워드선(140)에 전기적으로 접속되어 있는 복수의 메모리 셀(100)을 갖는 뱅크에 저장되어 있는 컨피규레이션 데이터를 기존의 컨피규레이션 메모리의 데이터와 치환하고, 상기 출력 워드선(140)에 비선택 신호가 공급되는 경우에 상기 뱅크에 있어서 저장되어 있는 컨피규레이션 데이터를 기존의 컨피규레이션 메모리의 데이터와 치환하지 않는다.

따라서, 도 2a에 도시된 바와 같이, 뱅크군(10)에 있어서는, 복수의 뱅크(Bank_1 내지 Bank_n) 중 어느 하나에서의 컨피규레이션 데이터(CD)의 저장과, 그 이외의 복수의 뱅크((n-1)개의 뱅크) 중 어느 하나에 저장되어 있는 컨피규레이션 데이터에 의한 컨피규레이션 메모리의 데이터의 재기록을 독립적으로 또 병행적으로 행할 수 있다.

<메모리 셀(100)의 구성예>

도 2b 내지 도 2e는, 도 2a에 도시된 메모리 셀(100)의 구성예를 도시한 회로도이다.

도 2b에 도시된 메모리 셀(100)은, 게이트가 입력 워드선(130)에 전기적으로 접속되고 소스 및 드레인 중 한쪽이 입력 비트선(110)에 전기적으로 접속되어 있는 트랜지스터(101)와, 게이트가 트랜지스터(101)의 소스 및 드레인 중 다른 쪽에 전기적으로 접속되고 소스 및 드레인 중 한쪽이 기준 전위선(150)에 전기적으로 접속되어 있는 트랜지스터(102)와, 게이트가 출력 워드선(140)에 전기적으로 접속되고 소스 및 드레인 중 한쪽이 트랜지스터(102)의 소스 및 드레인 중 다른 쪽에 전기적으로 접속되고 소스 및 드레인 중 다른 쪽이 출력 비트선(120)에 전기적으로 접속되어 있는 트랜지스터(103)를 갖는다.

또한, 입력 워드선(130)에는 선택 신호로서 트랜지스터(101)를 온 상태로 하는 전위가 공급되고, 또 비선택 신호로서 트랜지스터(101)를 오프 상태로 하는 전위가 공급된다. 또한, 출력 워드선(140)에는 선택 신호로서 트랜지스터(103)를 온 상태로 하는 전위가 공급되고, 또 비선택 신호로서 트랜지스터(103)를 오프 상태로 하는 전위가 공급된다. 또한, 기준 전위선(150)에는 특정한 고정 전위가 공급되어 있다.

도 2b에 도시된 메모리 셀(100)에서는, 트랜지스터(101)의 소스 및 드레인 중 다른 쪽, 및 트랜지스터(102)의 게이트가 전기적으로 접속되는 노드에 있어서 1비트의 데이터를 저장할 수 있다. 그리고, 저장된 데이터를 트랜지스터(102)의 상태(온 상태 또는 오프 상태)를 판별함으로써 검출할 수 있다. 예를 들어, 상기 데이터의 검출 방법으로서는, 트랜지스터(102) 및 출력 비트선(120)을 포함하는 분압 회로를 구성한 상태에서 상기 출력 비트선(120)의 전위를 검출하는 방법 또는 출력 비트선(120)에 미리 원하는 전위를 공급해 두고, 상기 출력 비트선(120)의 전위가 변화되는지 여부를 검출하는 방법 등을 들 수 있다.

또한, 여기서는 메모리 셀(100)이 1비트(2치(binary))의 데이터를 저장할 수 있는 것으로 설명하였지만, 상기 메모리 셀로서 다(多)비트(다치(multi-level))의 데이터를 저장할 수 있는 메모리 셀을 적용할 수도 있다.

또한, 도 2c에 도시된 바와 같이, 도 2b에 도시된 메모리 셀(100)에 한쪽의 전극이 트랜지스터(101)의 소스 및 드레인 중 다른 쪽에 전기적으로 접속되고, 다른 쪽의 전극이 접지되어 있는 커패시터(104)가 부가된 구성으로 할 수도 있다. 이로써 상기 메모리 셀(100)에서의 데이터 보유 특성의 향상을 도모할 수 있게 된다.

또한, 도 2d에 도시된 바와 같이, 도 2b에 도시된 메모리 셀(100)이 갖는 트랜지스터(102)의 게이트의 접속처와, 트랜지스터(103)의 게이트의 접속처가 치환된 구성으로 할 수도 있다. 또한, 이 경우 출력 워드선(140)에는 상기 메모리 셀(100)을 포함하는 뱅크에 저장되어 있는 컨피규레이션 데이터에 의하여 컨피규레이션 메모리의 데이터를 재기록할 때 트랜지스터(102)를 온 상태로 하는 전위가 공급되고, 또 그 이외의 기간에 있어서 트랜지스터(102)를 오프 상태로 하는 전위가 공급되게 된다.

또한, 도 2e에 도시된 바와 같이, 도 2d에 도시된 메모리 셀(100)에 커패시터(104)가 부가된 구성으로 할 수도 있다.

또한, 트랜지스터(101)로서는, 채널이 산화물 반도체층에 형성되는 트랜지스터를 적용하는 것이 바람직하다. 채널이 산화물 반도체층에 형성되는 트랜지스터는, 오프 전류 값이 극히 작다. 그래서, 트랜지스터(101)로서 채널이 산화물 반도체층에 형성되는 트랜지스터를 적용함으로써 메모리 셀(100)에 있어서의 데이터 보유 특성의 향상을 도모할 수 있다. 또한, 메모리 셀(100)에 있어서, 저장되는 데이터의 다비트화(다치화)를 용이하게 도모할 수 있다.

또한, 트랜지스터(101)뿐만 아니라 트랜지스터(102) 및 트랜지스터(103)도 채널이 산화물 반도체층에 형성되는 트랜지스터인 경우, 트랜지스터(101) 내지 트랜지스터(103)를 동일 공정으로 제작할 수 있게 된다. 또한, 트랜지스터(102) 및 트랜지스터(103)가, 채널이 산화물 반도체층에 형성되는 트랜지스터보다 이동도가 높은 트랜지스터(예를 들어, 채널이 결정질 실리콘층 또는 화합물 반도체층에 형성되는 트랜지스터)인 경우, 컨피규레이션 메모리의 데이터의 재기록 속도의 향상을 도모할 수 있다.

<메모리 셀(100)의 구조예>

상술한 메모리 셀(100)의 구조예에 대하여 설명한다. 구체적으로는, 도 2c에 도시된 트랜지스터(101) 및 트랜지스터(102), 그리고 커패시터(104)의 구조예 및 그 제작 방법예에 대하여 설명한다. 또한, 이하에서는 트랜지스터(101)로서 채널이 산화물 반도체층에 형성되는 트랜지스터를 적용하여 트랜지스터(102)로서 채널이 단결정 실리콘층에 형성되는 트랜지스터를 적용하는 경우에 대하여 설명한다. 또한, 도 2c에 도시된 트랜지스터(103)는 트랜지스터(102)와 마찬가지로 제작할 수 있다.

우선, 도 3a에 도시된 바와 같이, 기판(700) 위에 절연막(701)과, 단결정의 반도체 기판으로부터 분리된 반도체막(702)을 형성한다.

기판(700)으로서 사용할 수 있는 소재에 큰 제한은 없지만, 적어도 후의 가열 처리에 견딜 수 있을 정도의 내열성을 갖고 있는 것이 필요하게 된다. 예를 들어, 기판(700)에는 퓨전법이나 플로트법으로 제작되는 유리 기판, 석영 기판, 반도체 기판, 세라믹 기판 등을 사용할 수 있다. 유리 기판으로서는, 후의 가열 처리의 온도가 높은 경우에는 변형점이 730℃ 이상인 것을 사용하면 좋다.

또한, 반도체막(702)이 단결정 실리콘인 경우를 예로 들어, 트랜지스터(102)의 제작 방법에 대하여 이하에 설명한다. 또한, 구체적인 단결정 반도체막의 제작 방법의 일례에 대하여, 간단히 설명한다. 우선, 단결정 반도체 기판인 본드 기판에, 전계에 의하여 가속된 이온으로 이루어지는 이온빔을 주입하고, 본드 기판의 표면으로부터 일정 깊이의 영역에, 결정 구조가 흐트러짐으로써, 국소적으로 취약화된 취화층을 형성한다. 취화층이 형성되는 영역의 깊이는, 이온 빔의 가속 에너지와 이온 빔의 입사각에 의하여 조절할 수 있다. 그리고, 본드 기판과, 절연막(701)이 형성된 기판(700)을, 사이에 상기 절연막(701)이 개재(介在)되도록 접합한다. 접합은 본드 기판과 기판(700)을 중첩한 후, 본드 기판과 기판(700)의 일부에, 1N/cm2 이상 500N/cm2 이하, 바람직하게는 11N/cm2 이상 20N/cm2 이하 정도의 압력을 가한다. 압력을 가하면, 그 부분으로부터 본드 기판과 절연막(701)이 접합을 시작하고, 최종적으로는 밀착된 면 전체에 접합이 미친다. 다음에, 가열 처리를 행함으로써, 취화층에 존재하는 미소 보이드끼리가 결합하여, 미소 보이드의 체적이 증대된다. 그 결과, 취화층에 있어서 본드 기판의 일부인 단결정 반도체막이, 본드 기판으로부터 분리된다. 상기 가열 처리의 온도는, 기판(700)의 변형점을 넘지 않는 온도로 한다. 그리고, 상기 단결정 반도체막을 에칭 등에 의하여 원하는 형상으로 가공함으로써 반도체막을 형성할 수 있다.

반도체막(702)에는, 문턱 전압을 제어하기 위하여, 붕소, 알루미늄, 갈륨 등의 p형의 도전성을 부여하는 불순물 원소, 또는 인, 비소 등의 n형의 도전성을 부여하는 불순물 원소를 첨가하여도 좋다. 문턱 전압을 제어하기 위한 불순물 원소의 첨가는 소정의 형상으로 에칭에 의하여 가공하기 전의 반도체막에 행하여도 좋고, 소정의 형상으로 에칭에 의하여 가공한 후의 반도체막(702)에 대하여 행하여도 좋다. 또한 문턱 전압을 제어하기 위한 불순물 원소의 첨가를, 본드 기판에 대하여 행해도 좋다. 또는, 불순물 원소의 첨가를 문턱 전압을 대충 조정하기 위하여 본드 기판에 대하여 행한 후에 문턱 전압을 미세 조정하기 위하여 소정의 형상으로 에칭에 의하여 가공하기 전의 반도체막 또는 소정의 형상으로 에칭에 의하여 가공한 후의 반도체막(702)에 행하여도 좋다.

또한, 여기서는 단결정의 반도체막을 사용하는 예에 대하여 설명하였지만, 절연막(701) 위에 기상 성장법을 사용하여 형성된 다결정, 미결정, 비정질의 반도체막을 사용하여도 좋고, 상기 반도체막을 공지의 기술에 따라 결정화하여도 좋다. 공지의 결정화 방법으로서는, 레이저광을 사용한 레이저 결정화법, 촉매 원소를 사용하는 결정화법이 있다. 또는, 촉매 원소를 사용하는 결정화법과 레이저 결정화법을 조합하여 사용할 수도 있다. 또한, 석영 등 내열성이 뛰어난 기판을 사용하는 경우에는, 전열로를 사용한 열 결정화법, 적외광을 사용한 램프 가열 결정화법, 촉매 원소를 사용한 결정화법, 950℃ 정도의 고온 가열법을 조합한 결정화법을 사용하여도 좋다.

다음으로, 도 3b에 도시된 바와 같이, 반도체막(702) 위에 게이트 절연막(703)을 형성한다. 게이트 절연막(703)은 플라즈마 CVD법 또는 스퍼터링법 등을 사용하여 산화 실리콘, 질화 산화 실리콘, 산화 질화 실리콘, 질화 실리콘, 산화 하프늄, 산화 알루미늄, 산화 탄탈, 산화 이트륨, 하프늄 실리케이트(HfSixOy(x>0, y>0)), 질소가 첨가된 하프늄 실리케이트(HfSixOy(x>0, y>0)), 질소가 첨가된 하프늄 알루미네이트(HfAlxOy(x>0, y>0)) 등을 함유한 막을 단층으로 또는 적층시킴으로써 게이트 절연막(703)을 형성할 수 있다.

또한, 본 명세서에 있어서, 산화 질화물이란, 그 조성으로서, 질소보다도 산소의 함유량이 더 많은 물질이고, 또한, 질화 산화물이란, 그 조성으로서, 산소보다도 질소의 함유량이 더 많은 물질을 가리킨다.

또한, 게이트 절연막(703)은 고밀도 플라즈마 처리, 가열 처리 등을 행함으로써 반도체막(702) 표면을 산화 또는 질화함으로써 형성할 수도 있다. 고밀도 플라즈마 처리는 He, Ar, Kr, Xe 등의 희가스와 산소, 산화 질소, 암모니아, 질소, 수소 등의 혼합 가스를 사용하여 행할 수 있다. 이 경우, 플라즈마의 여기를 마이크로파를 도입하여 행함으로써, 저전자 온도로 고밀도의 플라즈마를 생성할 수 있다. 이와 같은 고밀도의 플라즈마로 생성된 산소 라디칼(OH 라디칼을 함유하는 경우도 있다)이나 질소 라디칼(NH 라디칼을 함유하는 경우도 있다)에 의하여, 반도체막의 표면을 산화 또는 질화함으로써, 1nm 내지 20nm, 바람직하게는 5nm 내지 10nm의 절연막이 반도체막에 접하도록 형성할 수 있다. 예를 들어, 아산화 질소(N2O)를 Ar로 1배 내지 3배(유량 비율)로 희석하고 10Pa 내지 30Pa의 압력으로 3kW 내지 5kW의 마이크로파(2.45GHz) 전력을 인가하여 반도체막(702) 표면을 산화 또는 질화시킨다. 이 처리에 의하여 1nm 내지 10nm(바람직하게는 2nm 내지 6nm)의 절연막을 형성한다. 또한, 아산화 질소(N2O)와 실란(SiH4)을 도입하고, 10Pa 내지 30Pa의 압력으로 3kW 내지 5kW의 마이크로파(2.45GHz) 전력을 인가하고 기상 성장법에 의하여 산화 질화 실리콘막을 형성함으로써 게이트 절연막을 형성한다. 고상 반응과 기상 성장법에 의한 반응을 조합함으로써 계면 준위 밀도가 낮고 절연 내압이 뛰어난 게이트 절연막을 형성할 수 있다.

상술한 고밀도 플라즈마 처리에 의한 반도체막의 산화 또는 질화는 고상 반응으로 진행되기 때문에, 게이트 절연막(703)과 반도체막(702)의 계면 준위 밀도를 극히 낮게 할 수 있다. 또한 고밀도 플라즈마 처리에 의하여 반도체막(702)을 직접 산화 또는 질화함으로써 형성되는 절연막의 두께 편차를 억제할 수 있다. 또한, 반도체막이 결정성을 갖는 경우, 고밀도 플라즈마 처리를 사용하여 반도체막 표면을 고상 반응으로 산화시킴으로써, 결정립계에 있어서만 산화가 빨리 진행되는 것을 억제하고, 균일성이 좋고 계면 준위 밀도가 낮은 게이트 절연막을 형성할 수 있다. 고밀도 플라즈마 처리에 의하여 형성된 절연막을, 게이트 절연막의 일부 또는 전부에 포함하여 형성되는 트랜지스터는, 특성의 편차를 억제할 수 있다.

게이트 절연막(703)의 두께는, 예를 들어, 1nm 이상 100nm 이하, 바람직하게는 10nm 이상 50nm 이하로 할 수 있다. 여기서는, 플라즈마 CVD법을 사용하여 산화 실리콘을 포함하는 단층의 절연막을, 게이트 절연막(703)으로서 사용한다.

다음으로, 도 3b에 도시된 바와 같이, 게이트 전극(707)을 형성한다.

게이트 전극(707)은 도전막을 형성한 후, 상기 도전막을 소정의 형상으로 가공함으로써 형성할 수 있다. 상기 도전막의 형성에는 CVD법, 스퍼터링법, 증착법, 스핀 코트법 등을 사용할 수 있다. 또한 도전막은, 탄탈(Ta), 텅스텐(W), 티타늄(Ti), 몰리브덴(Mo), 알루미늄(Al), 구리(Cu), 크롬(Cr), 니오븀(Nb) 등을 사용할 수 있다. 또한 상기 금속을 주성분으로 하는 합금을 사용하여도 좋고, 상기 금속을 함유하는 화합물을 사용하여도 좋다. 또는, 반도체막에 n형의 도전성을 부여하는 인 등의 불순물 원소를 도핑한 다결정 실리콘 등의 반도체를 사용하여 형성하여도 좋다.

또한, 여기서는 게이트 전극(707)을 단층의 도전막으로 형성하였지만, 게이트 전극(707)을 적층된 복수의 도전막으로 형성하여도 좋다.

2개의 도전막의 조합으로서, 1번째 층에 질화 탄탈 또는 탄탈을, 2번째 층에 텅스텐을 사용할 수 있다. 상기 예 외에, 질화 텅스텐과 텅스텐, 질화 몰리브덴과 몰리브덴, 알루미늄과 탄탈, 알루미늄과 티타늄 등을 들 수 있다. 텅스텐이나 질화 탄탈은 내열성이 높기 때문에, 2층의 도전막을 형성한 후의 공정에서 열 활성화를 목적으로 한 가열 처리를 행할 수 있다. 또한 2층의 도전막의 조합으로서, 예를 들어, n형의 도전성을 부여하는 불순물 원소가 도핑된 실리콘과 니켈 실리사이드, n형의 도전성을 부여하는 불순물 원소가 도핑된 실리콘과 텅스텐 실리사이드 등도 사용할 수 있다.

3개의 도전막을 적층하는 3층 구조의 경우는, 몰리브덴막과 알루미늄막과 몰리브덴막의 적층 구조를 채용하면 좋다.

또한, 게이트 전극(707)에 산화 인듐, 산화 인듐 산화 주석, 산화 인듐 산화 아연, 산화 아연, 산화 아연 알루미늄, 산질화 아연 알루미늄, 또는 산화 아연 갈륨 등의 투광성을 갖는 산화물 도전막을 이용할 수도 있다.

또한, 마스크를 사용하지 않고, 액적 토출법을 사용하여 선택적으로 게이트 전극(707)을 형성하여도 좋다. 액적 토출법이란, 소정의 조성물을 함유하는 액적을 세공으로부터 토출 또는 분출함으로써 소정의 패턴을 형성하는 방법을 의미하고, 잉크젯법 등이 그 범주에 포함된다.

또한, 게이트 전극(707)은, 도전막을 형성한 후, ICP(Inductively Coupled Plasma: 유도 결합형 플라즈마) 에칭법을 사용하여, 에칭 조건(코일형의 전극층에 인가되는 전력량, 기판 측의 전극층에 인가되는 전력량, 기판 측의 전극 온도 등)을 적절히 조절함으로써, 원하는 테이퍼 형상을 갖도록 에칭할 수 있다. 또한, 테이퍼 형상은, 마스크의 형상에 따라서도 각도 등을 제어할 수 있다. 또한, 에칭용 가스로서는, 염소, 염화 붕소, 염화 실리콘 또는 사염화 탄소 등의 염소계 가스, 사불화 탄소, 불화 황 또는 불화 질소 등의 불소계 가스 또는 산소를 적절히 사용할 수 있다.

다음에, 도 3c에 도시된 바와 같이, 게이트 전극(707)을 마스크로서 일도전성을 부여하는 불순물 원소를 반도체막(702)에 첨가함으로써, 게이트 전극(707)과 중첩되는 채널 형성 영역(710)과, 채널 형성 영역(710)을 사이에 끼우는 한 쌍의 불순물 영역(709)이 반도체막(702)에 형성된다.

여기서는, 반도체막(702)에 p형을 부여하는 불순물 원소(예를 들어, 붕소)를 첨가하는 경우를 예로 든다.

다음에, 도 4a에 도시된 바와 같이, 게이트 절연막(703), 게이트 전극(707)을 덮도록 절연막(712) 및 절연막(713)을 형성한다. 구체적으로, 절연막(712), 절연막(713)은, 산화 실리콘, 질화 실리콘, 질화 산화 실리콘, 산화 질화 실리콘, 질화 알루미늄, 질화 산화 알루미늄 등의 무기 절연막을 사용할 수 있다. 특히, 절연막(712), 절연막(713)에 유전율이 낮은(low-k) 재료를 사용함으로써, 각종 전극이나 배선의 중첩에 기인하는 용량을 충분히 저감시키는 것이 가능하게 되기 때문에 바람직하다. 또한, 절연막(712), 절연막(713)에, 상기 재료를 사용한 다공성의 절연막을 적용하여도 좋다. 다공성 절연막은 밀도가 높은 절연막과 비교하여 유전율이 저하되기 때문에 전극이나 배선에 기인한 기생 용량을 더 저감할 수 있다.

여기서는, 절연막(712)으로서 산화 질화 실리콘, 절연막(713)으로서 질화 산화 실리콘을 사용하는 경우를 예로 든다. 또한, 여기서는, 게이트 전극(707) 위에 절연막(712), 절연막(713)을 형성하고 있는 경우를 예시하고 있지만, 게이트 전극(707) 위에 절연막을 1층만 형성하여도 좋고, 3층 이상의 복수의 절연막을 적층하도록 형성하여도 좋다.

다음에, 도 4b에 도시된 바와 같이, 절연막(712) 및 절연막(713)에 CMP(화학적 기계 연마) 처리나 에칭 처리를 행함으로써 게이트 전극(707) 표면을 노출시킨다. 또한, 이후 형성되는 트랜지스터(101)의 특성을 향상시키기 위하여 절연막(712) 및 절연막(713) 표면은 가능한 한 평탄하게 해 두는 것이 바람직하다.

상술한 공정에 의하여 트랜지스터(102)를 형성할 수 있다.

다음에, 트랜지스터(101)의 제작 방법에 대하여 설명한다. 우선, 도 4c에 도시된 바와 같이, 절연막(713) 위에 산화물 반도체층(716)을 형성한다.

산화물 반도체층(716)은, 절연막(713) 위에 형성한 산화물 반도체막을 원하는 형상으로 가공함으로써 형성할 수 있다. 상기 산화물 반도체막의 막 두께는 2nm 이상 200nm 이하, 바람직하게는 3nm 이상 50nm 이하, 더욱 바람직하게는 3nm 이상 20nm 이하로 한다. 산화물 반도체막은, 산화물 반도체를 타깃으로서 사용하여, 스퍼터링법에 의하여 형성한다. 또한, 산화물 반도체막은, 희가스(예를 들어 아르곤) 분위기 하, 산소 분위기 하, 또는 희가스(예를 들어 아르곤) 및 산소 혼합 분위기 하에서 스퍼터링법에 의하여 형성할 수 있다.

또한, 산화물 반도체막을 스퍼터링법에 의하여 성막하기 전에, 아르곤 가스를 도입하여 플라즈마를 발생시키는 역 스퍼터링을 행하고, 절연막(712) 및 절연막(713) 표면에 부착되어 있는 먼지를 제거하는 것이 바람직하다. 역 스퍼터링은, 타깃 측에 전압을 인가하지 않고, 아르곤 분위기하에서 기판 측에 RF 전원을 사용하여 전압을 인가함으로써, 기판 근방에 플라즈마를 발생시켜 표면을 개질하는 방법이다. 또한, 아르곤 분위기 대신에 질소, 헬륨 등을 사용하여도 좋다. 또한, 아르곤 분위기에 산소, 또는 아산화 질소 등을 첨가한 분위기에서 행하여도 좋다. 또한, 아르곤 분위기에 염소 또는 사불화 탄소 등을 첨가한 분위기에서 행하여도 좋다.

산화물 반도체층으로서는 적어도 인듐(In) 또는 아연(Zn)을 함유하는 것이 바람직하다. 특히 In과 Zn을 함유하는 것이 바람직하다. 또한, 상기 산화물 반도체층을 사용한 트랜지스터의 전기 특성의 편차를 감소시키기 위한 스테빌라이저로서, In과 Zn에 추가하여 갈륨(Ga)을 갖는 것이 바람직하다. 또한, 스테빌라이저로서 주석(Sn)을 갖는 것이 바람직하다. 또한, 스테빌라이저로서 하프늄(Hf)을 갖는 것이 바람직하다. 또한, 스테빌라이저로서 알루미늄(Al)을 갖는 것이 바람직하다. 또한, 다른 스테빌라이저로서, 란타노이드인, 란탄(La), 세륨(Ce), 프라세오디뮴(Pr), 네오디뮴(Nd), 사마륨(Sm), 유로퓸(Eu), 가돌리늄(Gd), 테르븀(Tb), 디스프로슘(Dy), 홀뮴(Ho), 에르븀(Er), 툴륨(Tm), 이테르븀(Yb), 루테튬(Lu) 중 어느 1종 또는 복수종을 가져도 좋다. 예를 들어, 산화 인듐, 산화 주석, 산화 아연, 2원계 금속의 산화물인 In-Zn계 산화물, Sn-Zn계 산화물, Al-Zn계 산화물, Zn-Mg계 산화물, Sn-Mg계 산화물, In-Mg계 산화물, In-Ga계 산화물, 3원계 금속의 산화물인 In-Ga-Zn계 산화물(IGZO라고도 표기함), In-Al-Zn계 산화물, In-Sn-Zn계 산화물, Sn-Ga-Zn계 산화물, Al-Ga-Zn계 산화물, Sn-Al-Zn계 산화물, In-Hf-Zn계 산화물, In-La-Zn계 산화물, In-Ce-Zn계 산화물, In-Pr-Zn계 산화물, In-Nd-Zn계 산화물, In-Sm-Zn계 산화물, In-Eu-Zn계 산화물, In-Gd-Zn계 산화물, In-Tb-Zn계 산화물, In-Dy-Zn계 산화물, In-Ho-Zn계 산화물, In-Er-Zn계 산화물, In-Tm-Zn계 산화물, In-Yb-Zn계 산화물, In-Lu-Zn계 산화물, 4원계 금속의 산화물인 In-Sn-Ga-Zn계 산화물, In-Hf-Ga-Zn계 산화물, In-Al-Ga-Zn계 산화물, In-Sn-Al-Zn계 산화물, In-Sn-Hf-Zn계 산화물, In-Hf-Al-Zn계 산화물을 사용할 수 있다.

예를 들어, In-Ga-Zn계 산화물 반도체란 인듐(In), 갈륨(Ga), 아연(Zn)을 갖는 산화물 반도체를 의미하며, 그 조성은 불문한다.

또한, 산화물 반도체층으로서 화학식 InMO3(ZnO)m(m>0 또 m은 정수가 아님)으로 표기되는 박막을 사용할 수 있다. 여기서, M은 Ga, Fe, Mn 및 Co 중에서 선택된 하나 또는 복수의 금속 원소를 나타낸다. 또한, 산화물 반도체로서, In2SnO5(ZnO)n(n>0, 또 n은 정수)으로 표기되는 재료를 사용하여도 좋다.

또한, 산화물 반도체로서 In-Zn계 재료를 사용하는 경우에 사용되는 타깃의 조성은 원자 비율(atomic ratio)로 In:Zn=50:1 내지 1:2(몰비(molar ratio)로 환산하면 In2O3:ZnO=25:1 내지 1:4), 바람직하게는, In:Zn=20:1 내지 1:1(몰비로 환산하면In2O3:ZnO=10:1 내지 1:2), 더욱 바람직하게는, In:Zn=15:1 내지 1.5:1(몰비로 환산하면 In2O3:ZnO=15:2 내지 3:4)로 한다. 예를 들어, In-Zn계 산화물 반도체의 형성에 사용하는 타깃은, 원자 비율이 In:Zn:O=X:Y:Z일 때, Z>1.5X+Y로 한다.

여기서는, 인듐(In), 갈륨(Ga), 및 아연(Zn)을 함유하는 타깃을 사용한 스퍼터링법에 의하여 얻어지는 막 두께 30nm의 In-Ga-Zn계 산화물 반도체의 박막을, 산화물 반도체막으로서 사용한다. 상기 타깃으로서 예를 들어, 각 금속의 조성이 In:Ga:Zn=1:1:0.5, In:Ga:Zn=1:1:1, 또는 In:Ga:Zn=1:1:2인 타깃을 사용할 수 있다. 또한, In, Ga 및 Zn을 함유하는 타깃의 충전율은 90% 이상 100% 이하, 바람직하게는 95% 이상 100% 미만이다. 충전율이 높은 타깃을 사용함으로써, 성막한 산화물 반도체막은 치밀한 막이 된다.

여기서는, 감압 상태로 유지된 처리실 내에 기판을 유지하고, 처리실 내의 잔류 수분을 제거하면서 수소 및 수분이 제거된 스퍼터링 가스를 도입하고, 상기 타깃을 사용하여 산화물 반도체막을 형성한다. 형성할 때, 기판 온도를 100℃ 이상 600℃ 이하, 바람직하게는 200℃ 이상 400℃ 이하로 하여도 좋다. 기판을 가열하면서 형성함으로써, 형성된 산화물 반도체막에 함유되는 불순물 농도를 저감할 수 있다. 또한, 스퍼터링에 의한 손상이 경감된다. 처리실 내의 잔류 수분을 제거하기 위해서는, 흡착형의 진공 펌프를 사용하는 것이 바람직하다. 예를 들어, 크라이오 펌프, 이온 펌프, 티타늄 서블리메이션(sublimation) 펌프를 사용하는 것이 바람직하다. 또한, 배기 수단으로서는, 터보 펌프에 콜드 트랩(cold trap)을 더한 것이라도 좋다. 크라이오 펌프를 사용하여 처리실을 배기하면, 예를 들어, 수소 원자, 물(H2O) 등 수소 원자를 함유하는 화합물(보다 바람직하게는 탄소 원자를 함유하는 화합물도) 등이 배기되기 때문에, 상기 처리실에서 형성한 산화물 반도체막에 함유되는 불순물의 농도를 저감할 수 있다.

성막 조건의 일례로서는, 기판과 타깃 사이의 거리를 100mm, 압력 0.6Pa, 직류(DC) 전원 0.5kW, 산소(산소 유량 비율 100%) 분위기하의 조건이 적용된다. 또한, 펄스 직류(DC) 전원을 사용하면, 성막시에 발생하는 먼지를 경감할 수 있고, 막 두께 분포도 균일하게 되기 때문에 바람직하다.

또한, 스퍼터링 장치의 처리실의 누설 속도를 1×10-10Paㆍm3/초 이하로 함으로써, 스퍼터링법에 의한 성막 도중에서의 산화물 반도체막으로의 알칼리 금속, 수소화물 등의 불순물의 혼입을 저감할 수 있다. 또한, 배기계로서 상술한 흡착형의 진공 펌프를 사용함으로써 배기계로부터의 알칼리 금속, 수소 원자, 수소 분자, 물, 수산기 또는 수소화물 등의 불순물의 역류를 저감할 수 있다.

또한, 타깃의 순도를, 99.99% 이상으로 함으로써, 산화물 반도체막에 혼입하는 알칼리 금속, 수소 원자, 수소 분자, 물, 수산기, 또는 수소화물 등을 저감할 수 있다. 또한, 상기 타깃을 사용함으로써, 산화물 반도체막에 있어서, 리튬, 나트륨, 칼륨 등의 알칼리 금속의 농도를 저감할 수 있다.

또한, 산화물 반도체막에 수소, 수산기 및 수분이 가능한 한 함유되지 않도록 하기 위하여, 성막의 전처리로서, 스퍼터링 장치의 예비 가열실에서 절연막(712) 및 절연막(713)까지가 형성된 기판(700)을 예비 가열하고, 기판(700)에 흡착된 수분 또는 수소 등의 불순물을 탈리하여 배기하는 것이 바람직하다. 또한, 예비 가열의 온도로서는, 100℃ 이상 400℃ 이하, 바람직하게는 150℃ 이상 300℃ 이하이다. 또한, 예비 가열실에 제공하는 배기 수단은 크라이오 펌프가 바람직하다. 또한, 이 예비 가열의 처리는 생략할 수도 있다. 또한 이 예비 가열은, 나중에 행해지는 게이트 절연막(721)의 성막 전에, 도전막(719), 도전막(720)까지 형성한 기판(700)에도 마찬가지로 행하여도 좋다.

또한, 산화물 반도체층(716)을 형성하기 위한 에칭은 드라이 에칭과 웨트 에칭 중 어느 쪽이라도 좋고, 양쪽 모두를 사용하여도 좋다. 드라이 에칭에 사용하는 에칭 가스로서는, 염소를 함유하는 가스(염소계 가스, 예를 들어 염소(Cl2), 삼염화 붕소(BCl3), 사염화 실리콘(SiCl4), 사염화 탄소(CCl4) 등)이 바람직하다. 또한, 불소를 함유하는 가스(불소계 가스, 예를 들어 사불화 탄소(CF4), 육불화 황(SF6), 삼불화 질소(NF3), 트리플루오로메탄(CHF3) 등), 브로민화 수소(HBr), 산소(O2), 이들의 가스에 헬륨(He)이나 아르곤(Ar) 등의 희가스를 첨가한 가스, 등을 사용할 수 있다.

드라이 에칭법으로서는, 평행 평판형 RIE(Reactive Ion Etching)법이나, ICP(Inductively Coupled Plasma: 유도 결합형 플라즈마) 에칭법을 사용할 수 있다. 원하는 형상으로 에칭할 수 있도록 에칭 조건(코일형의 전극에 인가되는 전력량, 기판 측의 전극에 인가되는 전력량, 기판 측의 전극 온도 등)을 적절히 조절한다.

웨트 에칭에 사용하는 에칭액으로서, 인산과 아세트산과 질산을 혼합한 용액, 시트르산이나 옥살산 등의 유기산을 사용할 수 있다. 여기서는, ITO-07N(KANTO CHEMICAL CO.,INC. 제조)을 사용한다.

산화물 반도체층(716)을 형성하기 위한 레지스트 마스크를 잉크젯법에 의하여 형성하여도 좋다. 레지스트 마스크를 잉크젯법으로 형성하면 포토 마스크를 사용하지 않기 때문에, 제조 비용을 저감할 수 있다.

또한, 다음 공정의 도전막을 형성하기 전에 역 스퍼터링을 행하고, 산화물 반도체층(716) 및 절연막(712) 및 절연막(713) 표면에 부착되어 있는 레지스트 잔사 등을 제거하는 것이 바람직하다.

또한, 스퍼터링 등으로 성막된 산화물 반도체막 중에는, 불순물로서의 수분 또는 수소(수산기를 함유함)가 다량으로 함유되어 있는 경우가 있다. 수분 또는 수소는, 도너 준위를 형성하기 쉬우므로, 산화물 반도체에 있어서는 불순물이다. 따라서, 본 발명의 일 형태에서는 산화물 반도체막 중의 수분 또는 수소 등의 불순물을 저감(탈수화 또는 탈수소화)하기 위하여, 산화물 반도체층(716)에 대하여 감압 분위기하, 질소나 희가스 등의 불활성 가스 분위기하, 산소 가스 분위기하, 또는 초건조 에어(CRDS(캐비티 링 다운 레이저 분광법) 방식의 노점계를 사용하여 측정한 경우의 수분량이 20ppm(노점 환산으로 -55℃) 이하, 바람직하게는 1ppm 이하, 바람직하게는 10ppb 이하인 공기) 분위기하에서 산화물 반도체층(716)에 가열 처리를 행한다.

산화물 반도체층(716)에 가열 처리를 행함으로써, 산화물 반도체층(716) 내의 수분 또는 수소를 탈리시킬 수 있다. 구체적으로는, 250℃ 이상 750℃ 이하, 바람직하게는 400℃ 이상 기판의 변형점 미만의 온도로 가열 처리를 행하면 좋다. 예를 들어, 500℃, 3분간 이상 6분간 이하 정도로 행하면 좋다. 가열 처리에 RTA법을 사용하면, 단시간에 탈수화 또는 탈수소화를 행할 수 있기 때문에, 유리 기판의 변형점을 초과하는 온도로도 처리할 수 있다.

여기서는, 가열 처리 장치의 하나인 전기로를 사용한다.

또한, 가열 처리 장치는 전기로에 한정되지 않고, 저항 발열체 등의 발열체로부터의 열전도 또는 열복사에 의하여 피처리물을 가열하는 장치를 구비하여도 좋다. 예를 들어, GRTA(Gas Rapid Thermal Annealing) 장치, LRTA(Lamp Rapid Thermal Annealing) 장치 등의 RTA(Rapid Thermal Annealing) 장치를 사용할 수 있다. LRTA 장치는, 할로겐 램프, 메탈할라이드 램프, 크세논아크 램프, 카본아크 램프, 고압 나트륨 램프, 고압 수은 램프 등의 램프로부터 발하는 광(전자기파)의 복사에 의하여, 피처리물을 가열하는 장치이다. GRTA 장치는, 고온의 가스를 사용하여 가열 처리를 행하는 장치이다. 기체에는, 아르곤 등의 희가스, 또는 질소와 같이 가열 처리에 의하여 피처리물과 반응하지 않는 불활성 기체가 사용된다.

가열 처리에 있어서는, 질소, 또는 헬륨, 네온, 아르곤 등의 희가스에, 수분 또는 수소 등이 함유되지 않는 것이 바람직하다. 또는, 가열 처리 장치에 도입하는 질소, 또는 헬륨, 네온, 아르곤 등의 희가스의 순도를, 6N(99.9999%) 이상, 바람직하게는 7N(99.99999%) 이상(즉 불순물 농도를 1ppm 이하, 바람직하게는 0.1ppm 이하)으로 하는 것이 바람직하다.

또한, 알칼리 금속은 산화물 반도체를 구성하는 원소가 아니기 때문에, 불순물이다. 알칼리 토금속도 산화물 반도체를 구성하는 원소가 아닌 경우에, 불순물이 된다. 특히, 알칼리 금속 중 Na는 산화물 반도체층에 접하는 절연막이 산화물인 경우, 상기 절연막 중으로 확산되어 Na+가 된다. 또한, Na는 산화물 반도체층 내에서, 산화물 반도체를 구성하는 금속과 산소의 결합을 분단하거나, 또는, 그 결합 속에 끼어 든다. 그 결과, 예를 들어, 문턱 전압이 마이너스 방향으로 시프트함에 의한 노 멀리 온(normally ON)화, 이동도의 저하 등의 트랜지스터 특성의 열화가 일어나고, 게다가, 특성의 편차도 생긴다. 이 불순물에 의하여 초래되는 트랜지스터의 특성의 열화와 특성의 편차는, 산화물 반도체층 내의 수소 농도가 충분히 낮은 경우에서 현저하게 나타난다. 따라서, 산화물 반도체층 중의 수소 농도가 1×1018/cm3 이하, 보다 바람직하게는 1×1017/cm3 이하인 경우에는, 상기 불순물의 농도를 저감하는 것이 바람직하다. 구체적으로, 2차 이온 질량 분석법에 의한 Na 농도의 측정값은, 5×1016/cm3 이하, 바람직하게는 1×1016/cm3 이하, 더욱 바람직하게는 1×1015/cm3 이하로 하면 좋다. 마찬가지로 Li농도의 측정값은, 5×1015/cm3 이하, 바람직하게는 1×1015/cm3 이하로 하면 좋다. 마찬가지로 K 농도의 측정값은, 5×1015/cm3 이하, 바람직하게는 1×1015/cm3 이하로 하면 좋다.

상술한 공정에 의하여 산화물 반도체층(716) 내의 수소 농도를 저감할 수 있다. 또한, 유리 전이 온도 이하의 가열 처리로, 캐리어 밀도가 극도로 적고 밴드 갭이 넓은 산화물 반도체층을 형성할 수 있다. 따라서, 대면적 기판을 사용하여 트랜지스터를 제작할 수 있고, 양산성을 높일 수 있다. 상기 가열 처리는, 산화물 반도체막의 성막 이후이면, 언제라도 행할 수 있다.

또한, 산화물 반도체막은 단결정, 다결정(폴리크리스탈이라고도 함) 또는 비정질 등의 상태를 취한다.

바람직하게는, 산화물 반도체막은 CAAC-OS(C Axis Aligned Crystalline Oxide Semiconductor)막으로 한다.

CAAC-OS막은 완전한 단결정이 아니다. CAAC-OS막에 포함되는 결정부는 하나의 변이 100nm 미만인 입방체 내에 들어가는 크기인 경우가 많다. 또한, 투과형 전자 현미경(TEM: Transmission Electron Microscope)에 의한 관찰상에서는 CAAC-OS막에 포함되는 비정질부와 결정부의 경계는 명확하지 않다. 또한, TEM에 의하여 CAAC-OS막에는 입계(그레인 바운더리라고도 함)는 확인할 수 없다. 그래서, CAAC-OS막은 입계에 기인하는 전자 이동도의 저하가 억제된다.

CAAC-OS막에 포함되는 결정부는 c축이 CAAC-OS막의 피형성면의 법선 벡터 또는 표면의 법선 벡터에 평행한 방향으로 정렬되고, 또 ab면에 수직인 방향에서 보아서 삼각 형상 또는 육각 형상의 원자 배열을 갖고, c축에 수직인 방향에서 보아서 금속 원자가 층상 또는 금속 원자와 산소 원자가 층상으로 배열되어 있다. 또한, 상이한 결정부 사이에서 a축 및 b축의 방향이 각각 상이하여도 좋다. 본 명세서에서 단순히 “수직”이라고 기재하는 경우에는, 85° 이상 95° 이하의 범위도 포함되는 것으로 한다. 또한, 단순히 “평행”이라고 기재하는 경우에는, -5° 이상 5° 이하의 범위도 포함되는 것으로 한다.

또한, CAAC-OS막에서 결정부의 분포가 균일하지 않아도 좋다. 예를 들어, CAAC-OS막의 형성 과정에서 산화물 반도체막의 표면 측에서 결정 성장시키는 경우에는, 피형성면 근방보다 표면 근방에서 결정부가 차지하는 비율이 높게 되는 경우가 있다. 또한, CAAC-OS막에 불순물을 첨가함으로써 상기 불순물 첨가 영역에서 결정부의 결정성이 저하되는 경우도 있다.

CAAC-OS막에 포함되는 결정부의 c축은 CAAC-OS막의 피형성면의 법선 벡터 또는 표면의 법선 벡터에 평행한 방향으로 정렬되기 때문에, CAAC-OS막의 형상(피형성면의 단면 형상 또는 표면의 단면 형상)에 따라서는 서로 상이한 방향을 향하는 경우가 있다. 또한, 결정부의 c축 방향은 CAAC-OS막이 형성되었을 때의 피형성면의 법선 벡터 또는 표면의 법선 벡터에 평행한 방향이 된다. 성막 또는 성막 후에 가열 처리 등의 결정화 처리에 의하여 결정부가 형성된다.

CAAC-OS막을 사용한 트랜지스터는 가시광이나 자외광의 조사에 기인한 전기 특성의 변동이 작다. 따라서, 상기 트랜지스터는 신뢰성이 높다.

또한, 산화물 반도체막을 구성하는 산소의 일부는 질소로 치환되어도 좋다.

다음에, 도 5a에 도시된 바와 같이, 게이트 전극(707)과 접하고, 또 산화물 반도체층(716)과도 접하는 도전막(719)과, 산화물 반도체층(716)과 접하는 도전막(720)을 형성한다. 도전막(719) 및 도전막(720)은 소스 전극 또는 드레인 전극으로서 기능한다.

구체적으로, 도전막(719) 및 도전막(720)은, 스퍼터링법이나 진공 증착법으로 도전막을 형성한 후, 상기 도전막을 소정의 형상으로 가공함으로써, 형성할 수 있다.

도전막(719) 및 도전막(720)이 되는 도전막은 알루미늄, 크롬, 구리, 탄탈, 티타늄, 몰리브덴, 텅스텐 중에서 선택된 원소, 또는 상술한 원소를 성분으로 하는 합금, 상술한 원소를 조합한 합금막 등을 들 수 있다. 또한, 알루미늄, 구리 등의 금속막의 하측 또는 상측에 크롬, 탄탈, 티타늄, 몰리브덴, 텅스텐 등의 고융점 금속막을 적층시킨 구성으로 하여도 좋다. 또한, 알루미늄 또는 구리는, 내열성이나 부식성의 문제를 피하기 위하여, 고융점 금속 재료와 조합하여 사용하면 좋다. 고융점 금속 재료로서는, 몰리브덴, 티타늄, 크롬, 탄탈, 텅스텐, 네오디뮴, 스칸듐, 이트륨 등을 사용할 수 있다.

또한 도전막(719) 및 도전막(720)이 되는 도전막은, 단층 구조로 하여도 좋고, 2층 이상의 적층 구조로 하여도 좋다. 예를 들어, 실리콘을 함유하는 알루미늄막의 단층 구조, 알루미늄막 위에 티타늄막을 적층하는 2층 구조, 티타늄막과 그 티타늄막 위에 겹쳐 알루미늄막을 적층하고, 또한 그 위에 티타늄막을 형성하는 3층 구조 등을 들 수 있다. 또한, Cu-Mg-Al 합금, Mo-Ti 합금, Ti, Mo는 산화막과의 밀착성이 높다. 따라서, 아래층에 Cu-Mg-Al 합금, Mo-Ti 합금, Ti, 또는 Mo로 구성되는 도전막, 위층에 Cu로 구성되는 도전막을 적층하고, 상기 적층된 도전막을 도전막(719) 및 도전막(720)에 사용함으로써, 산화막인 절연막과, 도전막(719) 및 도전막(720)과의 밀착성을 높일 수 있다.

또한 도전막(719) 및 도전막(720)이 되는 도전막으로서는, 도전성 금속 산화물로 형성하여도 좋다. 도전성 금속 산화물로서는 산화 인듐, 산화 주석, 산화 아연, 산화 인듐 산화 주석, 산화 인듐 산화 아연, 또는 상기 금속 산화물 재료에 실리콘 또는 산화 실리콘을 함유시킨 것을 사용할 수 있다.

도전막을 형성한 후에 가열 처리를 행하는 경우에는, 이 가열 처리에 견딜 수 있는 내열성을 도전막에 갖게 하는 것이 바람직하다.

또한, 도전막을 에칭할 때 산화물 반도체층(716)이 가능한 한 제거되지 않도록 각각의 재료 및 에칭 조건을 적절히 조절한다. 에칭 조건에 따라서는 산화물 반도체층(716)의 노출된 부분이 부분적으로 에칭됨으로써 홈부(오목부)가 형성될 경우도 있다.

여기서는 도전막에 티타늄막을 사용한다. 그래서, 암모니아와 과산화 수소수를 함유하는 용액(암모니아 과수)을 사용하여 선택적으로 도전막을 웨트 에칭할 수 있다. 구체적으로는, 31wt%의 과산화 수소수와, 28wt%의 암모니아수와, 물을, 체적 비율 5:2:2로 혼합한 암모니아과수를 사용한다. 또는 염소(Cl2), 염화 붕소(BCl3) 등을 함유시킨 가스를 사용하여 도전막을 드라이 에칭하여도 좋다.

또한, 포토리소그래피 공정에서 사용하는 포토 마스크 수 및 공정 수를 삭감하기 위하여 투과한 광에 다단계의 강도를 갖게 하는 다계조 마스크로 형성된 레지스트 마스크를 사용하여 에칭 공정을 행하여도 좋다. 다계조 마스크를 사용하여 형성한 레지스트 마스크는 복수의 막 두께를 갖는 형상으로 되고, 에칭을 행함으로써 형상을 더 변형시킬 수 있기 때문에, 다른 패턴으로 가공하는 복수의 에칭 공정에 사용할 수 있다. 따라서, 1장의 다계조 마스크에 의하여 적어도 2종류 이상의 상이한 패턴에 대응하는 레지스트 마스크를 형성할 수 있다. 따라서 노광 마스크 수를 삭감할 수 있고, 대응하는 포토리소그래피 공정도 삭감할 수 있으므로 공정의 간략화가 가능해진다.

또한, 산화물 반도체층(716)과 소스 전극 또는 드레인 전극으로서 기능하는 도전막(719) 및 도전막(720) 사이에 소스 영역 및 드레인 영역으로서 기능하는 산화물 도전막을 제공하도록 하여도 좋다. 산화물 도전막의 재료로서는 산화 아연을 성분으로서 함유하는 것이 바람직하고, 산화 인듐을 함유하지 않는 것이 바람직하다. 이와 같은 산화물 도전막으로서, 산화 아연, 산화 아연 알루미늄, 산질화 아연 알루미늄, 산화 아연 갈륨 등을 적용할 수 있다.

예를 들어, 산화물 도전막을 형성하는 경우에는, 산화물 도전막을 형성하기 위한 에칭 가공과, 도전막(719) 및 도전막(720)을 형성하기 위한 에칭 가공을 일괄적으로 행하도록 하여도 좋다.

소스 영역 및 드레인 영역으로서 기능하는 산화물 도전막을 형성함으로써, 산화물 반도체층(716)과 도전막(719) 및 도전막(720) 사이의 저항을 낮출 수 있으므로 트랜지스터의 고속 동작을 실현할 수 있다. 또한, 소스 영역 및 드레인 영역으로서 기능하는 산화물 도전막을 제공함으로써 트랜지스터의 내압을 높일 수 있다.

계속해서, N2O, N2 또는 Ar 등의 가스를 사용한 플라즈마 처리를 행하도록 하여도 좋다. 이 플라즈마 처리에 의하여 노출되어 있는 산화물 반도체층 표면에 부착된 물 등을 제거한다. 또한, 산소와 아르곤의 혼합 가스를 사용하여 플라즈마 처리를 행하여도 좋다.

또한, 플라즈마 처리를 행한 후, 도 5b에 도시된 바와 같이 도전막(719) 및 도전막(720)과, 산화물 반도체층(716)을 덮도록 게이트 절연막(721)을 형성한다. 그리고, 게이트 절연막(721) 위에서 산화물 반도체층(716)과 중첩되는 위치에 게이트 전극(722)을 형성하고, 도전막(719)과 중첩되는 위치에 도전막(723)을 형성한다.

게이트 절연막(721)은 플라즈마 CVD법, 스퍼터링법, 또는 유기 금속 기상 성장법(MOCVD법) 등을 사용하여 산화 실리콘, 질화 산화 실리콘, 산화 질화 실리콘, 질화 실리콘, 산화 하프늄, 산화 알루미늄, 산화 탄탈, 산화 이트륨, 하프늄 실리케이트(HfSixOy(x>0, y>0)), 질소가 첨가된 하프늄 실리케이트(HfSixOy(x>0, y>0)), 질소가 첨가된 하프늄 알루미네이트(HfAlxOy(x>0, y>0)), 산화 갈륨, 트리메틸갈륨, 트리에틸갈륨 등을 함유하는 막을 단층으로 또는 적층시킴으로써 형성할 수 있다.

또한, 게이트 절연막(721)은, 수분이나, 수소 등의 불순물을 가능한 한 함유하지 않는 것이 바람직하고, 단층의 절연막이라도 좋고, 적층된 복수의 절연막으로 구성되어 있어도 좋다. 게이트 절연막(721)에 수소가 함유되면, 그 수소가 산화물 반도체층(716)으로 침입하거나, 또는 수소가 산화물 반도체층(716) 내의 산소를 뽑아 산화물 반도체층(716)이 저저항화(n형화)되기 때문에 기생 채널이 형성될 우려가 있다. 따라서, 게이트 절연막(721)은 가능한 한 수소를 함유하지 않는 막이 되도록, 성막 방법에 수소를 사용하지 않는 것이 중요하다. 상기 게이트 절연막(721)에는, 배리어성이 높은 재료를 사용하는 것이 바람직하다. 예를 들어, 배리어성이 높은 절연막으로서 질화 실리콘막, 질화 산화 실리콘막, 질화 알루미늄막 또는 질화 산화 알루미늄막 등을 사용할 수 있다. 적층된 복수의 절연막을 사용하는 경우에는, 질소의 함유 비율이 낮은 산화 실리콘막, 산화 질화 실리콘막 등의 절연막을 상기 배리어성이 높은 절연막보다 산화물 반도체층(716)에 가까운 측에 형성한다. 그리고, 질소의 함유 비율이 낮은 절연막을 개재하여 도전막(719), 도전막(720), 및 산화물 반도체층(716)과 중첩되도록 배리어성이 높은 절연막을 형성한다. 배리어성이 높은 절연막을 사용함으로써, 산화물 반도체층(716) 내, 게이트 절연막(721) 내, 또는 산화물 반도체층(716)과 다른 절연막의 계면과 그 근방에 수분 또는 수소 등의 불순물이 들어가는 것을 방지할 수 있다. 또한, 산화물 반도체층(716)과 접하도록 질소의 비율이 낮은 산화 실리콘막, 산화 질화 실리콘막 등의 절연막을 형성함으로써, 배리어성이 높은 재료를 사용한 절연막이 산화물 반도체층(716)과 접하는 것을 방지할 수 있다.

여기서는, 스퍼터링법으로 형성된 막 두께 200nm의 산화 실리콘막 위에, 스퍼터링법으로 형성된 막 두께 100nm의 질화 실리콘막을 적층시킨 구조를 갖는 게이트 절연막(721)을 형성한다. 성막시의 기판 온도는, 실온 이상 300℃ 이하로 하면 좋고, 여기서는 100℃로 한다.

또한, 게이트 절연막(721)을 형성한 후에, 가열 처리를 행하여도 좋다. 가열 처리는 질소, 초건조 공기 또는 희가스(아르곤, 헬륨 등)의 분위기 하에 있어서, 바람직하게는 200℃ 이상 400℃ 이하, 예를 들어 250℃ 이상 350℃ 이하로 행한다. 상기 가스는, 물의 함유량이 20ppm 이하, 바람직하게는 1ppm 이하, 보다 바람직하게는 10ppb 이하인 것이 바람직하다. 여기서는, 예를 들어, 질소 분위기 하에서 250℃로, 1시간 동안의 가열 처리를 행한다. 또는, 도전막(719) 및 도전막(720)을 형성하기 전에 수분 또는 수소를 저감시키기 위하여 산화물 반도체층에 대하여 행한 상기 가열 처리와 마찬가지로 고온으로 단시간의 RTA 처리를 행하여도 좋다. 산소를 함유한 게이트 절연막(721)이 제공된 후에 가열 처리가 행해짐으로써 산화물 반도체층(716)에 대하여 행한 상기 가열 처리로 인하여 산화물 반도체층(716)에 산소 결손이 발생하더라도 게이트 절연막(721)으로부터 산화물 반도체층(716)에 산소가 공급된다. 그리고, 산화물 반도체층(716)에 산소가 공급됨으로써, 산화물 반도체층(716)에서 도너가 되는 산소 결손을 저감하고, 화학량론적 조성을 만족시킬 수 있다. 산화물 반도체층(716)에는, 화학량론적 조성을 초과하는 양의 산소가 함유되어 있는 것이 바람직하다. 결과적으로, 산화물 반도체층(716)을 i형에 가깝게 할 수 있고, 산소 결손으로 인한 트랜지스터의 전기 특성의 편차를 경감하고, 전기 특성의 향상을 실현할 수 있다. 이 가열 처리를 행하는 타이밍은 게이트 절연막(721)을 형성한 후라면 특별히 한정되지 않고, 다른 공정, 예를 들어, 수지막을 형성할 때의 가열 처리나 투명 도전막을 저저항화시키기 위한 가열 처리가 이 가열 처리를 겸함으로써, 공정수를 증가시키지 않고 산화물 반도체층(716)을 i형에 가깝게 할 수 있다.

또한, 산소 분위기 하에서 산화물 반도체층(716)에 가열 처리를 행함으로써, 산화물 반도체에 산소를 첨가하여 산화물 반도체층(716) 내에서 도너가 되는 산소 결손을 저감시켜도 좋다. 가열 처리의 온도는, 예를 들어 100℃ 이상 350℃ 미만, 바람직하게는 150℃ 이상 250℃ 미만으로 행한다. 상기 산소 분위기 하에서의 가열 처리에 사용되는 산소 가스에는, 물, 수소 등이 함유되지 않는 것이 바람직하다. 또는, 가열 처리 장치에 도입하는 산소 가스의 순도를, 6N(99.9999%) 이상, 바람직하게는 7N(99.99999%) 이상, (즉 산소 내의 불순물 농도를 1ppm 이하, 바람직하게는 0.1ppm 이하)으로 하는 것이 바람직하다.

또는, 이온 주입법 또는 이온 도핑법 등을 사용하여 산화물 반도체층(716)에 산소를 첨가함으로써, 도너가 되는 산소 결손을 저감시켜도 좋다. 예를 들어, 2.45GHz의 마이크로파로 플라즈마화한 산소를 산화물 반도체층(716)에 첨가하면 좋다.

또한, 게이트 전극(722) 및 도전막(723)은 게이트 절연막(721) 위에 도전막을 형성한 후, 상기 도전막을 에칭에 의하여 가공함으로써 형성할 수 있다. 게이트 전극(722) 및 도전막(723)은, 게이트 전극(707), 또는 도전막(719) 및 도전막(720)과 같은 재료를 사용하여 형성할 수 있다.

게이트 전극(722) 및 도전막(723)의 막 두께는, 10nm 내지 400nm, 바람직하게는 100nm 내지 200nm로 한다. 여기서는, 텅스텐 타깃을 사용한 스퍼터링법에 의하여 150nm의 게이트 전극용의 도전막을 형성한 후, 상기 도전막을 에칭에 의하여 원하는 형상으로 가공함으로써, 게이트 전극(722) 및 도전막(723)을 형성한다. 또한, 레지스트 마스크를 잉크젯법으로 형성하여도 좋다. 레지스트 마스크를 잉크젯법으로 형성하면 포토 마스크를 사용하지 않기 때문에, 제조 비용을 저감할 수 있다.

상술한 공정에 의하여, 트랜지스터(101)가 형성된다.

또한, 트랜지스터(101)로서 산화물 반도체층에 채널이 형성된 트랜지스터에 한정되지 않고, 실리콘보다 밴드 갭이 넓고 진성 캐리어 밀도가 실리콘보다 낮은 반도체 재료를 채널 형성 영역에 포함하는 트랜지스터를 사용할 수도 있다. 이와 같은 반도체 재료로서는 산화물 반도체 외, 예를 들어, 탄소화 실리콘, 질화 갈륨 등을 들 수 있다. 이와 같은 반도체 재료를 채널 형성 영역에 포함함으로써 오프 전류가 매우 낮은 트랜지스터를 실현할 수 있다.

또한, 게이트 절연막(721)을 사이에 개재하여 도전막(719)과 도전막(723)이 중첩되는 부분이, 커패시터(104)에 상당한다.

또한, 트랜지스터(101)는 싱글 게이트 구조의 트랜지스터를 사용하여 설명하였지만, 필요에 따라 전기적으로 접속된 복수의 게이트 전극을 가짐으로써 복수의 채널 형성 영역을 갖는 멀티 게이트 구조의 트랜지스터도 형성할 수 있다.

또한, 산화물 반도체층(716)과 접하는 절연막(게이트 절연막(721)이 해당함)은 제 13 족 원소 및 산소를 함유한 절연 재료를 사용하도록 하여도 좋다. 산화물 반도체 재료에는 제 13 족 원소를 함유하는 것이 많으며, 제 13 족 원소를 함유하는 절연 재료는 산화물 반도체와의 상성(相性)이 좋고, 이것을 산화물 반도체층에 접하는 절연막에 사용함으로써, 산화물 반도체층과의 계면 상태를 양호하게 유지할 수 있다.

제 13 족 원소를 함유한 절연 재료란 절연 재료에 하나 또는 복수의 제 13 족 원소를 함유한 것을 가리킨다. 제 13 족 원소를 함유한 절연 재료로서는, 예를 들어, 산화 갈륨, 산화 알루미늄, 산화 알루미늄 갈륨, 산화 갈륨 알루미늄 등을 들 수 있다. 여기서, 산화 알루미늄 갈륨이란, 갈륨의 함유량(at.%)보다 알루미늄의 함유량(at.%)이 많은 것을 나타내고, 산화 갈륨 알루미늄이란, 갈륨의 함유량(at.%)이 알루미늄의 함유량(at.%) 이상인 것을 나타낸다.

예를 들어, 갈륨을 함유한 산화물 반도체층에 접하여 절연막을 형성하는 경우에, 절연막에 산화 갈륨을 함유한 재료를 사용함으로써 산화물 반도체층과 절연막의 계면 특성을 양호하게 유지할 수 있다. 예를 들어, 산화물 반도체층과 산화 갈륨을 함유하는 절연막을 접하여 제공함으로써, 산화물 반도체층과 절연막의 계면에 있어서의 수소의 파일업(pileup)을 저감시킬 수 있다. 또한, 절연막에 산화물 반도체의 성분 원소와 동일한 족의 원소를 사용하는 경우에는, 같은 효과를 얻는 것이 가능하다. 예를 들어, 산화 알루미늄을 함유하는 재료를 사용하여 절연막을 형성하는 것도 유효하다. 또한, 산화 알루미늄은 물을 투과시키기 어렵다는 특성을 갖고 있으므로, 상기 재료를 사용하는 것은, 산화물 반도체층으로의 물의 침입 방지라는 점에서도 바람직하다.

또한 산화물 반도체층(716)에 접하는 절연막은, 산소 분위기 하에서의 가열 처리나, 산소 도핑 등에 의하여, 절연 재료를 화학량론적 조성보다 산소가 많은 상태로 하는 것이 바람직하다. 산소 도핑이란, 산소를 벌크에 첨가하는 것을 말한다. 또한, 상기 벌크란 용어는, 산소를 박막 표면뿐만 아니라 박막 내부에 첨가하는 것을 명확하게 한다는 취지로 사용한다. 또한, 산소 도핑에는, 플라즈마화한 산소를 벌크에 첨가하는 산소 플라즈마 도핑이 포함된다. 또한, 산소 도핑은 이온 주입법 또는 이온 도핑법을 사용하여 행하여도 좋다.

예를 들어, 산화물 반도체층(716)과 접하는 절연막으로서 산화 갈륨을 사용한 경우에는, 산소 분위기하에서의 가열 처리나 산소 도핑을 행함으로써 산화 갈륨의 조성을 Ga2Ox(X=3+α, 0<α<1)로 할 수 있다.

또한, 산화물 반도체층(716)과 접하는 절연막으로서 산화 알루미늄을 사용한 경우에는, 산소 분위기하에서의 가열 처리나 산소 도핑을 행함으로써 산화 알루미늄의 조성을 Al2Ox(X=3+α, 0<α<1)로 할 수 있다.

또한, 산화물 반도체층(716)과 접하는 절연막으로서 산화 갈륨 알루미늄(산화 알루미늄 갈륨)을 사용한 경우에는, 산소 분위기하에서의 가열 처리나 산소 도핑을 행함으로써, 산화 갈륨 알루미늄(산화 알루미늄 갈륨)의 조성을 GaxAl2 - xO3 +α(0<X<2, 0<α<1)로 할 수 있다.

산소 도핑 처리를 행함으로써, 화학량론적 조성보다 산소가 많은 영역을 갖는 절연막을 형성할 수 있다. 이와 같은 영역을 구비한 절연막과 산화물 반도체층이 접함으로써, 절연막 내의 과잉 산소가 산화물 반도체층에 공급되고 산화물 반도체층 내 또는 산화물 반도체층과 절연막의 계면에서의 산소 결함을 저감하여 산화물 반도체층을 i형화 또는 i형에 매우 가깝게 할 수 있다.

또한, 화학량론적 조성보다 산소가 많은 영역을 갖는 절연막은 산화물 반도체층(716)과 접하는 절연막 중, 위층에 위치하는 절연막 또는 아래층에 위치하는 절연막의 한쪽에만 사용하여도 좋지만, 양쪽 모두의 절연막에 사용하는 것이 바람직하다. 화학량론적 조성보다 산소가 많은 영역을 갖는 절연막을, 산화물 반도체층(716)과 접하는 절연막의 위층 및 아래층에 위치하는 절연막에 사용하여, 산화물 반도체층(716)을 끼우는 구성으로 함으로써 상기 효과를 보다 높일 수 있다.

또한, 산화물 반도체층(716) 위층 또는 아래층에 사용하는 절연막은 위층과 아래층에서 동일한 구성 원소를 갖는 절연막으로 하여도 좋고, 상이한 구성 원소를 갖는 절연막으로 하여도 좋다. 예를 들어, 위층과 아래층 모두, 조성이 Ga2Ox(X=3+α, 0<α<1)인 산화 갈륨으로 하여도 좋고, 위층과 아래층의 한쪽을 조성이 Ga2Ox(X=3+α, 0<α<1)인 산화 갈륨으로 하고, 다른 쪽을 조성이 Al2Ox(X=3+α, 0<α<1)인 산화 알루미늄으로 하여도 좋다.

또한, 산화물 반도체층(716)과 접하는 절연막은, 화학량론적 조성보다 산소가 많은 영역을 갖는 절연막의 적층으로 하여도 좋다. 예를 들어, 산화물 반도체층(716) 위층으로서 조성이 Ga2Ox(X=3+α, 0<α<1)인 산화 갈륨을 형성하고, 그 위에 조성이 GaxAl2 - xO3 +α(0<X<2, 0<α<1)인 산화 갈륨 알루미늄(산화 알루미늄 갈륨)을 형성하여도 좋다. 또한, 산화물 반도체층(716)의 아래층을, 화학량론적 조성보다 산소가 많은 영역을 갖는 절연막의 적층으로 하여도 좋고, 산화물 반도체층(716)의 위층 및 아래층의 양쪽을, 화학량론적 조성보다 산소가 많은 영역을 갖는 절연막의 적층으로 하여도 좋다.

다음에, 도 5c에 도시된 바와 같이, 게이트 절연막(721), 도전막(723), 게이트 전극(722)을 덮도록 절연막(724)을 형성한다. 절연막(724)은 PVD법이나 CVD법 등을 사용하여 형성할 수 있다. 또한, 산화 실리콘, 산화 질화 실리콘, 질화 실리콘, 산화 하프늄, 산화 갈륨, 산화 알루미늄 등의 무기 절연 재료를 함유하는 재료를 사용하여 형성할 수 있다. 절연막(724)에는 유전율이 낮은 재료나, 유전율이 낮은 구조(다공성의 구조 등)를 사용하는 것이 바람직하다. 절연막(724)의 유전율을 낮게 함으로써, 배선이나 전극 등 사이에 발생하는 기생 용량을 저감시켜 동작의 고속화를 도모할 수 있기 때문이다. 또한, 여기서는 절연막(724)을 단층 구조로 하였지만, 2층 이상의 적층 구조로 하여도 좋다.

다음에 게이트 절연막(721), 절연막(724)에 개구부(725)를 형성하고, 도전막(720)의 일부를 노출시킨다. 그 후에 절연막(724) 위에, 상기 개구부(725)에 있어서 도전막(720)과 접하는 배선(726)을 형성한다.

배선(726)은 PVD법이나 CVD법을 사용하여 도전막을 형성한 후, 상기 도전막을 에칭에 의하여 가공함으로써 형성된다. 또한 도전막의 재료로서는, 알루미늄, 크롬, 구리, 탄탈, 티타늄, 몰리브덴, 텅스텐으로부터 선택된 원소나, 상술한 원소를 성분으로 하는 합금 등을 사용할 수 있다. 망간, 마그네슘, 지르코늄, 베릴륨, 네오디뮴, 스칸듐 중 어느 하나, 또는 이들을 복수로 조합한 재료를 사용하여도 좋다.

보다 구체적으로는, 예를 들어, 절연막(724)의 개구부(725)를 포함하는 영역에 PVD법에 의하여 티타늄막을 얇게(5nm 정도) 형성한 후, 개구부(725)가 매립되도록 알루미늄막을 형성하는 방법을 적용할 수 있다. 여기서, PVD법에 의하여 형성되는 티타늄막은, 피형성면의 산화막(자연 산화막 등)을 환원하여 하부 전극 등(여기서는 도전막(720))과의 접촉 저항을 저감시키는 기능을 갖는다. 또한, 알루미늄막의 힐록을 방지할 수 있다. 또한, 티타늄이나 질화 티타늄 등을 사용하여 배리어막을 형성한 후에 도금법에 의하여 구리막을 형성하여도 좋다.

다음에 배선(726)을 덮도록 절연막(727)을 형성한다. 상술한 일련의 공정에 의하여, 도 2c에 도시된 메모리 셀(100)을 제작할 수 있다.

또한, 상기 제작 방법에서는 소스 전극 및 드레인 전극으로서 기능하는 도전막(719) 및 도전막(720)이 산화물 반도체층(716)을 형성한 후에 형성된다. 따라서, 도 5b에 도시된 바와 같이, 상기 제작 방법을 사용하여 얻어지는 트랜지스터(101)는 도전막(719) 및 도전막(720)이 산화물 반도체층(716) 위에 형성되어 있다. 그러나, 트랜지스터(101)는 소스 전극 및 드레인 전극으로서 기능하는 도전막이 산화물 반도체층(716) 아래, 즉 산화물 반도체층(716)과 절연막(712) 및 절연막(713) 사이에 제공되어 있어도 좋다.

도 6에 소스 전극 및 드레인 전극으로서 기능하는 도전막(719) 및 도전막(720)이, 산화물 반도체층(716)과 절연막(712) 및 절연막(713)의 사이에 제공되어 있는 경우의 트랜지스터(101)의 단면도를 도시하였다. 도 6에 도시된 트랜지스터(101)는 절연막(713)을 형성한 후에 도전막(719) 및 도전막(720)을 형성하고, 다음에, 산화물 반도체층(716)을 형성함으로써 얻을 수 있다.

<논리 회로부(12)의 구성예>

논리 회로부(12)는 복수의 로직 엘리먼트와, 로직 엘리먼트간의 배선으로 구성된다. 각 로직 엘리먼트의 기능을 변경함으로써 논리 회로부(12)의 기능은 변경할 수 있다. 또한, 로직 엘리먼트간의 배선의 전기적인 접속 관계를 변경함으로써 논리 회로부(12)의 기능을 변경할 수 있다.

로직 엘리먼트는, 예를 들어, 룩업 테이블(LUT)이나 멀티플렉서 등으로 구성되어 있다. 이 룩업 테이블의 데이터를 기억하는 기억 소자에 특정한 컨피규레이션 데이터를 설정함으로써 로직 엘리먼트의 기능을 특정할 수 있다. 또한, 이 멀티플렉서의 입력 신호의 선택 정보를 기억하는 기억 소자에 특정한 컨피규레이션 데이터를 설정함으로써 로직 엘리먼트의 기능을 특정할 수 있다.

로직 엘리먼트간의 배선은 예를 들어, 복수의 입력 단자 및 복수의 출력 단자를 갖는 접속 스위치(복수의 로직 엘리먼트와 복수의 로직 엘리먼트간에 제공되고, 전자 복수의 로직 엘리먼트로부터의 출력 신호의 각각이, 후자 복수의 로직 엘리먼트 중 어느 것에 입력되는지를 선택하는 접속 스위치) 등으로 구성되어 있다. 로직 엘리먼트간의 배선의 전기적인 접속 관계는 상기 접속 스위치의 도통·비도통의 데이터를 기억하는 기억 소자에 특정한 컨피규레이션 데이터를 설정함으로써 특정할 수 있다.

상기 접속 스위치는, 도 2b 내지 도 2e에 도시된 회로를 사용하여 구성할 수 있다. 예를 들어, 상기 접속 스위치로서 도 9에 도시된 스위치(600)를 적용할 수 있다.

<스위치(600)의 구성예>

스위치(600)는 논리 회로부(12)에서의 로직 엘리먼트(612)와 로직 엘리먼트(618)의 접속을 제어한다. 그리고, 도 9에 도시된 로직 엘리먼트(612), 로직 엘리먼트(618)는 각각 룩업 테이블(613), 룩업 테이블(619), 플립플롭(614), 플립플롭(620), AND 회로(615), AND 회로(621)로 구성되어 있다.

스위치(600)는 제 1 트랜지스터, 제 2 트랜지스터, 및 제 3 트랜지스터의 세트(set)를 3세트 갖는 회로로 구성된다. 제 1 트랜지스터에는 실리콘보다 밴드 갭이 넓고 진성 캐리어 밀도가 실리콘보다 낮은 반도체 재료를 사용한다. 제 1 트랜지스터로서 산화물 반도체를 채널 형성 영역에 사용한다. 한편, 제 2 트랜지스터 및 제 3 트랜지스터는, 예를 들어 실리콘 등의 반도체 재료를 채널 형성 영역에 사용한 제 1 트랜지스터보다 고속으로 스위칭이 가능한 트랜지스터를 사용하면 좋다. 여기서는, 제 2 트랜지스터 및 제 3 트랜지스터는 n형의 트랜지스터를 사용하기로 한다.

도 9에 도시된 바와 같이, 스위치(600)는 구체적으로 제 1 트랜지스터(601a, 601b, 601c)와, 제 2 트랜지스터(602a, 602b, 602c)와, 제 3 트랜지스터(608a, 608b, 608c)를 갖는다. 제 1 트랜지스터(601a, 601b, 601c)의 게이트는 각각 배선(606a, 606b, 606c)과 전기적으로 접속되어 있다. 배선(606a, 606b, 606c)에는 기록 신호가 입력된다. 또한, 제 1 트랜지스터(601a, 601b, 601c)의 소스는 공통의 배선(607)과 전기적으로 접속되어 있다. 배선(607)에는 기록 데이터 신호가 입력된다. 또한, 제 1 트랜지스터(601a, 601b, 601c)의 드레인은 각각 제 2 트랜지스터(602a, 602b, 602c)의 게이트와 전기적으로 접속되어 있다. 또한, 제 2 트랜지스터(602a, 602b, 602c)의 드레인은 제 3 트랜지스터(608a, 608b, 608c)의 소스와 각각 전기적으로 접속되어 있다. 따라서, 제 2 트랜지스터(602a, 602b, 602c)와 제 3 트랜지스터(608a, 608b, 608c)는 각각 전기적으로 직렬 접속되어 있다. 또한, 제 3 트랜지스터(608a, 608b, 608c)의 드레인은 서로 접속되어 있다. 또한, 제 2 트랜지스터(602a, 602b, 602c)의 소스는 배선(610)을 통하여 로직 엘리먼트(612)의 출력 단자에 전기적으로 접속되고, 제 3 트랜지스터(608a, 608b, 608c)의 드레인은 배선(611)을 통하여 로직 엘리먼트(618)의 입력 단자에 전기적으로 접속되어 있다. 여기서, 제 1 트랜지스터(601a, 601b, 601c)의 드레인과 제 2 트랜지스터(602a, 602b, 602c)의 게이트의 전기적인 접속 부위를 각각 노드(603a, 603b, 603c)로 한다. 상기 노드(603a, 603b, 603c)에 컨피규레이션 데이터를 기억시킬 수 있다.

상술한 바와 같이, 도 9에 도시된 스위치(600)는 제 1 트랜지스터, 제 2 트랜지스터, 및 제 3 트랜지스터의 3세트(630, 631, 632)로 구성된다.

로직 엘리먼트(612)는 배선(610)에 신호를 출력한다. 그리고, 상기 신호는 스위치(600)를 통하여 배선(611)에 공급되어 로직 엘리먼트(618)의 입력 신호가 된다.

배선(606a, 606b, 606c)의 전위를 “H(High)”로 하고, 배선(607)에 “H” 또는 “L(Low)”에 대응하는 전위를 공급하면, 노드(603a, 603b, 603c)에 배선(607)의 전위에 대응한 전하량을 축적할 수 있다. 또한, 이 때 배선(610), 배선(611) 중 적어도 한쪽은 “L”로 하는 것이 바람직하다.

여기서, 제 1 트랜지스터(601a, 601b, 601c)에 오프 전류가 극히 낮은 트랜지스터를 사용함으로써, 배선(606a, 606b, 606c)을 “L”로 하는 동안은 노드(603a, 603b, 603c)에 축적된 전하량을 일정하게 유지할 수 있다. 즉, 입력된 데이터를 기억시킬 수 있다. 또한, 배선(606a, 606b, 606c)을 “L”로 하고, 배선(605a, 605b, 605c)을 “H”로 하여 제 3 트랜지스터(608a, 608b, 608c)를 도통 상태로 함으로써 노드(603a, 603b, 603c)에 축적된 전하량에 따른 제 2 트랜지스터(602a, 602b, 602c)의 도통 상태가 스위치(600)의 도통 상태를 결정한다. 즉, 배선(605a, 605b, 605c) 중 어느 하나를 선택함으로써 노드(603a, 603b, 603c)에 축적된 전하량에 따라 스위치(600)의 도통 상태를 순식간에 전환할 수 있다.

여기서, 노드(603a, 603b, 603c)에 축적된 전하량을 컨피규레이션 데이터로서 기억할 수 있고, 배선(605a, 605b, 605c)의 전환에 따라 컨피규레이션 데이터를 전환할 수 있게 된다.

상술한 바와 같은 구성으로 함으로써, 복수의 컨피규레이션 데이터를 저장하는 기억 장치로부터의 판독에 필요한 시간을 삭감할 수 있다. 따라서, 컨피규레이션 데이터를 고속으로 전환할 수 있는 논리 회로부(12)를 제공할 수 있다.

(실시예 1)

본 발명의 일 형태에 따른 프로그래머블 LSI를 사용한 반도체 장치는 표시 장치, 퍼스널 컴퓨터, 기록 매체를 구비한 화상 재생 장치(대표적으로는 DVD: Digital Versatile Disc 등의 기록 매체를 재생하여 그 화상을 표시할 수 있는 디스플레이를 갖는 장치)에 사용할 수 있다. 그 외, 본 발명의 일 형태에 따른 프로그래머블 LSI를 사용한 반도체 장치로서, 휴대 전화, 게임기(휴대형을 포함함), 휴대 정보 단말, 전자 서적, 비디오 카메라나 디지털 스틸 카메라 등의 카메라, 고글형 디스플레이(헤드 장착형 디스플레이), 내비게이션 시스템, 음향 재생 장치(카 오디오, 디지털 오디오 플레이어 등), 복사기, 팩시밀리, 프린터, 프린터 복합기, 현금 자동 입출금기(ATM), 자동 판매기 등을 들 수 있다.

본 발명의 일 형태에 따른 프로그래머블 LSI를 사용한 반도체 장치를 휴대 전화, 스마트폰, 전자 서적 등 휴대용 전자 기기에 응용한 경우에 대하여 설명한다.

도 7은 휴대용 전자 기기의 블록도이다. 도 7에 도시된 휴대용 전자 기기는 RF 회로(421), 아날로그 베이스밴드 회로(422), 디지털 베이스밴드 회로(423), 배터리(424), 전원 회로(425), 애플리케이션 프로세서(426), 플래시 메모리(430), 디스플레이 컨트롤러(431), 메모리 회로(432), 디스플레이(433), 터치 센서(439), 음성 회로(437), 키보드(438) 등으로 구성되어 있다. 디스플레이(433)는 표시부(434), 소스 드라이버(435), 게이트 드라이버(436)로 구성되어 있다. 애플리케이션 프로세서(426)는 CPU(427), DSP(428), 인터페이스(IF)(429)를 갖는다. CPU(427)에 상술한 프로그래머블 LSI를 채용함으로써 동작 지연의 억제 및 소비 전력 저감의 양립을 도모할 수 있다.

도 8은 전자 서적의 블록도이다. 전자 서적은 배터리(451), 전원 회로(452), 마이크로 프로세서(453), 플래시 메모리(454), 음성 회로(455), 키보드(456), 메모리 회로(457), 터치 패널(458), 디스플레이(459), 디스플레이 컨트롤러(460)로 구성된다. 상술한 프로그래머블 LSI를 마이크로 프로세서(453)에 채용함으로써 동작 지연의 억제 및 소비 전력 저감의 양립을 도모할 수 있다.

1: 프로그래머블 LSI

2: 컴파일러

10: 뱅크군

11: 컨피규레이션 메모리

12: 논리 회로부

100: 메모리 셀

101: 트랜지스터

102: 트랜지스터

103: 트랜지스터

104: 커패시터

110: 입력 비트선

120: 출력 비트선

130: 입력 워드선

140: 출력 워드선

150: 기준 전위선

421: RF 회로

422: 아날로그 베이스밴드 회로

423: 디지털 베이스밴드 회로

424: 배터리

425: 전원 회로

426: 애플리케이션 프로세서

427: CPU

428: DSP

429: 인터페이스

430: 플래시 메모리

431: 디스플레이 컨트롤러

432: 메모리 회로

433: 디스플레이

434: 표시부

435: 소스 드라이버

436: 게이트 드라이버

437: 음성 회로

438: 키보드

439: 터치 센서

451: 배터리

452: 전원 회로

453: 마이크로 프로세서

454: 플래시 메모리

455: 음성 회로

456: 키보드

457: 메모리 회로

458: 터치 패널

459: 디스플레이

460: 디스플레이 컨트롤러

600: 스위치

601a: 트랜지스터

601b: 트랜지스터

601c: 트랜지스터

602a: 트랜지스터

602b: 트랜지스터

602c: 트랜지스터

603a: 노드

603b: 노드

603c: 노드

605a: 배선

605b: 배선

605c: 배선

606a: 배선

606b: 배선

606c: 배선

607: 배선

608a: 트랜지스터

608b: 트랜지스터

608c: 트랜지스터

610: 배선

611: 배선

612: 로직 엘리먼트

613: 룩업 테이블

614: 플립플롭

615: AND 회로

618: 로직 엘리먼트

619: 룩업 테이블

620: 플립플롭

621: AND 회로

630: 세트

631: 세트

632: 세트

700: 기판

701: 절연막

702: 반도체막

703: 게이트 절연막

707: 게이트 전극

709: 불순물 영역

710: 채널 형성 영역

712: 절연막

713: 절연막

716: 산화물 반도체층

719: 도전막

720: 도전막

721: 게이트 절연막

722: 게이트 전극

723: 도전막

724: 절연막

725: 개구부

726: 배선

727: 절연막

2: 컴파일러

10: 뱅크군

11: 컨피규레이션 메모리

12: 논리 회로부

100: 메모리 셀

101: 트랜지스터

102: 트랜지스터

103: 트랜지스터

104: 커패시터

110: 입력 비트선

120: 출력 비트선

130: 입력 워드선

140: 출력 워드선

150: 기준 전위선

421: RF 회로

422: 아날로그 베이스밴드 회로

423: 디지털 베이스밴드 회로

424: 배터리

425: 전원 회로

426: 애플리케이션 프로세서

427: CPU

428: DSP

429: 인터페이스

430: 플래시 메모리

431: 디스플레이 컨트롤러

432: 메모리 회로

433: 디스플레이

434: 표시부

435: 소스 드라이버

436: 게이트 드라이버

437: 음성 회로

438: 키보드

439: 터치 센서

451: 배터리

452: 전원 회로

453: 마이크로 프로세서

454: 플래시 메모리

455: 음성 회로

456: 키보드

457: 메모리 회로

458: 터치 패널

459: 디스플레이

460: 디스플레이 컨트롤러

600: 스위치

601a: 트랜지스터

601b: 트랜지스터

601c: 트랜지스터

602a: 트랜지스터

602b: 트랜지스터

602c: 트랜지스터

603a: 노드

603b: 노드

603c: 노드

605a: 배선

605b: 배선

605c: 배선

606a: 배선

606b: 배선

606c: 배선

607: 배선

608a: 트랜지스터

608b: 트랜지스터

608c: 트랜지스터

610: 배선

611: 배선

612: 로직 엘리먼트

613: 룩업 테이블

614: 플립플롭

615: AND 회로

618: 로직 엘리먼트

619: 룩업 테이블

620: 플립플롭

621: AND 회로

630: 세트

631: 세트

632: 세트

700: 기판

701: 절연막

702: 반도체막

703: 게이트 절연막

707: 게이트 전극

709: 불순물 영역

710: 채널 형성 영역

712: 절연막

713: 절연막

716: 산화물 반도체층

719: 도전막

720: 도전막

721: 게이트 절연막

722: 게이트 전극

723: 도전막

724: 절연막

725: 개구부

726: 배선

727: 절연막

Claims (26)

- 반도체 장치에 있어서,

프로그래머블 LSI로서,

논리 회로부;

상기 논리 회로부의 구성을 결정하는 컨피규레이션 데이터를 보유하는 컨피규레이션 메모리; 및

복수의 컨피규레이션 데이터를 저장하는 복수의 뱅크를 포함하는, 상기 프로그래머블 LSI와;

컴파일러를 포함하고,

상기 프로그래머블 LSI는 상기 논리 회로부가 동작하는 상태에서 제 1 동작 및 제 2 동작이 독립적으로 또 병행적으로 행해지도록 하고,

상기 제 1 동작에서, 상기 컴파일러로부터 공급되는 상기 복수의 컨피규레이션 데이터는 상기 복수의 뱅크에 저장되고,

상기 제 2 동작에서, 상기 컨피규레이션 메모리에 보유되는 컨피규레이션 데이터는 상기 복수의 뱅크에 저장된 상기 복수의 컨피규레이션 데이터 중 하나로 재기록되는, 반도체 장치. - 제1항에 있어서,

상기 프로그래머블 LSI는 뱅크군을 더 포함하고,

상기 뱅크군은 상기 복수의 컨피규레이션 데이터를 저장하는, 반도체 장치. - 반도체 장치에 있어서,

제 1 컨피규레이션 데이터에 의거한 제 1 구성을 갖는 논리 회로부와, 제 2 컨피규레이션 데이터를 보유하는 제 1 뱅크 및 제 3 컨피규레이션 데이터를 보유하는 제 2 뱅크를 적어도 포함하는 뱅크군을 포함하는 프로그래머블 LSI와;

타임 스케줄과 복수의 컨피규레이션 데이터를 생성하는 컴파일러를 포함하고,

상기 컴파일러는 상기 타임 스케줄에 의거하여 독립적으로 또 병행적으로 상기 복수의 컨피규레이션 데이터 중 하나를 상기 제 1 뱅크에 저장하고, 상기 제 3 컨피규레이션 데이터에 따라 상기 제 1 구성을 제 2 구성으로 재구성하고,

상기 뱅크군은 복수의 메모리 셀을 포함하고,

상기 메모리 셀들 각각은 입력 비트선, 출력 비트선, 입력 워드선, 출력 워드선, 기준 전위선, 제 1 트랜지스터, 제 2 트랜지스터, 및 제 3 트랜지스터를 포함하고,

상기 제 1 트랜지스터는 상기 입력 워드선과 전기적으로 접속되는 게이트와, 소스 및 드레인 중 한쪽이 상기 입력 비트선과 전기적으로 접속되는 상기 소스 및 드레인을 포함하고,

상기 제 2 트랜지스터는 상기 제 1 트랜지스터의 상기 소스 및 드레인 중 다른 쪽과 전기적으로 접속되는 게이트와, 소스 및 드레인 중 한쪽이 상기 기준 전위선과 전기적으로 접속되는 상기 소스 및 드레인을 포함하고,

상기 제 3 트랜지스터는 상기 출력 워드선과 전기적으로 접속되는 게이트와, 소스 및 드레인 중 한쪽이 상기 제 2 트랜지스터의 상기 소스 및 드레인 중 다른 쪽과 전기적으로 접속되고 상기 소스 및 드레인 중 다른 쪽이 상기 출력 비트선과 전기적으로 접속되는 상기 소스 및 드레인을 포함하는, 반도체 장치. - 제2항에 있어서,

상기 뱅크군은 복수의 메모리 셀을 포함하고,

상기 메모리 셀들 각각은 입력 비트선, 출력 비트선, 입력 워드선, 출력 워드선, 기준 전위선, 제 1 트랜지스터, 제 2 트랜지스터, 및 제 3 트랜지스터를 포함하는, 반도체 장치. - 제4항에 있어서,

상기 제 1 트랜지스터는 상기 입력 워드선과 전기적으로 접속되는 게이트와, 소스 및 드레인 중 한쪽이 상기 입력 비트선과 전기적으로 접속되는 상기 소스 및 드레인을 포함하고,

상기 제 2 트랜지스터는 상기 제 1 트랜지스터의 상기 소스 및 드레인 중 다른 쪽과 전기적으로 접속되는 게이트와, 소스 및 드레인 중 한쪽이 상기 기준 전위선과 전기적으로 접속되는 상기 소스 및 드레인을 포함하고,

상기 제 3 트랜지스터는 상기 출력 워드선과 전기적으로 접속되는 게이트와, 소스 및 드레인 중 한쪽이 상기 제 2 트랜지스터의 상기 소스 및 드레인 중 다른 쪽과 전기적으로 접속되고 상기 소스 및 드레인 중 다른 쪽이 상기 출력 비트선과 전기적으로 접속되는 상기 소스 및 드레인을 포함하는, 반도체 장치. - 제4항에 있어서,

커패시터를 더 포함하고,

상기 제 1 트랜지스터는 상기 입력 워드선과 전기적으로 접속되는 게이트와, 소스 및 드레인 중 한쪽이 상기 입력 비트선과 전기적으로 접속되는 상기 소스 및 드레인을 포함하고,

상기 제 2 트랜지스터는 상기 제 1 트랜지스터의 상기 소스 및 드레인 중 다른 쪽 및 상기 커패시터의 한 쌍의 전극 중 하나와 전기적으로 접속되는 게이트와, 소스 및 드레인 중 한쪽이 상기 기준 전위선과 전기적으로 접속되는 상기 소스 및 드레인을 포함하고,

상기 제 3 트랜지스터는 상기 출력 워드선과 전기적으로 접속되는 게이트와, 소스 및 드레인 중 한쪽이 상기 제 2 트랜지스터의 상기 소스 및 드레인 중 다른 쪽과 전기적으로 접속되고 상기 소스 및 드레인 중 다른 쪽이 상기 출력 비트선과 전기적으로 접속되는 상기 소스 및 드레인을 포함하는, 반도체 장치. - 제4항에 있어서,

상기 제 1 트랜지스터는 상기 입력 워드선과 전기적으로 접속되는 게이트와, 소스 및 드레인 중 한쪽이 상기 입력 비트선과 전기적으로 접속되는 상기 소스 및 드레인을 포함하고,

상기 제 2 트랜지스터는 상기 출력 워드선과 전기적으로 접속되는 게이트와, 소스 및 드레인 중 한쪽이 상기 기준 전위선과 전기적으로 접속되는 상기 소스 및 드레인을 포함하고,

상기 제 3 트랜지스터는 상기 제 1 트랜지스터의 상기 소스 및 드레인 중 다른 쪽과 전기적으로 접속되는 게이트와, 소스 및 드레인 중 한쪽이 상기 제 2 트랜지스터의 상기 소스 및 드레인 중 다른 쪽과 전기적으로 접속되고 상기 소스 및 드레인 중 다른 쪽이 상기 출력 비트선과 전기적으로 접속되는 상기 소스 및 드레인을 포함하는, 반도체 장치. - 제4항에 있어서,

커패시터를 더 포함하고,

상기 제 1 트랜지스터는 상기 입력 워드선과 전기적으로 접속되는 게이트와, 소스 및 드레인 중 한쪽이 상기 입력 비트선과 전기적으로 접속되는 상기 소스 및 드레인을 포함하고,

상기 제 2 트랜지스터는 상기 출력 워드선과 전기적으로 접속되는 게이트와, 소스 및 드레인 중 한쪽이 상기 기준 전위선과 전기적으로 접속되는 상기 소스 및 드레인을 포함하고,

상기 제 3 트랜지스터는 상기 제 1 트랜지스터의 상기 소스 및 드레인 중 다른 쪽 및 상기 커패시터의 한 쌍의 전극 중 하나와 전기적으로 접속되는 게이트와, 소스 및 드레인 중 한쪽이 상기 제 2 트랜지스터의 상기 소스 및 드레인 중 다른 쪽과 전기적으로 접속되고 상기 소스 및 드레인 중 다른 쪽이 상기 출력 비트선과 전기적으로 접속되는 상기 소스 및 드레인을 포함하는, 반도체 장치. - 제4항에 있어서,

상기 제 1 트랜지스터, 상기 제 2 트랜지스터, 및 상기 제 3 트랜지스터 중 적어도 하나는 채널을 갖는 산화물 반도체층을 포함하는, 반도체 장치. - 제4항에 있어서,

상기 메모리 셀들 각각은 다치화된 데이터를 저장하는, 반도체 장치. - 논리 회로부를 포함하는 프로그래머블 LSI와 컴파일러를 포함하는 반도체 장치의 구동 방법에 있어서,

타임 스케줄과 복수의 컨피규레이션 데이터를 생성하는 단계와;

독립적으로 또 병행적으로 상기 타임 스케줄에 의거하여 상기 복수의 컨피규레이션 데이터 각각에 따라 상기 논리 회로부의 구성을 재구성하고, 상기 프로그래머블 LSI에 상기 컨피규레이션 데이터를 저장하는 단계를 포함하고,

상기 프로그래머블 LSI는 뱅크군을 더 포함하고,

상기 뱅크군은 상기 복수의 컨피규레이션 데이터를 저장하고,

상기 뱅크군은 복수의 메모리 셀을 포함하고,

상기 메모리 셀들 각각은 입력 비트선, 출력 비트선, 입력 워드선, 출력 워드선, 기준 전위선, 제 1 트랜지스터, 제 2 트랜지스터, 및 제 3 트랜지스터를 포함하고,

상기 제 1 트랜지스터는 상기 입력 워드선과 전기적으로 접속되는 게이트와, 소스 및 드레인 중 한쪽이 상기 입력 비트선과 전기적으로 접속되는 상기 소스 및 드레인을 포함하고,

상기 제 2 트랜지스터는 상기 제 1 트랜지스터의 상기 소스 및 드레인 중 다른 쪽과 전기적으로 접속되는 게이트와, 소스 및 드레인 중 한쪽이 상기 기준 전위선과 전기적으로 접속되는 상기 소스 및 드레인을 포함하고,

상기 제 3 트랜지스터는 상기 출력 워드선과 전기적으로 접속되는 게이트와, 소스 및 드레인 중 한쪽이 상기 제 2 트랜지스터의 상기 소스 및 드레인 중 다른 쪽과 전기적으로 접속되고 상기 소스 및 드레인 중 다른 쪽이 상기 출력 비트선과 전기적으로 접속되는 상기 소스 및 드레인을 포함하는, 반도체 장치의 구동 방법. - 삭제

- 삭제

- 삭제

- 삭제

- 삭제

- 삭제

- 제11항에 있어서,

상기 제 1 트랜지스터, 상기 제 2 트랜지스터, 및 상기 제 3 트랜지스터 중 적어도 하나는 채널을 갖는 산화물 반도체층을 포함하는, 반도체 장치의 구동 방법. - 제11항에 있어서,

상기 메모리 셀들 각각은 다치화된 데이터를 저장하는, 반도체 장치의 구동 방법. - 삭제

- 삭제

- 삭제

- 삭제

- 삭제

- 삭제

- 삭제

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2012102014 | 2012-04-27 | ||

| JPJP-P-2012-102014 | 2012-04-27 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR20130121730A KR20130121730A (ko) | 2013-11-06 |

| KR102047553B1 true KR102047553B1 (ko) | 2019-11-21 |

Family

ID=49323418

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020130045208A KR102047553B1 (ko) | 2012-04-27 | 2013-04-24 | 프로그래머블 lsi |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US9654107B2 (ko) |

| JP (1) | JP6144098B2 (ko) |

| KR (1) | KR102047553B1 (ko) |

| DE (1) | DE102013207217A1 (ko) |

Families Citing this family (35)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN104247268B (zh) | 2012-05-02 | 2016-10-12 | 株式会社半导体能源研究所 | 可编程逻辑器件 |

| CN104321967B (zh) | 2012-05-25 | 2018-01-09 | 株式会社半导体能源研究所 | 可编程逻辑装置及半导体装置 |

| JP6377317B2 (ja) | 2012-05-30 | 2018-08-22 | 株式会社半導体エネルギー研究所 | プログラマブルロジックデバイス |

| KR102102589B1 (ko) | 2012-10-17 | 2020-04-22 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 프로그램 가능한 논리 장치 |

| JP6254834B2 (ja) | 2012-12-06 | 2017-12-27 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| TWI611419B (zh) * | 2012-12-24 | 2018-01-11 | 半導體能源研究所股份有限公司 | 可程式邏輯裝置及半導體裝置 |

| US8952723B2 (en) | 2013-02-13 | 2015-02-10 | Semiconductor Energy Laboratory Co., Ltd. | Programmable logic device and semiconductor device |

| KR102125593B1 (ko) | 2013-02-13 | 2020-06-22 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 프로그래머블 로직 디바이스 및 반도체 장치 |

| US8947121B2 (en) | 2013-03-12 | 2015-02-03 | Semiconductor Energy Laboratory Co., Ltd. | Programmable logic device |

| JP6272713B2 (ja) | 2013-03-25 | 2018-01-31 | 株式会社半導体エネルギー研究所 | プログラマブルロジックデバイス及び半導体装置 |

| TWI621337B (zh) | 2013-05-14 | 2018-04-11 | 半導體能源研究所股份有限公司 | 信號處理裝置 |

| TWI638519B (zh) | 2013-05-17 | 2018-10-11 | 半導體能源研究所股份有限公司 | 可程式邏輯裝置及半導體裝置 |

| JP6368155B2 (ja) | 2013-06-18 | 2018-08-01 | 株式会社半導体エネルギー研究所 | プログラマブルロジックデバイス |

| JP6352070B2 (ja) | 2013-07-05 | 2018-07-04 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| JP6483402B2 (ja) | 2013-11-01 | 2019-03-13 | 株式会社半導体エネルギー研究所 | 記憶装置、及び記憶装置を有する電子機器 |

| JP6478562B2 (ja) | 2013-11-07 | 2019-03-06 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| JP6393590B2 (ja) | 2013-11-22 | 2018-09-19 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| JP6444723B2 (ja) | 2014-01-09 | 2018-12-26 | 株式会社半導体エネルギー研究所 | 装置 |

| US9379713B2 (en) | 2014-01-17 | 2016-06-28 | Semiconductor Energy Laboratory Co., Ltd. | Data processing device and driving method thereof |

| JP6521643B2 (ja) | 2014-01-24 | 2019-05-29 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| JP6473626B2 (ja) | 2014-02-06 | 2019-02-20 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| JP2015165226A (ja) | 2014-02-07 | 2015-09-17 | 株式会社半導体エネルギー研究所 | 装置 |

| US9869716B2 (en) | 2014-02-07 | 2018-01-16 | Semiconductor Energy Laboratory Co., Ltd. | Device comprising programmable logic element |

| WO2015118436A1 (en) | 2014-02-07 | 2015-08-13 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device, device, and electronic device |

| JP6442321B2 (ja) | 2014-03-07 | 2018-12-19 | 株式会社半導体エネルギー研究所 | 半導体装置及びその駆動方法、並びに電子機器 |

| JP6541376B2 (ja) | 2014-03-13 | 2019-07-10 | 株式会社半導体エネルギー研究所 | プログラマブルロジックデバイスの動作方法 |

| JP6677449B2 (ja) * | 2014-03-13 | 2020-04-08 | 株式会社半導体エネルギー研究所 | 半導体装置の駆動方法 |

| TWI643457B (zh) | 2014-04-25 | 2018-12-01 | 日商半導體能源研究所股份有限公司 | 半導體裝置 |

| JP6645793B2 (ja) | 2014-10-17 | 2020-02-14 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| WO2016092416A1 (en) * | 2014-12-11 | 2016-06-16 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device, memory device, and electronic device |

| JP2017102904A (ja) * | 2015-10-23 | 2017-06-08 | 株式会社半導体エネルギー研究所 | 半導体装置および電子機器 |

| KR102643895B1 (ko) | 2015-10-30 | 2024-03-05 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치, 전자 부품, 및 전자 기기 |

| KR20180081732A (ko) | 2015-11-13 | 2018-07-17 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치, 전자 부품, 및 전자 기기 |

| US9998119B2 (en) | 2016-05-20 | 2018-06-12 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device, electronic component, and electronic device |

| DE112017004148T5 (de) | 2016-08-19 | 2019-05-23 | Semiconductor Energy Laboratory Co., Ltd. | Verfahren zum Steuern der Stromzufuhr in einer Halbleitervorrichtung |

Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2008152697A1 (ja) * | 2007-06-12 | 2008-12-18 | Fujitsu Limited | コンフィグレーション装置 |

| JP2011119713A (ja) * | 2009-11-06 | 2011-06-16 | Semiconductor Energy Lab Co Ltd | 半導体装置 |

Family Cites Families (35)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4870302A (en) | 1984-03-12 | 1989-09-26 | Xilinx, Inc. | Configurable electrical circuit having configurable logic elements and configurable interconnects |

| US4609986A (en) | 1984-06-14 | 1986-09-02 | Altera Corporation | Programmable logic array device using EPROM technology |

| US4642487A (en) | 1984-09-26 | 1987-02-10 | Xilinx, Inc. | Special interconnect for configurable logic array |

| JPH0563551A (ja) | 1991-08-29 | 1993-03-12 | Kawasaki Steel Corp | プログラマブル論理回路装置 |

| JP4103968B2 (ja) | 1996-09-18 | 2008-06-18 | 株式会社半導体エネルギー研究所 | 絶縁ゲイト型半導体装置 |

| JP3106998B2 (ja) | 1997-04-11 | 2000-11-06 | 日本電気株式会社 | メモリ付加型プログラマブルロジックlsi |

| US6959378B2 (en) * | 2000-11-06 | 2005-10-25 | Broadcom Corporation | Reconfigurable processing system and method |

| JP2003122638A (ja) * | 2001-10-18 | 2003-04-25 | Fujitsu Ltd | 半導体集積回路装置 |

| US7221586B2 (en) * | 2002-07-08 | 2007-05-22 | Micron Technology, Inc. | Memory utilizing oxide nanolaminates |

| US7088606B2 (en) * | 2004-03-10 | 2006-08-08 | Altera Corporation | Dynamic RAM storage techniques |

| ITMI20041675A1 (it) * | 2004-08-30 | 2004-11-30 | St Microelectronics Srl | Blocco di commutazione e relativa matrice di commutazione, in particolare per architetture fpga. |

| JP2006287675A (ja) | 2005-04-01 | 2006-10-19 | Renesas Technology Corp | 半導体集積回路 |

| US7793040B2 (en) * | 2005-06-01 | 2010-09-07 | Microsoft Corporation | Content addressable memory architecture |

| EP1770788A3 (en) | 2005-09-29 | 2011-09-21 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device having oxide semiconductor layer and manufacturing method thereof |

| JP2007251329A (ja) | 2006-03-14 | 2007-09-27 | Matsushita Electric Ind Co Ltd | プログラマブルロジックデバイス |

| JP4866194B2 (ja) | 2006-09-29 | 2012-02-01 | 富士通セミコンダクター株式会社 | 集積回路及びリコンフィギュラブル回路の入力データ制御方法 |

| JP2008152409A (ja) | 2006-12-15 | 2008-07-03 | Renesas Technology Corp | 半導体集積回路 |

| EP2201569A4 (en) * | 2007-09-06 | 2011-07-13 | Tabula Inc | CONFIGURATION CONTEXT SWITCH |

| JP2009129046A (ja) * | 2007-11-21 | 2009-06-11 | Panasonic Corp | リコンフィギュラブル回路,リコンフィギュラブル回路の機能変更方法および通信装置 |

| JP5781720B2 (ja) | 2008-12-15 | 2015-09-24 | ルネサスエレクトロニクス株式会社 | 半導体装置及び半導体装置の製造方法 |

| KR101581882B1 (ko) * | 2009-04-20 | 2015-12-31 | 삼성전자주식회사 | 재구성 가능한 프로세서 및 그 재구성 방법 |

| US8359448B1 (en) * | 2009-07-17 | 2013-01-22 | Xilinx, Inc. | Specific memory controller implemented using reconfiguration |

| IN2012DN05920A (ko) | 2010-01-20 | 2015-09-18 | Semiconductor Energy Lab | |

| US8952721B2 (en) | 2010-06-24 | 2015-02-10 | Taiyo Yuden Co., Ltd. | Semiconductor device |

| KR20120036208A (ko) * | 2010-10-07 | 2012-04-17 | 삼성전자주식회사 | 재구성 기반 컴퓨팅 장치 및 이의 메모리 의존성 보정방법 |

| KR101899880B1 (ko) | 2011-02-17 | 2018-09-18 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 프로그래머블 lsi |

| US8542032B1 (en) * | 2012-01-06 | 2013-09-24 | Altera Corporation | Integrated circuits with interconnect selection circuitry |

| JP5613694B2 (ja) | 2012-01-19 | 2014-10-29 | ユーオーピー エルエルシー | 結晶性アルミノシリケートゼオライト質組成物:uzm−15 |

| JP6125850B2 (ja) | 2012-02-09 | 2017-05-10 | 株式会社半導体エネルギー研究所 | 半導体装置及び半導体装置の作製方法 |

| CN104247268B (zh) | 2012-05-02 | 2016-10-12 | 株式会社半导体能源研究所 | 可编程逻辑器件 |

| JP6377317B2 (ja) | 2012-05-30 | 2018-08-22 | 株式会社半導体エネルギー研究所 | プログラマブルロジックデバイス |

| JP2014030110A (ja) * | 2012-07-31 | 2014-02-13 | Toshiba Corp | リコンフィギャラブル集積回路装置およびその書き込み方法 |

| US9323544B2 (en) * | 2013-10-09 | 2016-04-26 | International Business Machines Corporation | Dynamic reconfiguration of queue pairs |

| US9727460B2 (en) * | 2013-11-01 | 2017-08-08 | Samsung Electronics Co., Ltd. | Selecting a memory mapping scheme by determining a number of functional units activated in each cycle of a loop based on analyzing parallelism of a loop |

| KR102149509B1 (ko) * | 2014-03-27 | 2020-08-28 | 삼성전자주식회사 | 구성 데이터를 압축 및 복원하는 방법 |

-

2013

- 2013-04-17 US US13/864,461 patent/US9654107B2/en active Active

- 2013-04-22 DE DE102013207217A patent/DE102013207217A1/de not_active Withdrawn

- 2013-04-24 KR KR1020130045208A patent/KR102047553B1/ko active IP Right Grant

- 2013-04-25 JP JP2013091916A patent/JP6144098B2/ja not_active Expired - Fee Related

Patent Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2008152697A1 (ja) * | 2007-06-12 | 2008-12-18 | Fujitsu Limited | コンフィグレーション装置 |

| JP2011119713A (ja) * | 2009-11-06 | 2011-06-16 | Semiconductor Energy Lab Co Ltd | 半導体装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| KR20130121730A (ko) | 2013-11-06 |

| US9654107B2 (en) | 2017-05-16 |

| JP6144098B2 (ja) | 2017-06-07 |

| US20130285697A1 (en) | 2013-10-31 |

| DE102013207217A1 (de) | 2013-10-31 |

| JP2013243657A (ja) | 2013-12-05 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR102047553B1 (ko) | 프로그래머블 lsi | |

| KR101899881B1 (ko) | 프로그래머블 lsi | |

| KR102058823B1 (ko) | 반도체 장치 | |

| JP7038238B2 (ja) | 半導体装置 | |

| US9818749B2 (en) | Storage element, storage device, and signal processing circuit | |

| KR101929770B1 (ko) | 기억 회로, 기억 장치, 신호 처리 회로 | |

| KR101932577B1 (ko) | 반도체 장치 | |

| KR20200013756A (ko) | 반도체 장치 및 반도체 장치의 제작 방법 | |

| JP2018137452A (ja) | 半導体装置 | |

| KR20120075411A (ko) | 신호 처리 회로 | |

| KR20120082823A (ko) | 기억 소자, 기억 장치, 신호 처리 회로, 기억 소자의 구동 방법 | |

| KR20130062237A (ko) | 반도체 장치 및 반도체 장치의 제작 방법 | |

| US8730730B2 (en) | Temporary storage circuit, storage device, and signal processing circuit |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A201 | Request for examination | ||

| E902 | Notification of reason for refusal | ||

| E701 | Decision to grant or registration of patent right |