JP7068676B2 - Iiia-n族デバイスのための非エッチ気体冷却エピタキシャルスタック - Google Patents

Iiia-n族デバイスのための非エッチ気体冷却エピタキシャルスタック Download PDFInfo

- Publication number

- JP7068676B2 JP7068676B2 JP2018534035A JP2018534035A JP7068676B2 JP 7068676 B2 JP7068676 B2 JP 7068676B2 JP 2018534035 A JP2018534035 A JP 2018534035A JP 2018534035 A JP2018534035 A JP 2018534035A JP 7068676 B2 JP7068676 B2 JP 7068676B2

- Authority

- JP

- Japan

- Prior art keywords

- iiia

- cap layer

- group

- layer

- deposition

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02518—Deposited layers

- H01L21/02521—Materials

- H01L21/02538—Group 13/15 materials

- H01L21/0254—Nitrides

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02367—Substrates

- H01L21/0237—Materials

- H01L21/02373—Group 14 semiconducting materials

- H01L21/02381—Silicon, silicon germanium, germanium

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02436—Intermediate layers between substrates and deposited layers

- H01L21/02439—Materials

- H01L21/02455—Group 13/15 materials

- H01L21/02458—Nitrides

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02436—Intermediate layers between substrates and deposited layers

- H01L21/02494—Structure

- H01L21/02496—Layer structure

- H01L21/02502—Layer structure consisting of two layers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02612—Formation types

- H01L21/02617—Deposition types

- H01L21/0262—Reduction or decomposition of gaseous compounds, e.g. CVD

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

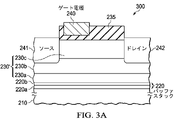

- H10D30/00—Field-effect transistors [FET]

- H10D30/40—FETs having zero-dimensional [0D], one-dimensional [1D] or two-dimensional [2D] charge carrier gas channels

- H10D30/47—FETs having zero-dimensional [0D], one-dimensional [1D] or two-dimensional [2D] charge carrier gas channels having 2D charge carrier gas channels, e.g. nanoribbon FETs or high electron mobility transistors [HEMT]

- H10D30/471—High electron mobility transistors [HEMT] or high hole mobility transistors [HHMT]

- H10D30/475—High electron mobility transistors [HEMT] or high hole mobility transistors [HHMT] having wider bandgap layer formed on top of lower bandgap active layer, e.g. undoped barrier HEMTs such as i-AlGaN/GaN HEMTs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D62/00—Semiconductor bodies, or regions thereof, of devices having potential barriers

- H10D62/80—Semiconductor bodies, or regions thereof, of devices having potential barriers characterised by the materials

- H10D62/85—Semiconductor bodies, or regions thereof, of devices having potential barriers characterised by the materials being Group III-V materials, e.g. GaAs

- H10D62/8503—Nitride Group III-V materials, e.g. AlN or GaN

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D64/00—Electrodes of devices having potential barriers

- H10D64/60—Electrodes characterised by their materials

- H10D64/602—Heterojunction gate electrodes for FETs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/01—Manufacture or treatment

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/01—Manufacture or treatment

- H10D84/02—Manufacture or treatment characterised by using material-based technologies

- H10D84/05—Manufacture or treatment characterised by using material-based technologies using Group III-V technology

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/80—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers characterised by the integration of at least one component covered by groups H10D12/00 or H10D30/00, e.g. integration of IGFETs

- H10D84/82—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers characterised by the integration of at least one component covered by groups H10D12/00 or H10D30/00, e.g. integration of IGFETs of only field-effect components

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D62/00—Semiconductor bodies, or regions thereof, of devices having potential barriers

- H10D62/10—Shapes, relative sizes or dispositions of the regions of the semiconductor bodies; Shapes of the semiconductor bodies

- H10D62/17—Semiconductor regions connected to electrodes not carrying current to be rectified, amplified or switched, e.g. channel regions

- H10D62/343—Gate regions of field-effect devices having PN junction gates

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/80—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers characterised by the integration of at least one component covered by groups H10D12/00 or H10D30/00, e.g. integration of IGFETs

- H10D84/82—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers characterised by the integration of at least one component covered by groups H10D12/00 or H10D30/00, e.g. integration of IGFETs of only field-effect components

- H10D84/83—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers characterised by the integration of at least one component covered by groups H10D12/00 or H10D30/00, e.g. integration of IGFETs of only field-effect components of only insulated-gate FETs [IGFET]

- H10D84/84—Combinations of enhancement-mode IGFETs and depletion-mode IGFETs

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Manufacturing & Machinery (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Chemical & Material Sciences (AREA)

- Materials Engineering (AREA)

- Junction Field-Effect Transistors (AREA)

- Insulated Gate Type Field-Effect Transistor (AREA)

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US14/981,348 US10529561B2 (en) | 2015-12-28 | 2015-12-28 | Method of fabricating non-etch gas cooled epitaxial stack for group IIIA-N devices |

| US14/981,348 | 2015-12-28 | ||

| PCT/US2016/069051 WO2017117315A1 (en) | 2015-12-28 | 2016-12-28 | Non-etch gas cooled epitaxial stack for group iiia-n devices |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2019500755A JP2019500755A (ja) | 2019-01-10 |

| JP2019500755A5 JP2019500755A5 (enExample) | 2020-02-06 |

| JP7068676B2 true JP7068676B2 (ja) | 2022-05-17 |

Family

ID=59086639

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2018534035A Active JP7068676B2 (ja) | 2015-12-28 | 2016-12-28 | Iiia-n族デバイスのための非エッチ気体冷却エピタキシャルスタック |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US10529561B2 (enExample) |

| EP (1) | EP3398203A4 (enExample) |

| JP (1) | JP7068676B2 (enExample) |

| CN (1) | CN108352324B (enExample) |

| WO (1) | WO2017117315A1 (enExample) |

Families Citing this family (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20190288089A9 (en) * | 2015-12-28 | 2019-09-19 | Texas Instruments Incorporated | Methods for transistor epitaxial stack fabrication |

| EP3655989A1 (en) * | 2017-07-20 | 2020-05-27 | Swegan AB | A heterostructure for a high electron mobility transistor and a method of producing the same |

| CN108417488B (zh) * | 2018-03-15 | 2021-04-06 | 吉林大学 | 一种复合绝缘结构、晶体管以及复合绝缘结构和晶体管的制作方法 |

| US11742390B2 (en) | 2020-10-30 | 2023-08-29 | Texas Instruments Incorporated | Electronic device with gallium nitride transistors and method of making same |

| CN113638043B (zh) * | 2021-08-16 | 2022-06-03 | 季华实验室 | 外延炉吹扫冷却系统、方法、装置、电子设备及存储介质 |

| CN114864380B (zh) * | 2022-04-22 | 2025-02-21 | 江苏第三代半导体研究院有限公司 | 降低裂纹的外延方法及其外延片 |

Citations (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2001320084A (ja) | 2000-03-02 | 2001-11-16 | Ricoh Co Ltd | Iii族窒化物半導体およびその作製方法および半導体装置 |

| JP2003031845A (ja) | 2001-04-30 | 2003-01-31 | Lumileds Lighting Us Llc | 低抵抗率p型窒化ガリウムの形成 |

| JP2007184353A (ja) | 2006-01-05 | 2007-07-19 | Matsushita Electric Ind Co Ltd | 窒化物系化合物半導体素子の製造方法、および、窒化物系化合物半導体素子 |

| JP2008098603A (ja) | 2006-09-15 | 2008-04-24 | Sumitomo Chemical Co Ltd | 半導体エピタキシャル結晶基板の製造方法 |

| JP2013074209A (ja) | 2011-09-28 | 2013-04-22 | Fujitsu Ltd | 半導体装置の製造方法及び半導体装置 |

| JP2014197645A (ja) | 2013-03-29 | 2014-10-16 | 富士通株式会社 | 化合物半導体装置及びその製造方法 |

| JP2015185809A (ja) | 2014-03-26 | 2015-10-22 | 住友電気工業株式会社 | 半導体基板の製造方法及び半導体装置 |

| JP2015192026A (ja) | 2014-03-28 | 2015-11-02 | 住友電気工業株式会社 | 半導体装置の製造方法 |

Family Cites Families (32)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0964477A (ja) * | 1995-08-25 | 1997-03-07 | Toshiba Corp | 半導体発光素子及びその製造方法 |

| WO1999066565A1 (en) * | 1998-06-18 | 1999-12-23 | University Of Florida | Method and apparatus for producing group-iii nitrides |

| CN1131547C (zh) * | 1999-09-28 | 2003-12-17 | 晶元光电股份有限公司 | 半导体的制造方法 |

| US6495867B1 (en) | 2000-07-26 | 2002-12-17 | Axt, Inc. | InGaN/AlGaN/GaN multilayer buffer for growth of GaN on sapphire |

| JP2002164571A (ja) * | 2000-11-22 | 2002-06-07 | Otts:Kk | 窒化ガリウム系化合物半導体およびその製造方法 |

| JP2002175994A (ja) * | 2000-12-08 | 2002-06-21 | Otts:Kk | 窒化ガリウム系化合物半導体の製造方法 |

| WO2005022655A1 (en) * | 2003-09-03 | 2005-03-10 | Epivalley Co., Ltd. | Algainn based optical device and fabrication method thereof |

| JP2005340762A (ja) * | 2004-04-28 | 2005-12-08 | Showa Denko Kk | Iii族窒化物半導体発光素子 |

| JP2008527687A (ja) * | 2004-12-30 | 2008-07-24 | オーミック ソシエテ パール アクション サンプリフィエ | エンハンスメント−デプレッション半導体構造及びその製造方法 |

| JP2006324465A (ja) * | 2005-05-19 | 2006-11-30 | Matsushita Electric Ind Co Ltd | 半導体装置及びその製造方法 |

| US20070018198A1 (en) * | 2005-07-20 | 2007-01-25 | Brandes George R | High electron mobility electronic device structures comprising native substrates and methods for making the same |

| US8435879B2 (en) * | 2005-12-12 | 2013-05-07 | Kyma Technologies, Inc. | Method for making group III nitride articles |

| JP2007189028A (ja) * | 2006-01-12 | 2007-07-26 | Hitachi Cable Ltd | p型窒化ガリウム系半導体の製造方法及びAlGaInN系発光素子の製造方法 |

| KR101502195B1 (ko) * | 2007-11-21 | 2015-03-12 | 미쓰비시 가가꾸 가부시키가이샤 | 질화물 반도체 및 질화물 반도체의 결정 성장 방법 그리고 질화물 반도체 발광 소자 |

| CN101359710B (zh) * | 2008-09-25 | 2011-12-28 | 上海蓝光科技有限公司 | 一种绿光发光二极管的制造方法 |

| WO2010141943A1 (en) * | 2009-06-05 | 2010-12-09 | The Regents Of The University Of California | LONG WAVELENGTH NONPOLAR AND SEMIPOLAR (Al,Ga,In)N BASED LASER DIODES |

| CN102414846A (zh) | 2009-10-07 | 2012-04-11 | 应用材料公司 | 用于led制造的改良多腔室分离处理 |

| US20110169138A1 (en) | 2009-11-03 | 2011-07-14 | The Regents Of The University Of California | TECHNIQUES FOR ACHIEVING LOW RESISTANCE CONTACTS TO NONPOLAR AND SEMIPOLAR P-TYPE (Al,Ga,In)N |

| CN102714162B (zh) | 2009-11-04 | 2015-04-29 | 同和电子科技有限公司 | 第iii族氮化物外延层压基板 |

| US8541817B2 (en) | 2009-11-06 | 2013-09-24 | Nitek, Inc. | Multilayer barrier III-nitride transistor for high voltage electronics |

| US8629531B2 (en) * | 2011-02-18 | 2014-01-14 | Taiwan Semiconductor Manufacturing Company, Ltd. | Structure and method to reduce wafer warp for gallium nitride on silicon wafer |

| US8778783B2 (en) * | 2011-05-20 | 2014-07-15 | Applied Materials, Inc. | Methods for improved growth of group III nitride buffer layers |

| JP2014520748A (ja) * | 2011-06-27 | 2014-08-25 | サン‐ゴバン、クリストー、エ、デテクトゥール | 半導体基板及び製造方法 |

| JP2013058741A (ja) | 2011-08-17 | 2013-03-28 | Hitachi Cable Ltd | 金属塩化物ガス発生装置、ハイドライド気相成長装置、及び窒化物半導体テンプレート |

| JP5879225B2 (ja) * | 2011-08-22 | 2016-03-08 | 住友化学株式会社 | 窒化物半導体テンプレート及び発光ダイオード |

| JP5558454B2 (ja) * | 2011-11-25 | 2014-07-23 | シャープ株式会社 | 窒化物半導体発光素子および窒化物半導体発光素子の製造方法 |

| JP5883331B2 (ja) * | 2012-01-25 | 2016-03-15 | 住友化学株式会社 | 窒化物半導体エピタキシャルウェハの製造方法及び電界効果型窒化物トランジスタの製造方法 |

| US9583574B2 (en) | 2012-09-28 | 2017-02-28 | Intel Corporation | Epitaxial buffer layers for group III-N transistors on silicon substrates |

| EP3154092B1 (en) | 2013-02-15 | 2021-12-15 | AZUR SPACE Solar Power GmbH | P-doping of group iii-nitride buffer layer structure on a heterosubstrate |

| CN104701364B (zh) * | 2015-02-04 | 2017-12-05 | 厦门市三安集成电路有限公司 | 一种氮化镓基场效应晶体管及其制备方法 |

| JP2016171196A (ja) * | 2015-03-12 | 2016-09-23 | 株式会社東芝 | 半導体装置の製造方法 |

| CN104716241B (zh) * | 2015-03-16 | 2018-10-16 | 映瑞光电科技(上海)有限公司 | 一种led结构及其制作方法 |

-

2015

- 2015-12-28 US US14/981,348 patent/US10529561B2/en active Active

-

2016

- 2016-12-28 EP EP16882621.2A patent/EP3398203A4/en not_active Withdrawn

- 2016-12-28 WO PCT/US2016/069051 patent/WO2017117315A1/en not_active Ceased

- 2016-12-28 CN CN201680064897.1A patent/CN108352324B/zh active Active

- 2016-12-28 JP JP2018534035A patent/JP7068676B2/ja active Active

Patent Citations (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2001320084A (ja) | 2000-03-02 | 2001-11-16 | Ricoh Co Ltd | Iii族窒化物半導体およびその作製方法および半導体装置 |

| JP2003031845A (ja) | 2001-04-30 | 2003-01-31 | Lumileds Lighting Us Llc | 低抵抗率p型窒化ガリウムの形成 |

| JP2007184353A (ja) | 2006-01-05 | 2007-07-19 | Matsushita Electric Ind Co Ltd | 窒化物系化合物半導体素子の製造方法、および、窒化物系化合物半導体素子 |

| JP2008098603A (ja) | 2006-09-15 | 2008-04-24 | Sumitomo Chemical Co Ltd | 半導体エピタキシャル結晶基板の製造方法 |

| JP2013074209A (ja) | 2011-09-28 | 2013-04-22 | Fujitsu Ltd | 半導体装置の製造方法及び半導体装置 |

| JP2014197645A (ja) | 2013-03-29 | 2014-10-16 | 富士通株式会社 | 化合物半導体装置及びその製造方法 |

| JP2015185809A (ja) | 2014-03-26 | 2015-10-22 | 住友電気工業株式会社 | 半導体基板の製造方法及び半導体装置 |

| JP2015192026A (ja) | 2014-03-28 | 2015-11-02 | 住友電気工業株式会社 | 半導体装置の製造方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| US10529561B2 (en) | 2020-01-07 |

| CN108352324A (zh) | 2018-07-31 |

| EP3398203A4 (en) | 2019-01-23 |

| EP3398203A1 (en) | 2018-11-07 |

| US20170186859A1 (en) | 2017-06-29 |

| JP2019500755A (ja) | 2019-01-10 |

| WO2017117315A1 (en) | 2017-07-06 |

| CN108352324B (zh) | 2022-08-09 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4530171B2 (ja) | 半導体装置 | |

| JP7068676B2 (ja) | Iiia-n族デバイスのための非エッチ気体冷却エピタキシャルスタック | |

| US7901994B2 (en) | Methods of manufacturing group III nitride semiconductor devices with silicon nitride layers | |

| JP6014023B2 (ja) | 酸化ニッケルを含むゲートを有する半導体デバイス及びその作製方法 | |

| CN100590886C (zh) | 半导体电子器件 | |

| US9620362B2 (en) | Seed layer structure for growth of III-V materials on silicon | |

| US20090045439A1 (en) | Heterojunction field effect transistor and manufacturing method thereof | |

| US9847223B2 (en) | Buffer stack for group IIIA-N devices | |

| US20210020760A1 (en) | Method for Manufacturing Transistor | |

| KR20150091706A (ko) | 질화물 반도체 소자 및 그 제조 방법 | |

| TW201822305A (zh) | 半導體元件、半導體基底及其形成方法 | |

| US8872308B2 (en) | AlN cap grown on GaN/REO/silicon substrate structure | |

| EP2600393A1 (en) | Semiconductor element, hemt element, and production method for semiconductor element | |

| US20170256635A1 (en) | Nitride semiconductor and nitride semiconductor manufacturing method | |

| US20230031662A1 (en) | Iii nitride semiconductor wafers | |

| US11424355B2 (en) | Method of making a high power transistor with gate oxide barriers | |

| KR20140139890A (ko) | 질화물 반도체 소자 및 그 제조 방법 | |

| TWI730516B (zh) | 氮化物半導體基板以及氮化物半導體裝置 | |

| JP7201571B2 (ja) | 窒化物半導体基板および窒化物半導体装置 | |

| CN113178389A (zh) | 氮化镓基器件及其制造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A821 Effective date: 20180628 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20191223 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20191223 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20201223 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A711 Effective date: 20210218 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20210322 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20210323 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20210521 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20210602 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20210607 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20210714 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20211013 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20211213 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20220114 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20220330 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20220418 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 7068676 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |