JP6628552B2 - 半導体装置およびセル電圧の測定方法 - Google Patents

半導体装置およびセル電圧の測定方法 Download PDFInfo

- Publication number

- JP6628552B2 JP6628552B2 JP2015212065A JP2015212065A JP6628552B2 JP 6628552 B2 JP6628552 B2 JP 6628552B2 JP 2015212065 A JP2015212065 A JP 2015212065A JP 2015212065 A JP2015212065 A JP 2015212065A JP 6628552 B2 JP6628552 B2 JP 6628552B2

- Authority

- JP

- Japan

- Prior art keywords

- voltage

- input terminal

- cell

- input

- battery cell

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 239000004065 semiconductor Substances 0.000 title claims description 45

- 238000000034 method Methods 0.000 title claims description 27

- 238000005259 measurement Methods 0.000 claims description 219

- 238000006243 chemical reaction Methods 0.000 claims description 7

- 238000000691 measurement method Methods 0.000 claims description 5

- 238000010586 diagram Methods 0.000 description 13

- 238000001514 detection method Methods 0.000 description 12

- 230000000052 comparative effect Effects 0.000 description 8

- 230000007704 transition Effects 0.000 description 5

- 238000012935 Averaging Methods 0.000 description 3

- 230000003321 amplification Effects 0.000 description 3

- 230000007274 generation of a signal involved in cell-cell signaling Effects 0.000 description 3

- 238000003199 nucleic acid amplification method Methods 0.000 description 3

- 239000003990 capacitor Substances 0.000 description 2

- 230000006641 stabilisation Effects 0.000 description 2

- 238000011105 stabilization Methods 0.000 description 2

- 230000000087 stabilizing effect Effects 0.000 description 2

- 238000012544 monitoring process Methods 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G01—MEASURING; TESTING

- G01R—MEASURING ELECTRIC VARIABLES; MEASURING MAGNETIC VARIABLES

- G01R31/00—Arrangements for testing electric properties; Arrangements for locating electric faults; Arrangements for electrical testing characterised by what is being tested not provided for elsewhere

- G01R31/36—Arrangements for testing, measuring or monitoring the electrical condition of accumulators or electric batteries, e.g. capacity or state of charge [SoC]

- G01R31/396—Acquisition or processing of data for testing or for monitoring individual cells or groups of cells within a battery

-

- G—PHYSICS

- G01—MEASURING; TESTING

- G01R—MEASURING ELECTRIC VARIABLES; MEASURING MAGNETIC VARIABLES

- G01R31/00—Arrangements for testing electric properties; Arrangements for locating electric faults; Arrangements for electrical testing characterised by what is being tested not provided for elsewhere

- G01R31/36—Arrangements for testing, measuring or monitoring the electrical condition of accumulators or electric batteries, e.g. capacity or state of charge [SoC]

- G01R31/3644—Constructional arrangements

- G01R31/3648—Constructional arrangements comprising digital calculation means, e.g. for performing an algorithm

Landscapes

- Physics & Mathematics (AREA)

- General Physics & Mathematics (AREA)

- Measurement Of Current Or Voltage (AREA)

- Tests Of Electric Status Of Batteries (AREA)

- Charge And Discharge Circuits For Batteries Or The Like (AREA)

- Secondary Cells (AREA)

Description

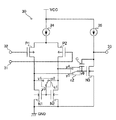

図1は、本発明の実施形態に係る半導体装置100の構成を示す回路ブロック図である。半導体装置100は、組電池を構成する直列接続された複数の電池セルの各々のセル電圧を測定する機能を有する電池監視IC(integrated circuit)を構成する。なお、セル電圧とは、1つの電池セルの陽極と陰極との間の電圧である。図1には、一例として、直列接続された12個の電池セルs1〜s12を備える組電池200が、半導体装置100と共に示されている。組電池200は、最も低電位の電池セルs1の陰極が、例えば、接地電位(GND)に接続される。

Vout=V1−V0+Vof ・・・(1)

Vout=V1−V0−Vof ・・・(2)

Vout=V2−V1−Vof ・・・(3)

Vout=V2−V1+Vof ・・・(4)

図5は、本発明の第2の実施形態に係る半導体装置101の構成を示す回路ブロック図である。半導体装置101は、第1のバッファ回路71および第2のバッファ回路81を更に含む点が、上記した第1の実施形態に係る半導体装置100と異なる。

図7は、本発明の第3の実施形態に係る半導体装置102の構成を示す回路ブロック図である。半導体装置102は、第1の実施形態に係る半導体装置100に対して入力電圧切り換え部20が削除され、接続切り換え部90が追加された構成を有する。

20 入力電圧切り換え部

30、72、82 演算増幅器

40 AD変換器

60 制御部

71、81 バッファ回路

73、83 第1のバッファ入力端子

74、84 第2のバッファ入力端子

75、85 バッファ出力端子

100、101、102 半導体装置

a1〜a26 スイッチ

b1〜b4 スイッチ

c1、c2 スイッチ

d1〜d8 スイッチ

e1〜e4 スイッチ

s1〜s12 電池セル

x0〜x12 セル電圧入力端子

Claims (8)

- 直列に接続された複数の電池セルを含む組電池の両端および前記電池セル同士の接続点の各々に接続される複数のセル電圧入力端子と、

第1の入力端子、第2の入力端子および出力端子を有し、前記第1の入力端子および前記第2の入力端子の各々に入力される電圧の差分に応じた差分電圧を前記出力端子から出力する差分電圧出力部と、

前記複数のセル電圧入力端子の各々と、前記第1の入力端子および前記第2の入力端子とを切り換え可能に接続する接続部と、

前記複数の電池セルのうちの1の電池セルの陽極に接続されるセル電圧入力端子が前記第1の入力端子に接続され、当該1の電池セルの陰極に接続されるセル電圧入力端子が前記第2の入力端子に接続された第1の接続状態、および当該1の電池セルの陰極に接続されるセル電圧入力端子が前記第1の入力端子に接続され、当該1の電池セルの陽極に接続されるセル電圧入力端子が前記第2の入力端子に接続された第2の接続状態を順次形成するように前記接続部を制御するセル電圧測定制御を前記複数の電池セルの各々について行う場合に、前記第1の接続状態および前記第2の接続状態のうち、当該1の電池セルについて最初に形成される接続状態が、直前に前記セル電圧測定制御が行われる他の電池セルについて最後に形成される接続状態と同じとなるように前記接続部を制御する制御部と、

を含み、

前記差分電圧出力部は、前記第1の入力端子に入力される電圧が前記第2の入力端子に入力される電圧よりも高い場合に前記差分電圧を出力する第1の回路接続と、前記第2の入力端子に入力される電圧が前記第1の入力端子に入力される電圧よりも高い場合に前記差分電圧を出力する第2の回路接続と、に切り換え可能に構成され、

前記制御部は、前記第1の接続状態を形成する場合に前記差分電圧出力部において前記第1の回路接続を形成し、前記第2の接続状態を形成する場合に前記差分電圧出力部において前記第2の回路接続を形成する

半導体装置。 - 前記第1の接続状態の下で前記差分電圧出力部の前記出力端子から出力された前記複数の電池セルのうちの1の電池セルのセル電圧に応じた差分電圧と、前記第2の接続状態の下で前記差分電圧出力部の前記出力端子から出力された当該1の電池セルのセル電圧に応じた差分電圧と、の平均値に相当する値を当該1の電池セルのセル電圧の測定値として算出する算出部を更に含む請求項1に記載の半導体装置。

- 前記接続部は、前記複数のセル電圧入力端子の各々を、前記第1の入力端子および前記第2の入力端子に対応する第1のノードおよび第2のノードに選択的に接続する複数のスイッチを含む第1のスイッチ群を含み、

前記制御部は、前記第1のスイッチ群における複数のスイッチのオンオフを制御する

請求項1または請求項2に記載の半導体装置。 - 前記接続部は、前記第1のノードおよび前記第2のノードに対応する第3のノードおよび第4のノードを選択的に前記第1の入力端子および前記第2の入力端子に接続する複数のスイッチを含む第2のスイッチ群を含み、

前記制御部は、前記第2のスイッチ群における複数のスイッチのオンオフを制御する

請求項3に記載の半導体装置。 - 前記複数のセル電圧入力端子と前記第1の入力端子および前記第2の入力端子との間に設けられ、入力される前記電池セルからの電圧をインピーダンス変換して出力する一対のバッファ回路を更に含む

請求項1から請求項4のいずれか1項に記載の半導体装置。 - 前記一対のバッファ回路の各々は、第1のバッファ入力端子、第2のバッファ入力端子およびバッファ出力端子を有し、前記第1のバッファ入力端子に前記電池セルからの電圧が入力され且つ前記第2のバッファ入力端子が前記バッファ出力端子に接続された第1の状態と、前記第2のバッファ入力端子に前記電池セルからの電圧が入力され且つ前記第1のバッファ入力端子が前記バッファ出力端子に接続された第2の状態と、に切り換え可能に構成され、

前記制御部は、前記第1の接続状態と前記第2の接続状態の切り換えに応じて、前記一対のバッファ回路の各々において、前記第1の状態と前記第2の状態との切り換えを行う

請求項5に記載の半導体装置。 - 前記差分電圧出力部は、一端に前記電池セルからの電圧が入力され、他端が前記第1の入力端子に接続された第1の抵抗素子と、一端が前記第1の入力端子に接続された第2の抵抗素子と、一端に前記電池セルからの電圧が入力され、他端が前記第2の入力端子に接続された第3の抵抗素子と、一端が前記第2の入力端子に接続された第4の抵抗素子と、を含み、

前記第2の抵抗素子の他端と固定電位との間に設けられた第1のスイッチと、前記第2の抵抗素子の他端と前記差分電圧出力部の前記出力端子との間に設けられた第2のスイッチと、前記第4の抵抗素子の他端と前記差分電圧出力部の前記出力端子との間に設けられた第3のスイッチと、前記第4の抵抗素子の他端と前記固定電位との間に設けられた第4のスイッチと、を更に含み、

前記制御部は、前記第1の接続状態を形成する場合に、前記第1のスイッチおよび前記第3のスイッチをオン状態とすると共に前記第2のスイッチおよび前記第4のスイッチをオフ状態とし、前記第2の接続状態を形成する場合に、前記第2のスイッチおよび前記第4のスイッチをオン状態とすると共に前記第1のスイッチおよび前記第3のスイッチをオフ状態とする

請求項1から請求項3のいずれか1項に記載の半導体装置。 - 第1の入力端子、第2の入力端子および出力端子を有し、前記第1の入力端子に入力される電圧が前記第2の入力端子に入力される電圧よりも高い場合に前記第1の入力端子および前記第2の入力端子の各々に入力される電圧の差分に応じた差分電圧を前記出力端子から出力する第1の回路接続と、前記第2の入力端子に入力される電圧が前記第1の入力端子に入力される電圧よりも高い場合に前記差分電圧を出力する第2の回路接続と、に切り換え可能に構成された差分電圧出力部の前記第1の入力端子および前記第2の入力端子に、直列に接続された複数の電池セルを含む組電池の両端および前記電池セル同士の接続点の各々を順次接続して前記複数の電池セルの各々のセル電圧を測定するセル電圧の測定方法であって、

前記複数の電池セルのうちの1の電池セルの陽極が前記第1の入力端子に接続され、当該1の電池セルの陰極が前記第2の入力端子に接続された第1の接続状態、および当該1の電池セルの陰極が前記第1の入力端子に接続され、当該1の電池セルの陽極が前記第2の入力端子に接続された第2の接続状態を順次形成するセル電圧測定制御を前記複数の電池セルの各々について行う場合に、前記第1の接続状態および前記第2の接続状態のうち、当該1の電池セルについて最初に形成される接続状態が、直前に前記セル電圧測定制御が行われる他の電池セルについて最後に形成される接続状態と同じとなるように、前記複数の電池セルの各々の陰極および陽極と、前記第1の入力端子および前記第2の入力端子との間の接続を切り換え、前記第1の接続状態を形成する場合に前記差分電圧出力部において前記第1の回路接続を形成し、前記第2の接続状態を形成する場合に前記差分電圧出力部において前記第2の回路接続を形成する

セル電圧の測定方法。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2015212065A JP6628552B2 (ja) | 2015-10-28 | 2015-10-28 | 半導体装置およびセル電圧の測定方法 |

| US15/334,442 US10060988B2 (en) | 2015-10-28 | 2016-10-26 | Semiconductor device and a method for measuring a cell voltage |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2015212065A JP6628552B2 (ja) | 2015-10-28 | 2015-10-28 | 半導体装置およびセル電圧の測定方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2017083303A JP2017083303A (ja) | 2017-05-18 |

| JP6628552B2 true JP6628552B2 (ja) | 2020-01-08 |

Family

ID=58634531

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2015212065A Active JP6628552B2 (ja) | 2015-10-28 | 2015-10-28 | 半導体装置およびセル電圧の測定方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US10060988B2 (ja) |

| JP (1) | JP6628552B2 (ja) |

Families Citing this family (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP6741945B2 (ja) * | 2016-09-13 | 2020-08-19 | ミツミ電機株式会社 | 電池制御回路 |

| EP3373407B1 (de) * | 2017-03-10 | 2020-02-12 | VARTA Microbattery GmbH | Verfahren zum betreiben eines modularen batteriespeichersystems, modulares batteriespeichersystem und batteriemanagementsystem hierfür |

| JP6817158B2 (ja) * | 2017-06-29 | 2021-01-20 | ラピスセミコンダクタ株式会社 | 半導体装置、及び電池監視システム |

| JP2019090703A (ja) * | 2017-11-15 | 2019-06-13 | 株式会社デンソー | 電圧検出装置 |

| KR102256602B1 (ko) * | 2017-12-14 | 2021-05-26 | 주식회사 엘지에너지솔루션 | 전압 측정 장치 및 방법 |

| JP7315290B2 (ja) * | 2019-03-29 | 2023-07-26 | ラピスセミコンダクタ株式会社 | 半導体装置及び電池電圧の測定方法 |

Family Cites Families (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4214787B2 (ja) * | 2002-02-06 | 2009-01-28 | 日本電気株式会社 | 増幅回路及びその制御方法 |

| JP4861791B2 (ja) * | 2006-10-27 | 2012-01-25 | ルネサスエレクトロニクス株式会社 | 演算増幅器及び表示装置 |

| JP4970224B2 (ja) * | 2007-11-30 | 2012-07-04 | ルネサスエレクトロニクス株式会社 | 半導体集積回路 |

| JP4770894B2 (ja) | 2008-09-03 | 2011-09-14 | 日本テキサス・インスツルメンツ株式会社 | 電圧検出装置 |

| JP2010085170A (ja) * | 2008-09-30 | 2010-04-15 | Mazda Motor Corp | 電池セルの電圧測定方法及び電圧測定装置 |

| JP5847995B2 (ja) * | 2010-04-27 | 2016-01-27 | ラピスセミコンダクタ株式会社 | 半導体装置 |

| JP5638311B2 (ja) * | 2010-08-18 | 2014-12-10 | ラピスセミコンダクタ株式会社 | 組電池システム、電圧監視システム、電圧監視装置及び半導体装置 |

| JP5606871B2 (ja) * | 2010-10-26 | 2014-10-15 | ラピスセミコンダクタ株式会社 | 半導体回路、半導体装置、配線の異常診断方法、及び異常診断プログラム |

| EP2699914A1 (en) * | 2011-04-19 | 2014-02-26 | 4Esys | Measurement system and method for a series connection of energy storage devices |

| JP5799786B2 (ja) * | 2011-12-09 | 2015-10-28 | 富士電機株式会社 | オートゼロアンプ及び該アンプを使用した帰還増幅回路 |

| CN103941189A (zh) * | 2013-01-18 | 2014-07-23 | 拉碧斯半导体株式会社 | 电池监视系统、半导体装置、电池组系统及电池监视ic |

-

2015

- 2015-10-28 JP JP2015212065A patent/JP6628552B2/ja active Active

-

2016

- 2016-10-26 US US15/334,442 patent/US10060988B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| US20170123010A1 (en) | 2017-05-04 |

| US10060988B2 (en) | 2018-08-28 |

| JP2017083303A (ja) | 2017-05-18 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6628552B2 (ja) | 半導体装置およびセル電圧の測定方法 | |

| JP6379578B2 (ja) | 温度測定装置、集積回路および温度測定方法 | |

| CN100471054C (zh) | 差分放大器电路及使用其的液晶显示单元的驱动电路 | |

| JP5171908B2 (ja) | 電源回路 | |

| CN108415502B (zh) | 一种无有限周期震荡的数字线性稳压电源及稳压方法 | |

| CN101514925A (zh) | 温度检测电路 | |

| CN207198220U (zh) | 电压比较器 | |

| US20160344290A1 (en) | Current sensing module and power conversion apparatus and electronic apparatus using the same | |

| JP2008104197A (ja) | 容量素子バラツキ依存性のないスイッチドキャパシタ増幅器およびその動作方法 | |

| JP2014137272A (ja) | 電圧監視装置 | |

| JP2014020827A (ja) | 静電容量型センサの検出回路 | |

| US10985721B2 (en) | Switched capacitor amplifier circuit, voltage amplification method, and infrared sensor device | |

| JP2019168892A (ja) | 演算増幅回路及びこれを使用した電流検出装置 | |

| JP2012075092A (ja) | 発振回路およびそれを用いた半導体装置 | |

| JP5891811B2 (ja) | 全差動増幅回路、コンパレーター回路、a/d変換回路、及び電子機器 | |

| WO2009096192A1 (ja) | バッファ回路及びそれを備えたイメージセンサチップ並びに撮像装置 | |

| JP2016090379A (ja) | 測定装置 | |

| WO2013001683A1 (ja) | 電圧計測用マルチプレクサおよびそれを備えた電圧計測器 | |

| EP3070845B1 (en) | Comparison circuit | |

| JP2014209670A (ja) | 差動増幅回路およびa/d変換器 | |

| JP4639162B2 (ja) | アナログ・ディジタル変換器 | |

| JP2010109963A (ja) | 逐次比較型ad変換回路および制御用半導体集積回路 | |

| JP2008199563A (ja) | 増幅回路 | |

| JP2015035761A (ja) | スイッチトキャパシタ回路 | |

| JP2006135655A (ja) | 半導体集積回路 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20180920 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20190719 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20190730 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20190927 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20191105 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20191203 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6628552 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |