JP6543908B2 - 変圧装置 - Google Patents

変圧装置 Download PDFInfo

- Publication number

- JP6543908B2 JP6543908B2 JP2014210011A JP2014210011A JP6543908B2 JP 6543908 B2 JP6543908 B2 JP 6543908B2 JP 2014210011 A JP2014210011 A JP 2014210011A JP 2014210011 A JP2014210011 A JP 2014210011A JP 6543908 B2 JP6543908 B2 JP 6543908B2

- Authority

- JP

- Japan

- Prior art keywords

- voltage

- output

- current

- switch

- duty

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 239000003990 capacitor Substances 0.000 claims description 45

- 238000001514 detection method Methods 0.000 claims description 18

- 230000003247 decreasing effect Effects 0.000 claims description 6

- 238000009499 grossing Methods 0.000 claims description 3

- 238000006243 chemical reaction Methods 0.000 claims 1

- 230000007423 decrease Effects 0.000 description 26

- 238000000034 method Methods 0.000 description 14

- 230000008569 process Effects 0.000 description 12

- 230000007704 transition Effects 0.000 description 12

- 238000010586 diagram Methods 0.000 description 10

- 230000006870 function Effects 0.000 description 10

- 230000003321 amplification Effects 0.000 description 6

- 238000003199 nucleic acid amplification method Methods 0.000 description 6

- 230000009471 action Effects 0.000 description 4

- 238000013459 approach Methods 0.000 description 4

- 230000009467 reduction Effects 0.000 description 3

- 230000009466 transformation Effects 0.000 description 3

- 230000006641 stabilisation Effects 0.000 description 2

- 238000011105 stabilization Methods 0.000 description 2

- 230000005669 field effect Effects 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 230000001105 regulatory effect Effects 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02M—APPARATUS FOR CONVERSION BETWEEN AC AND AC, BETWEEN AC AND DC, OR BETWEEN DC AND DC, AND FOR USE WITH MAINS OR SIMILAR POWER SUPPLY SYSTEMS; CONVERSION OF DC OR AC INPUT POWER INTO SURGE OUTPUT POWER; CONTROL OR REGULATION THEREOF

- H02M3/00—Conversion of dc power input into dc power output

- H02M3/02—Conversion of dc power input into dc power output without intermediate conversion into ac

- H02M3/04—Conversion of dc power input into dc power output without intermediate conversion into ac by static converters

- H02M3/10—Conversion of dc power input into dc power output without intermediate conversion into ac by static converters using discharge tubes with control electrode or semiconductor devices with control electrode

- H02M3/145—Conversion of dc power input into dc power output without intermediate conversion into ac by static converters using discharge tubes with control electrode or semiconductor devices with control electrode using devices of a triode or transistor type requiring continuous application of a control signal

- H02M3/155—Conversion of dc power input into dc power output without intermediate conversion into ac by static converters using discharge tubes with control electrode or semiconductor devices with control electrode using devices of a triode or transistor type requiring continuous application of a control signal using semiconductor devices only

- H02M3/156—Conversion of dc power input into dc power output without intermediate conversion into ac by static converters using discharge tubes with control electrode or semiconductor devices with control electrode using devices of a triode or transistor type requiring continuous application of a control signal using semiconductor devices only with automatic control of output voltage or current, e.g. switching regulators

- H02M3/158—Conversion of dc power input into dc power output without intermediate conversion into ac by static converters using discharge tubes with control electrode or semiconductor devices with control electrode using devices of a triode or transistor type requiring continuous application of a control signal using semiconductor devices only with automatic control of output voltage or current, e.g. switching regulators including plural semiconductor devices as final control devices for a single load

- H02M3/1582—Buck-boost converters

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02M—APPARATUS FOR CONVERSION BETWEEN AC AND AC, BETWEEN AC AND DC, OR BETWEEN DC AND DC, AND FOR USE WITH MAINS OR SIMILAR POWER SUPPLY SYSTEMS; CONVERSION OF DC OR AC INPUT POWER INTO SURGE OUTPUT POWER; CONTROL OR REGULATION THEREOF

- H02M1/00—Details of apparatus for conversion

- H02M1/08—Circuits specially adapted for the generation of control voltages for semiconductor devices incorporated in static converters

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02M—APPARATUS FOR CONVERSION BETWEEN AC AND AC, BETWEEN AC AND DC, OR BETWEEN DC AND DC, AND FOR USE WITH MAINS OR SIMILAR POWER SUPPLY SYSTEMS; CONVERSION OF DC OR AC INPUT POWER INTO SURGE OUTPUT POWER; CONTROL OR REGULATION THEREOF

- H02M1/00—Details of apparatus for conversion

- H02M1/0003—Details of control, feedback or regulation circuits

- H02M1/0009—Devices or circuits for detecting current in a converter

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Dc-Dc Converters (AREA)

Description

以上により、入力電圧を基準電圧に変圧し、該基準電圧を負荷に印加させることができる。

このため、前述した従来の変圧装置には、出力電流の上昇及び低下が交互に繰り返されて出力電流が安定しないという問題がある。

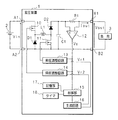

図1は本実施の形態における変圧装置1の回路図である。変圧装置1は好適に車両に搭載されている。変圧装置1は、入力端子対を構成する2つの入力端子A1,A2と、出力端子対を構成する2つの出力端子B1,B2とを備える。入力端子A1はバッテリ2の正極に接続され、入力端子A2はバッテリ2の負極に接続されている。出力端子B1は負荷3の一端に接続され、出力端子B2は負荷3の他端に接続されている。

変圧装置1では、昇圧動作及び降圧動作を並行して行い、昇圧動作及び降圧動作によって変圧された電圧、即ち、出力電圧Voutは出力端子B1,B2から出力される。

従って、差動増幅器12及び抵抗R1は、出力端子B1,B2間に流れる電流を検出する電流検出回路として機能し、更には、出力電流Ioutが大きい場合に高い電圧を出力し、出力電流Ioutが小さい場合に低い電圧を出力する出力手段として機能する。

タイマ18には、計時の開始を指示する開始指示と、計時の終了を指示する終了指示とが制御部15から入力される。タイマ18は、制御部15から開始指示が入力された場合、計時を開始する。タイマ18が計時した計時時間は制御部15によって読み出される。タイマ18は、制御部15から終了指示が入力された場合、計時を終了する。

参照電流Ir2は特許請求の範囲における電流I2に相当する。

参照電圧Vr2を分圧することによって参照電圧Vr1が生成されるため、参照電圧Vr2が調整された場合、参照電圧Vr1も自動的に調整される。

制御部15は、電圧Vdが目標電圧未満ではないと判定した場合、即ち、電圧Vdが目標電圧である場合(S10:NO)、処理をステップS3に戻す。

以上のように、電圧調整処理では、参照電圧Vr1,Vr2を調整することによって、出力端子B1,B2間に安定して流れている出力電流Ioutが調整される。

また、参照電圧Vr1,Vr2は固定値であってもよい。この場合、制御部15は電圧調整処理を行うことなく、生成回路16から昇圧調整回路13及び降圧調整回路14夫々に一定の参照電圧Vr1,Vr2が出力される。

12 差動増幅器(電流検出回路の一部、出力手段の一部)

13 昇圧調整回路

14 降圧調整回路

15 制御部(調整手段)

16 生成回路

A1,A2 入力端子(入力端子対)

B1,B2 出力端子(出力端子対)

Ir1 参照電流(電流I1)

Ir2 参照電流(電流I2)

R1 抵抗(電流検出回路の他部、出力手段の他部)

Vin 入力電圧

Vr1 参照電圧(電圧V1)

Vr2 参照電圧(電圧V2)

Claims (4)

- 入力端子対間に印加された入力電圧を、該入力電圧のN倍(N≧1)に昇圧させるための昇圧動作と、前記入力電圧を、該入力電圧のM倍(0≦M≦1)に降圧させるための降圧動作とを並行して行い、前記昇圧動作及び降圧動作によって変圧された電圧を出力端子対から出力する変圧装置であって、

前記入力端子対の一方の入力端子に一端が接続される第1スイッチと、

カソードが該第1スイッチの他端に接続され、アノードが前記入力端子対の他方の入力端子に接続される第1ダイオードと、

該第1ダイオードのカソードに一端が接続されるコイルと、

カソードが前記出力端子対の一方の出力端子に接続され、アノードが前記コイルの他端に接続される第2ダイオードと、

前記コイルの他端に一端が接続され、前記入力端子対の他方の入力端子、及び、前記出力端子対の他方の出力端子に他端が接続される第2スイッチと、

前記出力端子対間に流れる電流を検出する電流検出回路と、

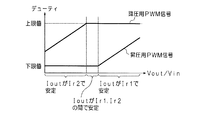

前記第2スイッチのオン及びオフへの切替えを交互に行うことによって前記昇圧動作を行い、前記電流検出回路が検出した検出電流が電流I1よりも大きい場合に、前記第2スイッチのオン及びオフへの切替えに係る昇圧デューティを低下させることによって、前記Nを低下させ、前記検出電流が前記電流I1よりも小さい場合に前記昇圧デューティを上昇させることによって前記Nを上昇させる昇圧調整回路と、

前記第1スイッチのオン及びオフへの切替えを交互に行うことによって前記降圧動作を行い、前記検出電流が電流I2(>前記電流I1)よりも大きい場合に、前記第1スイッチのオン及びオフへの切替えに係る降圧デューティを低下させることによって、前記Mを低下させ、前記検出電流が前記電流I2よりも小さい場合に前記降圧デューティを上昇させることによって前記Mを上昇させる降圧調整回路と

を備え、

前記昇圧調整回路及び降圧調整回路は、前記第1スイッチのオン及びオフへの切替えと、前記第2スイッチのオン及びオフへの切替えとを互いに独立して行うことによって、前記昇圧動作及び降圧動作を並行して行うこと

を特徴とする変圧装置。 - 入力端子対間に印加された入力電圧を、該入力電圧のN倍(N≧1)に昇圧させるための昇圧動作と、前記入力電圧を、該入力電圧のM倍(0≦M≦1)に降圧させるための降圧動作とを並行して行い、前記昇圧動作及び降圧動作によって変圧された電圧を出力端子対から出力する変圧装置であって、

前記入力端子対の一方の入力端子に一端が接続される第1スイッチと、

カソードが該第1スイッチの他端に接続され、アノードが前記入力端子対の他方の入力端子に接続される第1ダイオードと、

該第1ダイオードのカソードに一端が接続されるコイルと、

カソードが前記出力端子対の一方の出力端子に接続され、アノードが前記コイルの他端に接続される第2ダイオードと、

前記コイルの他端に一端が接続され、前記入力端子対の他方の入力端子、及び、前記出力端子対の他方の出力端子に他端が接続される第2スイッチと、

前記出力端子対間に流れる電流が大きい場合に高い電圧を出力し、前記出力端子対間に流れる電流が小さい場合に低い電圧を出力する出力手段と、

前記第2スイッチのオン及びオフへの切替えを交互に行うことによって前記昇圧動作を行い、前記出力手段が出力した電圧が電圧V1よりも高い場合に、前記第2スイッチのオン及びオフへの切替えに係る昇圧デューティを低下させることによって前記Nを低下させ、前記出力手段が出力した電圧が前記電圧V1よりも低い場合に、前記昇圧デューティを上昇させることによって前記Nを上昇させる昇圧調整回路と、

前記第1スイッチのオン及びオフへの切替えを交互に行うことによって前記降圧動作を行い、前記出力手段が出力した電圧が電圧V2(>前記電圧V1)よりも高い場合に、前記第1スイッチのオン及びオフへの切替えに係る降圧デューティを低下させることによって、前記Mを低下させ、前記出力手段が出力した電圧が前記電圧V2よりも低い場合に前記降圧デューティを上昇させることによって前記Mを上昇させる降圧調整回路と

を備え、

前記昇圧調整回路及び降圧調整回路は、前記第1スイッチのオン及びオフへの切替えと、前記第2スイッチのオン及びオフへの切替えとを互いに独立して行うことによって、前記昇圧動作及び降圧動作を並行して行うこと

を特徴とする変圧装置。 - 一定の電圧が一端に印加される第1抵抗と、

前記第1抵抗の他端に一端が接続される第2抵抗及び第3抵抗と、

前記第2抵抗の他端に一端が接続される第4抵抗と、

前記第4抵抗の他端に一端が接続される第5抵抗と、

前記第3抵抗の他端に一端が接続される第3スイッチと、

前記第1抵抗の他端から出力された電圧を平滑する第1コンデンサと、

前記第2抵抗の他端から出力された電圧を平滑する第2コンデンサと

を備え、

前記第1コンデンサが平滑した電圧が前記電圧V1として用いられ、

前記第2コンデンサが平滑した電圧が前記電圧V2として用いられること

を特徴とする請求項2に記載の変圧装置。 - 前記第3スイッチのオン及びオフへの切替えを交互に行い、該切替えに係るデューティを調整することによって、前記電圧V1及び電圧V2を調整する調整手段を備えること

を特徴とする請求項3に記載の変圧装置。

Priority Applications (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2014210011A JP6543908B2 (ja) | 2014-10-14 | 2014-10-14 | 変圧装置 |

| DE112015004739.5T DE112015004739T5 (de) | 2014-10-14 | 2015-09-29 | Spannungswandler |

| US15/516,604 US10224815B2 (en) | 2014-10-14 | 2015-09-29 | Voltage converter having a step-up and step-down adjustment circuit |

| CN201580052418.XA CN106716803B (zh) | 2014-10-14 | 2015-09-29 | 变压装置 |

| PCT/JP2015/077416 WO2016059965A1 (ja) | 2014-10-14 | 2015-09-29 | 変圧装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2014210011A JP6543908B2 (ja) | 2014-10-14 | 2014-10-14 | 変圧装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2016082647A JP2016082647A (ja) | 2016-05-16 |

| JP2016082647A5 JP2016082647A5 (ja) | 2017-04-27 |

| JP6543908B2 true JP6543908B2 (ja) | 2019-07-17 |

Family

ID=55746513

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2014210011A Active JP6543908B2 (ja) | 2014-10-14 | 2014-10-14 | 変圧装置 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US10224815B2 (ja) |

| JP (1) | JP6543908B2 (ja) |

| CN (1) | CN106716803B (ja) |

| DE (1) | DE112015004739T5 (ja) |

| WO (1) | WO2016059965A1 (ja) |

Families Citing this family (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN109510465A (zh) * | 2017-09-14 | 2019-03-22 | 中兴通讯股份有限公司 | 一种转换电路的工作模式切换方法、装置及升降压变换器 |

| JP6993207B2 (ja) * | 2017-12-20 | 2022-01-13 | Fdk株式会社 | 双方向スイッチング電源用の電流検出装置 |

| JP7140633B2 (ja) * | 2018-10-24 | 2022-09-21 | 矢崎総業株式会社 | 電力制御装置 |

| CN112286277B (zh) * | 2019-07-24 | 2022-07-08 | 杭州萤石软件有限公司 | 电压调节电路 |

Family Cites Families (24)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS6218970A (ja) * | 1985-07-17 | 1987-01-27 | Matsushita Electric Ind Co Ltd | 電源装置 |

| US5912552A (en) * | 1997-02-12 | 1999-06-15 | Kabushiki Kaisha Toyoda Jidoshokki Seisakusho | DC to DC converter with high efficiency for light loads |

| JP4439742B2 (ja) * | 1999-05-04 | 2010-03-24 | エヌエックスピー ビー ヴィ | Dc−dcコンバータ |

| US6166527A (en) * | 2000-03-27 | 2000-12-26 | Linear Technology Corporation | Control circuit and method for maintaining high efficiency in a buck-boost switching regulator |

| JP4487649B2 (ja) * | 2004-06-14 | 2010-06-23 | 富士電機システムズ株式会社 | 昇降圧型dc−dcコンバータの制御装置 |

| JP2006006004A (ja) | 2004-06-16 | 2006-01-05 | Ricoh Co Ltd | 昇降圧型dc−dcコンバータ |

| JP2007097361A (ja) * | 2005-09-30 | 2007-04-12 | Matsushita Electric Ind Co Ltd | 昇降圧コンバータ |

| US8164316B2 (en) * | 2006-06-26 | 2012-04-24 | Renesas Electronics Corporation | DC/DC converter |

| JP4910575B2 (ja) * | 2006-08-31 | 2012-04-04 | 日本テキサス・インスツルメンツ株式会社 | スイッチング電源装置 |

| TWI392989B (zh) * | 2008-06-03 | 2013-04-11 | Richtek Technology Corp | 切換式昇降壓電源供應器及其控制方法 |

| JP5199019B2 (ja) * | 2008-10-16 | 2013-05-15 | 株式会社小糸製作所 | 昇降圧dc−dcコンバータ |

| JP5300410B2 (ja) * | 2008-10-24 | 2013-09-25 | 株式会社小糸製作所 | Dc−dcコンバータ及びこのdc−dcコンバータを備えた車両用灯具の電源装置 |

| JP2010158116A (ja) * | 2008-12-27 | 2010-07-15 | Diamond Electric Mfg Co Ltd | Dc−dcコンバータ |

| JP2010268590A (ja) * | 2009-05-14 | 2010-11-25 | Koito Mfg Co Ltd | 昇降圧dc−dcコンバータ |

| JP2010284046A (ja) * | 2009-06-05 | 2010-12-16 | Koito Mfg Co Ltd | 昇降圧dc−dcコンバータ |

| US9467053B2 (en) * | 2009-07-09 | 2016-10-11 | Infineon Technologies Ag | Controlling a multi-mode switching converter |

| JP5599031B2 (ja) * | 2009-12-16 | 2014-10-01 | 株式会社小糸製作所 | 昇降圧型コンバータ |

| JP5479940B2 (ja) * | 2010-02-16 | 2014-04-23 | 株式会社小糸製作所 | 昇降圧dc−dcコンバータ及び車両用灯具 |

| US8508208B2 (en) * | 2010-07-02 | 2013-08-13 | Fairchild Semiconductor Corporation | Buck-boost regulator with converter bypass function |

| US8981737B2 (en) * | 2011-03-08 | 2015-03-17 | Intersil Americas LLC | High efficiency PFM control for buck-boost converter |

| WO2012176403A1 (ja) * | 2011-06-21 | 2012-12-27 | パナソニック株式会社 | 昇降圧型ac/dcコンバータ |

| JP5716631B2 (ja) * | 2011-10-18 | 2015-05-13 | 株式会社日本自動車部品総合研究所 | 電力変換装置 |

| CN102710131A (zh) * | 2012-06-13 | 2012-10-03 | 杭州士兰微电子股份有限公司 | 变换器及其驱动方法及包含该变换器的功率因数校正装置 |

| JP5939096B2 (ja) * | 2012-09-05 | 2016-06-22 | 株式会社日本自動車部品総合研究所 | 電力変換装置 |

-

2014

- 2014-10-14 JP JP2014210011A patent/JP6543908B2/ja active Active

-

2015

- 2015-09-29 CN CN201580052418.XA patent/CN106716803B/zh active Active

- 2015-09-29 DE DE112015004739.5T patent/DE112015004739T5/de not_active Withdrawn

- 2015-09-29 WO PCT/JP2015/077416 patent/WO2016059965A1/ja active Application Filing

- 2015-09-29 US US15/516,604 patent/US10224815B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| DE112015004739T5 (de) | 2017-07-06 |

| US10224815B2 (en) | 2019-03-05 |

| US20180234017A1 (en) | 2018-08-16 |

| WO2016059965A1 (ja) | 2016-04-21 |

| CN106716803B (zh) | 2019-08-27 |

| CN106716803A (zh) | 2017-05-24 |

| JP2016082647A (ja) | 2016-05-16 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US10972009B2 (en) | Multi-phase converter and control circuit thereof | |

| US8242760B2 (en) | Constant-voltage circuit device | |

| US8890501B2 (en) | System and method for soft-starting a power converter with a pre-charged output | |

| KR20160022807A (ko) | 전류 모드 스위칭 조절기를 위한 듀티-싸이클 의존성 기울기 보정 | |

| JP6962233B2 (ja) | 車載用のdcdcコンバータ | |

| US9362822B2 (en) | Average load current detector for a multi-mode switching converter | |

| JP6543908B2 (ja) | 変圧装置 | |

| TWI637579B (zh) | Charging device | |

| KR20060049915A (ko) | Dc-dc 컨버터 회로 | |

| US7151361B2 (en) | Current sensing circuitry for DC-DC converters | |

| US20150194888A1 (en) | Power source circuit | |

| TWI514735B (zh) | 控制電源轉換器輸出固定功率的控制器及其相關的方法 | |

| US10122260B2 (en) | Switched-mode power converter with a current limit circuit | |

| JP6904283B2 (ja) | 車載用のdcdcコンバータ | |

| US9929646B2 (en) | Charge pump circuit and step-down regulator circuit | |

| KR102096171B1 (ko) | Dc-dc 컨버터용 소프트 스타트 장치 및 방법 | |

| JP2010283999A (ja) | 電源装置、制御回路、電源装置の制御方法 | |

| US20120032659A1 (en) | Power supply device | |

| JP2008011585A (ja) | スイッチングレギュレータ | |

| JP6177813B2 (ja) | Dc−dcコンバータ | |

| JP5881664B2 (ja) | 電源装置、制御回路、電源装置の制御方法 | |

| JP4934442B2 (ja) | スイッチング電源装置 | |

| TWI537700B (zh) | 開關電源電壓調節器 | |

| JP4810132B2 (ja) | 遅延回路およびリップルコンバータ | |

| US9548728B2 (en) | Time signal generating circuit and time signal generating method |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20161031 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20170323 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20180109 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20180807 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20181002 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20190319 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20190521 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20190603 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6543908 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |