JP6173548B2 - 半導体装置 - Google Patents

半導体装置 Download PDFInfo

- Publication number

- JP6173548B2 JP6173548B2 JP2016174210A JP2016174210A JP6173548B2 JP 6173548 B2 JP6173548 B2 JP 6173548B2 JP 2016174210 A JP2016174210 A JP 2016174210A JP 2016174210 A JP2016174210 A JP 2016174210A JP 6173548 B2 JP6173548 B2 JP 6173548B2

- Authority

- JP

- Japan

- Prior art keywords

- layer

- transistor

- circuit

- voltage

- conductive layer

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000004065 semiconductor Substances 0.000 title claims description 219

- 230000006870 function Effects 0.000 claims description 76

- 238000006243 chemical reaction Methods 0.000 claims description 75

- 239000000758 substrate Substances 0.000 claims description 40

- 238000003860 storage Methods 0.000 claims description 30

- 230000015572 biosynthetic process Effects 0.000 claims description 21

- 239000003990 capacitor Substances 0.000 claims description 20

- 239000010410 layer Substances 0.000 description 531

- 239000000463 material Substances 0.000 description 39

- 238000005259 measurement Methods 0.000 description 37

- 239000012535 impurity Substances 0.000 description 35

- 238000010438 heat treatment Methods 0.000 description 34

- 229910044991 metal oxide Inorganic materials 0.000 description 29

- 150000004706 metal oxides Chemical group 0.000 description 29

- 238000011156 evaluation Methods 0.000 description 27

- 238000000034 method Methods 0.000 description 25

- 239000007789 gas Substances 0.000 description 21

- XLOMVQKBTHCTTD-UHFFFAOYSA-N Zinc monoxide Chemical compound [Zn]=O XLOMVQKBTHCTTD-UHFFFAOYSA-N 0.000 description 18

- 229910052760 oxygen Inorganic materials 0.000 description 16

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 15

- 238000010586 diagram Methods 0.000 description 15

- 239000001301 oxygen Substances 0.000 description 15

- 229910007541 Zn O Inorganic materials 0.000 description 13

- 239000012298 atmosphere Substances 0.000 description 12

- 238000002347 injection Methods 0.000 description 12

- 239000007924 injection Substances 0.000 description 12

- 238000009825 accumulation Methods 0.000 description 11

- 239000001257 hydrogen Substances 0.000 description 11

- 229910052739 hydrogen Inorganic materials 0.000 description 11

- 229910052782 aluminium Inorganic materials 0.000 description 10

- 230000008859 change Effects 0.000 description 10

- 238000004519 manufacturing process Methods 0.000 description 10

- 229910052710 silicon Inorganic materials 0.000 description 10

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N silicon dioxide Inorganic materials O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 10

- 238000004544 sputter deposition Methods 0.000 description 10

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 9

- 239000010703 silicon Substances 0.000 description 9

- 229910052814 silicon oxide Inorganic materials 0.000 description 9

- 239000011787 zinc oxide Substances 0.000 description 9

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 8

- 238000004891 communication Methods 0.000 description 8

- 230000000630 rising effect Effects 0.000 description 8

- 238000012795 verification Methods 0.000 description 7

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 7

- 239000011701 zinc Substances 0.000 description 7

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 6

- MYMOFIZGZYHOMD-UHFFFAOYSA-N Dioxygen Chemical compound O=O MYMOFIZGZYHOMD-UHFFFAOYSA-N 0.000 description 6

- 229910052581 Si3N4 Inorganic materials 0.000 description 6

- 239000013078 crystal Substances 0.000 description 6

- 229910001882 dioxygen Inorganic materials 0.000 description 6

- 150000002431 hydrogen Chemical class 0.000 description 6

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 6

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 6

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 5

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 5

- 239000000956 alloy Substances 0.000 description 5

- 229910052802 copper Inorganic materials 0.000 description 5

- 239000010949 copper Substances 0.000 description 5

- 239000007769 metal material Substances 0.000 description 5

- 230000008569 process Effects 0.000 description 5

- 239000010936 titanium Substances 0.000 description 5

- 229910052719 titanium Inorganic materials 0.000 description 5

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 4

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 4

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 4

- 150000004678 hydrides Chemical class 0.000 description 4

- 125000002887 hydroxy group Chemical group [H]O* 0.000 description 4

- 229910052751 metal Inorganic materials 0.000 description 4

- 229910052750 molybdenum Inorganic materials 0.000 description 4

- 239000011733 molybdenum Substances 0.000 description 4

- 229910052757 nitrogen Inorganic materials 0.000 description 4

- 230000002265 prevention Effects 0.000 description 4

- 230000001681 protective effect Effects 0.000 description 4

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 4

- 229910052721 tungsten Inorganic materials 0.000 description 4

- 239000010937 tungsten Substances 0.000 description 4

- QTBSBXVTEAMEQO-UHFFFAOYSA-N Acetic acid Chemical compound CC(O)=O QTBSBXVTEAMEQO-UHFFFAOYSA-N 0.000 description 3

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 3

- 229910019092 Mg-O Inorganic materials 0.000 description 3

- 229910019395 Mg—O Inorganic materials 0.000 description 3

- 229910052804 chromium Inorganic materials 0.000 description 3

- 239000011651 chromium Substances 0.000 description 3

- 238000005530 etching Methods 0.000 description 3

- 229910052733 gallium Inorganic materials 0.000 description 3

- 239000011261 inert gas Substances 0.000 description 3

- 239000002184 metal Substances 0.000 description 3

- 239000000203 mixture Substances 0.000 description 3

- 230000000737 periodic effect Effects 0.000 description 3

- 238000000206 photolithography Methods 0.000 description 3

- 229910052715 tantalum Inorganic materials 0.000 description 3

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 3

- 229910005191 Ga 2 O 3 Inorganic materials 0.000 description 2

- 229910052779 Neodymium Inorganic materials 0.000 description 2

- NBIIXXVUZAFLBC-UHFFFAOYSA-N Phosphoric acid Chemical compound OP(O)(O)=O NBIIXXVUZAFLBC-UHFFFAOYSA-N 0.000 description 2

- 229910006404 SnO 2 Inorganic materials 0.000 description 2

- 229910045601 alloy Inorganic materials 0.000 description 2

- 229910052786 argon Inorganic materials 0.000 description 2

- 229910052800 carbon group element Inorganic materials 0.000 description 2

- PMHQVHHXPFUNSP-UHFFFAOYSA-M copper(1+);methylsulfanylmethane;bromide Chemical compound Br[Cu].CSC PMHQVHHXPFUNSP-UHFFFAOYSA-M 0.000 description 2

- 230000007547 defect Effects 0.000 description 2

- 238000000151 deposition Methods 0.000 description 2

- 230000008021 deposition Effects 0.000 description 2

- 238000001312 dry etching Methods 0.000 description 2

- 239000011521 glass Substances 0.000 description 2

- 229910052748 manganese Inorganic materials 0.000 description 2

- TWNQGVIAIRXVLR-UHFFFAOYSA-N oxo(oxoalumanyloxy)alumane Chemical compound O=[Al]O[Al]=O TWNQGVIAIRXVLR-UHFFFAOYSA-N 0.000 description 2

- 238000009832 plasma treatment Methods 0.000 description 2

- 230000005855 radiation Effects 0.000 description 2

- 238000001552 radio frequency sputter deposition Methods 0.000 description 2

- 230000002441 reversible effect Effects 0.000 description 2

- 238000001039 wet etching Methods 0.000 description 2

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 1

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 1

- 206010021143 Hypoxia Diseases 0.000 description 1

- DGAQECJNVWCQMB-PUAWFVPOSA-M Ilexoside XXIX Chemical compound C[C@@H]1CC[C@@]2(CC[C@@]3(C(=CC[C@H]4[C@]3(CC[C@@H]5[C@@]4(CC[C@@H](C5(C)C)OS(=O)(=O)[O-])C)C)[C@@H]2[C@]1(C)O)C)C(=O)O[C@H]6[C@@H]([C@H]([C@@H]([C@H](O6)CO)O)O)O.[Na+] DGAQECJNVWCQMB-PUAWFVPOSA-M 0.000 description 1

- 108010083687 Ion Pumps Proteins 0.000 description 1

- GRYLNZFGIOXLOG-UHFFFAOYSA-N Nitric acid Chemical compound O[N+]([O-])=O GRYLNZFGIOXLOG-UHFFFAOYSA-N 0.000 description 1

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 1

- 239000004642 Polyimide Substances 0.000 description 1

- 229910004298 SiO 2 Inorganic materials 0.000 description 1

- 229910020923 Sn-O Inorganic materials 0.000 description 1

- AZWHFTKIBIQKCA-UHFFFAOYSA-N [Sn+2]=O.[O-2].[In+3] Chemical compound [Sn+2]=O.[O-2].[In+3] AZWHFTKIBIQKCA-UHFFFAOYSA-N 0.000 description 1

- NIXOWILDQLNWCW-UHFFFAOYSA-N acrylic acid group Chemical group C(C=C)(=O)O NIXOWILDQLNWCW-UHFFFAOYSA-N 0.000 description 1

- 230000009471 action Effects 0.000 description 1

- 229910000147 aluminium phosphate Inorganic materials 0.000 description 1

- 239000005407 aluminoborosilicate glass Substances 0.000 description 1

- 229910052788 barium Inorganic materials 0.000 description 1

- DSAJWYNOEDNPEQ-UHFFFAOYSA-N barium atom Chemical compound [Ba] DSAJWYNOEDNPEQ-UHFFFAOYSA-N 0.000 description 1

- UMIVXZPTRXBADB-UHFFFAOYSA-N benzocyclobutene Chemical compound C1=CC=C2CCC2=C1 UMIVXZPTRXBADB-UHFFFAOYSA-N 0.000 description 1

- 229910052796 boron Inorganic materials 0.000 description 1

- 239000005388 borosilicate glass Substances 0.000 description 1

- 229910052799 carbon Inorganic materials 0.000 description 1

- 239000000969 carrier Substances 0.000 description 1

- 239000000919 ceramic Substances 0.000 description 1

- 239000000470 constituent Substances 0.000 description 1

- 230000007423 decrease Effects 0.000 description 1

- 230000018044 dehydration Effects 0.000 description 1

- 238000006297 dehydration reaction Methods 0.000 description 1

- 238000006356 dehydrogenation reaction Methods 0.000 description 1

- 238000009792 diffusion process Methods 0.000 description 1

- 239000000428 dust Substances 0.000 description 1

- 239000000284 extract Substances 0.000 description 1

- 229910021480 group 4 element Inorganic materials 0.000 description 1

- 229910000449 hafnium oxide Inorganic materials 0.000 description 1

- WIHZLLGSGQNAGK-UHFFFAOYSA-N hafnium(4+);oxygen(2-) Chemical compound [O-2].[O-2].[Hf+4] WIHZLLGSGQNAGK-UHFFFAOYSA-N 0.000 description 1

- 229910052736 halogen Inorganic materials 0.000 description 1

- 150000002367 halogens Chemical class 0.000 description 1

- 229910052734 helium Inorganic materials 0.000 description 1

- 239000001307 helium Substances 0.000 description 1

- SWQJXJOGLNCZEY-UHFFFAOYSA-N helium atom Chemical compound [He] SWQJXJOGLNCZEY-UHFFFAOYSA-N 0.000 description 1

- -1 hydrogen compound Chemical class 0.000 description 1

- 229910003437 indium oxide Inorganic materials 0.000 description 1

- PJXISJQVUVHSOJ-UHFFFAOYSA-N indium(iii) oxide Chemical compound [O-2].[O-2].[O-2].[In+3].[In+3] PJXISJQVUVHSOJ-UHFFFAOYSA-N 0.000 description 1

- 239000012212 insulator Substances 0.000 description 1

- 230000007774 longterm Effects 0.000 description 1

- 230000007257 malfunction Effects 0.000 description 1

- 239000011159 matrix material Substances 0.000 description 1

- 238000000691 measurement method Methods 0.000 description 1

- 230000008018 melting Effects 0.000 description 1

- 238000002844 melting Methods 0.000 description 1

- QSHDDOUJBYECFT-UHFFFAOYSA-N mercury Chemical compound [Hg] QSHDDOUJBYECFT-UHFFFAOYSA-N 0.000 description 1

- 229910052753 mercury Inorganic materials 0.000 description 1

- 229910001507 metal halide Inorganic materials 0.000 description 1

- 150000005309 metal halides Chemical class 0.000 description 1

- 239000011259 mixed solution Substances 0.000 description 1

- QEFYFXOXNSNQGX-UHFFFAOYSA-N neodymium atom Chemical compound [Nd] QEFYFXOXNSNQGX-UHFFFAOYSA-N 0.000 description 1

- 229910017604 nitric acid Inorganic materials 0.000 description 1

- 239000012299 nitrogen atmosphere Substances 0.000 description 1

- 239000011368 organic material Substances 0.000 description 1

- 230000003071 parasitic effect Effects 0.000 description 1

- 239000002245 particle Substances 0.000 description 1

- 229910052698 phosphorus Inorganic materials 0.000 description 1

- 239000011574 phosphorus Substances 0.000 description 1

- 239000004033 plastic Substances 0.000 description 1

- 101150057826 plsC gene Proteins 0.000 description 1

- 229920001721 polyimide Polymers 0.000 description 1

- 239000011241 protective layer Substances 0.000 description 1

- 238000000746 purification Methods 0.000 description 1

- 239000010453 quartz Substances 0.000 description 1

- 230000009467 reduction Effects 0.000 description 1

- 239000003870 refractory metal Substances 0.000 description 1

- 229910052594 sapphire Inorganic materials 0.000 description 1

- 239000010980 sapphire Substances 0.000 description 1

- 229910052706 scandium Inorganic materials 0.000 description 1

- SIXSYDAISGFNSX-UHFFFAOYSA-N scandium atom Chemical compound [Sc] SIXSYDAISGFNSX-UHFFFAOYSA-N 0.000 description 1

- 229910052708 sodium Inorganic materials 0.000 description 1

- 239000011734 sodium Substances 0.000 description 1

- 238000000859 sublimation Methods 0.000 description 1

- 230000008022 sublimation Effects 0.000 description 1

- 239000000126 substance Substances 0.000 description 1

- 230000001360 synchronised effect Effects 0.000 description 1

- XOLBLPGZBRYERU-UHFFFAOYSA-N tin dioxide Chemical compound O=[Sn]=O XOLBLPGZBRYERU-UHFFFAOYSA-N 0.000 description 1

- 229910001887 tin oxide Inorganic materials 0.000 description 1

- 230000001052 transient effect Effects 0.000 description 1

- 230000007704 transition Effects 0.000 description 1

- 229910052724 xenon Inorganic materials 0.000 description 1

- FHNFHKCVQCLJFQ-UHFFFAOYSA-N xenon atom Chemical compound [Xe] FHNFHKCVQCLJFQ-UHFFFAOYSA-N 0.000 description 1

- OYQCBJZGELKKPM-UHFFFAOYSA-N zinc indium(3+) oxygen(2-) Chemical compound [O-2].[Zn+2].[O-2].[In+3] OYQCBJZGELKKPM-UHFFFAOYSA-N 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K5/00—Manipulating of pulses not covered by one of the other main groups of this subclass

- H03K5/01—Shaping pulses

- H03K5/04—Shaping pulses by increasing duration; by decreasing duration

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/04—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being a semiconductor body

- H01L27/08—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being a semiconductor body including only semiconductor components of a single kind

- H01L27/085—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being a semiconductor body including only semiconductor components of a single kind including field-effect components only

- H01L27/088—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being a semiconductor body including only semiconductor components of a single kind including field-effect components only the components being field-effect transistors with insulated gate

- H01L27/092—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being a semiconductor body including only semiconductor components of a single kind including field-effect components only the components being field-effect transistors with insulated gate complementary MIS field-effect transistors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/1222—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs with a particular composition, shape or crystalline structure of the active layer

- H01L27/1233—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs with a particular composition, shape or crystalline structure of the active layer with different thicknesses of the active layer in different devices

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/1237—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs with a different composition, shape, layout or thickness of the gate insulator in different devices

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/1251—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs comprising TFTs having a different architecture, e.g. top- and bottom gate TFTs

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/7869—Thin film transistors, i.e. transistors with a channel being at least partly a thin film having a semiconductor body comprising an oxide semiconductor material, e.g. zinc oxide, copper aluminium oxide, cadmium stannate

Description

じて、入力された信号のパルス幅が変化した信号を生成して出力する回路(パルス変換回

路ともいう)が知られている。

ば特許文献1)。

ること又はインバータを構成するトランジスタの数を増やすことにより、パルス幅を変え

ているため、インバータの回路面積が大きくなり、該パルス変換回路を具備する装置の小

型化を阻害してしまうという問題があった。

パルス変換回路において、P型トランジスタのチャネルが形成される層(チャネル形成層

ともいう)の材料とN型トランジスタのチャネル形成層の材料を異ならせることにより、

入力信号に対する出力信号のパルスの立ち上がりの際の遅延時間と、立ち下がりの際の遅

延時間とを異ならせるものである。

理回路は、ゲートに第1の信号が入力され、ゲートの電圧に応じて第2の信号の電圧を第

1の電圧に設定するか否かを制御するP型トランジスタと、エンハンスメント型であり、

閾値電圧の絶対値がP型トランジスタより大きく、ゲートに第1の信号が入力され、ゲー

トの電圧に応じて第2の信号の電圧を第1の電圧より高い第2の電圧に設定するか否かを

制御するN型トランジスタと、を備え、P型トランジスタは、チャネルが形成され、第1

4族の元素を含有する半導体層を含み、N型トランジスタは、チャネルが形成され、キャ

リア濃度が1×1014/cm3未満である酸化物半導体層を含むパルス変換回路である

。

第2の信号が入力され、第3の信号を出力する第2のインバータと、を具備し、第1のイ

ンバータは、ゲートに第1の信号が入力され、ゲートの電圧に応じて第2の信号の電圧を

第1の電圧に設定するか否かを制御するP型トランジスタと、エンハンスメント型であり

、閾値電圧の絶対値がP型トランジスタより大きく、ゲートに第1の信号が入力され、ゲ

ートの電圧に応じて第2の信号の電圧を第1の電圧より低い第2の電圧に設定するか否か

を制御するN型トランジスタと、を備え、P型トランジスタは、チャネルが形成され、第

14族の元素を含有する半導体層を含み、N型トランジスタは、チャネルが形成され、キ

ャリア濃度が1×1014/cm3未満である酸化物半導体層を含むパルス変換回路であ

る。

第2の信号が入力され、第3の信号を出力する第2のインバータと、を具備し、第2のイ

ンバータは、ゲートに第2の信号が入力され、ゲートの電圧に応じて第3の信号の電圧を

第1の電圧に設定するか否かを制御するP型トランジスタと、エンハンスメント型であり

、閾値電圧の絶対値がP型トランジスタより大きく、ゲートに第2の信号が入力され、ゲ

ートの電圧に応じて第3の信号の電圧を第1の電圧より低い第2の電圧に設定するか否か

を制御するN型トランジスタと、を備え、P型トランジスタは、チャネルが形成され、第

14族の元素を含有する半導体層を含み、N型トランジスタは、チャネルが形成され、キ

ャリア濃度が1×1014/cm3未満である酸化物半導体層を含むパルス変換回路であ

る。

値の電圧に変化することをいい、立ち下がりとは、ある電圧から該電圧より低い値の電圧

に変化することをいう。

トランジスタを用いてパルス変換回路を構成することができるため、パルス変換回路の面

積を低減することができる。

、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくそ

の形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本

発明は以下に示す実施の形態の記載内容に限定して解釈されるものではないとする。

の内容を互いに置き換えることができる。

本実施の形態では、入力信号に対する出力信号の遅延時間が立ち上がりと立ち下がりで異

なるパルス変換回路について説明する。

の形態におけるパルス変換回路の一例を説明するための図である。

図1(A)は、本実施の形態のパルス変換回路の構成例を示す回路図である。

出力する。

レイン、及びゲートを少なくとも有する。

は全部のことをいう。また、ソース電極とソース配線とを区別せずにソース電極及びソー

ス配線の両方の機能を有する導電層をソースという場合がある。

部若しくは全部のことをいう。また、ドレイン電極とドレイン配線とを区別せずにドレイ

ン電極及びドレイン配線の両方の機能を有する導電層をドレインという場合がある。

をいう。また、ゲート電極とゲート配線とを区別せずにゲート電極及びゲート配線の両方

の機能を有する導電層をゲートという場合がある。

、互いに入れ替わる場合がある。

タ101のゲートには、信号S11が入力される。なお、トランジスタ101は、P型ト

ランジスタである。トランジスタ101は、ゲートの電圧に応じて信号S12の電圧を電

圧V11に設定するか否かを制御する機能を有する。

の半導体(シリコンなど)を含有する半導体層を含むトランジスタを用いることができる

。

レインの他方に電気的に接続され、トランジスタ102のソース及びドレインの他方には

、電圧Vbが入力され、トランジスタ102のゲートには、信号S11が入力される。な

お、トランジスタ102は、N型トランジスタである。トランジスタ102は、ゲートの

電圧に応じて信号S12の電圧を電圧V12に設定するか否かを制御する機能を有する。

値がトランジスタ101より大きいトランジスタを用いることができ、例えば酸化物半導

体層を含むトランジスタを用いることができる。上記酸化物半導体層は、チャネルが形成

される層(チャネル形成層ともいう)としての機能を有する。また、上記酸化物半導体層

は、真性(I型ともいう)、又は実質的に真性である半導体層であり、キャリアの数が極

めて少なく、キャリア濃度は、1×1014/cm3未満、好ましくは1×1012/c

m3未満、さらに好ましくは1×1011/cm3未満である。

フ電流は、チャネル幅1μmあたり10aA(1×10−17A)以下、好ましくは1a

A(1×10−18A)以下、さらには好ましくは10zA(1×10−20A)以下、

さらに好ましくは1zA(1×10−21A)以下、さらに好ましくは100yA(1×

10−22A)以下である。

ジスタは、温度が変化した場合であっても、オフ電流が上記の値の範囲内である。例えば

トランジスタの温度が150℃であっても、オフ電流は、100zA/μm以下であるこ

とが好ましい。

及びドレインの他方との電気的接続箇所をノードN11ともいう。

する。つまり、トランジスタ102のソース及びドレインの一方の電圧は、信号S12の

電圧である。

。しかし、電圧及び電位の値は、回路図などにおいていずれもボルト(V)で表されるこ

とがあるため、区別が困難である。そこで、本明細書では、特に指定する場合を除き、あ

る一点の電位と基準となる電位(基準電位ともいう)との電位差を、該一点の電圧として

用いる場合がある。

の他方は、低電源電圧Vssである。高電源電圧Vddは、相対的に低電源電圧Vssよ

り高い値の電圧であり、低電源電圧Vssは、相対的に高電源電圧Vddより低い値の電

圧である。電圧Va及び電圧Vbの値は、例えばトランジスタの極性などにより互いに入

れ替わる場合がある。また、電圧Va及び電圧Vbの差が電源電圧となる。

。図1(B)は、図1(A)に示すパルス変換回路の動作例を説明するためのタイミング

チャートである。なお、ここでは、一例として電圧Vaとして低電源電圧Vssが入力さ

れ、電圧Vbとして高電源電圧Vddが入力されるとする。

タ101がオフ状態になり、トランジスタ102がオン状態になる。

刻T12で立ち上がる。

、トランジスタ102がオフ状態になる。

時刻で立ち下がる。なお、立ち上がりのときにおける信号S12の遅延時間は、立ち下が

りのときにおける信号S12の遅延時間より長い。この理由について、以下に説明する。

値電圧の絶対値がトランジスタ101の閾値電圧の絶対値より大きく、トランジスタ10

2のキャリア濃度がトランジスタ101のキャリア濃度より極めて低い場合、パルス変換

回路において、トランジスタ102がオフ状態からオン状態になる時間が、トランジスタ

101がオフ状態からオン状態になるまでの時間より長くなる。よって、立ち上がりのと

きにおける信号S12の遅延時間は、立ち下がりのときにおける信号S12の遅延時間よ

り長くなる。

れる信号に応じて出力信号の電圧を第1の電圧に設定するか否かを制御するP型トランジ

スタと、チャネル形成層の材料がP型トランジスタと異なり、エンハンスメント型であり

、P型トランジスタより閾値電圧の絶対値が大きく、ゲートに入力される信号に応じて出

力信号の電圧を第2の電圧に設定するか否かを制御するN型トランジスタと、を備える構

成である。上記構成により、2つのトランジスタのみを用いた場合であってもパルス変換

回路を構成することができ、また、同じサイズのトランジスタを用いてパルス変換回路を

構成することもできるため、パルス変換回路の回路面積を低減することができる。

本実施の形態では、複数のインバータを用いたパルス変換回路について説明する。

の形態におけるパルス変換回路の一例を説明するための図である。

図2(A)は、本実施の形態のパルス変換回路の構成例を示す回路図である。

る。なお、これに限定されず、インバータの数は、複数であればよい。

る信号S21に応じて設定される電圧を信号S22として出力する。

る信号S22に応じて設定される電圧を信号S23として出力する。なお、インバータ1

52には、必ずしも信号S22が直接入力されなくてもよい。例えば、別の回路を用いて

信号S22に応じて設定される、別の電圧の信号を生成し、該信号がインバータ152に

入力される構成としてもよい。この場合、信号S23の電圧は、信号S22に応じて設定

される電圧とみなすことができる。

路の構成にすることができる。なお、インバータ151及びインバータ152の一方のみ

の構成を上記実施の形態1に示す論理回路の構成にし、他方の構成を従来のインバータの

構成にすることもできる。このとき、電圧Vaが高電源電圧Vddであり、電圧Vbが低

電源電圧Vssである。

。図2(B)は、図2(A)に示すパルス変換回路の動作例を説明するためのタイミング

チャートである。なお、図2(B)では、一例としてインバータ151が図1(A)に示

す論理回路の構成であり、インバータ152が従来のインバータの構成である場合につい

て示す。

151におけるN型トランジスタにより遅延が生じ、信号S22は、時刻T21よりも遅

い時刻T22で立ち下がる。また、信号S22が時刻T22で立ち下がると、インバータ

152におけるP型トランジスタにより遅延が生じ、信号S23は、時刻T22よりも遅

い時刻で立ち上がる。

ジスタにより遅延が生じ、信号S22は、時刻T23より遅い時刻で立ち上がる。また、

信号S22が立ち上がると、インバータ152におけるN型トランジスタにより遅延が生

じ、信号S23は、時刻T23より遅い時刻で立ち下がる。なお、信号S21に対する信

号S23の遅延時間は、立ち上がり時の方が立ち下がり時より長い。この理由については

、上記実施の形態1にて述べた理由と同じである。

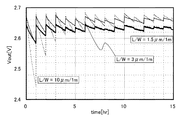

計算ソフトとしてGatewayVer.2.6.12.Rを用いて動作検証を行った。

なお、ここでは、インバータ151及びインバータ152の構成が従来のインバータの構

成である場合(構成1ともいう)、インバータ151の構成が図1(A)に示す論理回路

100の構成であり、インバータ152の構成が従来のインバータの構成である場合(構

成2ともいう)、及びインバータ151の構成が従来のインバータ構成であり、インバー

タ152の構成が図1(A)に示す論理回路100の構成である場合(構成3ともいう)

について、それぞれ動作検証を行った。また、従来のインバータとして、チャネルが形成

されるシリコン半導体層を含むN型トランジスタ及びP型トランジスタにより構成される

CMOSインバータを用いる。また、動作検証では、パルス変換回路における酸化物半導

体層を含むN型トランジスタにおいて、チャネル幅を1μmとし、チャネル長を1μmと

し、閾値電圧を1.58Vとし、S値を100mV/decとし、オフ電流(ゲート及び

ソース間の電圧が0Vのときのソース及びドレイン間の電流)を2.0×10−24Aと

し、オン電流(ゲート及びソース間の電圧が2Vのときのソース及びドレイン間の電流)

を7.8×10−7Aとし、従来のインバータのN型トランジスタにおいて、チャネル幅

を1μmとし、チャネル長を1μmとし、閾値電圧を0.42Vとし、S値を60mV/

decとし、オフ電流(ゲート及びソース間の電圧が0Vのときのソース及びドレイン間

の電流)を3.9×10−12Aとし、オン電流(ゲート及びソース間の電圧が2Vのと

きのソース及びドレイン間の電流)を7.4×10−5Aとし、P型トランジスタにおい

て、チャネル幅を1μmとし、チャネル長を1μmとし、閾値電圧を−0.52Vとし、

S値を90mV/decとし、オフ電流(ゲート及びソース間の電圧が0Vのときのソー

ス及びドレイン間の電流)を8.2×10−12Aとし、オン電流(ゲート及びソース間

の電圧が−2Vのときのソース及びドレイン間の電流)を7.3×10−5Aとした。ま

た、動作検証では、信号S21の振幅を0V〜2Vとし、電源電圧を2Vとした。

動作検証結果を示す図である。

は、構成2の信号S21及び信号S23の電圧波形を示しており、図3(C)は、構成3

の信号S21及び信号S23の電圧波形を示している。図3(A)乃至図3(C)に示す

ように、構成1では、信号S23の立ち上がり及び立ち下がりにおいて遅延時間は短い。

これに対し、構成2では、信号S23の立ち上がりの遅延時間が立ち下がりの遅延時間よ

り長く、構成3では、信号S23の立ち下がりの遅延時間が立ち上がり時間の遅延時間よ

り長いことがわかる。

インバータ及び第2のインバータを少なくとも備え、第1のインバータ及び第2のインバ

ータの一方が、ゲートに入力される信号に応じて出力信号の電圧を第1の電圧に設定する

か否かを制御するP型トランジスタと、チャネル形成層の材料がP型トランジスタと異な

り、エンハンスメント型であり、P型トランジスタより閾値電圧の絶対値が大きく、ゲー

トに入力される信号に応じて出力信号の電圧を第2の電圧に設定するか否かを制御するN

型トランジスタと、を備える構成である。上記構成により、少なくとも2つのインバータ

を用いてパルス変換回路を構成することができるため、出力信号の電圧を電源電圧以上に

することができ、且つ同じサイズのトランジスタを用いてパルス変換回路を構成すること

もできるため、パルス変換回路の回路面積を低減することができる。

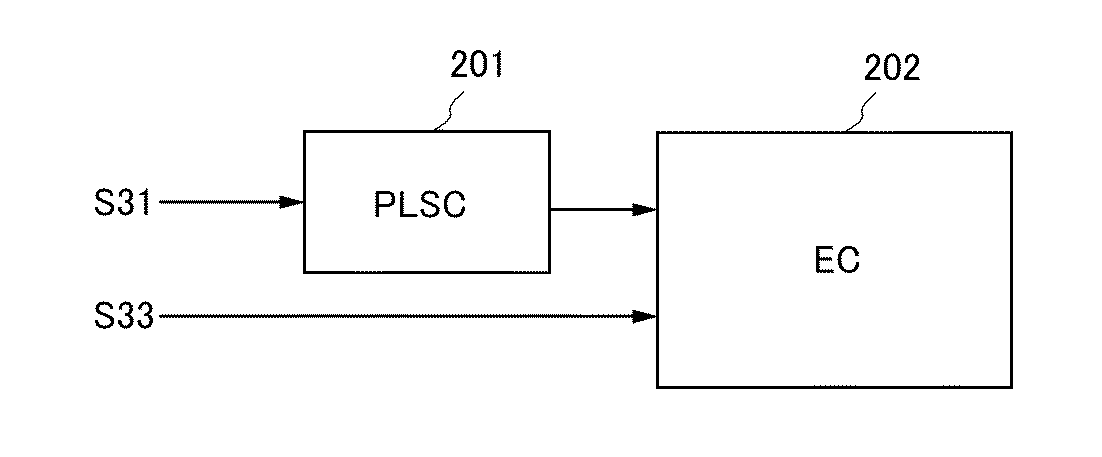

本実施の形態では、上記実施の形態のパルス変換回路を用いた電子回路について説明する

。

における電子回路の構成例を示すブロック図である。

ともいう)202と、を具備する。

れる信号S31に応じて設定される電圧を信号S32として出力する機能を有する。

変換回路を用いることができる。

される信号S32及び信号S33に応じて動作することにより、特定の機能を有する回路

である。

できる。

。

が、これに限定されず、信号S33が入力されるバッファ回路などを設け、信号S33に

応じて設定されるバッファ回路の出力信号が機能回路202に入力される構成としてもよ

い。

。図5は、本実施の形態における記憶回路を説明するための図である。

A)は、本実施の形態における記憶回路の構成例を示すブロック図である。

動回路(XDRVともいう)213xと、第2の駆動回路(YDRVともいう)213y

と、複数のパルス変換回路213wと、駆動制御回路(DCTLともいう)213vと、

を具備する。

られる領域を記憶部(MCAともいう)212という。

第1の駆動回路213xは、入力された行アドレス信号に従って1行以上の単位記憶回路

211を選択し、選択した単位記憶回路211に選択信号を出力する機能を有する。第1

の駆動回路213xは、例えばデコーダを用いて構成される。デコーダは、行毎に単位記

憶回路211を選択する機能を有する。

が入力される。第2の駆動回路213yは、入力される列アドレス信号に従って1列以上

の単位記憶回路211を選択し、選択した単位記憶回路211にデータ信号を出力する機

能を有する。また、第2の駆動回路213yは、読み出し信号(信号READともいう)

を出力し、読み出し信号により選択した単位記憶回路211に記憶されたデータを読み出

す機能を有する。第2の駆動回路213yは、例えばデコーダ、複数のアナログスイッチ

、読み出し信号出力回路、及び読み出し回路を用いて構成される。デコーダは、列毎に単

位記憶回路211を選択する機能を有し、複数のアナログスイッチは、デコーダから入力

される信号に応じてデータ信号を出力するか否かを制御する機能を有し、読み出し信号出

力回路は、読み出し信号を生成して出力する機能を有し、読み出し回路は、読み出し信号

により選択した単位記憶回路211に記憶されたデータを読み出す機能を有する。なお、

読み出し信号の電圧は、書き込み信号の電圧より低くすることができる。

入力される。駆動制御回路213vは、入力される書き込み制御信号、読み出し制御信号

、及びアドレス信号に応じて、第1の駆動回路213x及び第2の駆動回路213yの動

作を制御する信号を生成して出力する機能を有する。例えば、駆動制御回路213vは、

アドレス信号に応じて複数の行アドレス信号を第1の駆動回路213xに出力し、複数の

列アドレス信号を第2の駆動回路213yに出力する機能を有する。

なお、複数のパルス変換回路213wの数は、入力される行アドレス信号又は列アドレス

信号と同じ数である。また、複数のパルス変換回路213wのそれぞれに入力される行ア

ドレス信号又は列アドレス信号は、互いに異なる信号である。パルス変換回路213wは

、入力される信号のパルス幅を変換する機能を有する。パルス変換回路213wとして上

記実施の形態のパルス変換回路を用いることができる。例えば、行アドレス信号のパルス

幅を変換する場合には、上記実施の形態2における構成2のパルス変換回路を用いること

ができ、列アドレス信号のパルス幅を変換する場合には、上記実施の形態2における構成

3のパルス変換回路を用いることができる。

)は、単位記憶回路の構成例を示す回路図である。

スタ233と、を備える。

スタ231のゲートには、選択信号が入力される。トランジスタ231は、選択用トラン

ジスタとしての機能を有する。

理回路のN型トランジスタに適用可能なトランジスタを用いることができる。

、読み出し信号が入力され、容量素子232の第2の電極は、トランジスタ231のソー

ス及びドレインの他方に電気的に接続される。容量素子232は、保持容量としての機能

を有する。

タ233のソース及びドレインの他方の電圧が読み出されるデータ信号の電圧となり、ト

ランジスタ233のゲートは、トランジスタ231のソース及びドレインの他方に電気的

に接続される。なお、トランジスタ233のゲートと、容量素子232の第2の電極及び

トランジスタ231のソース及びドレインの他方との電気的接続箇所をノードN41とも

いう。また、電圧Vcは、所定の値の電圧である。また、トランジスタ233は、出力用

トランジスタとしての機能を有する。

の半導体(シリコンなど)を含有する半導体層を含むトランジスタを用いることができる

。

図5(C)は、図5(B)に示す単位記憶回路の動作例を説明するためのタイミングチャ

ートである。

ス信号のパルスに従って選択信号がトランジスタ231のゲートに入力され、選択信号に

従ってトランジスタ231がオン状態になり、列アドレス信号のパルスに従ってデータ信

号が単位記憶回路に入力される。このとき、ノードN41の電圧がデータ信号に応じた値

になり、単位記憶回路は、書き込み状態になる(状態WRTともいう)。

が変化し始めた後に行アドレス信号が変化し始める。よって、単位記憶回路が選択される

前に、選択される単位記憶回路に書き込むためのデータ信号を設定することができる。

示すように、読み出し信号のパルスに従って、ノードN41の電圧が変化する。さらに、

変化後のノードN41の電圧に応じてトランジスタ233がオン状態又はオフ状態になり

、トランジスタ233のソース及びドレインの他方の電圧をデータ信号として読み出す。

このとき、単位記憶回路は、読み出し状態(状態RDともいう)になる。以上が図5(B

)に示す単位記憶回路の動作例である。

アドレス信号の一方の信号のパルス幅をパルス変換回路により変化させる構成である。上

記構成にすることにより、回路面積を小さくすることができる。また、上記構成にするこ

とにより、行アドレス信号が変化する前に列アドレス信号を変化させることができるため

、所望のデータ以外のデータが単位記憶回路に書き込まれてしまうといった動作不良を抑

制することができる。

本実施の形態では、上記実施の形態3の記憶回路を備えた半導体装置の一例として、無線

通信によりデータ通信が可能な半導体装置について説明する。

実施の形態における半導体装置の構成例を示すブロック図である。

Gともいう)302と、復調回路(DMODともいう)303と、記憶制御回路(MCT

Lともいう)304と、記憶回路(MEMORYともいう)305と、符号化回路(EN

CDともいう)306と、変調回路(MODともいう)307と、を具備する。図6に示

す半導体装置は、無線通信装置(リーダライタ、または質問器など、無線により通信が可

能なもの)などの外部の回路とアンテナ回路301を介して無線信号の送受信を行う。

を生成する機能を有する。

る機能を有する。

号、及びアドレス信号などのアクセス信号を生成する機能を有する。

ead Only Memory)及びRAM(Random Access Memo

ry)の一つ又は複数を用いることができる。

する。

して送信するためのデータ信号を生成する機能を有する。

送波に応じて電圧が生成される。

れる。

成した電源電圧を、復調回路303、記憶制御回路304、記憶回路305、符号化回路

306、及び変調回路307に出力する。

タ信号を抽出し、抽出したデータ信号を記憶制御回路304に出力する。

出しを行う。

る。

送信する搬送波を変調する。以上が図6に示す半導体装置の動作の一例である。

が可能な半導体装置である。上記半導体装置に上記実施の形態の記憶回路を用いることに

より、回路面積が小さく、信頼性の高い半導体装置を提供することができる。

本実施の形態では、上記実施の形態に示すパルス変換回路、記憶回路、又は半導体装置に

おける酸化物半導体層を含むトランジスタに適用可能なトランジスタについて説明する。

性(I型ともいう)、又は実質的に真性にさせた酸化物半導体層を有するトランジスタで

ある。高純度化とは、酸化物半導体層中の水素を極力排除すること、及び酸化物半導体層

に酸素を供給して酸化物半導体層中の酸素欠乏に起因する欠陥を低減することの少なくと

も一方を含む概念である。

の形態におけるトランジスタの構造例を示す断面模式図である。

タガ型トランジスタともいう。

層403aと、導電層405aと、導電層406aと、を含む。

上に設けられ、酸化物半導体層403aは、絶縁層402aを介して導電層401aの上

に設けられ、導電層405a及び導電層406aは、酸化物半導体層403aの一部の上

にそれぞれ設けられる。

面に導電層405a及び導電層406aが設けられていない部分)は、酸化物絶縁層40

7aに接する。

ネルストップ型ともいう)トランジスタであり、逆スタガ型トランジスタともいう。

層403bと、絶縁層427と、導電層405bと、導電層406bと、を含む。

上に設けられ、酸化物半導体層403bは、絶縁層402bを介して導電層401bの上

に設けられ、絶縁層427は、絶縁層402b及び酸化物半導体層403bを介して導電

層401bの上に設けられ、導電層405b及び導電層406bは、絶縁層427を介し

て酸化物半導体層403bの一部の上にそれぞれ設けられる。また、導電層401bを酸

化物半導体層403bの全てと重なる構造にすることもできる。導電層401bを酸化物

半導体層403bの全てと重なる構造にすることにより、酸化物半導体層403bへの光

の入射を抑制することができる。また、これに限定されず、導電層401bを酸化物半導

体層403bの一部と重なる構造にすることもできる。

層403cと、導電層405cと、導電層406cと、を含む。

上に設けられ、導電層405c及び導電層406cは、絶縁層402cの一部の上に設け

られ、酸化物半導体層403cは、絶縁層402c、導電層405c、及び導電層406

cを介して導電層401cの上に設けられる。また、導電層401cを酸化物半導体層4

03cの全てと重なる構造にすることもできる。導電層401cを酸化物半導体層403

cの全てと重なる構造にすることにより、酸化物半導体層403cへの光の入射を抑制す

ることができる。また、これに限定されず、導電層401cを酸化物半導体層403cの

一部と重なる構造にすることもできる。

側面は、酸化物絶縁層407cに接する。

い。

層403dと、導電層405d及び導電層406dと、を含む。

405d及び導電層406dは、それぞれ酸化物半導体層403dの一部の上に設けられ

、絶縁層402dは、酸化物半導体層403d、導電層405d、及び導電層406dの

上に設けられ、導電層401dは、絶縁層402dを介して酸化物半導体層403dの上

に設けられる。

ウケイ酸ガラスなどのガラス基板を用いることができる。

ア基板などの絶縁体でなる基板を用いることもできる。また、基板400a乃至基板40

0dとして、結晶化ガラスを用いることもできる。また、基板400a乃至基板400d

として、プラスチック基板を用いることもできる。また、基板400a乃至基板400d

として、シリコンなどの半導体基板を用いることもできる。

層としての機能を有する。絶縁層447としては、例えば窒化シリコン層、酸化シリコン

層、窒化酸化シリコン層、酸化窒化シリコン層、酸化アルミニウム層、又は酸化窒化アル

ミニウム層を用いることができる。また、絶縁層447に適用可能な材料の層の積層によ

り絶縁層447を構成することもできる。また、絶縁層447として、遮光性を有する材

料の層と、上記絶縁層447に適用可能な材料の層との積層を用いることもできる。また

、遮光性を有する材料の層を用いて絶縁層447を構成することにより、酸化物半導体層

403dへの光の入射を抑制することができる。

ジスタと同様に、基板とゲート電極としての機能を有する導電層の間に絶縁層を設けても

よい。

能を有する。導電層401a乃至導電層401dとしては、例えばモリブデン、チタン、

クロム、タンタル、タングステン、アルミニウム、銅、ネオジム、若しくはスカンジウム

などの金属材料、又はこれらを主成分とする合金材料の層を用いることができる。また、

導電層401a乃至導電層401dの形成に適用可能な材料の層の積層により、導電層4

01a乃至導電層401dを構成することもできる。

機能を有する。絶縁層402a乃至絶縁層402dとしては、例えば酸化シリコン層、窒

化シリコン層、酸化窒化シリコン層、窒化酸化シリコン層、酸化アルミニウム層、窒化ア

ルミニウム層、酸化窒化アルミニウム層、窒化酸化アルミニウム層、又は酸化ハフニウム

層を用いることができる。また、絶縁層402a乃至絶縁層402dに適用可能な材料の

層の積層により絶縁層402a乃至絶縁層402dを構成することもできる。絶縁層40

2a乃至絶縁層402dに適用可能な材料の層は、例えばプラズマCVD法又はスパッタ

リング法などを用いて形成される。例えば、プラズマCVD法により窒化シリコン層を形

成し、プラズマCVD法により窒化シリコン層の上に酸化シリコン層を形成することによ

り絶縁層402a乃至絶縁層402dを構成することができる。

ネル形成層としての機能を有する。酸化物半導体層403a乃至酸化物半導体層403d

に適用可能な酸化物半導体としては、例えば四元系金属酸化物、三元系金属酸化物、又は

二元系金属酸化物などを用いることができる。四元系金属酸化物としては、例えばIn−

Sn−Ga−Zn−O系金属酸化物などを用いることができる。三元系金属酸化物として

は、例えばIn−Ga−Zn−O系金属酸化物、In−Sn−Zn−O系金属酸化物、I

n−Al−Zn−O系金属酸化物、Sn−Ga−Zn−O系金属酸化物、Al−Ga−Z

n−O系金属酸化物、又はSn−Al−Zn−O系金属酸化物などを用いることができる

。二元系金属酸化物としては、例えばIn−Zn−O系金属酸化物、Sn−Zn−O系金

属酸化物、Al−Zn−O系金属酸化物、Zn−Mg−O系金属酸化物、Sn−Mg−O

系金属酸化物、In−Mg−O系金属酸化物、又はIn−Sn−O系金属酸化物などを用

いることができる。また、酸化物半導体としては、例えばIn−O系金属酸化物、Sn−

O系金属酸化物、又はZn−O系金属酸化物などを用いることもできる。また、酸化物半

導体としては、上記酸化物半導体として適用可能な金属酸化物にSiO2を含む酸化物を

用いることもできる。

n=1:2(モル数比に換算するとIn2O3:ZnO=25:1乃至In2O3:Zn

O=1:4)、好ましくはIn:Zn=20:1乃至In:Zn=1:1(モル数比に換

算するとIn2O3:ZnO=10:1乃至In2O3:ZnO=1:2)、さらに好ま

しくはIn:Zn=15:1乃至In:Zn=1.5:1(モル数比に換算するとIn2

O3:ZnO=15:2乃至In2O3:ZnO=3:4)の組成比である酸化物ターゲ

ットを用いてIn−Zn−O系金属酸化物の半導体層を形成することができる。例えば、

In−Zn−O系酸化物半導体の形成に用いるターゲットは、原子数比がIn:Zn:O

=P:Q:Rのとき、R>1.5P+Qとする。Inの量を多くすることにより、トラン

ジスタの移動度を向上させることができる。

る材料を用いることができる。ここで、Mは、Ga、Al、Mn、及びCoから選ばれた

一つ又は複数の金属元素を示す。例えばMとしては、Ga、Ga及びAl、Ga及びMn

、又はGa及びCoなどが挙げられる。

、トランジスタのソース電極又はトランジスタのドレイン電極としての機能を有する。導

電層405a乃至導電層405d及び導電層406a乃至導電層406dとしては、例え

ばアルミニウム、クロム、銅、タンタル、チタン、モリブデン、若しくはタングステンな

どの金属材料、又はこれらの金属材料を主成分とする合金材料の層を用いることができる

。また、導電層405a乃至導電層405d、及び導電層406a乃至導電層406dに

適用可能な材料の層の積層により導電層405a乃至導電層405d、及び導電層406

a乃至導電層406dのそれぞれを構成することができる。

高融点金属層との積層により導電層405a乃至導電層405d及び導電層406a乃至

導電層406dを構成することができる。また、複数の高融点金属層の間にアルミニウム

又は銅の金属層が設けられた積層により導電層405a乃至導電層405d、及び導電層

406a乃至導電層406dを構成することもできる。また、ヒロックやウィスカーの発

生を防止する元素(Si、Nd、Scなど)が添加されているアルミニウム層を用いて導

電層405a乃至導電層405d、及び導電層406a乃至導電層406dを構成するこ

とにより、耐熱性を向上させることができる。

、導電性の金属酸化物を含む層を用いることもできる。導電性の金属酸化物としては、例

えば酸化インジウム(In2O3)、酸化スズ(SnO2)、酸化亜鉛(ZnO)、酸化

インジウム酸化スズ合金(In2O3―SnO2、ITOと略記する)、若しくは酸化イ

ンジウム酸化亜鉛合金(In2O3―ZnO)、又はこれらの金属酸化物に酸化シリコン

を含むものを用いることができる。

に用いられる材料を用いて他の配線を形成してもよい。

)としての機能を有する。絶縁層427としては、例えば絶縁層447に適用可能な材料

の層を用いることができる。また、絶縁層427に適用可能な材料の層の積層により絶縁

層427を構成することもできる。

でき、例えば酸化シリコン層などを用いることができる。また、酸化物絶縁層407a及

び酸化物絶縁層407cに適用可能な材料の層の積層により酸化物絶縁層407a及び酸

化物絶縁層407cを構成することもできる。

ジスタの作製方法例について、図8(A)乃至図8(D)を用いて説明する。図8(A)

乃至図8(D)は、図7(A)に示すトランジスタの作製方法例を説明するための断面模

式図である。

を選択的にエッチングすることにより導電層401aを形成する(図8(A)参照)。

マスクを形成し、第1のレジストマスクを用いて第1の導電膜をエッチングすることによ

り導電層401aを形成することができる。なお、この場合、導電層401aの形成後に

第1のレジストマスクを除去する。

きる。また、第1の導電膜に適用可能な材料の膜を積層させ、第1の導電膜を形成するこ

ともできる。

用いることにより、フォトマスクが不要になるため、製造コストを低減することができる

。また、多階調マスクを用いてレジストマスクを形成してもよい。多階調マスクは、透過

した光が複数の強度となる露光マスクである。多階調マスクを用いることにより、膜厚の

異なる部分を有するレジストマスクを形成することができるため、一つのレジストマスク

を用いて複数種のエッチングを連続して行うことができるため、製造コストを低減するこ

とができる。

、絶縁層402aの上に酸化物半導体膜を形成し、その後酸化物半導体膜のエッチング及

び第1の加熱処理を行うことにより酸化物半導体層403aを形成する(図8(B)参照

)。

ができる。例えば、高密度プラズマCVD法(例えばμ波(例えば、周波数2.45GH

zのμ波)を用いた高密度プラズマCVD法)を用いて第1の絶縁膜を形成することによ

り、絶縁層402aを緻密にすることができ、絶縁層402aの絶縁耐圧を向上させるこ

とができる。

る。また、第1の絶縁膜に適用可能な材料の膜を積層させ、第1の絶縁膜を形成すること

もできる。

き、希ガス雰囲気下、酸素雰囲気下、又は希ガスと酸素の混合雰囲気下で酸化物半導体膜

を形成してもよい。

形成することができる。

化物ターゲットを用いて酸化物半導体膜を形成することができる。また、例えば、In2

O3:Ga2O3:ZnO=1:1:2[mol数比]の組成比である酸化物ターゲット

を用いて酸化物半導体膜を形成してもよい。なお、用いられる酸化物ターゲットにおける

、全体の体積に対して全体の体積から空隙などが占める空間を除いた部分の体積の割合(

充填率ともいう)は、90%以上100%以下、さらには95%以上99.9%以下であ

ることが好ましい。充填率の高いターゲットを用いることにより、緻密な酸化物半導体膜

を形成することができる。

が除去された高純度ガスを用いて酸化物半導体膜を形成することが好ましい。

とにより、絶縁層402a及び酸化物半導体膜の水素、水分などの不純物を脱離すること

ができる。また、予備加熱室にて上記予備加熱を行う場合、予備加熱室に設ける排気手段

として例えばクライオポンプを用いることが好ましい。

好ましくは200℃以上400℃以下として酸化物半導体膜を形成してもよい。基板40

0aを加熱することにより、酸化物半導体膜の不純物濃度を低減することができ、また、

スパッタリング法による酸化物半導体膜の損傷を軽減することができる。

水分を除去することができる。吸着型の真空ポンプとしては、例えばクライオポンプ、イ

オンポンプ、又はチタンサブリメーションポンプなどを用いることができる。また、ター

ボポンプにコールドトラップを加えたものを用いて成膜室内の残留水分を除去することも

できる。

表面に付着している粉状物質(パーティクル、ごみともいう)を除去することが好ましい

。逆スパッタとは、アルゴン、窒素、ヘリウム、又は酸素雰囲気下で、ターゲット側に電

圧を印加せずに、基板側にRF電源を用いて電圧を印加し、プラズマを形成して基板の表

面を改質する方法である。

レジストマスクを形成し、第2のレジストマスクを用いて酸化物半導体膜をエッチングす

ることができる。なお、この場合酸化物半導体膜のエッチング後に第2のレジストマスク

を除去する。

ェットエッチングの両方を用いて酸化物半導体膜をエッチングすることができる。また、

例えば燐酸と酢酸と硝酸を混ぜた溶液などをエッチング液として用いることにより酸化物

半導体膜をエッチングすることができる。また、エッチング液としてITO07N(関東

化学社製)を用いて酸化物半導体膜をエッチングしてもよい。

1の加熱処理を行う。第1の加熱処理により脱水化又は脱水素化を行うことができる。

の熱伝導又は熱輻射により被処理物を加熱する装置を用いることができ、例えばGRTA

(Gas Rapid Thermal Anneal)装置又はLRTA(Lamp

Rapid Thermal Anneal)装置などのRTA(Rapid Ther

mal Anneal)装置を用いることができる。LRTA装置は、例えばハロゲンラ

ンプ、メタルハライドランプ、キセノンアークランプ、カーボンアークランプ、高圧ナト

リウムランプ、又は高圧水銀ランプなどのランプから発する光(電磁波)の輻射により、

被処理物を加熱する装置である。また、GRTA装置は、高温のガスを用いて加熱処理を

行う装置である。高温のガスとしては、例えば希ガス、又は加熱処理によって被処理物と

反応しない不活性気体(例えば窒素)を用いることができる。

熱する方式のGRTAを行ってもよい。

ガスの純度を、6N(99.9999%)以上、好ましくは7N(99.99999%)

以上、すなわち不純物濃度を1ppm以下、好ましくは0.1ppm以下とすることが好

ましい。

その加熱温度から降温する過程で、第1の加熱処理を行った炉と同じ炉に高純度の酸素ガ

ス、高純度のN2Oガス、又は超乾燥エア(露点が−40℃以下、好ましくは−60℃以

下の雰囲気)を導入してもよい。このとき、酸素ガス又はN2Oガスは、水、水素などを

含まないことが好ましい。また、加熱処理装置に導入する酸素ガス又はN2Oガスの純度

を、6N以上、好ましくは7N以上、すなわち、酸素ガス又はN2Oガス中の不純物濃度

を1ppm以下、好ましくは0.1ppm以下とすることが好ましい。酸素ガス又はN2

Oガスの作用により、酸化物半導体層403aに酸素が供給され、酸化物半導体層403

aを高純度化させることができる。

理を行ってもよい。また、酸化物半導体膜を形成し、第1の加熱処理を行った後に酸化物

半導体膜のエッチングを行ってもよい。

電層405a及び導電層406aを形成した後、又は導電層405a及び導電層406a

の上に酸化物絶縁層407aを形成した後に第1の加熱処理を行ってもよい。

加熱処理を行うことにより、膜表面に対して垂直にc軸配向した結晶領域を有する酸化物

半導体膜を形成してもよい。例えば、膜厚が3nm以上15nm以下の第1の酸化物半導

体膜を成膜し、さらに第1の加熱処理として、窒素、酸素、希ガス、又は乾燥エアの雰囲

気下で450℃以上850℃以下、好ましくは550℃以上750℃以下の加熱処理を行

い、表面を含む領域に結晶領域(板状結晶を含む)を有する第1の酸化物半導体膜を形成

する。そして、第1の酸化物半導体膜よりも厚い第2の酸化物半導体膜を形成する。さら

に第2の加熱処理として、450℃以上850℃以下、好ましくは600℃以上700℃

以下の加熱処理を行い、第1の酸化物半導体膜を結晶成長の種として、第1の酸化物半導

体膜から第2の酸化物半導体膜にかけて上方に向かって結晶成長させ、第2の酸化物半導

体膜の全体を結晶化させることにより、膜表面に対して垂直にc軸配向した結晶領域を有

する酸化物半導体膜を形成することができる。上記酸化物半導体膜は、1層のみの酸化物

半導体膜を形成する場合と比較して膜厚が厚い。

導電膜を選択的にエッチングすることにより導電層405a及び導電層406aを形成す

る(図8(C)参照)。

マスクを形成し、第3のレジストマスクを用いて第2の導電膜をエッチングすることによ

り導電層405a及び導電層406aを形成することができる。なお、この場合導電層4

05a及び導電層406aの形成後に第3のレジストマスクを除去する。

を形成することができる。また、第2の導電膜に適用可能な材料の膜を積層させ、第2の

導電膜を形成することもできる。

ン、若しくはタングステンなどの金属材料、又はこれらの金属材料を主成分とする合金材

料の膜を用いることができる。また、第2の導電膜に適用可能な膜の積層膜により第2の

導電膜を形成することができる。

マスクを形成することが好ましい。酸化物半導体層403aの上で隣り合う導電層405

aの下端部と導電層406aの下端部との間隔幅により、後に形成されるトランジスタの

チャネル長Lが決定される。なお、第3のレジストマスクの形成の際にチャネル長L=2

5nm未満となるように露光を行う場合には、数nm〜数10nmと極めて波長が短い超

紫外線(Extreme Ultraviolet)を用いて露光を行うとよい。超紫外

線による露光は、解像度が高く焦点深度も大きい。従って、後に形成されるトランジスタ

のチャネル長Lを10nm以上1000nm以下とすることができる。

。上記予備加熱は、上記予備加熱と同様に行うことができる。

合雰囲気下で、水又は水素などの不純物が混入しない方法(例えばスパッタリング法など

)を用いて酸化物半導体層403a、導電層405a、及び導電層406aの上に第2の

絶縁膜を形成することにより酸化物絶縁層407aを形成することができる。水又は水素

などの不純物が混入しない方法を用いて酸化物絶縁層407aを形成することにより、酸

化物半導体層のバックチャネルの抵抗の低下を抑制することができる。また、酸化物絶縁

層407a形成時の基板温度は、室温以上300℃以下であることが好ましい。

を形成することができる。例えば、シリコンターゲットを用い、酸素を含む雰囲気下でス

パッタリング法により、第2の絶縁膜として酸化シリコン膜を形成することができる。

が除去された高純度ガスを用いて第2の絶縁膜を形成することが好ましい。

プラズマ処理を行い、露出している酸化物半導体層403aの表面に付着した吸着水など

を除去してもよい。プラズマ処理を行った場合、その後、大気に触れることなく、酸化物

絶縁層407aを形成することが好ましい。

下で第2の加熱処理(好ましくは200℃以上400℃以下、例えば250℃以上350

℃以下)を行ってもよい。例えば、第2の加熱処理として、窒素雰囲気下で250℃、1

時間の加熱処理を行う。第2の加熱処理を行うと、酸化物半導体層403aの上面の一部

が酸化物絶縁層407aと接した状態で加熱される。

う)などの不純物を酸化物半導体層から意図的に排除し、且つ酸素を酸化物半導体層に供

給することができる。よって、酸化物半導体層は高純度化する。

コン層形成後の第2の加熱処理によって酸化物半導体層403a中に含まれる水素、水分

、水酸基、又は水素化物などの不純物を酸化物絶縁層407aに拡散させ、酸化物半導体

層403a中に含まれる該不純物をより低減させる効果を奏する。

パッタリング法を用いて絶縁膜を形成することにより保護絶縁層を形成する。RFスパッ

タリング法は、量産性がよいため、保護絶縁層の成膜方法として好ましい。以上が図7(

A)に示すトランジスタの作製方法の一例である。

処理を行ってもよい。例えば2.45GHzの高密度プラズマにより酸素ドーピング処理

を行ってもよい。なお、ゲート絶縁層としての機能を有する絶縁層形成後、酸化物半導体

膜成膜後、第1の加熱処理後、ソース電極又はドレイン電極としての機能を有する導電層

形成後、又は酸化物絶縁層形成後に酸素ドーピング処理を行うことができる。酸素ドーピ

ング処理を行うことにより作製されるトランジスタの電気特性のばらつきを低減すること

ができる。

例えば図7(B)乃至図7(D)に示す各構成要素において、名称が図7(A)に示す各

構成要素と同じであり且つ機能の少なくとも一部が図7(A)に示す各構成要素と同じで

あれば、図7(A)に示すトランジスタの作製方法の一例の説明を適宜援用することがで

きる。

ての機能を有する第1の導電層と、ゲート絶縁層としての機能を有する絶縁層と、絶縁層

を介して第1の導電層に重畳し、チャネルが形成される酸化物半導体層と、酸化物半導体

層に電気的に接続され、ソース電極及びドレイン電極の一方としての機能を有する第2の

導電層と、酸化物半導体層に電気的に接続され、ソース電極及びドレイン電極の他方とし

ての機能を有する第3の導電層と、を含み、該酸化物半導体層は、酸化物絶縁層に接する

構造である。

的にI型となった酸化物半導体層である。酸化物半導体層を高純度化させることにより、

酸化物半導体層のキャリア濃度を1×1014/cm3未満、好ましくは1×1012/

cm3未満、さらに好ましくは1×1011/cm3未満にすることができ、温度変化に

よる特性変化を抑制することができる。また、上記構造にすることにより、チャネル幅1

μmあたりのオフ電流を10aA(1×10−17A)以下にすること、さらにはチャネ

ル幅1μmあたりのオフ電流を1aA(1×10−18A)以下、さらにはチャネル幅1

μmあたりのオフ電流を10zA(1×10−20A)以下、さらにはチャネル幅1μm

あたりのオフ電流を1zA(1×10−21A)以下、さらには100yA(1×10−

22A)以下にすることができる。トランジスタのオフ電流は、低ければ低いほどよいが

、本実施の形態のトランジスタのオフ電流の下限値は、約10−30A/μmであると見

積もられる。

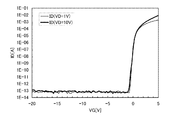

(ゲート及びソースの間の電圧(電圧VGともいう)とソース及びドレインの間の電流(

電流ID)との関係)を図9に示す。なお、測定において、基板温度を室温とし、ソース

−ドレイン間電圧(以下、ドレイン電圧または電圧VDという)を1V又は10Vとし、

ゲート及びソースの間の電圧を−20V〜+20Vとした。

ト型になり、該トランジスタでは、ドレイン電圧が1V及び10Vにおけるオフ電流が1

×10−13[A]以下であり、測定機(半導体パラメータ・アナライザ、Agilen

t 4156C;Agilent社製)の分解能(100fA)以下となっている。

タの一例のオフ電流の値の算出例について以下に説明する。

回路の構成を示す回路図である。

互いに並列に接続される。ここでは、一例として8個の測定系801が並列に接続される

構成とする。

ランジスタ814と、トランジスタ815と、を含む。

タ811のゲートには、電圧Vext_aが入力される。トランジスタ811は、電荷注

入用のトランジスタである。

レインの他方に接続され、トランジスタ812のソース及びドレインの他方には、電圧V

2が入力され、トランジスタ812のゲートには、電圧Vext_bが入力される。トラ

ンジスタ812は、リーク電流評価用のトランジスタである。なお、ここでのリーク電流

とは、トランジスタのオフ電流を含むリーク電流である。

され、容量素子813の第2の電極には、電圧V2が入力される。ここでは、電圧V2と

して0Vが入力される。

タ814のゲートは、トランジスタ811のソース及びドレインの他方に接続される。な

お、トランジスタ814のゲートと、トランジスタ811のソース及びドレインの他方、

トランジスタ812のソース及びドレインの一方、並びに容量素子813の第1の電極と

の接続箇所をノードAともいう。

レインの他方に接続され、トランジスタ815のソース及びドレインの他方には、電圧V

4が入力され、トランジスタ815のゲートには、電圧Vext_cが入力される。なお

、ここでは、電圧Vext_cとして0.5Vが入力される。

スタ815のソース及びドレインの一方との接続箇所の電圧を出力電圧Voutとして出

力する。

0μm、チャネル幅W=10μmのトランジスタを用いる。また、トランジスタ814及

びトランジスタ815の一例として、酸化物半導体層を含み、チャネル長L=3μm、チ

ャネル幅W=100μmのトランジスタを用いる。また、トランジスタ812の一例とし

て、酸化物半導体層を含み、酸化物半導体層の上部にソース電極及びドレイン電極が接し

、ソース電極及びドレイン電極と、ゲート電極とのオーバーラップ領域を設けず、幅1μ

mのオフセット領域を有するボトムゲート構造のトランジスタを用いる。オフセット領域

を設けることにより、寄生容量を低減することができる。さらにトランジスタ812とし

ては、チャネル長L及びチャネル幅Wの異なる6条件のトランジスタを用いる(表1参照

)。

を別々に設けることにより、電荷注入の際に、リーク電流評価用のトランジスタを常にオ

フ状態に保つことができる。電荷注入用のトランジスタを設けない場合には、電荷注入の

際に、リーク電流評価用トランジスタを一度オン状態にする必要があるが、オン状態から

オフ状態の定常状態に到るまでに時間を要するような素子では、測定に時間を要してしま

う。

ことにより、それぞれのトランジスタを適切なサイズとすることができる。また、リーク

電流評価用トランジスタのチャネル幅Wを、電荷注入用のトランジスタのチャネル幅Wよ

りも大きくすることにより、リーク電流評価用トランジスタのリーク電流以外の特性評価

回路のリーク電流成分を相対的に小さくすることができる。その結果、リーク電流評価用

トランジスタのリーク電流を高い精度で測定することができる。同時に、電荷注入の際に

、リーク電流評価用トランジスタを一度オン状態とする必要がないため、リーク電流評価

用トランジスタのチャネル形成領域の電荷の一部がノードAに流れ込むことによるノード

Aの電圧変動の影響もない。

ネル幅Wよりも小さくすることにより、電荷注入用トランジスタのリーク電流を相対的に

小さくすることができる。また、電荷注入の際に、電荷注入用トランジスタのチャネル形

成領域の電荷の一部がノードAに流れ込むことによるノードAの電圧変動の影響も小さい

。

正確に特性評価回路のリーク電流を算出することができる。

流の値の算出方法について説明する。

る。図11は、図10に示す特性評価回路を用いたリーク電流測定方法を説明するための

タイミングチャートである。

分けられる。それぞれの期間における動作について、以下に説明する。

となるような電圧VL(−3V)を入力する。また、電圧V1として、書き込み電圧Vw

を入力した後、電圧Vext_aとして、一定期間トランジスタ811がオン状態となる

ような電圧VH(5V)を入力する。これによって、ノードAに電荷が蓄積され、ノード

Aの電圧は、書き込み電圧Vwと同等の値になる。その後、電圧Vext_aとして、ト

ランジスタ811がオフ状態となるような電圧VLを入力する。その後、電圧V1として

、電圧VSS(0V)を入力する。

の電圧の変化量の測定を行う。電圧の変化量から、トランジスタ812のソース電極とド

レイン電極との間を流れる電流値を算出することができる。以上により、ノードAの電荷

の蓄積とノードAの電圧の変化量の測定とを行うことができる。

ともいう)を繰り返し行う。まず、第1の蓄積及び測定動作を15回繰り返し行う。第1

の蓄積及び測定動作では、書き込み期間に書き込み電圧Vwとして5Vの電圧を入力し、

保持期間に1時間の保持を行う。次に、第2の蓄積及び測定動作を2回繰り返し行う。第

2の蓄積及び測定動作では、書き込み期間に書き込み電圧Vwとして3.5Vの電圧を入

力し、保持期間に50時間の保持を行う。次に、第3の蓄積及び測定動作を1回行う。第

3の蓄積及び測定動作では、書き込み期間に書き込み電圧Vwとして4.5Vの電圧を入

力し、保持期間に10時間の保持を行う。蓄積及び測定動作を繰り返し行うことにより、

測定した電流値が、定常状態における値であることを確認することができる。言い換える

と、ノードAを流れる電流IAのうち、過渡電流(測定開始後から時間経過とともに減少

していく電流成分)を除くことができる。その結果、より高い精度でリーク電流を測定す

ることができる。

る。

数(const)を用いて、式(2)のように表される。ここで、ノードAに接続される

容量CAは、容量素子813の容量と容量素子813以外の容量成分の和である。

時間微分であるから、ノードAの電流IAは、式(3)のように表される。

に接続される容量CAと、出力電圧Voutから、リーク電流であるノードAの電流IA

を求めることができるため、特性評価回路のリーク電流を求めることができる。

算出した特性評価回路のリーク電流の値を示す。

測定動作)に係る経過時間Timeと、出力電圧Voutとの関係を示す。図13に、上

記測定に係る経過時間Timeと、該測定によって算出された電流IAとの関係を示す。

測定開始後から出力電圧Voutが変動しており、定常状態に到るためには10時間以上

必要であることがわかる。

ノードAの電圧とリーク電流の関係を示す。図14では、例えば条件4において、ノード

Aの電圧が3.0Vの場合、リーク電流は28yA/μmである。リーク電流にはトラン

ジスタ812のオフ電流も含まれるため、トランジスタ812のオフ電流も28yA/μ

m以下とみなすことができる。

積もられた条件1乃至条件6におけるノードAの電圧とリーク電流の関係を示す。図15

乃至図17に示すように、150℃の場合であっても、リーク電流は、100zA/μm

以下であることがわかる。

むトランジスタを用いた特性評価用回路において、リーク電流が十分に低いため、上記ト

ランジスタのオフ電流が十分に小さいことがわかる。また、上記トランジスタのオフ電流

は、温度が上昇した場合であっても十分に低いことがわかる。

本実施の形態では、上記実施の形態の記憶回路の構造例について説明する。

図18及び図19は、本実施の形態における記憶回路の構造例を示す図であり、図18(

A)は、パルス変換回路の平面模式図であり、図18(B)は、図18(A)における線

分A−Bの断面模式図であり、図19(A)は、単位記憶回路の平面模式図であり、図1

9(B)は、図19(A)における線分C−Dの断面模式図であり、図19(C)は、図

19(A)における線分E−Fの断面模式図である。なお、図18及び図19では、酸化

物半導体層を含むトランジスタの一例として、上記実施の形態における、図7(A)を用

いて説明した構造のトランジスタを用いる場合を示す。

505と、導電層506aと、導電層506bと、絶縁層507と、導電層508a乃至

導電層508cと、絶縁層509と、半導体層510aと、半導体層510bと、導電層

511a乃至導電層511hと、絶縁層512と、導電層513a乃至導電層513cと

、を含む。

の一平面に設けられる。

4aを含む。半導体層502aは、パルス変換回路におけるP型トランジスタのチャネル

形成層としての機能を有する。また、不純物領域503aは、パルス変換回路におけるP

型トランジスタのソース領域及びドレイン領域の一方としての機能を有する。また、不純

物領域504aは、パルス変換回路におけるP型トランジスタのソース領域及びドレイン

領域の他方としての機能を有する。

。

4bを有する。半導体層502cは、単位記憶回路における出力用トランジスタのチャネ

ル形成層としての機能を有する。また、不純物領域503bは、単位記憶回路における出

力用トランジスタのソース領域及びドレイン領域の一方としての機能を有する。また、不

純物領域504bは、単位記憶回路における出力用トランジスタのソース領域及びドレイ

ン領域の他方としての機能を有する。

500の一平面に設けられる。絶縁層505は、パルス変換回路におけるP型トランジス

タのゲート絶縁層、単位記憶回路における保持容量の誘電体層、及び単位記憶回路におけ

る出力用トランジスタのゲート絶縁層としての機能を有する。

は、パルス変換回路におけるP型トランジスタのゲート電極としての機能を有する。

は、単位記憶回路における出力用トランジスタのゲート電極としての機能を有する。

縁層507は、平坦化絶縁層としての機能を有する。

を有する。

を有する。

。また、導電層508cは、単位記憶回路における保持容量の第2の電極としての機能を

有する。

縁層509は、パルス変換回路におけるN型トランジスタのゲート絶縁層及び単位記憶回

路における選択用トランジスタのゲート絶縁層としての機能を有する。

aは、パルス変換回路におけるN型トランジスタのチャネル形成層としての機能を有する

。

bは、単位記憶回路における選択用トランジスタのチャネル形成層としての機能を有する

。

。導電層511aは、パルス変換回路におけるP型トランジスタのソース電極及びドレイ

ン電極の一方としての機能を有する。

に電気的に接続される。導電層511bは、パルス変換回路におけるP型トランジスタの

ソース電極及びドレイン電極の他方、並びにパルス変換回路におけるN型トランジスタの

ソース電極及びドレイン電極の一方としての機能を有する。

変換回路におけるN型トランジスタのソース電極及びドレイン電極の他方としての機能を

有する。

憶回路における選択用トランジスタのソース電極及びドレイン電極の一方としての機能を

有する。

憶回路における選択用トランジスタのソース電極及びドレイン電極の他方としての機能を

有する。

。導電層511fは、単位記憶回路における出力用トランジスタのソース電極及びドレイ

ン電極の一方としての機能を有する。

。導電層511gは、単位記憶回路における出力用トランジスタのソース電極及びドレイ

ン電極の他方としての機能を有する。

においてデータ信号が入力されるビット線としての機能を有する。

1a乃至導電層511hに接する。

回路において行アドレス信号が入力されるワード線としての機能を有する。なお、導電層

513aを必ずしも設けなくてもよく、導電層508bがワード線としての機能を有する

構成にしてもよい。

回路において読み出し信号が入力される読み出し線としての機能を有する。なお、導電層

513bを必ずしも設けなくてもよく、導電層508cが読み出し線としての機能を有す

る構成にしてもよい。

できる。

ことができる。また、絶縁層501に適用可能な材料の層を積層して絶縁層501を構成

してもよい。

(シリコンなど)を含有する半導体層を用いることができる。

加することにより形成される。また、不純物領域503b及び不純物領域504bは、P

型又はN型の導電性を付与する不純物元素を添加することにより形成される。P型の導電

性を付与する不純物元素としては、例えばボロンなどを用いることができ、N型の導電性

を付与する不純物元素としては、例えばリンなどを用いることができる。

な材料の層を用いることができる。また、絶縁層505及び絶縁層509に適用可能な材

料の層を積層して絶縁層505及び絶縁層509を構成してもよい。

えば図7(A)における導電層401aに適用可能な材料の層を用いることができる。ま

た、導電層506a、導電層506b、及び導電層508a乃至導電層508cに適用可

能な材料の層を積層して導電層506a、導電層506b、及び導電層508a乃至導電

層508cを構成してもよい。

材料の層を用いることができる。また平坦化絶縁層としては、低誘電率材料(low−k

材料ともいう)の層を用いることもできる。また、絶縁層507に適用可能な材料の層の

積層により絶縁層507を構成することもできる。

3aに適用可能な材料の層を用いることができる。

図7(A)における導電層405a又は導電層406aに適用可能な材料の層を用いるこ

とができる。また、導電層511a乃至導電層511h及び導電層513a乃至導電層5

13cに適用可能な材料の層を積層して導電層511a乃至導電層511h及び導電層5

13a乃至導電層513cを構成してもよい。

を用いることができる。また、絶縁層512に適用可能な層を積層して絶縁層512を構

成してもよい。

ルス変換回路及び単位記憶回路を備える構造である。上記構造にすることにより同一工程

でパルス変換回路及び単位記憶回路を作製することができるため、製造コストを低減する

ことができる。なお、本実施の形態の記憶回路を、パルス変換回路及び単位記憶回路と、

他の回路(第1の駆動回路、第2の駆動回路、及び制御回路の一つ又は複数)と、を同一

基板上に備える構造としてもよい。

本実施の形態では、上記実施の形態の無線通信により信号の送受信が可能な半導体装置を

備えた情報媒体について説明する。

本実施の形態における情報媒体の構成例を示す図である。

A)に示すカード型証明書は、チップ900を有する。図20(A)に示すカード型証明

書は、チップ900を設けることにより、偽造防止など、セキュリティ機能を向上させる

ことができる。カード型証明書としては、例えば、免許証又は住民票などが挙げられる。

チップ900は、信頼性が高いため、上記カード型証明書などの長い期間使用するものに

好適である。

ト型情報媒体は、チップ901を有する。図20(B)に示すチケット型情報媒体は、チ

ップ901を設けることにより、チケット型情報媒体に記載された情報以外の情報をチッ

プ901に記録しておくことができる。また、図20(B)に示すチケット型情報媒体は

、チップ901を設けることにより、偽造防止など、セキュリティ機能を向上させること

ができる。なお、チップ901は、信頼性が高いため、例えばチケットの一部に切り取り

部を設け、チケット型情報媒体が不要になった際に、該切り取り部によりチップ901の

みを切り取って回収し、チップ901のみを再利用することもできる。チケット型情報媒

体としては、例えば紙幣又は乗車券、有価証券、若しくはその他の券などが挙げられる。

902を有する。図20(C)に示すコイン型情報媒体は、チップ902を設けることに

より、コイン型情報媒体に記載された情報以外の情報をチップ902に記録しておくこと

ができる。また、図20(C)に示すコイン型情報媒体は、チップ902を設けることに

より、偽造防止など、セキュリティ機能を向上させることができる。コイン型情報媒体と

しては、例えば硬貨又は乗車券、有価証券、若しくはその他の券などが挙げられる。

D)に示す物品は、チップ903を設けることにより、物品に記載された情報以外の情報

をチップ903に記録しておくことができる。また、図20(D)に示す物品は、チップ

903を設けることにより、偽造防止など、セキュリティ機能を向上させることができる

。なお、物品としては、特に限定されず、例えば電化製品又は生活用品など様々なものが

挙げられる。

半導体装置を適用することができる。

プを有する構成である。上記構成にすることにより、回路面積を小さくすることができる

。また、上記構成にすることにより、無線通信によりチップが設けられた情報媒体の固有

情報を読み出し、読み出した固有情報を利用することができる。これにより、情報媒体の

管理が容易になり、また、セキュリティ性を向上させることができる。

102 トランジスタ

151 インバータ

152 インバータ

201 パルス変換回路

202 機能回路

211 単位記憶回路

213v 駆動制御回路

213w パルス変換回路

213x 第1の駆動回路

213y 第2の駆動回路

231 トランジスタ

232 容量素子

233 トランジスタ

301 アンテナ回路

302 電源回路

303 復調回路

304 記憶制御回路

305 記憶回路

306 符号化回路

307 変調回路

400a 基板

400b 基板

400c 基板

400d 基板

401a 導電層

401b 導電層

401c 導電層

401d 導電層

402a 絶縁層

402b 絶縁層

402c 絶縁層

402d 絶縁層

403a 酸化物半導体層

403b 酸化物半導体層

403c 酸化物半導体層

403d 酸化物半導体層

405a 導電層

405b 導電層

405c 導電層

405d 導電層

406a 導電層

406b 導電層

406c 導電層

406d 導電層

407a 酸化物絶縁層

407c 酸化物絶縁層

427 絶縁層

447 絶縁層

500 基板

501 絶縁層

502a 半導体層

502b 半導体層

502c 半導体層

503a 不純物領域

503b 不純物領域

504a 不純物領域

504b 不純物領域

505 絶縁層

506a 導電層

506b 導電層

507 絶縁層

508a 導電層

508b 導電層

508c 導電層

509 絶縁層

510a 半導体層

510b 半導体層

511a 導電層

511b 導電層

511c 導電層

511d 導電層

511e 導電層

511f 導電層

511g 導電層

511h 導電層

512 絶縁層

513a 導電層

513b 導電層

513c 導電層

801 測定系

811 トランジスタ

812 トランジスタ

813 容量素子

814 トランジスタ

815 トランジスタ

900 チップ

901 チップ

902 チップ

903 チップ

Claims (2)

- 基板上の第1乃至第3の半導体層と、

前記第1乃至第3の半導体層上の第1の絶縁層と、

前記第1の絶縁層上の、前記第1の半導体層と重なる第1の導電層と、

前記第1の絶縁層上の、前記第3の半導体層と重なる第2の導電層と、

前記第1の絶縁層、前記第1の導電層、及び前記第2の導電層上の第2の絶縁層と、

前記第2の絶縁層上の第3の導電層と、

前記第2の絶縁層上の第4の導電層と、

前記第2の絶縁層上の、前記第2の半導体層と重なる第5の導電層と、

前記第2の絶縁層、前記第3の導電層、前記第4の導電層、及び前記第5の導電層上の第3の絶縁層と、

前記第3の絶縁層上の、前記第3の導電層と重なる第4の半導体層と、

前記第3の絶縁層上の、前記第4の導電層と重なる第5の半導体層と、

前記第3の絶縁層上の、前記第1の半導体層と電気的に接続された第6の導電層と、

前記第3の絶縁層上の、前記第1の半導体層及び前記第4の半導体層と電気的に接続された第7の導電層と、

前記第3の絶縁層上の、前記第4の半導体層と電気的に接続された第8の導電層と、

前記第3の絶縁層上の、前記第5の半導体層と電気的に接続された第9の導電層と、

前記第3の絶縁層上の、前記第2の半導体層及び前記第5の半導体層と電気的に接続された第10の導電層と、

前記第3の絶縁層上の、前記第3の半導体層と電気的に接続された第11の導電層と、

前記第3の絶縁層上の、前記第3の半導体層と電気的に接続された第12の導電層と、を有し、

前記第1の半導体層は、パルス変換回路におけるP型トランジスタのチャネル形成層としての機能を有し、

前記第2の半導体層は、単位記憶回路における保持容量の第1の電極としての機能を有し、

前記第3の半導体層は、前記単位記憶回路における出力用トランジスタのチャネル形成層としての機能を有し、

前記第4の半導体層は、前記パルス変換回路におけるN型トランジスタのチャネル形成層としての機能を有し、

前記第5の半導体層は、前記単位記憶回路における選択用トランジスタのチャネル形成層としての機能を有することを特徴とする半導体装置。 - 請求項1において、

前記第4の半導体層及び前記第5の半導体層は、酸化物半導体を有することを特徴とする半導体装置。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2010116861 | 2010-05-21 | ||

| JP2010116861 | 2010-05-21 |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2015049476A Division JP2015146606A (ja) | 2010-05-21 | 2015-03-12 | 半導体装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2017022397A JP2017022397A (ja) | 2017-01-26 |

| JP6173548B2 true JP6173548B2 (ja) | 2017-08-02 |

Family

ID=44972009

Family Applications (3)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2011105042A Expired - Fee Related JP5714973B2 (ja) | 2010-05-21 | 2011-05-10 | 半導体装置 |

| JP2015049476A Withdrawn JP2015146606A (ja) | 2010-05-21 | 2015-03-12 | 半導体装置 |

| JP2016174210A Expired - Fee Related JP6173548B2 (ja) | 2010-05-21 | 2016-09-07 | 半導体装置 |

Family Applications Before (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2011105042A Expired - Fee Related JP5714973B2 (ja) | 2010-05-21 | 2011-05-10 | 半導体装置 |

| JP2015049476A Withdrawn JP2015146606A (ja) | 2010-05-21 | 2015-03-12 | 半導体装置 |

Country Status (3)

| Country | Link |

|---|---|

| US (2) | US9209206B2 (ja) |

| JP (3) | JP5714973B2 (ja) |

| CN (1) | CN102355252B (ja) |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9850702B2 (en) | 2003-08-20 | 2017-12-26 | Hunter Douglas Inc | Method for making a window covering having operable vanes |

| US10030438B2 (en) | 2003-08-20 | 2018-07-24 | Hunter Douglas Inc. | Retractable shade with collapsible vanes |

Families Citing this family (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR101874144B1 (ko) | 2011-05-06 | 2018-07-03 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 기억 장치 |

| TWI568181B (zh) | 2011-05-06 | 2017-01-21 | 半導體能源研究所股份有限公司 | 邏輯電路及半導體裝置 |

| TWI536502B (zh) | 2011-05-13 | 2016-06-01 | 半導體能源研究所股份有限公司 | 記憶體電路及電子裝置 |

| JP5947099B2 (ja) | 2011-05-20 | 2016-07-06 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| JP5951351B2 (ja) | 2011-05-20 | 2016-07-13 | 株式会社半導体エネルギー研究所 | 加算器及び全加算器 |

| US8508256B2 (en) | 2011-05-20 | 2013-08-13 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor integrated circuit |

| JP2013016243A (ja) | 2011-06-09 | 2013-01-24 | Semiconductor Energy Lab Co Ltd | 記憶装置 |

| US8736315B2 (en) | 2011-09-30 | 2014-05-27 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| JP6099372B2 (ja) | 2011-12-05 | 2017-03-22 | 株式会社半導体エネルギー研究所 | 半導体装置及び電子機器 |

| JP2013232548A (ja) * | 2012-04-27 | 2013-11-14 | Panasonic Corp | 薄膜トランジスタ装置の製造方法、薄膜トランジスタ装置および表示装置 |

| US9135182B2 (en) | 2012-06-01 | 2015-09-15 | Semiconductor Energy Laboratory Co., Ltd. | Central processing unit and driving method thereof |

| US9515661B2 (en) * | 2014-05-09 | 2016-12-06 | Semiconductor Energy Laboratory Co., Ltd. | Circuit, semiconductor device, and clock tree |

| US10056497B2 (en) | 2015-04-15 | 2018-08-21 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and manufacturing method thereof |

| US10559696B2 (en) * | 2017-10-11 | 2020-02-11 | Shenzhen China Star Optoelectronics Semiconductor Display Technology Co., Ltd. | Hybrid CMOS device and manufacturing method thereof |

| JP6448743B2 (ja) * | 2017-10-30 | 2019-01-09 | 株式会社半導体エネルギー研究所 | 半導体装置 |

Family Cites Families (125)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS60198861A (ja) | 1984-03-23 | 1985-10-08 | Fujitsu Ltd | 薄膜トランジスタ |

| JPH0244256B2 (ja) | 1987-01-28 | 1990-10-03 | Kagaku Gijutsucho Mukizaishitsu Kenkyushocho | Ingazn2o5deshimesarerurotsuhoshokeinosojokozoojusurukagobutsuoyobisonoseizoho |

| JPS63210023A (ja) | 1987-02-24 | 1988-08-31 | Natl Inst For Res In Inorg Mater | InGaZn↓4O↓7で示される六方晶系の層状構造を有する化合物およびその製造法 |

| JPH0244258B2 (ja) | 1987-02-24 | 1990-10-03 | Kagaku Gijutsucho Mukizaishitsu Kenkyushocho | Ingazn3o6deshimesarerurotsuhoshokeinosojokozoojusurukagobutsuoyobisonoseizoho |

| JPH0244260B2 (ja) | 1987-02-24 | 1990-10-03 | Kagaku Gijutsucho Mukizaishitsu Kenkyushocho | Ingazn5o8deshimesarerurotsuhoshokeinosojokozoojusurukagobutsuoyobisonoseizoho |

| JPH0244262B2 (ja) | 1987-02-27 | 1990-10-03 | Kagaku Gijutsucho Mukizaishitsu Kenkyushocho | Ingazn6o9deshimesarerurotsuhoshokeinosojokozoojusurukagobutsuoyobisonoseizoho |

| JPH0244263B2 (ja) | 1987-04-22 | 1990-10-03 | Kagaku Gijutsucho Mukizaishitsu Kenkyushocho | Ingazn7o10deshimesarerurotsuhoshokeinosojokozoojusurukagobutsuoyobisonoseizoho |

| JPH05251705A (ja) | 1992-03-04 | 1993-09-28 | Fuji Xerox Co Ltd | 薄膜トランジスタ |

| JP2655053B2 (ja) | 1993-11-01 | 1997-09-17 | 日本電気株式会社 | 半導体集積回路装置 |

| EP0653843A3 (en) | 1993-11-17 | 1996-05-01 | Hewlett Packard Co | CMOS circuits with adaptive voltage threshold. |

| JPH07202677A (ja) | 1993-12-27 | 1995-08-04 | Nippon Telegr & Teleph Corp <Ntt> | Cmos出力バッファ回路 |

| JP3479375B2 (ja) | 1995-03-27 | 2003-12-15 | 科学技術振興事業団 | 亜酸化銅等の金属酸化物半導体による薄膜トランジスタとpn接合を形成した金属酸化物半導体装置およびそれらの製造方法 |

| WO1997006554A2 (en) | 1995-08-03 | 1997-02-20 | Philips Electronics N.V. | Semiconductor device provided with transparent switching element |

| JP3625598B2 (ja) | 1995-12-30 | 2005-03-02 | 三星電子株式会社 | 液晶表示装置の製造方法 |

| JP3333429B2 (ja) | 1997-06-30 | 2002-10-15 | 株式会社東芝 | 半導体集積回路 |

| JPH11233789A (ja) | 1998-02-12 | 1999-08-27 | Semiconductor Energy Lab Co Ltd | 半導体装置 |

| JP4170454B2 (ja) | 1998-07-24 | 2008-10-22 | Hoya株式会社 | 透明導電性酸化物薄膜を有する物品及びその製造方法 |

| JP2000150861A (ja) | 1998-11-16 | 2000-05-30 | Tdk Corp | 酸化物薄膜 |

| JP3276930B2 (ja) | 1998-11-17 | 2002-04-22 | 科学技術振興事業団 | トランジスタ及び半導体装置 |

| JP2001053164A (ja) | 1999-08-04 | 2001-02-23 | Sony Corp | 半導体記憶装置 |

| TW460731B (en) | 1999-09-03 | 2001-10-21 | Ind Tech Res Inst | Electrode structure and production method of wide viewing angle LCD |

| JP4089858B2 (ja) | 2000-09-01 | 2008-05-28 | 国立大学法人東北大学 | 半導体デバイス |

| KR20020038482A (ko) | 2000-11-15 | 2002-05-23 | 모리시타 요이찌 | 박막 트랜지스터 어레이, 그 제조방법 및 그것을 이용한표시패널 |

| JP3997731B2 (ja) | 2001-03-19 | 2007-10-24 | 富士ゼロックス株式会社 | 基材上に結晶性半導体薄膜を形成する方法 |

| JP2002289859A (ja) | 2001-03-23 | 2002-10-04 | Minolta Co Ltd | 薄膜トランジスタ |

| JP3925839B2 (ja) | 2001-09-10 | 2007-06-06 | シャープ株式会社 | 半導体記憶装置およびその試験方法 |

| JP4090716B2 (ja) | 2001-09-10 | 2008-05-28 | 雅司 川崎 | 薄膜トランジスタおよびマトリクス表示装置 |

| WO2003040441A1 (en) | 2001-11-05 | 2003-05-15 | Japan Science And Technology Agency | Natural superlattice homologous single crystal thin film, method for preparation thereof, and device using said single crystal thin film |

| JP4164562B2 (ja) | 2002-09-11 | 2008-10-15 | 独立行政法人科学技術振興機構 | ホモロガス薄膜を活性層として用いる透明薄膜電界効果型トランジスタ |

| JP2003188266A (ja) | 2001-12-19 | 2003-07-04 | Sony Corp | 遅延回路 |

| JP4083486B2 (ja) | 2002-02-21 | 2008-04-30 | 独立行政法人科学技術振興機構 | LnCuO(S,Se,Te)単結晶薄膜の製造方法 |

| US7049190B2 (en) | 2002-03-15 | 2006-05-23 | Sanyo Electric Co., Ltd. | Method for forming ZnO film, method for forming ZnO semiconductor layer, method for fabricating semiconductor device, and semiconductor device |

| JP3933591B2 (ja) | 2002-03-26 | 2007-06-20 | 淳二 城戸 | 有機エレクトロルミネッセント素子 |

| US7339187B2 (en) | 2002-05-21 | 2008-03-04 | State Of Oregon Acting By And Through The Oregon State Board Of Higher Education On Behalf Of Oregon State University | Transistor structures |

| JP2004022625A (ja) | 2002-06-13 | 2004-01-22 | Murata Mfg Co Ltd | 半導体デバイス及び該半導体デバイスの製造方法 |

| US7105868B2 (en) | 2002-06-24 | 2006-09-12 | Cermet, Inc. | High-electron mobility transistor with zinc oxide |

| US7067843B2 (en) | 2002-10-11 | 2006-06-27 | E. I. Du Pont De Nemours And Company | Transparent oxide semiconductor thin film transistors |

| JP2004200426A (ja) | 2002-12-19 | 2004-07-15 | Nec Electronics Corp | 半導体集積回路装置 |

| JP4166105B2 (ja) | 2003-03-06 | 2008-10-15 | シャープ株式会社 | 半導体装置およびその製造方法 |

| JP2004273732A (ja) | 2003-03-07 | 2004-09-30 | Sharp Corp | アクティブマトリクス基板およびその製造方法 |

| JP4108633B2 (ja) | 2003-06-20 | 2008-06-25 | シャープ株式会社 | 薄膜トランジスタおよびその製造方法ならびに電子デバイス |

| US7262463B2 (en) | 2003-07-25 | 2007-08-28 | Hewlett-Packard Development Company, L.P. | Transistor including a deposited channel region having a doped portion |

| US7282782B2 (en) | 2004-03-12 | 2007-10-16 | Hewlett-Packard Development Company, L.P. | Combined binary oxide semiconductor device |

| KR101078509B1 (ko) | 2004-03-12 | 2011-10-31 | 도꾸리쯔교세이호징 가가꾸 기쥬쯔 신꼬 기꼬 | 박막 트랜지스터의 제조 방법 |

| US7297977B2 (en) | 2004-03-12 | 2007-11-20 | Hewlett-Packard Development Company, L.P. | Semiconductor device |

| US7145174B2 (en) | 2004-03-12 | 2006-12-05 | Hewlett-Packard Development Company, Lp. | Semiconductor device |

| JP2005311624A (ja) | 2004-04-20 | 2005-11-04 | Sanyo Electric Co Ltd | 遅延回路 |

| US7211825B2 (en) | 2004-06-14 | 2007-05-01 | Yi-Chi Shih | Indium oxide-based thin film transistors and circuits |

| US7180363B2 (en) * | 2004-07-28 | 2007-02-20 | United Memories, Inc. | Powergating method and apparatus |

| JP2006100760A (ja) | 2004-09-02 | 2006-04-13 | Casio Comput Co Ltd | 薄膜トランジスタおよびその製造方法 |

| US7285501B2 (en) | 2004-09-17 | 2007-10-23 | Hewlett-Packard Development Company, L.P. | Method of forming a solution processed device |

| US7298084B2 (en) | 2004-11-02 | 2007-11-20 | 3M Innovative Properties Company | Methods and displays utilizing integrated zinc oxide row and column drivers in conjunction with organic light emitting diodes |

| CA2585071A1 (en) | 2004-11-10 | 2006-05-18 | Canon Kabushiki Kaisha | Field effect transistor employing an amorphous oxide |

| US7453065B2 (en) | 2004-11-10 | 2008-11-18 | Canon Kabushiki Kaisha | Sensor and image pickup device |

| US7863611B2 (en) * | 2004-11-10 | 2011-01-04 | Canon Kabushiki Kaisha | Integrated circuits utilizing amorphous oxides |

| WO2006051994A2 (en) | 2004-11-10 | 2006-05-18 | Canon Kabushiki Kaisha | Light-emitting device |

| US7791072B2 (en) | 2004-11-10 | 2010-09-07 | Canon Kabushiki Kaisha | Display |

| US7829444B2 (en) | 2004-11-10 | 2010-11-09 | Canon Kabushiki Kaisha | Field effect transistor manufacturing method |

| JP5053537B2 (ja) * | 2004-11-10 | 2012-10-17 | キヤノン株式会社 | 非晶質酸化物を利用した半導体デバイス |

| JP5126729B2 (ja) * | 2004-11-10 | 2013-01-23 | キヤノン株式会社 | 画像表示装置 |

| CN102938420B (zh) | 2004-11-10 | 2015-12-02 | 佳能株式会社 | 无定形氧化物和场效应晶体管 |

| US7098694B2 (en) * | 2004-11-12 | 2006-08-29 | Agere Systems Inc. | Overvoltage tolerant input buffer |

| US7579224B2 (en) | 2005-01-21 | 2009-08-25 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing a thin film semiconductor device |

| TWI472037B (zh) | 2005-01-28 | 2015-02-01 | Semiconductor Energy Lab | 半導體裝置,電子裝置,和半導體裝置的製造方法 |

| TWI569441B (zh) | 2005-01-28 | 2017-02-01 | 半導體能源研究所股份有限公司 | 半導體裝置,電子裝置,和半導體裝置的製造方法 |

| US7858451B2 (en) | 2005-02-03 | 2010-12-28 | Semiconductor Energy Laboratory Co., Ltd. | Electronic device, semiconductor device and manufacturing method thereof |

| US7948171B2 (en) | 2005-02-18 | 2011-05-24 | Semiconductor Energy Laboratory Co., Ltd. | Light emitting device |

| US20060197092A1 (en) | 2005-03-03 | 2006-09-07 | Randy Hoffman | System and method for forming conductive material on a substrate |

| US8681077B2 (en) | 2005-03-18 | 2014-03-25 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device, and display device, driving method and electronic apparatus thereof |

| JP2006269473A (ja) * | 2005-03-22 | 2006-10-05 | Seiko Epson Corp | 半導体装置および昇圧回路 |

| WO2006105077A2 (en) | 2005-03-28 | 2006-10-05 | Massachusetts Institute Of Technology | Low voltage thin film transistor with high-k dielectric material |

| US7645478B2 (en) | 2005-03-31 | 2010-01-12 | 3M Innovative Properties Company | Methods of making displays |

| US8300031B2 (en) | 2005-04-20 | 2012-10-30 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device comprising transistor having gate and drain connected through a current-voltage conversion element |

| JP2006344849A (ja) | 2005-06-10 | 2006-12-21 | Casio Comput Co Ltd | 薄膜トランジスタ |

| US7691666B2 (en) | 2005-06-16 | 2010-04-06 | Eastman Kodak Company | Methods of making thin film transistors comprising zinc-oxide-based semiconductor materials and transistors made thereby |

| US7402506B2 (en) | 2005-06-16 | 2008-07-22 | Eastman Kodak Company | Methods of making thin film transistors comprising zinc-oxide-based semiconductor materials and transistors made thereby |

| US7507618B2 (en) | 2005-06-27 | 2009-03-24 | 3M Innovative Properties Company | Method for making electronic devices using metal oxide nanoparticles |

| KR100711890B1 (ko) | 2005-07-28 | 2007-04-25 | 삼성에스디아이 주식회사 | 유기 발광표시장치 및 그의 제조방법 |

| JP2007059128A (ja) | 2005-08-23 | 2007-03-08 | Canon Inc | 有機el表示装置およびその製造方法 |

| JP2007073705A (ja) | 2005-09-06 | 2007-03-22 | Canon Inc | 酸化物半導体チャネル薄膜トランジスタおよびその製造方法 |

| JP4280736B2 (ja) | 2005-09-06 | 2009-06-17 | キヤノン株式会社 | 半導体素子 |

| JP5116225B2 (ja) | 2005-09-06 | 2013-01-09 | キヤノン株式会社 | 酸化物半導体デバイスの製造方法 |

| JP4850457B2 (ja) | 2005-09-06 | 2012-01-11 | キヤノン株式会社 | 薄膜トランジスタ及び薄膜ダイオード |

| JP5006598B2 (ja) | 2005-09-16 | 2012-08-22 | キヤノン株式会社 | 電界効果型トランジスタ |

| EP1995787A3 (en) | 2005-09-29 | 2012-01-18 | Semiconductor Energy Laboratory Co, Ltd. | Semiconductor device having oxide semiconductor layer and manufacturing method therof |

| JP5037808B2 (ja) | 2005-10-20 | 2012-10-03 | キヤノン株式会社 | アモルファス酸化物を用いた電界効果型トランジスタ、及び該トランジスタを用いた表示装置 |

| CN101707212B (zh) | 2005-11-15 | 2012-07-11 | 株式会社半导体能源研究所 | 半导体器件及其制造方法 |

| TWI292281B (en) | 2005-12-29 | 2008-01-01 | Ind Tech Res Inst | Pixel structure of active organic light emitting diode and method of fabricating the same |

| US7867636B2 (en) | 2006-01-11 | 2011-01-11 | Murata Manufacturing Co., Ltd. | Transparent conductive film and method for manufacturing the same |

| JP4977478B2 (ja) | 2006-01-21 | 2012-07-18 | 三星電子株式会社 | ZnOフィルム及びこれを用いたTFTの製造方法 |

| US7414877B2 (en) * | 2006-01-23 | 2008-08-19 | Freescale Semiconductor, Inc. | Electronic device including a static-random-access memory cell and a process of forming the electronic device |

| US7576394B2 (en) | 2006-02-02 | 2009-08-18 | Kochi Industrial Promotion Center | Thin film transistor including low resistance conductive thin films and manufacturing method thereof |

| US7977169B2 (en) | 2006-02-15 | 2011-07-12 | Kochi Industrial Promotion Center | Semiconductor device including active layer made of zinc oxide with controlled orientations and manufacturing method thereof |

| KR20070101595A (ko) | 2006-04-11 | 2007-10-17 | 삼성전자주식회사 | ZnO TFT |

| US20070252928A1 (en) | 2006-04-28 | 2007-11-01 | Toppan Printing Co., Ltd. | Structure, transmission type liquid crystal display, reflection type display and manufacturing method thereof |

| JP5060738B2 (ja) | 2006-04-28 | 2012-10-31 | 株式会社ジャパンディスプレイイースト | 画像表示装置 |

| JP5028033B2 (ja) | 2006-06-13 | 2012-09-19 | キヤノン株式会社 | 酸化物半導体膜のドライエッチング方法 |

| JP4609797B2 (ja) | 2006-08-09 | 2011-01-12 | Nec液晶テクノロジー株式会社 | 薄膜デバイス及びその製造方法 |