JP6157100B2 - 半導体装置 - Google Patents

半導体装置 Download PDFInfo

- Publication number

- JP6157100B2 JP6157100B2 JP2012272137A JP2012272137A JP6157100B2 JP 6157100 B2 JP6157100 B2 JP 6157100B2 JP 2012272137 A JP2012272137 A JP 2012272137A JP 2012272137 A JP2012272137 A JP 2012272137A JP 6157100 B2 JP6157100 B2 JP 6157100B2

- Authority

- JP

- Japan

- Prior art keywords

- semiconductor device

- seal ring

- tsv

- dielectric constant

- constant film

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/58—Structural electrical arrangements for semiconductor devices not otherwise provided for, e.g. in combination with batteries

- H01L23/585—Structural electrical arrangements for semiconductor devices not otherwise provided for, e.g. in combination with batteries comprising conductive layers or plates or strips or rods or rings

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/481—Internal lead connections, e.g. via connections, feedthrough structures

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/522—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body

- H01L23/5226—Via connections in a multilevel interconnection structure

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/522—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body

- H01L23/528—Geometry or layout of the interconnection structure

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/522—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body

- H01L23/532—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body characterised by the materials

- H01L23/53204—Conductive materials

- H01L23/53209—Conductive materials based on metals, e.g. alloys, metal silicides

- H01L23/53228—Conductive materials based on metals, e.g. alloys, metal silicides the principal metal being copper

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/02—Bonding areas ; Manufacturing methods related thereto

- H01L24/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L24/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/02—Bonding areas ; Manufacturing methods related thereto

- H01L24/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L24/06—Structure, shape, material or disposition of the bonding areas prior to the connecting process of a plurality of bonding areas

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L25/00—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof

- H01L25/03—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes

- H01L25/04—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers

- H01L25/065—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers the devices being of a type provided for in group H01L27/00

- H01L25/0657—Stacked arrangements of devices

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/0212—Auxiliary members for bonding areas, e.g. spacers

- H01L2224/02122—Auxiliary members for bonding areas, e.g. spacers being formed on the semiconductor or solid-state body

- H01L2224/02163—Auxiliary members for bonding areas, e.g. spacers being formed on the semiconductor or solid-state body on the bonding area

- H01L2224/02165—Reinforcing structures

- H01L2224/02166—Collar structures

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

- H01L2224/0554—External layer

- H01L2224/0555—Shape

- H01L2224/05552—Shape in top view

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

- H01L2224/0554—External layer

- H01L2224/0555—Shape

- H01L2224/05552—Shape in top view

- H01L2224/05553—Shape in top view being rectangular

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

- H01L2224/0554—External layer

- H01L2224/0556—Disposition

- H01L2224/05567—Disposition the external layer being at least partially embedded in the surface

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

- H01L2224/0554—External layer

- H01L2224/0556—Disposition

- H01L2224/0557—Disposition the external layer being disposed on a via connection of the semiconductor or solid-state body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

- H01L2224/0554—External layer

- H01L2224/05599—Material

- H01L2224/056—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof

- H01L2224/05617—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof the principal constituent melting at a temperature of greater than or equal to 400°C and less than 950°C

- H01L2224/05624—Aluminium [Al] as principal constituent

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/06—Structure, shape, material or disposition of the bonding areas prior to the connecting process of a plurality of bonding areas

- H01L2224/061—Disposition

- H01L2224/0618—Disposition being disposed on at least two different sides of the body, e.g. dual array

- H01L2224/06181—On opposite sides of the body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/07—Structure, shape, material or disposition of the bonding areas after the connecting process

- H01L2224/08—Structure, shape, material or disposition of the bonding areas after the connecting process of an individual bonding area

- H01L2224/081—Disposition

- H01L2224/0812—Disposition the bonding area connecting directly to another bonding area, i.e. connectorless bonding, e.g. bumpless bonding

- H01L2224/08135—Disposition the bonding area connecting directly to another bonding area, i.e. connectorless bonding, e.g. bumpless bonding the bonding area connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip

- H01L2224/08145—Disposition the bonding area connecting directly to another bonding area, i.e. connectorless bonding, e.g. bumpless bonding the bonding area connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip the bodies being stacked

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2225/00—Details relating to assemblies covered by the group H01L25/00 but not provided for in its subgroups

- H01L2225/03—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00

- H01L2225/04—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers

- H01L2225/065—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers the devices being of a type provided for in group H01L27/00

- H01L2225/06503—Stacked arrangements of devices

- H01L2225/06513—Bump or bump-like direct electrical connections between devices, e.g. flip-chip connection, solder bumps

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2225/00—Details relating to assemblies covered by the group H01L25/00 but not provided for in its subgroups

- H01L2225/03—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00

- H01L2225/04—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers

- H01L2225/065—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers the devices being of a type provided for in group H01L27/00

- H01L2225/06503—Stacked arrangements of devices

- H01L2225/06517—Bump or bump-like direct electrical connections from device to substrate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2225/00—Details relating to assemblies covered by the group H01L25/00 but not provided for in its subgroups

- H01L2225/03—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00

- H01L2225/04—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers

- H01L2225/065—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers the devices being of a type provided for in group H01L27/00

- H01L2225/06503—Stacked arrangements of devices

- H01L2225/06541—Conductive via connections through the device, e.g. vertical interconnects, through silicon via [TSV]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2225/00—Details relating to assemblies covered by the group H01L25/00 but not provided for in its subgroups

- H01L2225/03—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00

- H01L2225/04—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers

- H01L2225/065—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers the devices being of a type provided for in group H01L27/00

- H01L2225/06503—Stacked arrangements of devices

- H01L2225/06541—Conductive via connections through the device, e.g. vertical interconnects, through silicon via [TSV]

- H01L2225/06544—Design considerations for via connections, e.g. geometry or layout

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2225/00—Details relating to assemblies covered by the group H01L25/00 but not provided for in its subgroups

- H01L2225/03—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00

- H01L2225/04—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers

- H01L2225/065—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers the devices being of a type provided for in group H01L27/00

- H01L2225/06503—Stacked arrangements of devices

- H01L2225/06555—Geometry of the stack, e.g. form of the devices, geometry to facilitate stacking

- H01L2225/06565—Geometry of the stack, e.g. form of the devices, geometry to facilitate stacking the devices having the same size and there being no auxiliary carrier between the devices

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/28—Encapsulations, e.g. encapsulating layers, coatings, e.g. for protection

- H01L23/31—Encapsulations, e.g. encapsulating layers, coatings, e.g. for protection characterised by the arrangement or shape

- H01L23/3107—Encapsulations, e.g. encapsulating layers, coatings, e.g. for protection characterised by the arrangement or shape the device being completely enclosed

- H01L23/3121—Encapsulations, e.g. encapsulating layers, coatings, e.g. for protection characterised by the arrangement or shape the device being completely enclosed a substrate forming part of the encapsulation

- H01L23/3128—Encapsulations, e.g. encapsulating layers, coatings, e.g. for protection characterised by the arrangement or shape the device being completely enclosed a substrate forming part of the encapsulation the substrate having spherical bumps for external connection

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/02—Bonding areas ; Manufacturing methods related thereto

- H01L24/07—Structure, shape, material or disposition of the bonding areas after the connecting process

- H01L24/08—Structure, shape, material or disposition of the bonding areas after the connecting process of an individual bonding area

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/00014—Technical content checked by a classifier the subject-matter covered by the group, the symbol of which is combined with the symbol of this group, being disclosed without further technical details

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/151—Die mounting substrate

- H01L2924/153—Connection portion

- H01L2924/1531—Connection portion the connection portion being formed only on the surface of the substrate opposite to the die mounting surface

- H01L2924/15311—Connection portion the connection portion being formed only on the surface of the substrate opposite to the die mounting surface being a ball array, e.g. BGA

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Computer Hardware Design (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Geometry (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

Description

図1は、第1の実施の形態にかかる3次元集積回路80を示す。3次元集積回路80は、パッケージ基板90の上に、4つの半導体装置100が積層されている。例として、パッケージ基板90の上に積層された半導体装置の数が4であるが、この数は、限定されることがなく、2以上の任意の値とすることができる。

例えば、クラックの1つの進行方向が方向1であるとする。方向1に向かって進行するクラックを阻止するためには、方向1と略垂直する形状を有する阻止物が効果的であると考えられる。

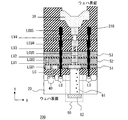

第2の実施の形態も、複数の半導体装置が積層されてなる3次元集積回路である。図6は、本第2の実施の形態にかかる3次元集積回路における半導体装置200を示す。

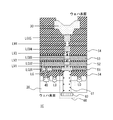

第3の実施の形態も、複数の半導体装置が積層されてなる3次元集積回路である。図7は、本第3の実施の形態にかかる3次元集積回路における半導体装置300を示す。図7に対して、半導体装置200と異なる点についてのみ説明する。

上述した各実施の形態における半導体装置は、TSVがアルミ電極まで接続された例である。本技術は、TSVがアルミ電極に接続されない半導体装置にも適用可能である。本第4の実施の形態は、このような半導体装置について説明する。

シリコン基板に最も近い低比誘電率膜(第1の低比誘電率膜)から、シリコン基板から最も遠い低比誘電率膜(第2の低比誘電率膜)までシールリングを設ければ、低比誘電率膜のクラックの発生と進行を抑制できることは、上記にて説明した。シールリングを第1の低比誘電率膜より下のコンタクト層まで、すなわち拡散層の表面まで設け、拡散層と接続することにより、シールリングを基板と同電位にすることができる。そのため、近傍の半導体素子への給電に利用することができる。図9を参照して1例を説明する。

図11に示す第6の実施の形態の半導体装置600も、拡散層までシールリングを設け、半導体素子の給電に使用する例である。半導体装置600においても、例として、半導体素子40は、N型のトランジスタであり、拡散層LDは、P+拡散層となる。

20 シリコン基板

30 アルミ電極

40 半導体素子

51 第1の低比誘電率膜

52 低比誘電率膜

53 第2の低比誘電率膜

54 絶縁膜

60 TSV

61 TSV電極

62 TSV電極パッド

80 3次元集積回路

90 パッケージ基板

100 半導体装置

110 シールリング

200 半導体装置

210 シールリング

300 半導体装置

310 シールリング

330 アルミ電極

360 TSV

361 TSV電極

362 TSV電極パッド

400 半導体装置

410 シールリング

500 半導体装置

510 シールリング

600 半導体装置

610 シールリング

LC コンタクト層

LD 拡散層

LCU1 第1の銅配線層

LCU2 第2の銅配線層

LCU3 第3の銅配線層

LCU4 第4の銅配線層

LCU5 第5の銅配線層

LV1 第1のビア層

LV2 第2のビア層

LV3 第3のビア層

LV4 第4のビア層

Claims (4)

- シリコン基板と、

前記シリコン基板を貫通するTSV(Through−Silicon Via)とを備える半導体装置であって、

前記シリコン基板に最も近い低比誘電率膜である第1の低比誘電率膜から、前記シリコン基板から最も遠い低比誘電率膜である第2の低比誘電率膜までシールリングが設けられており、

前記シールリングは、前記シリコン基板を俯瞰する方向で見たときに、前記TSVの近傍において前記TSVを囲むように形成されており、

前記シールリングは、前記第1の低比誘電率膜より下のコンタクト層まで設けられ、拡散層に接続されており、

前記シールリングは、半導体素子の電極にさらに接続されており、

前記拡散層から前記シールリングを介して前記半導体素子の電極に対して給電される、

半導体装置。 - 前記シールリングは、前記第2の低比誘電率膜よりも上の層まで設けられている、

請求項1に記載の半導体装置。 - 複数の前記TSVを備え、

前記シールリングは、前記シリコン基板を俯瞰する方向で見たときに、前記複数のTSVを囲むように形成されている、

請求項1又は2に記載の半導体装置。 - 前記シールリングは、

前記シリコン基板を俯瞰する方向で見たときに、四方形の4つの角を夫々45度にカットして得た八角形を成す、

請求項1から3のいずれか1項に記載の半導体装置。

Priority Applications (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2012272137A JP6157100B2 (ja) | 2012-12-13 | 2012-12-13 | 半導体装置 |

| US14/077,503 US9673153B2 (en) | 2012-12-13 | 2013-11-12 | Semiconductor device |

| CN201310685194.9A CN103872047B (zh) | 2012-12-13 | 2013-12-13 | 半导体器件 |

| US15/585,468 US10062655B2 (en) | 2012-12-13 | 2017-05-03 | Semiconductor device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2012272137A JP6157100B2 (ja) | 2012-12-13 | 2012-12-13 | 半導体装置 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2017111407A Division JP2017147475A (ja) | 2017-06-06 | 2017-06-06 | 半導体装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2014120504A JP2014120504A (ja) | 2014-06-30 |

| JP2014120504A5 JP2014120504A5 (ja) | 2015-10-08 |

| JP6157100B2 true JP6157100B2 (ja) | 2017-07-05 |

Family

ID=50910421

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2012272137A Active JP6157100B2 (ja) | 2012-12-13 | 2012-12-13 | 半導体装置 |

Country Status (3)

| Country | Link |

|---|---|

| US (2) | US9673153B2 (ja) |

| JP (1) | JP6157100B2 (ja) |

| CN (1) | CN103872047B (ja) |

Families Citing this family (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN105336710B (zh) * | 2014-07-10 | 2018-03-23 | 中芯国际集成电路制造(上海)有限公司 | 一种芯片的密封环 |

| JP6519785B2 (ja) * | 2015-05-11 | 2019-05-29 | 国立研究開発法人産業技術総合研究所 | 貫通電極及びその製造方法、並びに半導体装置及びその製造方法 |

| CN108352321B (zh) | 2015-10-28 | 2022-09-16 | 奥林巴斯株式会社 | 半导体装置 |

| CN108155155B (zh) * | 2016-12-02 | 2020-03-10 | 中芯国际集成电路制造(上海)有限公司 | 半导体结构及其形成方法 |

| CN109830464A (zh) * | 2019-02-15 | 2019-05-31 | 德淮半导体有限公司 | 半导体结构及其形成方法 |

| US12014997B2 (en) | 2021-07-01 | 2024-06-18 | Taiwan Semiconductor Manufacturing Co., Ltd. | Dummy stacked structures surrounding TSVs and method forming the same |

| US20230187289A1 (en) * | 2021-12-14 | 2023-06-15 | Micron Technology, Inc. | Semiconductor device and method of forming the same |

Family Cites Families (22)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4502173B2 (ja) * | 2003-02-03 | 2010-07-14 | ルネサスエレクトロニクス株式会社 | 半導体装置及びその製造方法 |

| JP2005142553A (ja) * | 2003-10-15 | 2005-06-02 | Toshiba Corp | 半導体装置 |

| US7049701B2 (en) * | 2003-10-15 | 2006-05-23 | Kabushiki Kaisha Toshiba | Semiconductor device using insulating film of low dielectric constant as interlayer insulating film |

| JP4689244B2 (ja) * | 2004-11-16 | 2011-05-25 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

| US7224069B2 (en) * | 2005-07-25 | 2007-05-29 | Taiwan Semiconductor Manufacturing Company, Ltd. | Dummy structures extending from seal ring into active circuit area of integrated circuit chip |

| JP5021992B2 (ja) * | 2005-09-29 | 2012-09-12 | ルネサスエレクトロニクス株式会社 | 半導体装置およびその製造方法 |

| JP2007115988A (ja) * | 2005-10-21 | 2007-05-10 | Renesas Technology Corp | 半導体装置 |

| JP5098647B2 (ja) | 2005-12-27 | 2012-12-12 | 富士通セミコンダクター株式会社 | 半導体装置とその製造方法 |

| JP5329068B2 (ja) | 2007-10-22 | 2013-10-30 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

| JP2009123734A (ja) * | 2007-11-12 | 2009-06-04 | Renesas Technology Corp | 半導体装置及びその製造方法 |

| US8188578B2 (en) * | 2008-05-29 | 2012-05-29 | Mediatek Inc. | Seal ring structure for integrated circuits |

| US8053902B2 (en) | 2008-12-02 | 2011-11-08 | Taiwan Semiconductor Manufacturing Company, Ltd. | Isolation structure for protecting dielectric layers from degradation |

| US8749027B2 (en) * | 2009-01-07 | 2014-06-10 | Taiwan Semiconductor Manufacturing Company, Ltd. | Robust TSV structure |

| US20100224878A1 (en) | 2009-03-05 | 2010-09-09 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| US8299583B2 (en) * | 2009-03-05 | 2012-10-30 | International Business Machines Corporation | Two-sided semiconductor structure |

| US8169055B2 (en) | 2009-03-18 | 2012-05-01 | International Business Machines Corporation | Chip guard ring including a through-substrate via |

| JP2011129722A (ja) | 2009-12-17 | 2011-06-30 | Panasonic Corp | 半導体装置 |

| JP2011176047A (ja) * | 2010-02-23 | 2011-09-08 | On Semiconductor Trading Ltd | 半導体装置及びその製造方法 |

| JP2011216753A (ja) | 2010-04-01 | 2011-10-27 | Panasonic Corp | 半導体装置及びその製造方法 |

| JP5300814B2 (ja) | 2010-10-14 | 2013-09-25 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

| JP5685060B2 (ja) * | 2010-11-18 | 2015-03-18 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

| JP2012256787A (ja) * | 2011-06-10 | 2012-12-27 | Renesas Electronics Corp | 半導体装置及び半導体装置の製造方法 |

-

2012

- 2012-12-13 JP JP2012272137A patent/JP6157100B2/ja active Active

-

2013

- 2013-11-12 US US14/077,503 patent/US9673153B2/en not_active Expired - Fee Related

- 2013-12-13 CN CN201310685194.9A patent/CN103872047B/zh not_active Expired - Fee Related

-

2017

- 2017-05-03 US US15/585,468 patent/US10062655B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| JP2014120504A (ja) | 2014-06-30 |

| CN103872047A (zh) | 2014-06-18 |

| CN103872047B (zh) | 2018-02-27 |

| US9673153B2 (en) | 2017-06-06 |

| US20170236789A1 (en) | 2017-08-17 |

| US10062655B2 (en) | 2018-08-28 |

| US20140167286A1 (en) | 2014-06-19 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6157100B2 (ja) | 半導体装置 | |

| KR101227872B1 (ko) | 3d ic를 위한 esd 보호 구조 | |

| CN103378034B (zh) | 具有硅通孔内连线的半导体封装 | |

| US9087822B2 (en) | Semiconductor device | |

| JP2007184449A (ja) | 半導体装置及びその製造方法 | |

| US9947627B2 (en) | Guard ring structure and method for forming the same | |

| EP2733736A2 (en) | Method for electrically connecting wafers using butting contact struture and semiconductor device fabricated through the same | |

| US20160172406A1 (en) | Semiconductor device and solid-state imaging device | |

| TW201801263A (zh) | 扇出型晶圓級封裝結構 | |

| TWI596737B (zh) | 靜電放電保護器件 | |

| US11450633B2 (en) | Package structure of semiconductor device with improved bonding between the substrates | |

| CN103579208A (zh) | 三维集成电路及其制作方法 | |

| TWI520330B (zh) | 半導體裝置 | |

| US9269645B1 (en) | Fan-out wafer level package | |

| JP2017147475A (ja) | 半導体装置 | |

| US8350272B2 (en) | Semiconductor device | |

| JP5574639B2 (ja) | 半導体装置およびその製造方法 | |

| JP6211855B2 (ja) | 半導体装置 | |

| JP2014022485A (ja) | 半導体装置及びその製造方法 | |

| JP2011066459A (ja) | 半導体装置 | |

| JP5401056B2 (ja) | 半導体装置 | |

| JP2014192295A (ja) | 半導体装置 | |

| TWI587449B (zh) | 半導體封裝結構及其製造方法 | |

| JP5920239B2 (ja) | 半導体装置 | |

| JP2011199191A (ja) | 半導体装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20150820 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20150820 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20160720 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20160906 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20161102 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20170509 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20170606 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6157100 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |