JP5868049B2 - 撮像装置 - Google Patents

撮像装置 Download PDFInfo

- Publication number

- JP5868049B2 JP5868049B2 JP2011158232A JP2011158232A JP5868049B2 JP 5868049 B2 JP5868049 B2 JP 5868049B2 JP 2011158232 A JP2011158232 A JP 2011158232A JP 2011158232 A JP2011158232 A JP 2011158232A JP 5868049 B2 JP5868049 B2 JP 5868049B2

- Authority

- JP

- Japan

- Prior art keywords

- pixel

- signal

- reference signal

- counter

- respect

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M1/00—Analogue/digital conversion; Digital/analogue conversion

- H03M1/004—Reconfigurable analogue/digital or digital/analogue converters

- H03M1/008—Reconfigurable analogue/digital or digital/analogue converters among different conversion characteristics, e.g. between mu-255 and a-laws

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

- H04N25/70—SSIS architectures; Circuits associated therewith

- H04N25/71—Charge-coupled device [CCD] sensors; Charge-transfer registers specially adapted for CCD sensors

- H04N25/75—Circuitry for providing, modifying or processing image signals from the pixel array

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M1/00—Analogue/digital conversion; Digital/analogue conversion

- H03M1/12—Analogue/digital converters

- H03M1/1205—Multiplexed conversion systems

- H03M1/123—Simultaneous, i.e. using one converter per channel but with common control or reference circuits for multiple converters

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M1/00—Analogue/digital conversion; Digital/analogue conversion

- H03M1/12—Analogue/digital converters

- H03M1/50—Analogue/digital converters with intermediate conversion to time interval

- H03M1/56—Input signal compared with linear ramp

Landscapes

- Engineering & Computer Science (AREA)

- Multimedia (AREA)

- Signal Processing (AREA)

- Theoretical Computer Science (AREA)

- Transforming Light Signals Into Electric Signals (AREA)

Description

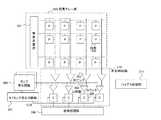

図1は、本発明の実施形態に係る撮像装置の構成例を示すブロック図である。撮像装置は、例えばカメラシステムであり、列並列AD変換器搭載イメージセンサ110の画素領域に入射光を導く(被写体像を結像する)光学系、例えば入射光(像光)を撮像面上に結像させるレンズ101を有する。撮像装置は、列並列AD変換器搭載イメージセンサ110と、イメージセンサ110からの画素信号に対し所定の信号処理を行う画像処理部108と、画像処理部108の駆動を制御する全体制御部109とを有する。全体制御部109は、イメージセンサ110内の回路を駆動するスタートパルスやクロックパルスを含む各種タイミング信号を生成するタイミングジェネレータを有し、所定のタイミングでイメージセンサ110を駆動する。また、画像処理部108は、RGBの画素出力信号をY,Cb,Cr色空間への変換や、ガンマ補正などの所定の画像処理を施す。画像処理部108で処理された画像信号は、例えばメモリなどの記録媒体に記録される。記録媒体に記憶された画像情報は、プリンタなどによってハードコピーされる。また、画像処理回路108で処理された画像信号は、液晶ディスプレイなどからなるモニターに動画として映し出される。列並列AD変換器搭載イメージセンサ110は、レンズ101によって結像された光を電気信号に変換する画素アレー部102と、AD変換の際に参照信号として用いられる参照信号を発生させるランプ発生回路部103とを有する。参照信号は、時間に対して変化する参照信号である。さらに、イメージセンサ110は、画素アレー部102からのアナログ信号をデジタル信号に変換する列並列AD変換部104と、AD変換時の制御パルスを発生させるタイミング発生回路部105とを有する。さらに、イメージセンサ110は、相関二重サンプリング(CDS)などの処理をAD変換出力結果に対して行う信号処理部106と、LVDSなどの外部インターフェース(I/F)部107とを有する。撮像装置は、その他さまざまな機能部位をもつが、本実施形態での特徴的な部位のみを記述した。

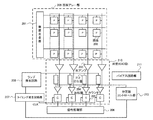

図8は、本発明の第2の実施形態による撮像装置の構成例を示す図である。第1の実施形態においては、複数種類の参照信号を生成するために複数個のランプ発生回路208を用いた。本発明の第2の実施形態では、複数種類の参照信号を生成する別の手段として、分圧器212を用いて参照信号を生成する。本実施形態(図8)は、第1の実施形態(図2)に対して、分圧器212を追加したものである。以下、本実施形態が第1の実施形態と異なる点を説明する。

図9は、本発明の第1の実施形態による撮像装置の構成例を示す図である。本実施形態(図9)は、第1の実施形態(図4)に対して、画素列901及び902が異なる。以下、本実施形態が第1の実施形態と異なる点を説明する。第1の実施形態では、R、Gr、Gb、Bの4画素が隣り合うように配列されたカラーフィルタを用いた例を説明した。カラーフィルタの配列によっては、信号処理部401が選択する画素を、第1の実施形態から変更することが必要になる場合がある。そのような例として、R、R、Gr、Gr、Gb、Gb、B、B配列のカラーフィルタを用いた場合を、本発明の第3の実施形態として説明する。以下、本実施形態が第1の実施形態と異なる点を説明する。

Claims (7)

- 光電変換により信号を生成する第1の画素と、

前記第1の画素に対して同一行に配列され、光電変換により信号を生成する第2の画素と、

前記第1の画素に基づく信号と時間に対してレベルが変化する第1の参照信号とを比較する第1の比較器と、

前記第2の画素に基づく信号と前記第1の参照信号に対して時間に対する変化率が異なる第2の参照信号とを比較する第2の比較器と、

前記第1の比較器が前記第1の画素に基づく信号と前記第1の参照信号との大小関係が逆転することを示す信号を出力するまでの間にカウントを行う第1のカウンタと、

前記第2の比較器が前記第2の画素に基づく信号と前記第2の参照信号との大小関係が逆転することを示す信号を出力するまでの間にカウントを行う第2のカウンタと、

少なくとも前記第1のカウンタのカウント値及び/又は前記第2のカウンタのカウント値を基に1個の画素信号を生成する処理部とを有し、

前記第2の参照信号は、前記第1の参照信号に対して時間に対する変化率が大きく、

前記処理部は、前記第1の画素に基づく信号と前記第1の参照信号との大小関係が逆転せず、前記第2の画素に基づく信号と前記第2の参照信号との大小関係が逆転したときには、前記第2のカウンタのカウント値を選択して1個の画素信号を生成することを特徴とする撮像装置。 - 光電変換により信号を生成する第1の画素と、

前記第1の画素に対して同一行に配列され、光電変換により信号を生成する第2の画素と、

前記第1の画素に基づく信号と時間に対してレベルが変化する第1の参照信号とを比較する第1の比較器と、

前記第2の画素に基づく信号と前記第1の参照信号に対して時間に対する変化率が異なる第2の参照信号とを比較する第2の比較器と、

前記第1の比較器が前記第1の画素に基づく信号と前記第1の参照信号との大小関係が逆転することを示す信号を出力するまでの間にカウントを行う第1のカウンタと、

前記第2の比較器が前記第2の画素に基づく信号と前記第2の参照信号との大小関係が逆転することを示す信号を出力するまでの間にカウントを行う第2のカウンタと、

少なくとも前記第1のカウンタのカウント値及び/又は前記第2のカウンタのカウント値を基に1個の画素信号を生成する処理部とを有し、

前記第2の参照信号は、前記第1の参照信号に対して時間に対する変化率が大きく、

前記処理部は、前記第1の画素に基づく信号と前記第1の参照信号との大小関係が逆転し、前記第2の画素に基づく信号と前記第2の参照信号との大小関係が逆転したときには、前記第1のカウンタのカウント値を選択して1個の画素信号を生成することを特徴とする撮像装置。 - 光電変換により信号を生成する第1の画素と、

前記第1の画素に対して同一行に配列され、光電変換により信号を生成する第2の画素と、

前記第1の画素に基づく信号と時間に対してレベルが変化する第1の参照信号とを比較する第1の比較器と、

前記第2の画素に基づく信号と前記第1の参照信号に対して時間に対する変化率が異なる第2の参照信号とを比較する第2の比較器と、

前記第1の比較器が前記第1の画素に基づく信号と前記第1の参照信号との大小関係が逆転することを示す信号を出力するまでの間にカウントを行う第1のカウンタと、

前記第2の比較器が前記第2の画素に基づく信号と前記第2の参照信号との大小関係が逆転することを示す信号を出力するまでの間にカウントを行う第2のカウンタと、

少なくとも前記第1のカウンタのカウント値及び/又は前記第2のカウンタのカウント値を基に1個の画素信号を生成する処理部とを有し、

前記処理部は、前記第1の画素に基づく信号と前記第1の参照信号との大小関係が逆転し、前記第2の画素に基づく信号と前記第2の参照信号との大小関係が逆転したときには、前記第1のカウンタのカウント値及び前記第2のカウンタのカウント値を合成して1個の画素信号を生成することを特徴とする撮像装置。 - 前記処理部は、前記第1の参照信号及び前記第2の参照信号の時間に対する変化率の違いに対応する前記第1のカウンタのカウント値及び前記第2のカウンタのカウント値のゲインの違いを補正することを特徴とする請求項1〜3のいずれか1項に記載の撮像装置。

- 前記第2の比較器は、第1のモードでは、前記第2の画素に基づく信号と前記第1の参照信号に対して時間に対する変化率が異なる第2の参照信号とを比較し、第2のモードでは、前記第2の画素に基づく信号と前記第1の参照信号に対して時間に対する変化率が同じ第2の参照信号とを比較することを特徴とする請求項1〜4のいずれか1項に記載の撮像装置。

- 前記第1の画素及び前記第2の画素は、同色のカラーフィルタが設けられた2画素であることを特徴とする請求項1〜5のいずれか1項に記載の撮像装置。

- 前記第1の画素及び前記第2の画素は、列方向に隣接する同色のカラーフィルタが設けられた2画素であることを特徴とする請求項1〜5のいずれか1項に記載の撮像装置。

Priority Applications (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2011158232A JP5868049B2 (ja) | 2011-07-19 | 2011-07-19 | 撮像装置 |

| US13/540,168 US9148590B2 (en) | 2011-07-19 | 2012-07-02 | Imaging apparatus with reference signals having different rate of change first and second pixels having same color |

| CN201210245585.4A CN102891967B (zh) | 2011-07-19 | 2012-07-16 | 成像装置 |

| EP12176647.1A EP2549743B1 (en) | 2011-07-19 | 2012-07-17 | Imaging apparatus |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2011158232A JP5868049B2 (ja) | 2011-07-19 | 2011-07-19 | 撮像装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2013026734A JP2013026734A (ja) | 2013-02-04 |

| JP2013026734A5 JP2013026734A5 (ja) | 2014-08-14 |

| JP5868049B2 true JP5868049B2 (ja) | 2016-02-24 |

Family

ID=46514217

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2011158232A Active JP5868049B2 (ja) | 2011-07-19 | 2011-07-19 | 撮像装置 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US9148590B2 (ja) |

| EP (1) | EP2549743B1 (ja) |

| JP (1) | JP5868049B2 (ja) |

| CN (1) | CN102891967B (ja) |

Families Citing this family (21)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5808162B2 (ja) * | 2011-06-23 | 2015-11-10 | キヤノン株式会社 | 撮像素子、撮像装置及び撮像素子の駆動方法 |

| JP5868065B2 (ja) * | 2011-08-05 | 2016-02-24 | キヤノン株式会社 | 撮像装置 |

| US8963759B2 (en) * | 2012-05-03 | 2015-02-24 | Semiconductor Components Industries, Llc | Imaging systems with per-column analog-to-digital converter non-linearity correction capabilities |

| US9137455B1 (en) * | 2014-11-05 | 2015-09-15 | Duelight Llc | Image sensor apparatus and method for obtaining multiple exposures with zero interframe time |

| US10558848B2 (en) | 2017-10-05 | 2020-02-11 | Duelight Llc | System, method, and computer program for capturing an image with correct skin tone exposure |

| JP2014239289A (ja) * | 2013-06-06 | 2014-12-18 | ソニー株式会社 | Ad変換器、信号処理方法、固体撮像装置、および電子機器 |

| JP6190184B2 (ja) | 2013-06-28 | 2017-08-30 | キヤノン株式会社 | 撮像素子、撮像装置、その制御方法、および制御プログラム |

| KR102057575B1 (ko) * | 2013-07-25 | 2019-12-20 | 삼성전자주식회사 | 이미지 센서 및 그것의 제어 방법 |

| JP6386722B2 (ja) * | 2013-11-26 | 2018-09-05 | キヤノン株式会社 | 撮像素子、撮像装置及び携帯電話機 |

| JP6413235B2 (ja) * | 2013-12-06 | 2018-10-31 | 株式会社ニコン | 撮像素子および撮像装置 |

| CN106464819B (zh) * | 2014-05-26 | 2020-01-14 | 索尼公司 | 信号处理器件、控制方法、图像传感器件和电子设备 |

| JP6478488B2 (ja) * | 2014-06-18 | 2019-03-06 | キヤノン株式会社 | Ad変換装置及び固体撮像装置 |

| JP6454490B2 (ja) * | 2014-07-17 | 2019-01-16 | ルネサスエレクトロニクス株式会社 | 半導体装置及びランプ信号の制御方法 |

| JP6677909B2 (ja) * | 2015-01-30 | 2020-04-08 | ソニー株式会社 | 固体撮像装置および電子機器 |

| KR20160103302A (ko) * | 2015-02-24 | 2016-09-01 | 에스케이하이닉스 주식회사 | 램프전압 제너레이터 및 그를 포함하는 이미지 센싱 장치 |

| US9986185B2 (en) * | 2016-03-09 | 2018-05-29 | Ricoh Company, Ltd. | Semiconductor integrated circuit and image capturing apparatus |

| JP6195142B1 (ja) * | 2017-01-30 | 2017-09-13 | テックポイント インクTechpoint,Inc. | Ad変換装置及び撮像装置 |

| JP6871815B2 (ja) | 2017-06-30 | 2021-05-12 | キヤノン株式会社 | 撮像装置及びその駆動方法 |

| JP6632580B2 (ja) * | 2017-08-03 | 2020-01-22 | キヤノン株式会社 | 撮像素子および撮像装置 |

| JP6704944B2 (ja) * | 2018-02-09 | 2020-06-03 | キヤノン株式会社 | 撮像装置、撮像システム、移動体 |

| JP2022180670A (ja) | 2019-10-30 | 2022-12-07 | ソニーセミコンダクタソリューションズ株式会社 | 固体撮像素子 |

Family Cites Families (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2006109117A (ja) * | 2004-10-06 | 2006-04-20 | Sony Corp | Ad変換用参照信号の伝達方法および伝達装置、ad変換方法およびad変換装置、並びに物理情報取得方法および物理情報取得装置 |

| JP4682750B2 (ja) * | 2005-08-22 | 2011-05-11 | ソニー株式会社 | Da変換装置 |

| JP4744343B2 (ja) * | 2006-04-10 | 2011-08-10 | ソニー株式会社 | 固体撮像装置および固体撮像装置の駆動方法 |

| JP4882652B2 (ja) | 2006-10-06 | 2012-02-22 | ソニー株式会社 | 固体撮像装置、固体撮像装置の駆動方法および撮像装置 |

| JP4379504B2 (ja) * | 2007-08-13 | 2009-12-09 | ソニー株式会社 | 固体撮像素子、およびカメラシステム |

| US7995124B2 (en) | 2007-09-14 | 2011-08-09 | Omnivision Technologies, Inc. | Image sensor apparatus and method for improved dynamic range with multiple readout circuit paths |

| JP2009303088A (ja) * | 2008-06-17 | 2009-12-24 | Panasonic Corp | 固体撮像装置、その駆動方法及びカメラ |

| JP4661912B2 (ja) * | 2008-07-18 | 2011-03-30 | ソニー株式会社 | 固体撮像素子およびカメラシステム |

| JP2010251957A (ja) * | 2009-04-14 | 2010-11-04 | Sony Corp | Ad変換装置、固体撮像素子、およびカメラシステム |

| US8144215B2 (en) | 2009-05-11 | 2012-03-27 | Himax Imaging, Inc. | Method and apparatus of using processor with analog-to-digital converter within image sensor to achieve high dynamic range of image sensor |

| JP5219962B2 (ja) * | 2009-08-13 | 2013-06-26 | キヤノン株式会社 | 固体撮像素子、その駆動方法、及び撮像システム |

| US8717474B2 (en) * | 2009-12-04 | 2014-05-06 | Canon Kabushiki Kaisha | Imaging apparatus and method for driving the same |

| JP5591586B2 (ja) * | 2010-05-19 | 2014-09-17 | パナソニック株式会社 | 固体撮像装置、画像処理装置、カメラシステム |

-

2011

- 2011-07-19 JP JP2011158232A patent/JP5868049B2/ja active Active

-

2012

- 2012-07-02 US US13/540,168 patent/US9148590B2/en active Active

- 2012-07-16 CN CN201210245585.4A patent/CN102891967B/zh active Active

- 2012-07-17 EP EP12176647.1A patent/EP2549743B1/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| CN102891967B (zh) | 2016-01-20 |

| CN102891967A (zh) | 2013-01-23 |

| EP2549743B1 (en) | 2018-03-21 |

| EP2549743A2 (en) | 2013-01-23 |

| JP2013026734A (ja) | 2013-02-04 |

| US9148590B2 (en) | 2015-09-29 |

| EP2549743A3 (en) | 2014-03-12 |

| US20130021493A1 (en) | 2013-01-24 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5868049B2 (ja) | 撮像装置 | |

| US10104326B2 (en) | Imaging apparatus including analog-to-digital conversion circuits to convert analog signals into digital signals, imaging system including analog-to-digital conversion circuits to convert analog signals into digital signals, and imaging apparatus driving method | |

| JP5868065B2 (ja) | 撮像装置 | |

| JP4569647B2 (ja) | Ad変換装置、ad変換方法、固体撮像素子、およびカメラシステム | |

| US8687098B2 (en) | Solid-state imaging device, control method therefor, and camera system | |

| JP4442695B2 (ja) | 固体撮像装置及びカメラ装置 | |

| JP5591586B2 (ja) | 固体撮像装置、画像処理装置、カメラシステム | |

| JP4618349B2 (ja) | 固体撮像素子、撮像方法及び撮像装置 | |

| JP5256874B2 (ja) | 固体撮像素子およびカメラシステム | |

| US9036052B2 (en) | Image pickup apparatus that uses pixels different in sensitivity, method of controlling the same, and storage medium | |

| US10523882B2 (en) | Ad converter, signal processing method, solid-state imaging device, and electronic apparatus | |

| WO2010073584A1 (ja) | 固体撮像装置、デジタルカメラ及びad変換方法 | |

| JP6164867B2 (ja) | 固体撮像装置、その制御方法、および制御プログラム | |

| TWI401950B (zh) | Solid-state imaging elements and camera systems | |

| JP2018014602A (ja) | 撮像装置及びその制御方法、プログラム、記憶媒体 | |

| JP6257348B2 (ja) | 固体撮像装置、撮像システム及び複写機 | |

| JP7109998B2 (ja) | 撮像装置および撮像装置の制御方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140702 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20140702 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20150423 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20150512 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20150708 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20151208 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20160105 |

|

| R151 | Written notification of patent or utility model registration |

Ref document number: 5868049 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R151 |