JP5864954B2 - 基材 - Google Patents

基材 Download PDFInfo

- Publication number

- JP5864954B2 JP5864954B2 JP2011185134A JP2011185134A JP5864954B2 JP 5864954 B2 JP5864954 B2 JP 5864954B2 JP 2011185134 A JP2011185134 A JP 2011185134A JP 2011185134 A JP2011185134 A JP 2011185134A JP 5864954 B2 JP5864954 B2 JP 5864954B2

- Authority

- JP

- Japan

- Prior art keywords

- layer

- wiring

- base material

- layers

- glass

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000000463 material Substances 0.000 title claims description 106

- 239000010410 layer Substances 0.000 claims description 268

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 claims description 67

- 239000010703 silicon Substances 0.000 claims description 67

- 229910052710 silicon Inorganic materials 0.000 claims description 67

- 239000011521 glass Substances 0.000 claims description 65

- 239000012792 core layer Substances 0.000 claims description 63

- 239000004020 conductor Substances 0.000 claims description 61

- 239000012790 adhesive layer Substances 0.000 claims description 52

- 239000000758 substrate Substances 0.000 claims description 23

- 230000000149 penetrating effect Effects 0.000 claims description 10

- TWNQGVIAIRXVLR-UHFFFAOYSA-N oxo(oxoalumanyloxy)alumane Chemical compound O=[Al]O[Al]=O TWNQGVIAIRXVLR-UHFFFAOYSA-N 0.000 claims description 8

- 238000004519 manufacturing process Methods 0.000 description 37

- 239000010949 copper Substances 0.000 description 34

- 230000004048 modification Effects 0.000 description 29

- 238000012986 modification Methods 0.000 description 29

- 238000000034 method Methods 0.000 description 20

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 17

- 229910052802 copper Inorganic materials 0.000 description 17

- 230000000694 effects Effects 0.000 description 14

- 239000004642 Polyimide Substances 0.000 description 8

- UMIVXZPTRXBADB-UHFFFAOYSA-N benzocyclobutene Chemical compound C1=CC=C2CCC2=C1 UMIVXZPTRXBADB-UHFFFAOYSA-N 0.000 description 8

- 229920002577 polybenzoxazole Polymers 0.000 description 8

- 229920001721 polyimide Polymers 0.000 description 8

- 239000010936 titanium Substances 0.000 description 8

- 229910004298 SiO 2 Inorganic materials 0.000 description 7

- 238000002844 melting Methods 0.000 description 7

- 239000004065 semiconductor Substances 0.000 description 7

- 239000003822 epoxy resin Substances 0.000 description 6

- 230000008018 melting Effects 0.000 description 6

- 229920000647 polyepoxide Polymers 0.000 description 6

- 229920005989 resin Polymers 0.000 description 6

- 239000011347 resin Substances 0.000 description 6

- 229910000679 solder Inorganic materials 0.000 description 6

- 230000003647 oxidation Effects 0.000 description 5

- 238000007254 oxidation reaction Methods 0.000 description 5

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 4

- 239000007769 metal material Substances 0.000 description 4

- 229910052719 titanium Inorganic materials 0.000 description 4

- 235000012431 wafers Nutrition 0.000 description 4

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 3

- 239000000853 adhesive Substances 0.000 description 3

- 230000001070 adhesive effect Effects 0.000 description 3

- 239000002313 adhesive film Substances 0.000 description 3

- 229910052782 aluminium Inorganic materials 0.000 description 3

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 3

- 239000005388 borosilicate glass Substances 0.000 description 3

- 238000009713 electroplating Methods 0.000 description 3

- 238000007747 plating Methods 0.000 description 3

- BASFCYQUMIYNBI-UHFFFAOYSA-N platinum Chemical compound [Pt] BASFCYQUMIYNBI-UHFFFAOYSA-N 0.000 description 3

- 238000005498 polishing Methods 0.000 description 3

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 description 2

- QAOWNCQODCNURD-UHFFFAOYSA-N Sulfuric acid Chemical compound OS(O)(=O)=O QAOWNCQODCNURD-UHFFFAOYSA-N 0.000 description 2

- 238000005229 chemical vapour deposition Methods 0.000 description 2

- 230000008878 coupling Effects 0.000 description 2

- 238000010168 coupling process Methods 0.000 description 2

- 238000005859 coupling reaction Methods 0.000 description 2

- 238000005336 cracking Methods 0.000 description 2

- 229910052709 silver Inorganic materials 0.000 description 2

- 239000004332 silver Substances 0.000 description 2

- 239000004593 Epoxy Substances 0.000 description 1

- PNEYBMLMFCGWSK-UHFFFAOYSA-N aluminium oxide Inorganic materials [O-2].[O-2].[O-2].[Al+3].[Al+3] PNEYBMLMFCGWSK-UHFFFAOYSA-N 0.000 description 1

- 239000010407 anodic oxide Substances 0.000 description 1

- 229910052797 bismuth Inorganic materials 0.000 description 1

- JCXGWMGPZLAOME-UHFFFAOYSA-N bismuth atom Chemical compound [Bi] JCXGWMGPZLAOME-UHFFFAOYSA-N 0.000 description 1

- KGBXLFKZBHKPEV-UHFFFAOYSA-N boric acid Chemical compound OB(O)O KGBXLFKZBHKPEV-UHFFFAOYSA-N 0.000 description 1

- 239000004327 boric acid Substances 0.000 description 1

- 238000006243 chemical reaction Methods 0.000 description 1

- 239000000470 constituent Substances 0.000 description 1

- 239000003792 electrolyte Substances 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- -1 for example Substances 0.000 description 1

- 229910052738 indium Inorganic materials 0.000 description 1

- APFVFJFRJDLVQX-UHFFFAOYSA-N indium atom Chemical compound [In] APFVFJFRJDLVQX-UHFFFAOYSA-N 0.000 description 1

- 239000011810 insulating material Substances 0.000 description 1

- 239000012212 insulator Substances 0.000 description 1

- 238000010030 laminating Methods 0.000 description 1

- 229910052751 metal Inorganic materials 0.000 description 1

- 239000002184 metal Substances 0.000 description 1

- 229910052759 nickel Inorganic materials 0.000 description 1

- 229910052697 platinum Inorganic materials 0.000 description 1

- 229920001296 polysiloxane Polymers 0.000 description 1

- 238000007650 screen-printing Methods 0.000 description 1

- RMAQACBXLXPBSY-UHFFFAOYSA-N silicic acid Chemical compound O[Si](O)(O)O RMAQACBXLXPBSY-UHFFFAOYSA-N 0.000 description 1

- 235000012239 silicon dioxide Nutrition 0.000 description 1

- 239000007787 solid Substances 0.000 description 1

- 238000004528 spin coating Methods 0.000 description 1

- 238000004544 sputter deposition Methods 0.000 description 1

- 239000000126 substance Substances 0.000 description 1

- 238000006467 substitution reaction Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/46—Manufacturing multilayer circuits

- H05K3/4602—Manufacturing multilayer circuits characterized by a special circuit board as base or central core whereon additional circuit layers are built or additional circuit boards are laminated

- H05K3/4608—Manufacturing multilayer circuits characterized by a special circuit board as base or central core whereon additional circuit layers are built or additional circuit boards are laminated comprising an electrically conductive base or core

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/02—Details

- H05K1/0286—Programmable, customizable or modifiable circuits

- H05K1/0287—Programmable, customizable or modifiable circuits having an universal lay-out, e.g. pad or land grid patterns or mesh patterns

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/02—Details

- H05K1/03—Use of materials for the substrate

- H05K1/0306—Inorganic insulating substrates, e.g. ceramic, glass

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/09—Shape and layout

- H05K2201/09209—Shape and layout details of conductors

- H05K2201/095—Conductive through-holes or vias

- H05K2201/09609—Via grid, i.e. two-dimensional array of vias or holes in a single plane

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/0011—Working of insulating substrates or insulating layers

- H05K3/0017—Etching of the substrate by chemical or physical means

- H05K3/002—Etching of the substrate by chemical or physical means by liquid chemical etching

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/40—Forming printed elements for providing electric connections to or between printed circuits

- H05K3/4038—Through-connections; Vertical interconnect access [VIA] connections

- H05K3/4053—Through-connections; Vertical interconnect access [VIA] connections by thick-film techniques

- H05K3/4061—Through-connections; Vertical interconnect access [VIA] connections by thick-film techniques for via connections in inorganic insulating substrates

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/40—Forming printed elements for providing electric connections to or between printed circuits

- H05K3/42—Plated through-holes or plated via connections

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Manufacturing & Machinery (AREA)

- Production Of Multi-Layered Print Wiring Board (AREA)

Description

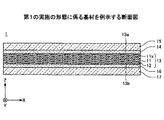

[第1の実施の形態に係る基材の構造]

まず、第1の実施の形態に係る基材の構造について説明する。図1は、第1の実施の形態に係る基材を例示する断面図である。図1において、X方向はコア層13の一方の面13aと平行な方向、Y方向はコア層13の一方の面13a内においてX方向に垂直な方向、Z方向はX方向及びY方向に垂直な方向(基材1の厚さ方向)をそれぞれ示している(以降の図においても同様)。

次に、第1の実施の形態に係る基材の製造方法について説明する。図2〜図5は、第1の実施の形態に係る基材の製造工程を例示する図である。

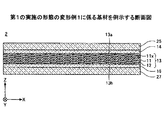

第1の実施の形態の変形例1では、シリコン層に代えて、ガラス層を形成する例を示す。なお、第1の実施の形態の変形例1において、既に説明した実施の形態と同一構成部品についての説明は省略する。

第2の実施の形態では、コア層13の一方の面13a及び他方の面13bに配線層を形成する例を示す。なお、第2の実施の形態において、既に説明した実施の形態と同一構成部品についての説明は省略する。

第2の実施の形態の変形例1では、配線層を擬似同軸構造とする例を示す。なお、第2の実施の形態の変形例1において、既に説明した実施の形態と同一構成部品についての説明は省略する。

第2の実施の形態の変形例2では、コア層の両面に直接ガラス層を形成する例を示す。なお、第2の実施の形態の変形例2において、既に説明した実施の形態と同一構成部品についての説明は省略する。

第3の実施の形態では、コア層13の一方の面13aに配線層及び絶縁層を積層形成する例を示す。なお、第3の実施の形態において、既に説明した実施の形態と同一構成部品についての説明は省略する。

第3の実施の形態に係る基材6を配線基板として用いる例を示す。図11は、第3の実施の形態に係る基材を用いた配線基板を例示する断面図である。

7 配線基板

11 板状体

11x 貫通孔

12 線状導体

13 コア層

13a コア層の一方の面

13b コア層の他方の面

14、16 接着層

15、17 シリコン層

15x、17x、61x、63x ビアホール

25、27、55、57 ガラス層

31、32、62、64、71、73 配線層

31s、32s 信号配線

31g、32g GND配線

61、63 絶縁層

72、74 ソルダーレジスト層

72x、74x 開口部

P 間隔

φ 直径

Claims (5)

- 酸化アルミニウムからなる板状体、及び前記板状体を厚さ方向に貫通する複数の線状導体を備えたコア層と、

前記コア層の一方の面側及び他方の面側に、接着層を介して接合された板状のシリコン層又はガラス層と、を有し、

前記線状導体は、隣接する前記線状導体の間隔が、前記線状導体の直径よりも小さくなるように形成されている基材。 - 前記一方の面側及び前記他方の面側の何れか一面側には、接着層を介して、前記シリコン層が接合され、

前記一面側の反対面側には、接着層を介して、前記ガラス層が接合されている請求項1記載の基材。 - 前記一方の面側及び前記他方の面側の少なくとも一面側には、複数の前記線状導体と電気的に接続され、前記接着層に覆われた配線層が形成されている請求項1又は2記載の基材。

- 酸化アルミニウムからなる板状体、及び前記板状体を厚さ方向に貫通する複数の線状導体を備えたコア層を有し、

前記コア層の一方の面側及び他方の面側には、複数の前記線状導体と電気的に接続された配線層、前記配線層を覆う絶縁層、前記絶縁層を介して前記配線層と電気的に接続された第2の配線層、前記第2の配線層を覆う接着層、板状のシリコン層又はガラス層が順次積層され、

前記線状導体は、隣接する前記線状導体の間隔が、前記線状導体の直径よりも小さくなるように形成されている基材。 - 前記配線層は、信号配線と前記信号配線を平面視において囲むように形成されたグランド配線とを含む請求項3又は4記載の基材。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2011185134A JP5864954B2 (ja) | 2011-08-26 | 2011-08-26 | 基材 |

| US13/588,013 US20130048350A1 (en) | 2011-08-26 | 2012-08-17 | Base member |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2011185134A JP5864954B2 (ja) | 2011-08-26 | 2011-08-26 | 基材 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2013046036A JP2013046036A (ja) | 2013-03-04 |

| JP2013046036A5 JP2013046036A5 (ja) | 2014-08-14 |

| JP5864954B2 true JP5864954B2 (ja) | 2016-02-17 |

Family

ID=47741998

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2011185134A Expired - Fee Related JP5864954B2 (ja) | 2011-08-26 | 2011-08-26 | 基材 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US20130048350A1 (ja) |

| JP (1) | JP5864954B2 (ja) |

Families Citing this family (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20140151095A1 (en) * | 2012-12-05 | 2014-06-05 | Samsung Electro-Mechanics Co., Ltd. | Printed circuit board and method for manufacturing the same |

| WO2017154167A1 (ja) * | 2016-03-10 | 2017-09-14 | 三井金属鉱業株式会社 | 多層積層板及びこれを用いた多層プリント配線板の製造方法 |

| WO2018181236A1 (ja) * | 2017-03-31 | 2018-10-04 | パナソニックIpマネジメント株式会社 | 半導体装置及びその製造方法 |

| TW202119877A (zh) * | 2019-11-05 | 2021-05-16 | 南韓商普因特工程有限公司 | 多層配線基板及包括其的探針卡 |

| KR20210121445A (ko) * | 2020-03-30 | 2021-10-08 | (주)포인트엔지니어링 | 양극산화막 구조체 |

Family Cites Families (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4712161A (en) * | 1985-03-25 | 1987-12-08 | Olin Corporation | Hybrid and multi-layer circuitry |

| JPH10173410A (ja) * | 1996-12-12 | 1998-06-26 | Sharp Corp | ストリップ線路を用いた伝送回路 |

| JPH11214450A (ja) * | 1997-11-18 | 1999-08-06 | Matsushita Electric Ind Co Ltd | 電子部品実装体とそれを用いた電子機器と電子部品実装体の製造方法 |

| JP3603663B2 (ja) * | 1999-04-28 | 2004-12-22 | 株式会社デンソー | 厚膜回路基板とその製造方法 |

| JP3530149B2 (ja) * | 2001-05-21 | 2004-05-24 | 新光電気工業株式会社 | 配線基板の製造方法及び半導体装置 |

| JP3964822B2 (ja) * | 2003-05-07 | 2007-08-22 | 日東電工株式会社 | 回路付サスペンション基板の製造方法 |

| TWI255466B (en) * | 2004-10-08 | 2006-05-21 | Ind Tech Res Inst | Polymer-matrix conductive film and method for fabricating the same |

| JP5068060B2 (ja) * | 2006-10-30 | 2012-11-07 | 新光電気工業株式会社 | 半導体パッケージおよびその製造方法 |

| JPWO2008069055A1 (ja) * | 2006-11-28 | 2010-03-18 | 京セラ株式会社 | 配線基板およびそれを用いた半導体素子の実装構造体 |

| TWI343109B (en) * | 2007-03-23 | 2011-06-01 | Unimicron Technology Corp | Flip-chip substrate using aluminum oxide as its core sunbstrate |

| JP5145110B2 (ja) * | 2007-12-10 | 2013-02-13 | 富士フイルム株式会社 | 異方導電性接合パッケージの製造方法 |

| JP5385682B2 (ja) * | 2009-05-19 | 2014-01-08 | 新光電気工業株式会社 | 電子部品の実装構造 |

| JP2011151185A (ja) * | 2010-01-21 | 2011-08-04 | Shinko Electric Ind Co Ltd | 配線基板及び半導体装置 |

-

2011

- 2011-08-26 JP JP2011185134A patent/JP5864954B2/ja not_active Expired - Fee Related

-

2012

- 2012-08-17 US US13/588,013 patent/US20130048350A1/en not_active Abandoned

Also Published As

| Publication number | Publication date |

|---|---|

| US20130048350A1 (en) | 2013-02-28 |

| JP2013046036A (ja) | 2013-03-04 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| WO2019117073A1 (ja) | ガラス配線基板、その製造方法及び半導体装置 | |

| TWI508196B (zh) | 具有內建加強層之凹穴基板之製造方法 | |

| JP4274290B2 (ja) | 両面電極構造の半導体装置の製造方法 | |

| US7939935B2 (en) | Electronic device substrate, electronic device and methods for fabricating the same | |

| US7745924B2 (en) | Capacitor embedded in interposer, semiconductor device including the same, and method for manufacturing capacitor embedded in interposer | |

| JP5237242B2 (ja) | 配線回路構造体およびそれを用いた半導体装置の製造方法 | |

| JP5833398B2 (ja) | 配線基板及びその製造方法、半導体装置 | |

| CN105814687B (zh) | 半导体封装及其安装结构 | |

| JP5608605B2 (ja) | 配線基板の製造方法 | |

| JP5864954B2 (ja) | 基材 | |

| TWI509760B (zh) | 用於半導體裝置之製造方法 | |

| JP2007184438A (ja) | 半導体装置 | |

| JP2017017300A (ja) | チップパッケージ | |

| JP2013004576A (ja) | 半導体装置 | |

| WO2018117111A1 (ja) | 貫通電極基板、半導体装置及び貫通電極基板の製造方法 | |

| JP2019016672A (ja) | 実装基板及び実装基板の製造方法 | |

| CN104247584A (zh) | 印刷电路板及其制造方法 | |

| JP2009194079A (ja) | 半導体装置用配線基板とその製造方法及びそれを用いた半導体装置 | |

| JPWO2011002031A1 (ja) | 素子搭載用基板および半導体モジュール | |

| JP5786331B2 (ja) | 部品内蔵配線板 | |

| JPWO2009028596A1 (ja) | 受動素子内蔵基板、製造方法、及び半導体装置 | |

| JP6756134B2 (ja) | 薄膜部品シート、電子部品内蔵基板、及び薄膜部品シートの製造方法 | |

| JP6100617B2 (ja) | 多層配線基板およびプローブカード用基板 | |

| JP5980554B2 (ja) | 電気的接続部材、検査方法及び電気的接続部材の製造方法 | |

| JP2012009560A (ja) | フレキシブル多層配線板、フレキシブル半導体装置及びフレキシブル多層配線板の製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140627 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20140627 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20150316 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20150407 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20150601 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20151215 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20151225 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5864954 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| LAPS | Cancellation because of no payment of annual fees |