JP5174355B2 - 配線基板及びその製造方法と半導体装置 - Google Patents

配線基板及びその製造方法と半導体装置 Download PDFInfo

- Publication number

- JP5174355B2 JP5174355B2 JP2007024228A JP2007024228A JP5174355B2 JP 5174355 B2 JP5174355 B2 JP 5174355B2 JP 2007024228 A JP2007024228 A JP 2007024228A JP 2007024228 A JP2007024228 A JP 2007024228A JP 5174355 B2 JP5174355 B2 JP 5174355B2

- Authority

- JP

- Japan

- Prior art keywords

- wiring board

- unit

- substrate

- unit wiring

- wiring pattern

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L2224/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

- H01L2224/161—Disposition

- H01L2224/16151—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/16221—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/16225—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/49—Structure, shape, material or disposition of the wire connectors after the connecting process of a plurality of wire connectors

- H01L2224/491—Disposition

- H01L2224/4912—Layout

- H01L2224/49175—Parallel arrangements

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/151—Die mounting substrate

- H01L2924/153—Connection portion

- H01L2924/1531—Connection portion the connection portion being formed only on the surface of the substrate opposite to the die mounting surface

- H01L2924/15311—Connection portion the connection portion being formed only on the surface of the substrate opposite to the die mounting surface being a ball array, e.g. BGA

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/181—Encapsulation

Landscapes

- Production Of Multi-Layered Print Wiring Board (AREA)

Description

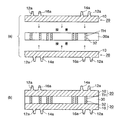

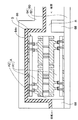

図2〜図8は本発明の第1実施形態の配線基板の製造方法を示す断面図、図9は本発明の第1実施形態の配線基板を示す断面図、図10は同じく半導体装置を示す断面図である。

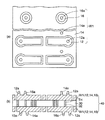

図11は本発明の第2実施形態の半導体装置を示す断面図、図12は本発明の第2実施形態に係るリードフレームから形成された第1配線パターンに半導体チップが接続されて実装された様子を示す平面図である。

Claims (8)

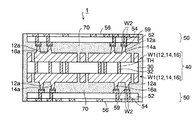

- 基板と、前記基板の少なくとも上面に形成され、垂直方向に立設する層間接続部が一体的に設けられた第1配線パターンとにより構成される第1ユニット配線板と、

前記第1ユニット配線板の上に形成され、上下側を導通可能にする第2配線パターンを備えた第2ユニット配線板と、

前記第1ユニット配線板と前記第2ユニット配線板の間に充填された樹脂部とを有し、

前記第1配線パターンは電源プレーン及びグランドプレーンを含み、前記第2配線パターンは前記第1ユニット配線板の前記層間接続部に接続され、

前記第1配線パターン及びそれに繋がって立設する前記層間接続部は、リードフレームが加工されて一体的に形成され、前記第1配線パターンの厚みは前記第2配線パターンの厚みより厚いことを特徴とする配線基板。 - 前記第1ユニット配線板の前記基板は貫通電極を備えており、

前記第1ユニット配線板は、前記基板の両面側に、前記貫通電極に接続されて外側に前記層間接続部が立設した前記第1配線パターンがそれぞれ形成されて構成され、

前記第2ユニット配線板が前記第1ユニット配線板の両面側の第1配線パターンの前記層間接続部にそれぞれ接続されて配置されており、

前記樹脂部は、前記第1ユニット配線板とその両面側に配置された前記第2ユニット配線板との間にそれぞれ充填されていることを特徴とする請求項1に記載の配線基板。 - 請求項1又は2の配線基板と、

前記配線基板における前記第2ユニット配線板の外面側の前記第2配線パターンにフリップチップ接続された半導体チップとを有することを特徴とする半導体装置。 - 前記第1ユニット配線板の上に前記樹脂部に埋設された状態で実装され、前記第1配線パターンに接続された電子部品をさらに有することを特徴とする請求項3に記載の半導体装置。

- 基板と、垂直方向に立設する層間接続部が設けられて、連結部によって相互に繋がって形成された第1配線パターンを備えたリードフレームとを用意する工程と、

前記基板の少なくとも上面に、前記第1配線パターンの前記層間接続部が外側に配置されるように前記リードフレームを接着する工程と、

前記リードフレームの前記連結部を除去して前記第1配線パターンを相互に分離することにより、前記基板と前記第1配線パターンにより構成される第1ユニット配線板を得る工程と、

上下側を導通可能にする第2配線パターンを備えた第2ユニット配線板を用意し、前記第1ユニット配線板の前記第1配線パターンの前記層間接続部に、前記第2ユニット配線板の前記第2配線パターンを接続する工程と、

真空トランスファモールド法によって、前記第1ユニット配線板と前記第2ユニット配線板の間に樹脂を充填することにより、前記第1ユニット配線板及び前記第2ユニット配線板を一体化する樹脂部を形成する工程とを有し、

前記リードフレームを用意する工程は、

金属薄板の上に形成されたマスク材をマスクにして、前記金属薄板を厚みの途中までウェットエッチングすることにより前記層間接続部を形成する工程と、

前記層間接続部を形成する工程の前又は後に、前記金属薄板を貫通加工することにより前記第1配線パターンを形成する工程とを含むことを特徴とする配線基板の製造方法。 - 前記基板を用意する工程において、前記基板は半硬化状態のプリプレグからなり、

前記リードフレームを前記基板に接着する工程において、前記プリプレグを熱処理して硬化させることによって前記基板を得ると共に、前記基板の上に前記リードフレームを接着させることを特徴とする請求項5に記載の配線基板の製造方法。 - 前記基板は貫通電極を備えており、

前記リードフレームを前記基板に接着する工程において、前記基板の両面側に、前記貫通電極に接続される前記リードフレームをそれぞれ接着し、

第1ユニット配線板を得る工程、及び前記第2ユニット配線板を前記第1ユニット配線板に接続する工程は、前記基板の両面側で行われ、

前記樹脂部は、前記第1ユニット配線板とその両面側に配置された前記第2ユニット配線板の間に充填されることを特徴とする請求項5に記載の配線基板の製造方法。 - 前記第1ユニット配線板を得る工程の後に、第1ユニット配線板の上に、電子部品を前記第1配線パターンに接続して実装する工程をさらに有し、

樹脂部を形成する工程において、前記電子部品が樹脂部に埋設されることを特徴とする請求項5に記載の配線基板の製造方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007024228A JP5174355B2 (ja) | 2007-02-02 | 2007-02-02 | 配線基板及びその製造方法と半導体装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007024228A JP5174355B2 (ja) | 2007-02-02 | 2007-02-02 | 配線基板及びその製造方法と半導体装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2008192740A JP2008192740A (ja) | 2008-08-21 |

| JP2008192740A5 JP2008192740A5 (ja) | 2010-02-12 |

| JP5174355B2 true JP5174355B2 (ja) | 2013-04-03 |

Family

ID=39752576

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2007024228A Active JP5174355B2 (ja) | 2007-02-02 | 2007-02-02 | 配線基板及びその製造方法と半導体装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5174355B2 (ja) |

Families Citing this family (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5577760B2 (ja) * | 2009-03-09 | 2014-08-27 | 新光電気工業株式会社 | パッケージ基板および半導体装置の製造方法 |

| JP2023006236A (ja) * | 2021-06-30 | 2023-01-18 | 株式会社オートネットワーク技術研究所 | 回路構成体及び電気接続箱 |

Family Cites Families (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0383396A (ja) * | 1989-08-28 | 1991-04-09 | Fujitsu Ltd | 多層プリント配線板 |

| JPH08181417A (ja) * | 1994-12-26 | 1996-07-12 | Furukawa Electric Co Ltd:The | 回路材の製造方法 |

| JP3553043B2 (ja) * | 2001-01-19 | 2004-08-11 | 松下電器産業株式会社 | 部品内蔵モジュールとその製造方法 |

| JP2004014679A (ja) * | 2002-06-05 | 2004-01-15 | Fcm Kk | 積層用回路基板および積層回路 |

-

2007

- 2007-02-02 JP JP2007024228A patent/JP5174355B2/ja active Active

Also Published As

| Publication number | Publication date |

|---|---|

| JP2008192740A (ja) | 2008-08-21 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4926692B2 (ja) | 配線基板及びその製造方法と半導体装置 | |

| JP4055717B2 (ja) | 半導体装置およびその製造方法 | |

| JP5711472B2 (ja) | 配線基板及びその製造方法並びに半導体装置 | |

| JP6539992B2 (ja) | 配線回路基板、半導体装置、配線回路基板の製造方法、半導体装置の製造方法 | |

| US9232657B2 (en) | Wiring substrate and manufacturing method of wiring substrate | |

| JP4298559B2 (ja) | 電子部品実装構造及びその製造方法 | |

| JP5395360B2 (ja) | 電子部品内蔵基板の製造方法 | |

| JP5389770B2 (ja) | 電子素子内蔵印刷回路基板及びその製造方法 | |

| US7705446B2 (en) | Package structure having semiconductor chip embedded therein and method for fabricating the same | |

| KR101119303B1 (ko) | 전자부품 내장형 인쇄회로기판 및 그 제조방법 | |

| KR102107037B1 (ko) | 인쇄회로기판 및 그 제조방법 | |

| US20140151876A1 (en) | Semiconductor package and process for fabricating same | |

| JP4730426B2 (ja) | 実装基板及び半導体モジュール | |

| US9313894B2 (en) | Wiring substrate and manufacturing method of wiring substrate | |

| KR20160091050A (ko) | 전자부품 내장 기판 및 그 제조방법 | |

| JPWO2007126090A1 (ja) | 回路基板、電子デバイス装置及び回路基板の製造方法 | |

| JP2010034403A (ja) | 配線基板及び電子部品装置 | |

| JP2015106615A (ja) | プリント配線板、プリント配線板の製造方法 | |

| JP2008028376A (ja) | 回路基板、半導体モジュールおよび回路基板の製造方法 | |

| JP2017108019A (ja) | 配線基板、半導体パッケージ、半導体装置、配線基板の製造方法及び半導体パッケージの製造方法 | |

| JP5406572B2 (ja) | 電子部品内蔵配線基板及びその製造方法 | |

| JP2009252942A (ja) | 部品内蔵配線板、部品内蔵配線板の製造方法 | |

| JP5174355B2 (ja) | 配線基板及びその製造方法と半導体装置 | |

| JP4438389B2 (ja) | 半導体装置の製造方法 | |

| KR101092945B1 (ko) | 패키지 기판, 이를 구비한 전자소자 패키지, 및 패키지 기판 제조 방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20091216 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20091216 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20111007 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20111025 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20111213 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120612 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120726 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20121218 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20121228 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5174355 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |