JP5134779B2 - 遅延同期回路 - Google Patents

遅延同期回路 Download PDFInfo

- Publication number

- JP5134779B2 JP5134779B2 JP2006067243A JP2006067243A JP5134779B2 JP 5134779 B2 JP5134779 B2 JP 5134779B2 JP 2006067243 A JP2006067243 A JP 2006067243A JP 2006067243 A JP2006067243 A JP 2006067243A JP 5134779 B2 JP5134779 B2 JP 5134779B2

- Authority

- JP

- Japan

- Prior art keywords

- signal

- circuit

- locked loop

- delay

- control

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 230000000630 rising effect Effects 0.000 description 23

- 239000004065 semiconductor Substances 0.000 description 21

- 230000007704 transition Effects 0.000 description 21

- 238000010586 diagram Methods 0.000 description 20

- 230000007257 malfunction Effects 0.000 description 10

- 238000000034 method Methods 0.000 description 10

- 230000005526 G1 to G0 transition Effects 0.000 description 7

- 230000003111 delayed effect Effects 0.000 description 7

- 230000005540 biological transmission Effects 0.000 description 6

- 238000011084 recovery Methods 0.000 description 6

- 230000001360 synchronised effect Effects 0.000 description 6

- 238000009966 trimming Methods 0.000 description 4

- 230000000873 masking effect Effects 0.000 description 2

- 230000004048 modification Effects 0.000 description 2

- 238000012986 modification Methods 0.000 description 2

- 230000001934 delay Effects 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 238000004519 manufacturing process Methods 0.000 description 1

- 230000003252 repetitive effect Effects 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03L—AUTOMATIC CONTROL, STARTING, SYNCHRONISATION OR STABILISATION OF GENERATORS OF ELECTRONIC OSCILLATIONS OR PULSES

- H03L7/00—Automatic control of frequency or phase; Synchronisation

- H03L7/06—Automatic control of frequency or phase; Synchronisation using a reference signal applied to a frequency- or phase-locked loop

- H03L7/08—Details of the phase-locked loop

- H03L7/085—Details of the phase-locked loop concerning mainly the frequency- or phase-detection arrangement including the filtering or amplification of its output signal

- H03L7/089—Details of the phase-locked loop concerning mainly the frequency- or phase-detection arrangement including the filtering or amplification of its output signal the phase or frequency detector generating up-down pulses

- H03L7/0891—Details of the phase-locked loop concerning mainly the frequency- or phase-detection arrangement including the filtering or amplification of its output signal the phase or frequency detector generating up-down pulses the up-down pulses controlling source and sink current generators, e.g. a charge pump

-

- A—HUMAN NECESSITIES

- A23—FOODS OR FOODSTUFFS; TREATMENT THEREOF, NOT COVERED BY OTHER CLASSES

- A23N—MACHINES OR APPARATUS FOR TREATING HARVESTED FRUIT, VEGETABLES OR FLOWER BULBS IN BULK, NOT OTHERWISE PROVIDED FOR; PEELING VEGETABLES OR FRUIT IN BULK; APPARATUS FOR PREPARING ANIMAL FEEDING- STUFFS

- A23N5/00—Machines for hulling, husking or cracking nuts

- A23N5/08—Machines for hulling, husking or cracking nuts for removing fleshy or fibrous hulls of nuts

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B02—CRUSHING, PULVERISING, OR DISINTEGRATING; PREPARATORY TREATMENT OF GRAIN FOR MILLING

- B02C—CRUSHING, PULVERISING, OR DISINTEGRATING IN GENERAL; MILLING GRAIN

- B02C4/00—Crushing or disintegrating by roller mills

- B02C4/28—Details

- B02C4/30—Shape or construction of rollers

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B02—CRUSHING, PULVERISING, OR DISINTEGRATING; PREPARATORY TREATMENT OF GRAIN FOR MILLING

- B02C—CRUSHING, PULVERISING, OR DISINTEGRATING IN GENERAL; MILLING GRAIN

- B02C4/00—Crushing or disintegrating by roller mills

- B02C4/28—Details

- B02C4/42—Driving mechanisms; Roller speed control

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03L—AUTOMATIC CONTROL, STARTING, SYNCHRONISATION OR STABILISATION OF GENERATORS OF ELECTRONIC OSCILLATIONS OR PULSES

- H03L7/00—Automatic control of frequency or phase; Synchronisation

- H03L7/06—Automatic control of frequency or phase; Synchronisation using a reference signal applied to a frequency- or phase-locked loop

- H03L7/08—Details of the phase-locked loop

- H03L7/081—Details of the phase-locked loop provided with an additional controlled phase shifter

- H03L7/0812—Details of the phase-locked loop provided with an additional controlled phase shifter and where no voltage or current controlled oscillator is used

- H03L7/0816—Details of the phase-locked loop provided with an additional controlled phase shifter and where no voltage or current controlled oscillator is used the controlled phase shifter and the frequency- or phase-detection arrangement being connected to a common input

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03L—AUTOMATIC CONTROL, STARTING, SYNCHRONISATION OR STABILISATION OF GENERATORS OF ELECTRONIC OSCILLATIONS OR PULSES

- H03L7/00—Automatic control of frequency or phase; Synchronisation

- H03L7/06—Automatic control of frequency or phase; Synchronisation using a reference signal applied to a frequency- or phase-locked loop

- H03L7/08—Details of the phase-locked loop

- H03L7/10—Details of the phase-locked loop for assuring initial synchronisation or for broadening the capture range

Landscapes

- Engineering & Computer Science (AREA)

- Food Science & Technology (AREA)

- Life Sciences & Earth Sciences (AREA)

- Chemical & Material Sciences (AREA)

- Polymers & Plastics (AREA)

- Stabilization Of Oscillater, Synchronisation, Frequency Synthesizers (AREA)

- Pulse Circuits (AREA)

- Dram (AREA)

Description

図1に、本発明の実施形態1に係る遅延同期回路の構成を示す。

結局、図6記載のパルス発生器24は、基準信号(Fr)の最初の立ち上がりエッジを検出してワンショットパルス信号を出力してその後はハイを保持し続ける制御信号(S)を生成する。

図7に、本発明の実施形態2に係る遅延同期回路の構成を示す。

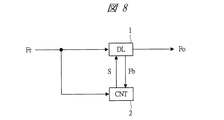

図8に、本発明の実施形態3に係る遅延同期回路の構成例を示す。本実施形態3は前記実施形態2の変形例である。

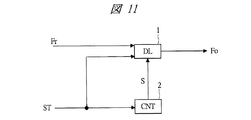

図11に、本発明の実施形態4に係る遅延同期回路の構成を示す。

本発明の実施形態5に係る半導体集積回路装置は、前記実施形態1〜4に係る遅延同期回路を半導体集積回路装置に適用したものである。

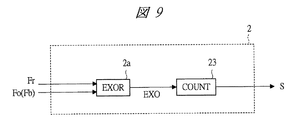

2,3 制御回路(CNT)

2a 排他的論理和回路(EXOR)

4 リンク層(LINK)

5 発振子

6 半導体集積回路装置(LSI)

7 メディア

8 ピックアップ(Pick−up)

9 ホスト(HOST)

10 遅延同期回路(DLL)

11 位相周波数比較器(PFD)

11a,11f,11g,111,112,113,114,115,116,117,118,119,244 NANDゲート

11b,11c,11d,11e,212,213,214,215,216,217,218,242,246 インバータ

12 チャージポンプ(CP)

13 ループフィルタ(LF)

14 電圧制御遅延線(VCDL)

15 プリチャージ(PC)

16 エッジコンバイナ(EC)

21 遅延回路(DELAY)

22 トリミング部(TRIM)

23 カウンタ(COUNT)

24 パルス発生器(SHOT)

31 アナログフロントエンド(AFE)

32 エンコーダ(ENC)

33 デシリアライザ(DES)

34,35 クロックデータリカバリ(CDR)

36 マルチプレクサ(MUX)

37 デコーダ(DEC)

38 シリアライザ(SER)

61,611,613 論理回路(LOGIC)

62 送受信部(ATAPI)

241,243 NORゲート

245 Dフリップフロップ(DFF)

247 スタンバイシーケンス回路(SEQ)

Claims (10)

- 遅延同期ループと、

前記遅延同期ループの動作を制御する制御信号を出力する制御回路とを具備して成り、

前記遅延同期ループは、基準信号と前記制御信号とが入力して出力信号を出力し、

前記制御回路は、基準信号と前記出力信号とが入力して前記制御信号を出力し、

前記制御回路は、排他的論理和回路とカウンタとを含み、

前記排他的論理和回路は、前記基準信号と前記出力信号とが入力し、前記排他的論理和回路の出力が前記カウンタに入力され、

前記カウンタにより前記排他的論理和回路の出力をカウントし、前記カウンタのカウント数が設定値に到達するまでは前記制御信号として前記遅延同期ループが動作しない設定信号を出力し、前記カウンタのカウント数が前記設定値に到達した後、前記制御信号として前記遅延同期ループが動作する設定信号を出力することを特徴とする遅延同期回路。 - 遅延同期ループと、

前記遅延同期ループの動作を制御する制御信号を出力する制御回路とを具備して成り、

前記遅延同期ループは、基準信号と前記制御信号とが入力して出力信号を出力し、

前記制御回路は、基準信号が入力して前記制御信号を出力し、

前記遅延同期ループは、さらに、帰還信号を出力し、前記帰還信号が前記制御回路に入力され、

前記制御回路は、排他的論理和回路とカウンタとを含み、

前記排他的論理和回路は、前記基準信号と前記帰還信号とが入力し、前記排他的論理和回路の出力が前記カウンタに入力され、

前記カウンタにより前記排他的論理和回路の出力をカウントし、前記カウンタのカウント数が設定値に到達するまでは前記制御信号として前記遅延同期ループが動作しない設定信号を出力し、前記カウンタのカウント数が前記設定値に到達した後、前記制御信号として前記遅延同期ループが動作する設定信号を出力することを特徴とする遅延同期回路。 - 請求項1において、

前記遅延同期ループは、位相比較器を具備して成り、

前記基準信号と前記出力信号と前記制御信号とが、前記位相比較器に入力し、

前記位相比較器は、前記制御信号を用い、前記基準信号と前記出力信号との位相を比較することを特徴とする遅延同期回路。 - 請求項2において、

前記遅延同期ループは、位相比較器を具備して成り、

前記基準信号と前記出力信号と前記制御信号とが、前記位相比較器に入力し、

前記位相比較器は、前記制御信号を用い、前記基準信号と前記出力信号との位相を比較することを特徴とする遅延同期回路。 - 請求項1において、

前記遅延同期ループは、さらに、スタンバイ信号が入力し、

前記制御回路は、さらに、前記スタンバイ信号が入力する回路であることを特徴とする遅延同期回路。 - 請求項1において、

前記遅延同期ループは、位相比較器を具備して成り、

前記基準信号と前記出力信号と前記制御信号とが、前記位相比較器に入力し、

前記位相比較器は、前記制御信号により、前記基準信号と前記出力信号との位相を比較する回路であることを特徴とする遅延同期回路。 - 請求項6において、

前記遅延同期ループは、さらに、スタンバイ信号が入力し、

前記制御回路は、さらに、前記スタンバイ信号が入力する回路であることを特徴とする遅延同期回路。 - 請求項2において、

前記遅延同期ループは、さらに、スタンバイ信号が入力し、

前記制御回路は、さらに、前記スタンバイ信号が入力する回路であることを特徴とする遅延同期回路。 - 請求項2において、

前記遅延同期ループは、位相比較器を具備して成り、

前記基準信号と前記出力信号と前記制御信号とが、前記位相比較器に入力し、

前記位相比較器は、前記制御信号により、前記基準信号と前記出力信号との位相を比較する回路であることを特徴とする遅延同期回路。 - 請求項9において、

前記遅延同期ループは、さらに、スタンバイ信号が入力し、

前記制御回路は、さらに、前記スタンバイ信号が入力する回路であることを特徴とする遅延同期回路。

Priority Applications (7)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2006067243A JP5134779B2 (ja) | 2006-03-13 | 2006-03-13 | 遅延同期回路 |

| TW095145171A TWI399038B (zh) | 2006-03-13 | 2006-12-05 | Delay synchronous circuit and semiconductor integrated circuit device |

| CN2006101566680A CN101039108B (zh) | 2006-03-13 | 2006-12-30 | 延迟同步电路及半导体集成电路器件 |

| US11/648,652 US7482850B2 (en) | 2006-03-13 | 2007-01-03 | Delay locked loop circuit and semiconductor integrated circuit device |

| KR1020070002478A KR20070093322A (ko) | 2006-03-13 | 2007-01-09 | 지연동기회로 및 반도체 집적회로장치 |

| EP07000456.9A EP1835623B1 (en) | 2006-03-13 | 2007-01-10 | Delay locked loop circuit and semiconductor integrated circuit device |

| US12/354,391 US7675334B2 (en) | 2006-03-13 | 2009-01-15 | Delay locked loop circuit and semiconductor integrated circuit device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2006067243A JP5134779B2 (ja) | 2006-03-13 | 2006-03-13 | 遅延同期回路 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2007243877A JP2007243877A (ja) | 2007-09-20 |

| JP2007243877A5 JP2007243877A5 (ja) | 2009-03-12 |

| JP5134779B2 true JP5134779B2 (ja) | 2013-01-30 |

Family

ID=38050939

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2006067243A Expired - Fee Related JP5134779B2 (ja) | 2006-03-13 | 2006-03-13 | 遅延同期回路 |

Country Status (6)

| Country | Link |

|---|---|

| US (2) | US7482850B2 (ja) |

| EP (1) | EP1835623B1 (ja) |

| JP (1) | JP5134779B2 (ja) |

| KR (1) | KR20070093322A (ja) |

| CN (1) | CN101039108B (ja) |

| TW (1) | TWI399038B (ja) |

Families Citing this family (19)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8169241B2 (en) | 2008-01-15 | 2012-05-01 | Atmel Rousset S.A.S. | Proportional phase comparator and method for phase-aligning digital signals |

| JP2009278528A (ja) * | 2008-05-16 | 2009-11-26 | Elpida Memory Inc | Dll回路、および半導体装置 |

| KR100996175B1 (ko) * | 2008-12-26 | 2010-11-24 | 주식회사 하이닉스반도체 | 반도체 장치 |

| KR101012678B1 (ko) * | 2009-02-04 | 2011-02-09 | 연세대학교 산학협력단 | 지연 동기 루프 및 이를 포함하는 전자 장치 |

| TWI474184B (zh) * | 2009-06-08 | 2015-02-21 | Via Tech Inc | 通用序列匯流排裝置與系統 |

| JP5588254B2 (ja) | 2009-08-04 | 2014-09-10 | キヤノン株式会社 | 遅延同期ループ回路 |

| TWI396386B (zh) * | 2010-05-06 | 2013-05-11 | Princeton Technology Corp | 可整合於晶片中之單擊電路、可縮短啟動時間之發射器及其方法 |

| US8248124B2 (en) * | 2010-06-03 | 2012-08-21 | Intel Corporation | Methods and apparatuses for delay-locked loops and phase-locked loops |

| KR102053352B1 (ko) * | 2013-02-25 | 2019-12-09 | 삼성전자주식회사 | 고조파 락을 방지할 수 있는 위상 동기 루프 및 이를 포함하는 장치들 |

| KR101657339B1 (ko) * | 2013-05-22 | 2016-09-19 | 매그나칩 반도체 유한회사 | Dll 동작 모드 제어회로 및 그 방법 |

| US9584105B1 (en) * | 2016-03-10 | 2017-02-28 | Analog Devices, Inc. | Timing generator for generating high resolution pulses having arbitrary widths |

| JP6390683B2 (ja) * | 2016-09-28 | 2018-09-19 | ミツミ電機株式会社 | 半導体集積回路 |

| WO2018208990A1 (en) * | 2017-05-09 | 2018-11-15 | The Regents Of The University Of California | Systems and methods for low-power near-field-communication |

| US11387685B2 (en) | 2017-08-14 | 2022-07-12 | The Regents Of The University Of California | Load-induced resonance-shift-keying modulation scheme for simultaneous near-field wireless power and data transmission through a pair of inductive coils |

| US11527992B2 (en) | 2019-09-19 | 2022-12-13 | Analog Devices International Unlimited Company | Rotary traveling wave oscillators with distributed stubs |

| CN113179099B (zh) * | 2020-09-18 | 2022-04-01 | 上海司南卫星导航技术股份有限公司 | 一种锁相环电路和其控制方法、半导体器件及电子设备 |

| US11539353B2 (en) * | 2021-02-02 | 2022-12-27 | Analog Devices International Unlimited Company | RTWO-based frequency multiplier |

| US11290114B1 (en) | 2021-06-01 | 2022-03-29 | SambaNova Systems, Inc. | Variable-length clock stretcher with passive mode jitter reduction |

| CN113381753B (zh) * | 2021-06-08 | 2022-07-12 | 天津大学 | 用于延迟锁相环的启动电路 |

Family Cites Families (20)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS6098727A (ja) * | 1983-11-04 | 1985-06-01 | Mitsubishi Electric Corp | 同期はずれ検出回路 |

| JPS62247624A (ja) * | 1986-04-07 | 1987-10-28 | Mitsubishi Electric Corp | 位相同期ル−プ回路 |

| JPS63136825A (ja) * | 1986-11-28 | 1988-06-09 | Mitsubishi Electric Corp | 同期・非同期状態検出カウンタ−付位相ロツクル−プ |

| JP3275222B2 (ja) * | 1994-03-04 | 2002-04-15 | 富士通株式会社 | 位相同期発振器 |

| JP3481148B2 (ja) * | 1998-10-15 | 2003-12-22 | 富士通株式会社 | Dll回路を有する集積回路装置 |

| JPH11205102A (ja) * | 1998-01-13 | 1999-07-30 | Mitsubishi Electric Corp | 遅延同期回路 |

| US6239634B1 (en) * | 1999-05-19 | 2001-05-29 | Parthus Technologies | Apparatus and method for ensuring the correct start-up and locking of a delay locked loop |

| JP3808670B2 (ja) | 1999-08-19 | 2006-08-16 | 富士通株式会社 | 半導体集積回路 |

| JP2002064371A (ja) | 2000-08-14 | 2002-02-28 | Nec Corp | 位相周波数比較器および位相周波数比較器の初期化方法 |

| US6504408B1 (en) * | 2001-07-09 | 2003-01-07 | Broadcom Corporation | Method and apparatus to ensure DLL locking at minimum delay |

| US6628154B2 (en) * | 2001-07-31 | 2003-09-30 | Cypress Semiconductor Corp. | Digitally controlled analog delay locked loop (DLL) |

| US6683478B2 (en) | 2001-11-13 | 2004-01-27 | Samsung Electronics Co., Ltd. | Apparatus for ensuring correct start-up and phase locking of delay locked loop |

| TW558872B (en) * | 2002-05-21 | 2003-10-21 | Via Tech Inc | Delay-locked loop device and method for generating clock signal |

| US7477716B2 (en) | 2003-06-25 | 2009-01-13 | Mosaid Technologies, Inc. | Start up circuit for delay locked loop |

| US6867627B1 (en) * | 2003-09-16 | 2005-03-15 | Integrated Device Technology, Inc. | Delay-locked loop (DLL) integrated circuits having high bandwidth and reliable locking characteristics |

| US7002384B1 (en) * | 2004-01-16 | 2006-02-21 | Altera Corporation | Loop circuitry with low-pass noise filter |

| KR100605588B1 (ko) | 2004-03-05 | 2006-07-28 | 주식회사 하이닉스반도체 | 반도체 기억 소자에서의 지연 고정 루프 및 그의 클럭록킹 방법 |

| JP3993860B2 (ja) | 2004-04-19 | 2007-10-17 | 富士通株式会社 | Dll回路 |

| KR100537202B1 (ko) * | 2004-05-06 | 2005-12-16 | 주식회사 하이닉스반도체 | 지연고정루프의 지연고정상태 정보의 이용이 가능한반도체 소자 |

| US7355464B2 (en) * | 2005-05-09 | 2008-04-08 | Micron Technology, Inc. | Apparatus and method for controlling a delay- or phase-locked loop as a function of loop frequency |

-

2006

- 2006-03-13 JP JP2006067243A patent/JP5134779B2/ja not_active Expired - Fee Related

- 2006-12-05 TW TW095145171A patent/TWI399038B/zh not_active IP Right Cessation

- 2006-12-30 CN CN2006101566680A patent/CN101039108B/zh not_active Expired - Fee Related

-

2007

- 2007-01-03 US US11/648,652 patent/US7482850B2/en not_active Expired - Fee Related

- 2007-01-09 KR KR1020070002478A patent/KR20070093322A/ko not_active Application Discontinuation

- 2007-01-10 EP EP07000456.9A patent/EP1835623B1/en active Active

-

2009

- 2009-01-15 US US12/354,391 patent/US7675334B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| US20070210842A1 (en) | 2007-09-13 |

| JP2007243877A (ja) | 2007-09-20 |

| US7675334B2 (en) | 2010-03-09 |

| EP1835623A1 (en) | 2007-09-19 |

| EP1835623B1 (en) | 2013-08-14 |

| US20090134924A1 (en) | 2009-05-28 |

| TWI399038B (zh) | 2013-06-11 |

| US7482850B2 (en) | 2009-01-27 |

| KR20070093322A (ko) | 2007-09-18 |

| CN101039108B (zh) | 2010-09-08 |

| TW200737726A (en) | 2007-10-01 |

| CN101039108A (zh) | 2007-09-19 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5134779B2 (ja) | 遅延同期回路 | |

| US8542044B2 (en) | Semiconductor integrated circuit and method for driving the same | |

| JP5149076B2 (ja) | 遅延固定ループ | |

| US7368966B2 (en) | Clock generator and clock duty cycle correction method | |

| JP4868353B2 (ja) | 遅延固定ループ | |

| US7633324B2 (en) | Data output strobe signal generating circuit and semiconductor memory apparatus having the same | |

| US6593786B2 (en) | Register controlled DLL reducing current consumption | |

| US7605623B2 (en) | Semiconductor memory apparatus with a delay locked loop circuit | |

| TW201007424A (en) | Apparatus and method for multi-phase clock generation | |

| TWI417879B (zh) | 半導體裝置之延遲鎖定迴路 | |

| US8144530B2 (en) | Semiconductor memory device and method for generating output enable signal | |

| US8164370B2 (en) | Clock control circuit and semiconductor device including the same | |

| JP2008219866A (ja) | 半導体メモリ装置及びその駆動方法 | |

| US8482331B2 (en) | Open loop type delay locked loop and method for operating the same | |

| JP2004325410A (ja) | 入出力回路 | |

| US8638137B2 (en) | Delay locked loop | |

| JP4583088B2 (ja) | ストローブ信号遅延装置及び同装置を備える半導体装置 | |

| KR20210029400A (ko) | 지연 라인, 지연 고정 루프 회로 및 이를 이용하는 반도체 장치 | |

| TWI407437B (zh) | 半導體記憶體裝置與驅動半導體記憶體裝置之方法 | |

| KR100911191B1 (ko) | 주파수 조정 장치 및 이를 포함하는 dll 회로 | |

| KR100685613B1 (ko) | 고속 동작을 위한 dll 회로 | |

| KR20090121469A (ko) | 반도체 메모리 장치 | |

| Jaiswal et al. | Adaptive Low-Power Synchronization Technique for Multiple Source-Synchronous Clocks in High-Speed Communication Systems | |

| KR20210029402A (ko) | 지연 라인, 지연 고정 루프 회로 및 이를 이용하는 반도체 장치 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20081002 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090122 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20100528 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20100617 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100706 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100903 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20110222 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120919 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20121112 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20151116 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| LAPS | Cancellation because of no payment of annual fees |