JP5111867B2 - 表示装置 - Google Patents

表示装置 Download PDFInfo

- Publication number

- JP5111867B2 JP5111867B2 JP2007006570A JP2007006570A JP5111867B2 JP 5111867 B2 JP5111867 B2 JP 5111867B2 JP 2007006570 A JP2007006570 A JP 2007006570A JP 2007006570 A JP2007006570 A JP 2007006570A JP 5111867 B2 JP5111867 B2 JP 5111867B2

- Authority

- JP

- Japan

- Prior art keywords

- signal line

- oxide layer

- transparent oxide

- region

- pixel

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/01—Manufacture or treatment

- H10D86/021—Manufacture or treatment of multiple TFTs

- H10D86/0221—Manufacture or treatment of multiple TFTs comprising manufacture, treatment or patterning of TFT semiconductor bodies

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/1333—Constructional arrangements; Manufacturing methods

- G02F1/1343—Electrodes

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/67—Thin-film transistors [TFT]

- H10D30/674—Thin-film transistors [TFT] characterised by the active materials

- H10D30/6755—Oxide semiconductors, e.g. zinc oxide, copper aluminium oxide or cadmium stannate

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/40—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs

- H10D86/421—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs having a particular composition, shape or crystalline structure of the active layer

- H10D86/423—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs having a particular composition, shape or crystalline structure of the active layer comprising semiconductor materials not belonging to the Group IV, e.g. InGaZnO

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/40—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs

- H10D86/441—Interconnections, e.g. scanning lines

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/40—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs

- H10D86/60—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs wherein the TFTs are in active matrices

Landscapes

- Physics & Mathematics (AREA)

- Nonlinear Science (AREA)

- Optics & Photonics (AREA)

- Crystallography & Structural Chemistry (AREA)

- Chemical & Material Sciences (AREA)

- General Physics & Mathematics (AREA)

- Mathematical Physics (AREA)

- Liquid Crystal (AREA)

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Thin Film Transistor (AREA)

- Electroluminescent Light Sources (AREA)

- Devices For Indicating Variable Information By Combining Individual Elements (AREA)

Description

ソース信号線と、薄膜トランジスタのソース領域部と、チャネル領域部(ゲート電極の直下の部分)と、ドレイン領域部と、画素電極とを、第1透明酸化物層で形成される同一の層に一体的に形成し、

前記チャネル領域部はキャリア濃度が低くシート抵抗が高い膜(半導体層)として形成してなり、

前記第1透明酸化物層の上に、絶縁膜を形成し、

前記絶縁膜の上に、ゲート信号線および該ゲート信号線に接続される薄膜トランジスタのゲート電極を第2透明酸化物層で形成される同一の層に一体的に形成し、

前記第2透明酸化物層にレーザ光を照射して前記ゲート信号線および薄膜トランジスタのゲート電極を結晶改質してキャリア濃度が高くシート抵抗が低い膜(導体層)として形成してなることを特徴とする。

前記絶縁膜上に第1絶縁膜を介して該画素電極に重畳して配置されるとともに、並設された複数の電極からなる櫛歯状電極として構成され該画素電極との間で電界を生じさせる対向電極を有し、

前記対向電極の各電極の中途部において該対向電極と一体となって前記ゲート信号線とほぼ平行に走行するコモン信号線を形成し、

前記コモン信号線を通して映像信号に対して基準となる基準電圧を前記櫛歯状電極に印加するようにしたことを特徴とする。

前記チャネル領域部はキャリア濃度が低くシート抵抗が高い膜(半導体層)として形成してなり、

前記第1透明酸化物層の上に、絶縁膜を形成し、

前記絶縁膜の上に、ゲート信号線および該ゲート信号線に接続される薄膜トランジスタのゲート電極を第2透明酸化物層で形成される同一の層に一体的に形成し、

前記第2透明酸化物層にレーザ光を照射して前記ゲート信号線および薄膜トランジスタのゲート電極を結晶改質してキャリア濃度が高くシート抵抗が低い膜(導体層)として形成してなり、

前記金属層はソース信号線を構成し、

前記第1透明酸化物層は少なくとも前記ゲート電極の直下のチャネル領域部を除いた他の領域が導電体化され、該導電体化された部分で前記ソース信号線と接続された薄膜トランジスタのソース領域部、画素電極、該画素電極に接続される前記薄膜トランジスタのドレイン領域部を構成していることを特徴とする。

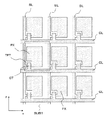

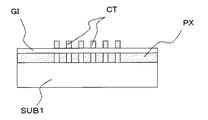

図1は、液晶表示装置の液晶を介して対向配置される各基板のうち一方の基板SUB1の液晶側の面の液晶表示領域に形成される回路の一実施例を示す構成図である。

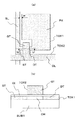

図8(a)に示すように、たとえばガラスからなる基板SUB1を用意し、この基板SUB1の表面(液晶側の面)にたとえばZnO等からなる高抵抗の第1透明酸化物層TOX1およびたとえばSiO2等からなる第1絶縁膜GI1を順次成膜する。ここで、前記第1絶縁膜GI1は薄膜トランジスタTFTの形成領域においてそのゲート絶縁膜として機能するようになっている。

図8(b)に示すように、前記第1絶縁膜GI1の上面の全域に第1フォトレジスト膜PRT1を形成し、この第1フォトレジスト膜PRT1を所定のパターンに形成する。

図8(c)に示すように、前記第1フォトレジスト膜PRT1の表面を底面方向に適当量の除去を行うことによって、該第1フォトレジスト膜PRT1を、ソース信号線SL、このソース信号線SLと接続される薄膜トランジスタTFT(そのチャネル領域部およびLDD領域部の部分を除く)、この薄膜トランジスタTFTと接続される画素電極PXの各形成領域において完全に除去し、前記薄膜トランジスタTFTのチャネル領域部およびLDD領域部の形成領域にのみ残存させるようにする。

図8(d)に示すように、前記第1フォトレジスト膜PRT1を全て除去する。

図8(e)に示すように、たとえばSiO2からなる第2絶縁膜GI2、たとえばITO(Indium Tin Oxide)からなる第2透明酸化物層TOX2を順次成膜する。ここで、前記第2絶縁膜GI2は、ソース信号線SLに対する後述のゲート信号線GLの層間絶縁膜として機能するようになる。

図8(f)に示すように、前記第2透明酸化物層TOX2の上面に第2フォトレジスト膜PRT2を形成し、この第2フォトレジスト膜PRT2を所定のパターンに形成する。すなわち、ゲート信号線GL、このゲート信号線GLと接続される前記薄膜トランジスタTFTのゲート電極GTの各形成領域に前記第2フォトレジスト膜を残存させる。ここで、ゲート電極GTの形成領域は、薄膜トランジスタTFTのチャネル領域部の直上の部分であり、該チャネル領域の両脇のLDD領域は除かれる。

図8(g)に示すように、前記第2フォトレジスト膜PRT2を全て除去する。その後は、基板SUB1の表面に図示せぬ配向膜を形成することによって完了する。

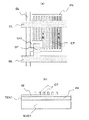

図9(a)に示すように、基板SUB1を用意し、この基板SUB1の表面(液晶側の面)にたとえばZnO等からなる高抵抗の第1透明酸化物層TOX1およびたとえばSiO2等からなる第1絶縁膜GI1を順次成膜する。

図9(b)に示すように、前記第1絶縁膜GI1の上面の全域に第1フォトレジスト膜PRT1を形成し、この第1フォトレジスト膜PRT1を所定のパターンに形成する。

図9(c)に示すように、前記第1フォトレジスト膜PRT1の表面を底面方向に適当量の除去を行うことによって、該第1フォトレジスト膜PRT1を、ソース信号線SLの形成領域において完全に除去し、前記薄膜トランジスタTFTのチャネル領域部、このチャネル領域部に隣接しソース信号線SL側のLDD領域部、および画素電極PXの各形成領域にのみ残存させるようにする。

図9(d)に示すように、前記第1フォトレジスト膜PRT1を全て除去する。

図9(e)に示すように、たとえばSiO2からなる第2絶縁膜GI2、たとえばITO(Indium Tin Oxide)からなる第2透明酸化物層TOX2を順次成膜する。

図9(f)に示すように、前記第2透明酸化物層TOX2の上面に第2フォトレジスト膜PRT2を形成し、この第2フォトレジスト膜PRT2を所定のパターンに形成する。すなわち、ゲート信号線GL、このゲート信号線GLと接続される前記薄膜トランジスタTFTのゲート電極GTの各形成領域に前記第2フォトレジスト膜PRT2を残存させる。ここで、ゲート電極GTの形成領域は、薄膜トランジスタTFTのチャネル領域部の直上の部分であり、該チャネル領域部に隣接するソース信号線SL側のLDD領域LDは除かれる。

図10は、本発明による表示装置の画素の構成の他の実施例を示す平面図で、図2(a)に対応した図となっている。

図11(a)は、本発明による表示装置の画素の構成の他の実施例を示す平面図で、図7、10(a)と対応した図である。また、図11(b)は図11(a)のb−b線における断面図である。

図14(a)は、本発明による表示装置の画素の構成の他の実施例を示す平面図で、図11(a)と対応した図である。また、図14(b)は図14(a)のb−b線における断面図である。

図15(a)に示すように、基板SUB1を用意し、この基板SUB1の表面にたとえばZnO等からなる高抵抗の第1透明酸化物層TOX1およびたとえばSiO2等からなる第1絶縁膜GI1を順次成膜する。

図15(b)に示すように、前記第1絶縁膜GI1の上面の全域に第1フォトレジスト膜PRT1を形成し、この第1フォトレジスト膜PRT1を所定のパターンに形成する。

図15(c)に示すように、前記第1フォトレジスト膜PRT1の表面を底面方向に適当量の除去を行うことによって、該第1フォトレジスト膜PRT1を、薄膜トランジスタTFTのチャネル領域部およびその両脇のLDD領域部の形成領域にのみ残存させるようにする。

図15(d)に示すように、前記第1フォトレジスト膜PRT1を全て除去する。

図15(e)に示すように、基板SUB1の表面に第2フォトレジスト膜PRT2を形成し、該第2フォトレジスト膜PRT2をパターン化することによって、ソース信号線SLを形成する部分において除去され他の部分において残存される第2フォトレジスト膜PRT2を形成する。

図15(f)に示すように、前記第2フォトレジスト膜PRT2を除去し、たとえばSiO2からなる第2絶縁膜GI2およびたとえばITO膜からなる第2透明酸化物層TOX2を順次形成する。

図15(g)に示すように、基板SUB1の表面に第3フォトレジスト膜PRT3を形成し、該第3フォトレジスト膜PRT3をパターン化することによって、ゲート信号線GLおよび薄膜トランジスタTFTのゲート電極GTを形成する部分において残存される第3フォトレジスト膜PRT3を形成する。

図15(h)に示すように、前記第3フォトレジスト膜PRT3を除去する。

図16(a)に示すように、基板SUB1を用意し、この基板SUB1の表面にたとえばZnO等からなる高抵抗の第1透明酸化物層TOX1およびたとえばSiO2等からなる第1絶縁膜GI1を順次成膜する。

図16(b)に示すように、前記第1絶縁膜GI1の上面の全域に第1フォトレジスト膜PRT1を形成し、この第1フォトレジスト膜PRT1を所定のパターンに形成する。

図16(c)に示すように、前記第1フォトレジスト膜PRT1の表面を底面方向に適当量の除去を行うことによって、該第1フォトレジスト膜PRT1を、薄膜トランジスタTFTのチャネル領域部およびその両脇のLDD領域部の形成領域にのみ残存させるようにする。

図16(d)に示すように、基板SUB1の表面の全域に金属を蒸着し、金属層MTを形成する。

図16(e)に示すように、基板SUB1の表面の全域に第2フォトレジスト膜PRT2を形成し、この第2フォトレジスト膜PRT2をパターン化して、ソース信号線SLの形成領域に第2フォトレジスト膜PRT2を残存させる。

図16(f)に示すように、たとえばSiO2からなる第2絶縁膜GI2およびたとえばITO膜からなる第2透明酸化物層TOX2を順次形成する。

図16(g)に示すように、基板SUB1の表面に第3フォトレジスト膜PRT3を形成し、該第3フォトレジスト膜PRT3をパターン化することによって、ゲート信号線GLおよび薄膜トランジスタTFTのゲート電極GTを形成する部分において残存される第3フォトレジスト膜PRT3を形成する。

図16(h)に示すように、前記第3フォトレジスト膜PRT3を除去する。

図17(a)は、本発明による表示装置の画素の構成の他の実施例を示す平面図である。また、図17(b)は、図17(a)のb−b線における断面図である。

図20(a)は、本発明による表示装置の画素の構成の他の実施例を示す平面図であり、基板SUB1の面に形成する2つの各透明酸化物層のうち上層に形成される第2透明酸化物層TOX2が画素の領域の全域に形成され、その一部にゲート信号線GLおよびゲート電極GTが形成されていることを示した図となっている。また、図20(b)は、図20(a)のb−b線における断面図である。

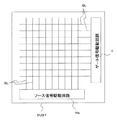

図22は基板SUB1の表面にアレイ状に配置された各画素の一実施例を示した平面図で、図1と対応した図である。

図25(a)に示すように、基板SUB1を用意し、この基板SUB1の表面にたとえば不純物がドープされたZnOからなる第1透明酸化物層TOX1を形成する。

図25(b)に示すように、基板SUB1の表面に第1フォトレジスト膜PRT1を形成し、これをパターン化することにより、ソース信号線SL、このソース信号線SLの延在部となる薄膜トランジスタTFTのソース領域部ST、画素電極PX、この画素電極PXの延在部となる薄膜トランジスタTFTのドレイン領域部DTの形成領域における第1フォトレジスト膜PRT1を残存させる。

図25(c)に示すように、前記第1フォトレジスト膜PRT1を除去する。

図25(d)に示すように、基板SUB1の表面に第2フォトレジスト膜PRT2を形成し、これをパターン化することにより、前記ソース領域部STとドレイン領域部DTの離間部、ソース領域部STの前記離間部側の先端部、ドレイン領域部DTの前記離間部側の先端部を露出させるように穴開けがなされた第2フォトレジスト膜PRT2を残存させる。

図25(e)に示すように、前記第2フォトレジスト膜PRT2を除去することにより、ソース領域部STとドレイン領域部DTの離間部において、一端が前記ソース領域部STと重畳し他端が前記ドレイン領域部DTと重畳して配置される第2透明酸化物層TOX2を選択的に形成する。いわゆるリフトオフ法による形成である。この第2透明酸化物層TOX2は薄膜トランジスタTFTの半導体層SCとして構成される。

図25(f)に示すように、基板SUB1の表面に、たとえばSiO2膜からなる絶縁膜GI、たとえばITO膜からなる第3透明酸化物層TOX3を順次形成する。

図25(g)に示すように、基板SUB1の表面に第3フォトレジスト膜PRT3を形成し、これをパターン化することにより、ゲート電極GTおよびこのゲート電極GTに接続されるゲート信号線GLの形成領域における第3フォトレジスト膜PRT3を残存させる。

図25(h)に示すように、第3フォトレジスト膜PRT3を除去する。

図27(a)に示すように、基板SUB1を用意し、この基板SUB1の表面にたとえば不純物がドープされたZnOからなる第1透明酸化物層TOX1を形成する。

図27(b)に示すように、基板SUB1の表面に第1フォトレジスト膜PRT1を形成し、これをパターン化することにより、薄膜トランジスタTFTの半導体層SCが形成される領域において孔開けされた第1フォトレジスト膜PRT1を残存させる。

図27(c)に示すように、前記第1フォトレジスト膜PRT1を除去する。

図27(d)に示すように、基板SUB1の表面に、真性あるいは低濃度の不純物がドープされたたとえばZnOからなる第2透明酸化物層TOX2を形成する。

図27(e)に示すように、基板SUB1の表面に第2フォトレジスト膜PRT2を形成し、これをパターン化することにより、ソース信号線SL、薄膜トランジスタTFTのソース領域部ST、チャネル領域部CH、ドレイン領域部DT、および画素電極PXの形成領域における第2フォトレジスト膜PRT2を残存させる。

図27(f)に示すように、前記第2フォトレジスト膜PRT2を除去する。これにより、基板SUB1の表面には、ソース信号線SL、このソース信号線SLの延在部として構成される薄膜トランジスタTFTのソース領域部ST、画素電極PX、この画素電極PXの延在部として構成される薄膜トランジスタTFTのドレイン領域部DTを構成する第1透明酸化物層TOX1、および薄膜トランジスタTFTの半導体層SCの形成領域(前記第1透明酸化物層TOX1の開口が設けられた部分)、前記第1透明酸化物層TOX1の上方の領域に第2透明酸化物層TOX2が形成されることになる。

図27(g)に示すように、基板SUB1の表面にたとえばSiO2膜からなる絶縁膜GI、たとえばITO膜からなる第3透明酸化物層TOX3を順次形成する。

図27(h)に示すように、基板SUB1の表面に第3フォトレジスト膜PRT3を形成し、これをパターン化することにより、ゲート電極GTおよびこのゲート電極GTに接続されるゲート信号線GLの形成領域における第3フォトレジスト膜PRT3を残存させる。

図27(i)に示すように、第3フォトレジスト膜PRT3を除去する。

図28(a)に示すように、基板SUB1を用意し、この基板SUB1の表面に、たとえばZnOからなる第1透明酸化物層TOX1、さらにたとえば不純物がドープされたZnOからなる第2透明酸化物層TOX2を順次形成する。

図28(b)に示すように、基板SUB1の表面に第1フォトレジスト膜PRT1を形成し、この第1フォトレジスト膜PRT1をパターン化することにより、ソース信号線SL、このソース信号線SLの延在部として構成される薄膜トランジスタTFTのソース領域部ST、薄膜トランジスタTFTのチャネル領域部CH、画素電極PX、この画素電極PXの延在部として構成される薄膜トランジスタTFTのドレイン領域部DTの形成領域に残存させ、かつ、薄膜トランジスタTFTのチャネル領域部CHの形成領域において他の部分よりも厚さの小さい第1フォトレジスト膜PRT1を形成する。

図28(c)に示すように、前記第1フォトレジスト膜PRT1の表面を底面方向に適当量の除去を行うことによって、薄膜トランジスタTFTのチャネル領域部の形成領域における第2透明酸化物層TOX2の表面を露呈させ、その他の部分において該第1フォトレジスト膜PRT1を残存させる。

図28(d)に示すように、前記第1フォトレジスト膜PRT1を除去する。そして、その後の工程は、図27(g)ないし(i)を経て完了する。

図30(a)に示すように、基板SUB1を用意し、この基板SUB1の表面にたとえば不純物がドープされたZnOからなる第1透明酸化物層TOX1を形成する。

図30(b)に示すように、基板SUB1の表面に第1フォトレジスト膜PRT1を形成し、これをパターン化することにより、ソース信号線SL、ソース信号線SLの延在部として構成される薄膜トランジスタTFTのソース領域部ST、画素電極PX、画素電極PXの延在部として構成される薄膜トランジスタTFTのドレイン領域部DTの形成領域に第1フォトレジスト膜PRT1を残存させる。

図30(c)に示すように、第1フォトレジスト膜PRT1を除去する。

図30(d)に示すように、基板SUB1の表面に、真性あるいは低濃度の不純物がドープされたたとえばZnOからなる半導体層SC、たとえばSiO2膜からなる絶縁膜GIを順次形成する。

図30(e)に示すように、基板SUB1の表面に第2フォトレジスト膜PRT2を形成し、これをパターン化することにより、ゲート電極GTおよびこのゲート電極GTに接続されるゲート信号線GLの形成領域における第2フォトレジスト膜PRT2を残存させる。

図30(f)に示すように、第2フォトレジスト膜PRT2を除去する。

図31(a)は、本発明による表示装置の画素の構成の他の実施例を示す平面図で、図23(a)と対応した図となっている。また、図31(b)は図31(a)のb−b線における断面図である。

図34(a)は、本発明による表示装置の画素の構成の他の実施例を示す平面図であり、図23(a)と対応した図となっている。また、図34(b)は図34(a)のb−b線における断面図である。

図36は、基板SUB1に上述した構成の画素(図示せず)が形成されているとともに、各ゲート信号線GLへの走査信号の供給は該基板SUB1に搭載されるゲート信号駆動回路Vによってなされ、各ソース信号線SLへの映像信号の供給は該基板SUB1に搭載されるソース信号駆動回路Heによってなされることを示している。

Claims (8)

- 基板上の画素領域に、

ソース信号線と、薄膜トランジスタのソース領域部と、チャネル領域部(ゲート電極の直下の部分)と、ドレイン領域部と、画素電極とを、第1透明酸化物層で形成される同一の層に一体的に形成し、

前記チャネル領域部はキャリア濃度が低くシート抵抗が高い膜(半導体層)として形成してなり、

前記第1透明酸化物層の上に、絶縁膜を形成し、

前記絶縁膜の上に、ゲート信号線および該ゲート信号線に接続される薄膜トランジスタのゲート電極を第2透明酸化物層で形成される同一の層に一体的に形成し、

前記第2透明酸化物層にレーザ光を照射して前記ゲート信号線および薄膜トランジスタのゲート電極を結晶改質してキャリア濃度が高くシート抵抗が低い膜(導体層)として形成してなる

ことを特徴とする表示装置。 - 前記第1透明酸化物層は、ZnOによって構成したものであることを特徴とする請求項1に記載の表示装置。

- 前記基板の液晶側の画素領域には、

前記絶縁膜上に第1絶縁膜を介して該画素電極に重畳して配置されるとともに、並設された複数の電極からなる櫛歯状電極として構成され該画素電極との間で電界を生じさせる対向電極を有し、

前記対向電極の各電極の中途部において該対向電極と一体となって前記ゲート信号線とほぼ平行に走行するコモン信号線を形成し、

前記コモン信号線を通して映像信号に対して基準となる基準電圧を前記櫛歯状電極に印加するようにしたことを特徴とする請求項1に記載の表示装置。 - 前記絶縁膜は画素領域の全域に形成されていることを特徴とする請求項1に記載の表示装置。

- 前記導体層は、画素領域の全域に形成された第2透明酸化物層を選択的に導電体化させて形成されていることを特徴とする請求項1に記載の表示装置。

- 前記第1透明酸化物層に、前記ゲート電極の直下のチャネル領域部とソース領域部およびドレイン領域部のそれぞれの間に、前記ソース領域部およびドレイン領域部よりもキャリア濃度の低いLDD領域部(電界緩和領域)が形成されていることを特徴する請求項1に記載の表示装置。

- 前記第1透明酸化物層のソース信号線を構成する部分の上層あるいは下層に金属層が形成されていることを特徴とする請求項1に記載の表示装置。

- 基板上の画素領域に、

ソース信号線と、薄膜トランジスタのソース領域部と、チャネル領域部(ゲート電極の直下の部分)と、ドレイン領域部と、画素電極とを同一の層で一体的に形成する第1透明酸化物層および金属層がそのいずれかを上層として形成し、

前記チャネル領域部はキャリア濃度が低くシート抵抗が高い膜(半導体層)として形成してなり、

前記第1透明酸化物層の上に、絶縁膜を形成し、

前記絶縁膜の上に、ゲート信号線および該ゲート信号線に接続される薄膜トランジスタのゲート電極を第2透明酸化物層で形成される同一の層に一体的に形成し、

前記第2透明酸化物層にレーザ光を照射して前記ゲート信号線および薄膜トランジスタのゲート電極を結晶改質してキャリア濃度が高くシート抵抗が低い膜(導体層)として形成してなり、

前記金属層はソース信号線を構成し、

前記第1透明酸化物層は少なくとも前記ゲート電極の直下のチャネル領域部を除いた他の領域が導電体化され、該導電体化された部分で前記ソース信号線と接続された薄膜トランジスタのソース領域部、画素電極、該画素電極に接続される前記薄膜トランジスタのドレイン領域部を構成している

ことを特徴とする表示装置。

Priority Applications (10)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007006570A JP5111867B2 (ja) | 2007-01-16 | 2007-01-16 | 表示装置 |

| TW096142729A TW200839401A (en) | 2007-01-16 | 2007-11-12 | Display device |

| KR1020070120116A KR101454919B1 (ko) | 2007-01-16 | 2007-11-23 | 표시장치 |

| US12/003,462 US8242505B2 (en) | 2007-01-16 | 2007-12-26 | Display device |

| CN2007103004216A CN101226311B (zh) | 2007-01-16 | 2007-12-27 | 显示装置 |

| EP07025121A EP1947695B1 (en) | 2007-01-16 | 2007-12-27 | Display device |

| AT07025121T ATE518253T1 (de) | 2007-01-16 | 2007-12-27 | Anzeigevorrichtung |

| US13/537,462 US8629451B2 (en) | 2007-01-16 | 2012-06-29 | Display device |

| US14/106,287 US8802511B2 (en) | 2007-01-16 | 2013-12-13 | Display device |

| US14/278,358 US10068932B2 (en) | 2007-01-16 | 2014-05-15 | Display device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007006570A JP5111867B2 (ja) | 2007-01-16 | 2007-01-16 | 表示装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2008175842A JP2008175842A (ja) | 2008-07-31 |

| JP5111867B2 true JP5111867B2 (ja) | 2013-01-09 |

Family

ID=39301275

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2007006570A Active JP5111867B2 (ja) | 2007-01-16 | 2007-01-16 | 表示装置 |

Country Status (7)

| Country | Link |

|---|---|

| US (4) | US8242505B2 (ja) |

| EP (1) | EP1947695B1 (ja) |

| JP (1) | JP5111867B2 (ja) |

| KR (1) | KR101454919B1 (ja) |

| CN (1) | CN101226311B (ja) |

| AT (1) | ATE518253T1 (ja) |

| TW (1) | TW200839401A (ja) |

Families Citing this family (35)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5111867B2 (ja) * | 2007-01-16 | 2013-01-09 | 株式会社ジャパンディスプレイイースト | 表示装置 |

| JP2010108957A (ja) * | 2008-10-28 | 2010-05-13 | Hitachi Displays Ltd | 表示装置およびその製造方法 |

| KR101510900B1 (ko) * | 2008-12-04 | 2015-04-10 | 엘지디스플레이 주식회사 | 산화물 반도체층을 이용한 액정표시장치용 어레이 기판의 제조방법 |

| JP4844627B2 (ja) * | 2008-12-24 | 2011-12-28 | ソニー株式会社 | 薄膜トランジスタの製造方法および表示装置の製造方法 |

| US8174021B2 (en) * | 2009-02-06 | 2012-05-08 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and method of manufacturing the semiconductor device |

| KR101746198B1 (ko) * | 2009-09-04 | 2017-06-12 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 표시장치 및 전자기기 |

| CN102763214B (zh) | 2010-02-19 | 2015-02-18 | 株式会社半导体能源研究所 | 半导体器件 |

| CN102148196B (zh) * | 2010-04-26 | 2013-07-10 | 北京京东方光电科技有限公司 | Tft-lcd阵列基板及其制造方法 |

| WO2011142371A1 (en) | 2010-05-14 | 2011-11-17 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| US9035299B2 (en) | 2010-12-01 | 2015-05-19 | Sharp Kabushiki Kaisha | Semiconductor device and method for producing same |

| JP5743064B2 (ja) * | 2011-02-17 | 2015-07-01 | 株式会社Joled | 薄膜トランジスタおよびその製造方法、並びに表示装置 |

| FR2981090B1 (fr) * | 2011-10-10 | 2014-03-14 | Commissariat Energie Atomique | Procede de preparation d'oxyde de zinc zno de type p ou de znmgo de type p. |

| CN102629585B (zh) * | 2011-11-17 | 2014-07-23 | 京东方科技集团股份有限公司 | 一种显示装置、薄膜晶体管、阵列基板及其制造方法 |

| US9099560B2 (en) * | 2012-01-20 | 2015-08-04 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and manufacturing method thereof |

| JP6148024B2 (ja) * | 2012-02-09 | 2017-06-14 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| CN102629590B (zh) * | 2012-02-23 | 2014-10-22 | 京东方科技集团股份有限公司 | 一种薄膜晶体管阵列基板及其制作方法 |

| TWI477867B (zh) * | 2012-07-16 | 2015-03-21 | E Ink Holdings Inc | 畫素結構及其製造方法 |

| KR102101863B1 (ko) * | 2013-01-07 | 2020-04-21 | 삼성디스플레이 주식회사 | 박막 트랜지스터, 이의 제조 방법 및 이를 구비하는 표시 장치 |

| JP2014132621A (ja) * | 2013-01-07 | 2014-07-17 | Nippon Hoso Kyokai <Nhk> | 薄膜デバイスの製造方法 |

| KR102040812B1 (ko) * | 2013-02-12 | 2019-11-06 | 삼성디스플레이 주식회사 | 액정 표시 장치 |

| KR102054000B1 (ko) * | 2013-09-11 | 2019-12-10 | 삼성디스플레이 주식회사 | 박막 트랜지스터 표시판, 액정 표시 장치 및 박막 트랜지스터 표시판의 제조방법 |

| KR102345617B1 (ko) * | 2014-01-13 | 2022-01-03 | 삼성디스플레이 주식회사 | 표시패널 |

| CN103746014B (zh) * | 2014-01-20 | 2016-03-30 | 瑞德兴阳新能源技术有限公司 | 一种ito栅线太阳能电池及其制备方法 |

| CN103746013B (zh) * | 2014-01-20 | 2016-03-30 | 瑞德兴阳新能源技术有限公司 | 一种石墨烯太阳能电池及其制备方法 |

| US9853070B2 (en) * | 2014-12-09 | 2017-12-26 | Sharp Kabushiki Kaisha | Method of manufacturing display panel substrate |

| US9837547B2 (en) * | 2015-05-22 | 2017-12-05 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device comprising oxide conductor and display device including the semiconductor device |

| WO2016204227A1 (ja) | 2015-06-17 | 2016-12-22 | 富士電機株式会社 | 半導体装置および半導体装置の製造方法 |

| EP3136446A1 (en) * | 2015-08-28 | 2017-03-01 | Nederlandse Organisatie voor toegepast- natuurwetenschappelijk onderzoek TNO | Tft device and manufacturing method |

| JP2017075982A (ja) * | 2015-10-13 | 2017-04-20 | 株式会社ジャパンディスプレイ | 表示装置 |

| WO2018100466A1 (en) * | 2016-11-30 | 2018-06-07 | Semiconductor Energy Laboratory Co., Ltd. | Display device, display module, and electronic device |

| CN108039353B (zh) * | 2017-12-26 | 2020-07-21 | 深圳市华星光电技术有限公司 | 阵列基板及其制备方法、显示装置 |

| CN110224003B (zh) * | 2018-03-01 | 2023-06-09 | 天马日本株式会社 | 显示装置 |

| US20200035717A1 (en) | 2018-07-26 | 2020-01-30 | Sharp Kabushiki Kaisha | Thin film transistor substrate and method of producing thin film transistor substrate |

| JP6753986B2 (ja) * | 2019-07-04 | 2020-09-09 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| CN113596013B (zh) * | 2021-07-26 | 2024-02-09 | 深圳Tcl新技术有限公司 | 设备控制权限的设置方法、装置、计算机设备和存储介质 |

Family Cites Families (18)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS62145247A (ja) | 1985-12-19 | 1987-06-29 | Nec Corp | フオトマスク |

| JP2794678B2 (ja) * | 1991-08-26 | 1998-09-10 | 株式会社 半導体エネルギー研究所 | 絶縁ゲイト型半導体装置およびその作製方法 |

| JP3259119B2 (ja) | 1994-06-28 | 2002-02-25 | 富士通株式会社 | 配線パターン基板及び薄膜トランジスタマトリクス基板とその製造方法 |

| JPH09269503A (ja) * | 1996-03-29 | 1997-10-14 | Toshiba Corp | 液晶表示装置 |

| JPH09318975A (ja) * | 1996-05-30 | 1997-12-12 | Nec Corp | 薄膜電界効果型トランジスタ素子アレイおよびその製造 方法 |

| JP2001076885A (ja) * | 1999-09-02 | 2001-03-23 | Auto Network Gijutsu Kenkyusho:Kk | 有機el表示デバイスにおける透明配線の抵抗値調節方法 |

| JP3617458B2 (ja) | 2000-02-18 | 2005-02-02 | セイコーエプソン株式会社 | 表示装置用基板、液晶装置及び電子機器 |

| KR20020038482A (ko) * | 2000-11-15 | 2002-05-23 | 모리시타 요이찌 | 박막 트랜지스터 어레이, 그 제조방법 및 그것을 이용한표시패널 |

| JP2003050405A (ja) * | 2000-11-15 | 2003-02-21 | Matsushita Electric Ind Co Ltd | 薄膜トランジスタアレイ、その製造方法およびそれを用いた表示パネル |

| JP2002319682A (ja) * | 2002-01-04 | 2002-10-31 | Japan Science & Technology Corp | トランジスタ及び半導体装置 |

| JP4141309B2 (ja) * | 2003-04-15 | 2008-08-27 | シャープ株式会社 | 半導体装置およびその製造方法 |

| US6960497B2 (en) | 2003-06-25 | 2005-11-01 | Chunghwa Picture Tubes, Ltd. | Method for forming pi-type assistant electrode |

| JP4404881B2 (ja) * | 2006-08-09 | 2010-01-27 | 日本電気株式会社 | 薄膜トランジスタアレイ、その製造方法及び液晶表示装置 |

| TWI374544B (en) * | 2006-11-13 | 2012-10-11 | Au Optronics Corp | Thin film transistor array substrates and fbricating method thereof |

| JP5111867B2 (ja) * | 2007-01-16 | 2013-01-09 | 株式会社ジャパンディスプレイイースト | 表示装置 |

| CN104576748B (zh) * | 2009-06-30 | 2019-03-15 | 株式会社半导体能源研究所 | 半导体装置的制造方法 |

| KR20180001562A (ko) * | 2010-02-26 | 2018-01-04 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치를 제작하기 위한 방법 |

| DE112011101395B4 (de) * | 2010-04-23 | 2014-10-16 | Semiconductor Energy Laboratory Co., Ltd. | Verfahren zum Herstellen einer Halbleitervorrichtung |

-

2007

- 2007-01-16 JP JP2007006570A patent/JP5111867B2/ja active Active

- 2007-11-12 TW TW096142729A patent/TW200839401A/zh unknown

- 2007-11-23 KR KR1020070120116A patent/KR101454919B1/ko active Active

- 2007-12-26 US US12/003,462 patent/US8242505B2/en active Active

- 2007-12-27 CN CN2007103004216A patent/CN101226311B/zh active Active

- 2007-12-27 AT AT07025121T patent/ATE518253T1/de not_active IP Right Cessation

- 2007-12-27 EP EP07025121A patent/EP1947695B1/en active Active

-

2012

- 2012-06-29 US US13/537,462 patent/US8629451B2/en active Active

-

2013

- 2013-12-13 US US14/106,287 patent/US8802511B2/en active Active

-

2014

- 2014-05-15 US US14/278,358 patent/US10068932B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| EP1947695A3 (en) | 2010-05-19 |

| TW200839401A (en) | 2008-10-01 |

| KR101454919B1 (ko) | 2014-10-27 |

| US20080169469A1 (en) | 2008-07-17 |

| US20140248748A1 (en) | 2014-09-04 |

| EP1947695B1 (en) | 2011-07-27 |

| US20140106490A1 (en) | 2014-04-17 |

| ATE518253T1 (de) | 2011-08-15 |

| CN101226311A (zh) | 2008-07-23 |

| US20120261668A1 (en) | 2012-10-18 |

| CN101226311B (zh) | 2012-12-12 |

| EP1947695A2 (en) | 2008-07-23 |

| KR20080067562A (ko) | 2008-07-21 |

| US8802511B2 (en) | 2014-08-12 |

| US8629451B2 (en) | 2014-01-14 |

| JP2008175842A (ja) | 2008-07-31 |

| US8242505B2 (en) | 2012-08-14 |

| TWI370312B (ja) | 2012-08-11 |

| US10068932B2 (en) | 2018-09-04 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5111867B2 (ja) | 表示装置 | |

| JP5697737B2 (ja) | 薄膜トランジスタアレイ基板及びその製造方法 | |

| KR101138624B1 (ko) | 표시 장치 | |

| JP5323604B2 (ja) | 表示装置及びその製造方法 | |

| JP2009099887A (ja) | 表示装置 | |

| EP3621120B1 (en) | Thin film transistor and preparation method therefor, array substrate and preparation method therefor | |

| CN105470262A (zh) | 薄膜晶体管基板及使用薄膜晶体管基板的显示设备 | |

| JP2005079283A (ja) | 薄膜半導体装置及びその製造方法、電気光学装置、並びに電子機器 | |

| KR101059024B1 (ko) | 표시 장치 | |

| CN102436104B (zh) | 像素结构及像素结构的制造方法 | |

| CN1873989B (zh) | 薄膜晶体管以及制造薄膜晶体管基板的方法 | |

| JP2023081048A (ja) | アクティブマトリクス基板、液晶表示装置およびアクティブマトリクス基板の製造方法 | |

| KR100924493B1 (ko) | 구동회로 일체형 액정표시장치용 어레이기판 제조방법 | |

| CN101925988A (zh) | 半导体装置及其制造方法 | |

| JP2009130016A (ja) | 半導体装置の製造方法及び電子機器 | |

| US20060065894A1 (en) | Thin film transistor array panel and manufacturing method thereof | |

| KR100894594B1 (ko) | 표시장치용 소자기판 및 이의 제조방법 | |

| KR101148526B1 (ko) | 액정표시장치의 박막트랜지스터 제조방법 | |

| KR20060040327A (ko) | 박막 트랜지스터 표시판 및 그 제조 방법 | |

| KR20070045457A (ko) | 영상 표시 장치 및 그 제조 방법 | |

| JP2012151417A (ja) | 薄膜トランジスタ回路基板及びその製造方法 | |

| KR20080025494A (ko) | 박막 트랜지스터 표시판의 제조 방법 | |

| KR20060070366A (ko) | 박막 트랜지스터 및 박막 트랜지스터 표시판의 제조 방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20090623 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20110218 |

|

| RD03 | Notification of appointment of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7423 Effective date: 20110218 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120120 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120124 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120312 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120807 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120904 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20121009 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20121010 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20151019 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5111867 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| S533 | Written request for registration of change of name |

Free format text: JAPANESE INTERMEDIATE CODE: R313533 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313117 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313117 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |