JP4909737B2 - 電荷蓄積場所を有するメモリ - Google Patents

電荷蓄積場所を有するメモリ Download PDFInfo

- Publication number

- JP4909737B2 JP4909737B2 JP2006532423A JP2006532423A JP4909737B2 JP 4909737 B2 JP4909737 B2 JP 4909737B2 JP 2006532423 A JP2006532423 A JP 2006532423A JP 2006532423 A JP2006532423 A JP 2006532423A JP 4909737 B2 JP4909737 B2 JP 4909737B2

- Authority

- JP

- Japan

- Prior art keywords

- charge storage

- layer

- gate

- region

- gate structure

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

- 238000003860 storage Methods 0.000 title claims description 104

- 230000015654 memory Effects 0.000 title claims description 50

- 239000004065 semiconductor Substances 0.000 claims description 62

- 239000000463 material Substances 0.000 claims description 25

- 238000004519 manufacturing process Methods 0.000 claims description 20

- 238000000034 method Methods 0.000 claims description 18

- 239000000758 substrate Substances 0.000 claims description 16

- 238000005530 etching Methods 0.000 claims description 8

- 239000011232 storage material Substances 0.000 claims description 5

- 150000004767 nitrides Chemical class 0.000 description 20

- 238000000151 deposition Methods 0.000 description 7

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical group [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 6

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 6

- 229920005591 polysilicon Polymers 0.000 description 6

- 229910021332 silicide Inorganic materials 0.000 description 6

- 229910052710 silicon Inorganic materials 0.000 description 6

- 239000010703 silicon Substances 0.000 description 6

- 230000006870 function Effects 0.000 description 5

- 239000002159 nanocrystal Substances 0.000 description 5

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 4

- 239000003989 dielectric material Substances 0.000 description 4

- 239000002019 doping agent Substances 0.000 description 4

- 238000001312 dry etching Methods 0.000 description 4

- 229910052581 Si3N4 Inorganic materials 0.000 description 3

- 239000004020 conductor Substances 0.000 description 3

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical compound [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 description 3

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 3

- 125000006850 spacer group Chemical group 0.000 description 3

- 238000001039 wet etching Methods 0.000 description 3

- 239000006117 anti-reflective coating Substances 0.000 description 2

- 230000015572 biosynthetic process Effects 0.000 description 2

- 230000008021 deposition Effects 0.000 description 2

- 238000010586 diagram Methods 0.000 description 2

- 238000005516 engineering process Methods 0.000 description 2

- 238000002347 injection Methods 0.000 description 2

- 239000007924 injection Substances 0.000 description 2

- 238000012986 modification Methods 0.000 description 2

- 230000004048 modification Effects 0.000 description 2

- 230000003647 oxidation Effects 0.000 description 2

- 238000007254 oxidation reaction Methods 0.000 description 2

- 238000002161 passivation Methods 0.000 description 2

- 238000000059 patterning Methods 0.000 description 2

- 235000012239 silicon dioxide Nutrition 0.000 description 2

- 239000000377 silicon dioxide Substances 0.000 description 2

- 239000010409 thin film Substances 0.000 description 2

- 229910000577 Silicon-germanium Inorganic materials 0.000 description 1

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 1

- LEVVHYCKPQWKOP-UHFFFAOYSA-N [Si].[Ge] Chemical compound [Si].[Ge] LEVVHYCKPQWKOP-UHFFFAOYSA-N 0.000 description 1

- 238000009825 accumulation Methods 0.000 description 1

- 238000003491 array Methods 0.000 description 1

- 239000013626 chemical specie Substances 0.000 description 1

- 238000005229 chemical vapour deposition Methods 0.000 description 1

- 239000010941 cobalt Substances 0.000 description 1

- 229910017052 cobalt Inorganic materials 0.000 description 1

- GUTLYIVDDKVIGB-UHFFFAOYSA-N cobalt atom Chemical compound [Co] GUTLYIVDDKVIGB-UHFFFAOYSA-N 0.000 description 1

- 238000007796 conventional method Methods 0.000 description 1

- 230000005669 field effect Effects 0.000 description 1

- 229910052732 germanium Inorganic materials 0.000 description 1

- GNPVGFCGXDBREM-UHFFFAOYSA-N germanium atom Chemical compound [Ge] GNPVGFCGXDBREM-UHFFFAOYSA-N 0.000 description 1

- 239000011521 glass Substances 0.000 description 1

- 238000000227 grinding Methods 0.000 description 1

- 239000007943 implant Substances 0.000 description 1

- 239000012212 insulator Substances 0.000 description 1

- 238000005468 ion implantation Methods 0.000 description 1

- 230000000873 masking effect Effects 0.000 description 1

- 229910052751 metal Inorganic materials 0.000 description 1

- 239000002184 metal Substances 0.000 description 1

- 150000002739 metals Chemical class 0.000 description 1

- RUFLMLWJRZAWLJ-UHFFFAOYSA-N nickel silicide Chemical compound [Ni]=[Si]=[Ni] RUFLMLWJRZAWLJ-UHFFFAOYSA-N 0.000 description 1

- 229910021334 nickel silicide Inorganic materials 0.000 description 1

- 238000000206 photolithography Methods 0.000 description 1

- 229920002120 photoresistant polymer Polymers 0.000 description 1

- 238000005498 polishing Methods 0.000 description 1

- 239000000126 substance Substances 0.000 description 1

- 229910052715 tantalum Inorganic materials 0.000 description 1

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 1

- 239000010936 titanium Substances 0.000 description 1

- 229910052719 titanium Inorganic materials 0.000 description 1

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 1

- 229910052721 tungsten Inorganic materials 0.000 description 1

- 239000010937 tungsten Substances 0.000 description 1

Images

Classifications

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B82—NANOTECHNOLOGY

- B82Y—SPECIFIC USES OR APPLICATIONS OF NANOSTRUCTURES; MEASUREMENT OR ANALYSIS OF NANOSTRUCTURES; MANUFACTURE OR TREATMENT OF NANOSTRUCTURES

- B82Y10/00—Nanotechnology for information processing, storage or transmission, e.g. quantum computing or single electron logic

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/401—Multistep manufacturing processes

- H01L29/4011—Multistep manufacturing processes for data storage electrodes

- H01L29/40114—Multistep manufacturing processes for data storage electrodes the electrodes comprising a conductor-insulator-conductor-insulator-semiconductor structure

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66409—Unipolar field-effect transistors

- H01L29/66477—Unipolar field-effect transistors with an insulated gate, i.e. MISFET

- H01L29/66825—Unipolar field-effect transistors with an insulated gate, i.e. MISFET with a floating gate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/788—Field effect transistors with field effect produced by an insulated gate with floating gate

- H01L29/7887—Programmable transistors with more than two possible different levels of programmation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/792—Field effect transistors with field effect produced by an insulated gate with charge trapping gate insulator, e.g. MNOS-memory transistors

- H01L29/7923—Programmable transistors with more than two possible different levels of programmation

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/04—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS

- G11C16/0408—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS comprising cells containing floating gate transistors

- G11C16/0441—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS comprising cells containing floating gate transistors comprising cells containing multiple floating gate devices, e.g. separate read-and-write FAMOS transistors with connected floating gates

- G11C16/0458—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS comprising cells containing floating gate transistors comprising cells containing multiple floating gate devices, e.g. separate read-and-write FAMOS transistors with connected floating gates comprising two or more independent floating gates which store independent data

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/04—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS

- G11C16/0466—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS comprising cells with charge storage in an insulating layer, e.g. metal-nitride-oxide-silicon [MNOS], silicon-oxide-nitride-oxide-silicon [SONOS]

- G11C16/0475—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS comprising cells with charge storage in an insulating layer, e.g. metal-nitride-oxide-silicon [MNOS], silicon-oxide-nitride-oxide-silicon [SONOS] comprising two or more independent storage sites which store independent data

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C2216/00—Indexing scheme relating to G11C16/00 and subgroups, for features not directly covered by these groups

- G11C2216/02—Structural aspects of erasable programmable read-only memories

- G11C2216/06—Floating gate cells in which the floating gate consists of multiple isolated silicon islands, e.g. nanocrystals

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66409—Unipolar field-effect transistors

- H01L29/66477—Unipolar field-effect transistors with an insulated gate, i.e. MISFET

- H01L29/66787—Unipolar field-effect transistors with an insulated gate, i.e. MISFET with a gate at the side of the channel

- H01L29/66795—Unipolar field-effect transistors with an insulated gate, i.e. MISFET with a gate at the side of the channel with a horizontal current flow in a vertical sidewall of a semiconductor body, e.g. FinFET, MuGFET

- H01L29/66818—Unipolar field-effect transistors with an insulated gate, i.e. MISFET with a gate at the side of the channel with a horizontal current flow in a vertical sidewall of a semiconductor body, e.g. FinFET, MuGFET the channel being thinned after patterning, e.g. sacrificial oxidation on fin

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/785—Field effect transistors with field effect produced by an insulated gate having a channel with a horizontal current flow in a vertical sidewall of a semiconductor body, e.g. FinFET, MuGFET

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/785—Field effect transistors with field effect produced by an insulated gate having a channel with a horizontal current flow in a vertical sidewall of a semiconductor body, e.g. FinFET, MuGFET

- H01L29/7855—Field effect transistors with field effect produced by an insulated gate having a channel with a horizontal current flow in a vertical sidewall of a semiconductor body, e.g. FinFET, MuGFET with at least two independent gates

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- General Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- Ceramic Engineering (AREA)

- Manufacturing & Machinery (AREA)

- Chemical & Material Sciences (AREA)

- Nanotechnology (AREA)

- Mathematical Physics (AREA)

- Theoretical Computer Science (AREA)

- Crystallography & Structural Chemistry (AREA)

- Semiconductor Memories (AREA)

- Non-Volatile Memory (AREA)

Description

他に言及されない限り、種々の図面において同じ参照符号を用いて同一の物が指示される。

以下の説明は、本発明を実施するための1つの形態の詳細な説明を述べる。その説明は、本発明を例示することを目的としており、限定するものと解釈されるべきではない。

の組み合わせのような他のゲート材料から形成することができる。図示される実施形態では、その後、層203上に、コンフォーマルな窒化物層205が堆積される。一実施形態では、層205は反射防止コーティングとして、及び層203をエッチングするためのハードマスクとして用いられる。実施形態によっては、層205は含まれない場合もある。実施形態によっては、層205を堆積する前に、層203にドープすることができる。これらの実施形態では、層205に種々のエネルギー、角度及び/又は化学種で1つ又は複数の移植材料をドープすることができる。たとえば、一実施形態では、層203の左側に、図2に示される図に対して第1の角度で第1のドーパントをドープして、その部分に第1の導電型を与えることができ、層203の右側に、図2に示される図に対して第2の角度でドープして、その部分に第2の導電型を与えることができる。

3の部分707及び709が、層203のエッチング中に除去されるのを防ぐ。ゲート構造701及びゲート構造703はそれぞれ、構造104の側壁に沿って配置される垂直な部分を有する。

機能する。ゲート構造1503が機能トランジスタのうちの一方のためのゲートとしての役割を果たし、ゲート構造1505が他方の機能トランジスタのゲートとしての役割を果たす。電荷蓄積場所1709及び電荷蓄積場所1711は、そのゲートとしてゲート構造1503を有する機能トランジスタの電荷蓄積場所としての役割を果たす。電荷蓄積場所1713及び電荷蓄積場所1715は、そのゲートとしてゲート構造1505を有する機能トランジスタの電荷蓄積場所としての役割を果たす。

ミングし、読み出し、且つ/又は消去するために、他のプログラミング技法、読出し技法及び/又は消去技法を利用することができる。たとえば、2つの記憶場所を有する不揮発性メモリセルを読み出すための他の従来の技法を用いることができる。

、蓄積場所1713、1709、1715及び1711に類似の4つの蓄積場所を含む。

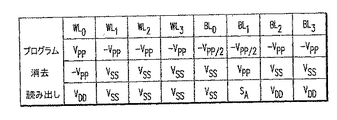

図19及び図20の表に示されるように、プログラミングされるか、消去されるか、又は読み出される電荷蓄積場所の対向するセルのゲートは、これらの動作中にグランド(VSS)にバイアスをかけられる。たとえば、ゲート構造1503は、電荷蓄積場所1713の反対側にあり、場所1713のプログラミング、消去及び読出し動作中にVSSにバイアスをかけられる。

含む。またそのメモリは、第3のワード線に結合される第1のゲート構造及び第4のワード線に結合される第2のゲート構造を有する複数のメモリセルから成る第2の行を含む。そのメモリはさらに、第1の行及び第2の行の第1の部分を含み、第1のビット線に結合される第1のドープされた領域及び第2のビット線に結合される第2のドープされた領域を有する、複数のメモリセルから成る第1の列を含む。そのメモリはさらに、第1の行及び第2の行の第2の部分を含み、第2のビット線に結合される第1のドープされた領域及び第3のビット線に結合される第2のドープされた領域を有する、複数のメモリセルから成る第2の列を含む。

Claims (4)

- フィン型トランジスタからなるメモリデバイスであって、

基板と、

該基板上に設けられ、第1の電流領域と、第2の電流領域と、前記基板に沿った方向で該第1及び第2の電流領域の間にあるチャネル領域とからなるとともに、前記チャネル領域の一方の外側面である第1の側壁と、他方の外側面に、前記第1の側壁に対向している第2の側壁とを備える半導体構造と、

前記第1の側壁に隣接し、第1及び第2の電荷蓄積場所を備える第1の電荷蓄積構造と、

前記第1の電荷蓄積構造の近傍に設けられるゲート構造とを備え、

前記基板と平行の、ある一定の面で切り取ったときに、前記チャネル領域と前記第1及び第2の電荷蓄積場所は前記一定の面上に配置されている、メモリデバイス。 - 前記電荷蓄積場所は、離散した電荷蓄積材料を含む構造内に実装される、請求項1に記載のメモリデバイス。

- 基板上に設けられ、第1の電流領域と、第2の電流領域と、前記基板に沿った方向で該第1及び第2の電流領域の間にあるチャネル領域とからなるとともに、前記チャネル領域の一方の外側面である第1の側壁と、他方の外側面に、前記第1の側壁に対向している第2の側壁とを備える半導体構造と、

前記第1の側壁に隣接し、第1及び第2の電荷蓄積場所を備える第1の電荷蓄積構造と、

前記第2の側壁に隣接し、第3及び第4の電荷蓄積場所を備える第2の電荷蓄積構造と、

前記第1の電荷蓄積構造の近傍に設けられる第1のゲート構造及び前記第2の電荷蓄積構造の近傍に設けられる第2のゲート構造とを備え、

前記基板と平行の、ある一定の面で切り取ったときに、前記チャネル領域と前記第1、第2、第3及び第4の電荷蓄積場所は前記一定の面上に配置されている、フィン型トランジスタのメモリセルを複数備えているメモリにおいて、

第1のワード線に結合される前記第1のゲート構造と、第2のワード線に結合される前記第2のゲート構造とを有する前記複数のメモリセルから成る第1の行と、

第3のワード線に結合される前記第1のゲート構造と、第4のワード線に結合される前記第2のゲート構造とを有する前記複数のメモリセルから成る第2の行と、

前記第1の行及び前記第2の行の第1の部分を含み、第1のビット線に結合される前記第1の電流領域と、第2のビット線に結合される前記第2の電流領域とを有する、前記複数のメモリセルから成る第1の列と、

前記第1の行及び前記第2の行の第2の部分を含み、前記第2のビット線に結合される前記第1の電流領域と、第3のビット線に結合される前記第2の電流領域とを有する、前記複数のメモリセルから成る第2の列とを備える、メモリ。 - 第1の電流領域と、第2の電流領域と、前記基板に沿った方向で該第1及び第2の電流領域の間にあるチャネル領域とからなるとともに、前記チャネル領域の一方の外側面である第1の側壁と、他方の外側面に、前記第1の側壁に対向している第2の側壁とを備える半導体構造を基板上に形成するステップと、

前記第1及び第2の側壁の上に電荷蓄積構造を形成するステップと、

前記電荷蓄積構造の上にゲート材料からなる層を形成するステップと、

前記ゲート材料からなる層をエッチングすることによって、前記第1の側壁の上方には第1のゲート構造を、前記第2の側壁の上方には第2のゲート構造を形成する、ゲート材料層をエッチングするステップとを備え、

前記基板と平行の、ある一定の面で切り取ったときに、前記チャネル領域と前記第1及び第2の電荷蓄積場所は前記一定の面上に配置されるとともに、前記第1の電荷蓄積構造には第1及び第2の電荷蓄積場所が設けられる、フィン型半導体デバイスの製造方法。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US10/443,908 US6903967B2 (en) | 2003-05-22 | 2003-05-22 | Memory with charge storage locations and adjacent gate structures |

| US10/443,908 | 2003-05-22 | ||

| PCT/US2004/011868 WO2004107351A1 (en) | 2003-05-22 | 2004-04-16 | Memory with charge storage locations |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2007500949A JP2007500949A (ja) | 2007-01-18 |

| JP2007500949A5 JP2007500949A5 (ja) | 2007-06-07 |

| JP4909737B2 true JP4909737B2 (ja) | 2012-04-04 |

Family

ID=33489340

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2006532423A Expired - Lifetime JP4909737B2 (ja) | 2003-05-22 | 2004-04-16 | 電荷蓄積場所を有するメモリ |

Country Status (6)

| Country | Link |

|---|---|

| US (1) | US6903967B2 (ja) |

| JP (1) | JP4909737B2 (ja) |

| KR (1) | KR20060009955A (ja) |

| CN (1) | CN100587838C (ja) |

| TW (1) | TWI257171B (ja) |

| WO (1) | WO2004107351A1 (ja) |

Families Citing this family (46)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| DE10131276B4 (de) * | 2001-06-28 | 2007-08-02 | Infineon Technologies Ag | Feldeffekttransistor und Verfahren zu seiner Herstellung |

| DE10220923B4 (de) * | 2002-05-10 | 2006-10-26 | Infineon Technologies Ag | Verfahren zur Herstellung eines nicht-flüchtigen Flash-Halbleiterspeichers |

| KR100517559B1 (ko) * | 2003-06-27 | 2005-09-28 | 삼성전자주식회사 | 핀 전계효과 트랜지스터 및 그의 핀 형성방법 |

| US7196372B1 (en) | 2003-07-08 | 2007-03-27 | Spansion Llc | Flash memory device |

| KR100496891B1 (ko) * | 2003-08-14 | 2005-06-23 | 삼성전자주식회사 | 핀 전계효과 트랜지스터를 위한 실리콘 핀 및 그 제조 방법 |

| JP2005064500A (ja) * | 2003-08-14 | 2005-03-10 | Samsung Electronics Co Ltd | マルチ構造のシリコンフィンおよび製造方法 |

| US6946377B2 (en) * | 2003-10-29 | 2005-09-20 | Texas Instruments Incorporated | Multiple-gate MOSFET device with lithography independent silicon body thickness and methods for fabricating the same |

| US7029958B2 (en) * | 2003-11-04 | 2006-04-18 | Advanced Micro Devices, Inc. | Self aligned damascene gate |

| US7091566B2 (en) * | 2003-11-20 | 2006-08-15 | International Business Machines Corp. | Dual gate FinFet |

| US20070029623A1 (en) * | 2003-12-05 | 2007-02-08 | National Inst Of Adv Industrial Science And Tech | Dual-gate field effect transistor |

| KR100598109B1 (ko) * | 2004-10-08 | 2006-07-07 | 삼성전자주식회사 | 비휘발성 기억 소자 및 그 형성 방법 |

| US7397081B2 (en) * | 2004-12-13 | 2008-07-08 | International Business Machines Corporation | Sidewall semiconductor transistors |

| KR100680291B1 (ko) * | 2005-04-22 | 2007-02-07 | 한국과학기술원 | H자형 이중 게이트 구조를 갖는 다중비트 비휘발성 메모리소자와 이의 제조 방법 및 다중비트 동작을 위한 동작방법 |

| KR101172853B1 (ko) * | 2005-07-22 | 2012-08-10 | 삼성전자주식회사 | 반도체 소자의 형성 방법 |

| US7381649B2 (en) * | 2005-07-29 | 2008-06-03 | Taiwan Semiconductor Manufacturing Company, Ltd. | Structure for a multiple-gate FET device and a method for its fabrication |

| US7446372B2 (en) * | 2005-09-01 | 2008-11-04 | Micron Technology, Inc. | DRAM tunneling access transistor |

| KR100652433B1 (ko) * | 2005-09-08 | 2006-12-01 | 삼성전자주식회사 | 다중 비트 저장이 가능한 비휘발성 메모리 소자 및 그 제조방법 |

| EP1932171B1 (en) | 2005-09-28 | 2011-11-16 | Nxp B.V. | Finfet-based non-volatile memory device |

| US7968394B2 (en) * | 2005-12-16 | 2011-06-28 | Freescale Semiconductor, Inc. | Transistor with immersed contacts and methods of forming thereof |

| US7432122B2 (en) * | 2006-01-06 | 2008-10-07 | Freescale Semiconductor, Inc. | Electronic device and a process for forming the electronic device |

| US20070166903A1 (en) * | 2006-01-17 | 2007-07-19 | Bohumil Lojek | Semiconductor structures formed by stepperless manufacturing |

| US20070166971A1 (en) * | 2006-01-17 | 2007-07-19 | Atmel Corporation | Manufacturing of silicon structures smaller than optical resolution limits |

| US7563681B2 (en) * | 2006-01-27 | 2009-07-21 | Freescale Semiconductor, Inc. | Double-gated non-volatile memory and methods for forming thereof |

| US7535060B2 (en) * | 2006-03-08 | 2009-05-19 | Freescale Semiconductor, Inc. | Charge storage structure formation in transistor with vertical channel region |

| US7583542B2 (en) * | 2006-03-28 | 2009-09-01 | Freescale Semiconductor Inc. | Memory with charge storage locations |

| KR100743655B1 (ko) | 2006-06-29 | 2007-07-30 | 주식회사 하이닉스반도체 | 새들 돌기형 트랜지스터의 제조방법 |

| US7445984B2 (en) | 2006-07-25 | 2008-11-04 | Freescale Semiconductor, Inc. | Method for removing nanoclusters from selected regions |

| US7432158B1 (en) | 2006-07-25 | 2008-10-07 | Freescale Semiconductor, Inc. | Method for retaining nanocluster size and electrical characteristics during processing |

| JP2008130645A (ja) * | 2006-11-17 | 2008-06-05 | Oki Electric Ind Co Ltd | 半導体記憶装置 |

| US8223548B2 (en) | 2007-05-24 | 2012-07-17 | National Institute Of Advanced Industrial Science And Technology | Memory device with reduced programming voltage method of reduction of programming voltage and method of reading such memory device |

| TW200847292A (en) * | 2007-05-29 | 2008-12-01 | Nanya Technology Corp | Method of manufacturing a self-aligned FinFET device |

| US7898021B2 (en) * | 2007-10-26 | 2011-03-01 | International Business Machines Corporation | Semiconductor fin based nonvolatile memory device and method for fabrication thereof |

| KR100975912B1 (ko) * | 2008-02-15 | 2010-08-13 | 한양대학교 산학협력단 | 다중 비트 비휘발성 메모리 소자 및 상기 소자의 동작 방법 |

| US7898857B2 (en) * | 2008-03-20 | 2011-03-01 | Micron Technology, Inc. | Memory structure having volatile and non-volatile memory portions |

| US20090309139A1 (en) * | 2008-06-13 | 2009-12-17 | International Business Machines Corporation | Asymmetric gate electrode and method of manufacture |

| US7999332B2 (en) * | 2009-05-14 | 2011-08-16 | International Business Machines Corporation | Asymmetric semiconductor devices and method of fabricating |

| JP2011023637A (ja) * | 2009-07-17 | 2011-02-03 | Toshiba Corp | 不揮発性半導体記憶装置及び不揮発性半導体記憶装置の製造方法 |

| US8021949B2 (en) * | 2009-12-01 | 2011-09-20 | International Business Machines Corporation | Method and structure for forming finFETs with multiple doping regions on a same chip |

| KR101140010B1 (ko) * | 2011-02-28 | 2012-06-14 | 에스케이하이닉스 주식회사 | 반도체 소자 및 그 형성방법 |

| JP2013021277A (ja) * | 2011-07-14 | 2013-01-31 | Toshiba Corp | 半導体装置および半導体装置の製造方法 |

| JP5624567B2 (ja) * | 2012-02-03 | 2014-11-12 | 株式会社東芝 | 不揮発性半導体記憶装置及びその製造方法 |

| US8785273B2 (en) | 2012-04-11 | 2014-07-22 | International Business Machines Corporation | FinFET non-volatile memory and method of fabrication |

| US8699273B2 (en) * | 2012-07-31 | 2014-04-15 | Spansion Llc | Bitline voltage regulation in non-volatile memory |

| US9397112B1 (en) * | 2015-02-06 | 2016-07-19 | Taiwan Semiconductor Manufacturing Co., Ltd. | L-shaped capacitor in thin film storage technology |

| WO2019089762A1 (en) * | 2017-11-01 | 2019-05-09 | The Charles Stark Draper Laboratory, Inc. | Vesflash non-volatile memory |

| FR3089343B1 (fr) * | 2018-11-29 | 2021-10-08 | Commissariat Energie Atomique | Procede de realisation d’un transistor fet |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH09213822A (ja) * | 1996-02-05 | 1997-08-15 | Hitachi Ltd | 半導体記憶装置とその製造方法 |

| JP2001237330A (ja) * | 1999-12-17 | 2001-08-31 | Sony Corp | 不揮発性半導体記憶装置およびその動作方法 |

| WO2002065522A1 (en) * | 2001-02-09 | 2002-08-22 | Micron Technology, Inc. | Flash memory with ultra thin vertical body transistors |

Family Cites Families (27)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4859623A (en) * | 1988-02-04 | 1989-08-22 | Amoco Corporation | Method of forming vertical gate thin film transistors in liquid crystal array |

| JPH08204191A (ja) * | 1995-01-20 | 1996-08-09 | Sony Corp | 電界効果トランジスタ及びその製造方法 |

| US5689127A (en) * | 1996-03-05 | 1997-11-18 | International Business Machines Corporation | Vertical double-gate field effect transistor |

| US6150687A (en) * | 1997-07-08 | 2000-11-21 | Micron Technology, Inc. | Memory cell having a vertical transistor with buried source/drain and dual gates |

| US6768165B1 (en) * | 1997-08-01 | 2004-07-27 | Saifun Semiconductors Ltd. | Two bit non-volatile electrically erasable and programmable semiconductor memory cell utilizing asymmetrical charge trapping |

| US6097065A (en) * | 1998-03-30 | 2000-08-01 | Micron Technology, Inc. | Circuits and methods for dual-gated transistors |

| US6104068A (en) * | 1998-09-01 | 2000-08-15 | Micron Technology, Inc. | Structure and method for improved signal processing |

| DE19846063A1 (de) | 1998-10-07 | 2000-04-20 | Forschungszentrum Juelich Gmbh | Verfahren zur Herstellung eines Double-Gate MOSFETs |

| JP2003508920A (ja) * | 1999-08-27 | 2003-03-04 | マクロニックス・アメリカ・インコーポレーテッド | 2ビット保存用の不揮発性記憶装置構造体及びその製造方法 |

| US6172905B1 (en) * | 2000-02-01 | 2001-01-09 | Motorola, Inc. | Method of operating a semiconductor device |

| US6413802B1 (en) * | 2000-10-23 | 2002-07-02 | The Regents Of The University Of California | Finfet transistor structures having a double gate channel extending vertically from a substrate and methods of manufacture |

| US6372559B1 (en) * | 2000-11-09 | 2002-04-16 | International Business Machines Corporation | Method for self-aligned vertical double-gate MOSFET |

| US6472258B1 (en) * | 2000-11-13 | 2002-10-29 | International Business Machines Corporation | Double gate trench transistor |

| US6396108B1 (en) * | 2000-11-13 | 2002-05-28 | Advanced Micro Devices, Inc. | Self-aligned double gate silicon-on-insulator (SOI) device |

| US6300182B1 (en) * | 2000-12-11 | 2001-10-09 | Advanced Micro Devices, Inc. | Field effect transistor having dual gates with asymmetrical doping for reduced threshold voltage |

| US6566682B2 (en) * | 2001-02-09 | 2003-05-20 | Micron Technology, Inc. | Programmable memory address and decode circuits with ultra thin vertical body transistors |

| US6531350B2 (en) * | 2001-02-22 | 2003-03-11 | Halo, Inc. | Twin MONOS cell fabrication method and array organization |

| US6458662B1 (en) * | 2001-04-04 | 2002-10-01 | Advanced Micro Devices, Inc. | Method of fabricating a semiconductor device having an asymmetrical dual-gate silicon-germanium (SiGe) channel MOSFET and a device thereby formed |

| DE10125967C1 (de) | 2001-05-29 | 2002-07-11 | Infineon Technologies Ag | DRAM-Zellanordnung mit vertikalen MOS-Transistoren und Verfahren zu deren Herstellung |

| KR100431489B1 (ko) * | 2001-09-04 | 2004-05-12 | 한국과학기술원 | 플래쉬 메모리 소자 및 제조방법 |

| US6689650B2 (en) * | 2001-09-27 | 2004-02-10 | International Business Machines Corporation | Fin field effect transistor with self-aligned gate |

| EP1300888B1 (en) * | 2001-10-08 | 2013-03-13 | STMicroelectronics Srl | Process for manufacturing a dual charge storage location memory cell |

| US6433609B1 (en) * | 2001-11-19 | 2002-08-13 | International Business Machines Corporation | Double-gate low power SOI active clamp network for single power supply and multiple power supply applications |

| US6800905B2 (en) * | 2001-12-14 | 2004-10-05 | International Business Machines Corporation | Implanted asymmetric doped polysilicon gate FinFET |

| US6583469B1 (en) * | 2002-01-28 | 2003-06-24 | International Business Machines Corporation | Self-aligned dog-bone structure for FinFET applications and methods to fabricate the same |

| US6657252B2 (en) * | 2002-03-19 | 2003-12-02 | International Business Machines Corporation | FinFET CMOS with NVRAM capability |

| US6846734B2 (en) * | 2002-11-20 | 2005-01-25 | International Business Machines Corporation | Method and process to make multiple-threshold metal gates CMOS technology |

-

2003

- 2003-05-22 US US10/443,908 patent/US6903967B2/en not_active Expired - Lifetime

-

2004

- 2004-04-16 CN CN200480014053A patent/CN100587838C/zh not_active Expired - Lifetime

- 2004-04-16 WO PCT/US2004/011868 patent/WO2004107351A1/en active Application Filing

- 2004-04-16 KR KR1020057022358A patent/KR20060009955A/ko not_active Application Discontinuation

- 2004-04-16 JP JP2006532423A patent/JP4909737B2/ja not_active Expired - Lifetime

- 2004-04-27 TW TW093111766A patent/TWI257171B/zh not_active IP Right Cessation

Patent Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH09213822A (ja) * | 1996-02-05 | 1997-08-15 | Hitachi Ltd | 半導体記憶装置とその製造方法 |

| JP2001237330A (ja) * | 1999-12-17 | 2001-08-31 | Sony Corp | 不揮発性半導体記憶装置およびその動作方法 |

| WO2002065522A1 (en) * | 2001-02-09 | 2002-08-22 | Micron Technology, Inc. | Flash memory with ultra thin vertical body transistors |

| JP2004527904A (ja) * | 2001-02-09 | 2004-09-09 | マイクロン・テクノロジー・インコーポレーテッド | 極薄垂直ボデイトランジスタを有するフラッシュメモリ |

Also Published As

| Publication number | Publication date |

|---|---|

| WO2004107351A1 (en) | 2004-12-09 |

| JP2007500949A (ja) | 2007-01-18 |

| TWI257171B (en) | 2006-06-21 |

| CN100587838C (zh) | 2010-02-03 |

| TW200507245A (en) | 2005-02-16 |

| CN1795510A (zh) | 2006-06-28 |

| KR20060009955A (ko) | 2006-02-01 |

| US20050057964A1 (en) | 2005-03-17 |

| US6903967B2 (en) | 2005-06-07 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4909737B2 (ja) | 電荷蓄積場所を有するメモリ | |

| KR101079562B1 (ko) | 독립 게이트 구조들을 구비한 트랜지스터 | |

| US6831310B1 (en) | Integrated circuit having multiple memory types and method of formation | |

| US6969656B2 (en) | Method and circuit for multiplying signals with a transistor having more than one independent gate structure | |

| US7433243B2 (en) | Operation method of non-volatile memory | |

| US7807526B2 (en) | Method of fabricating high-density, trench-based non-volatile random access SONOS memory cells for SOC applications | |

| US7098502B2 (en) | Transistor having three electrically isolated electrodes and method of formation | |

| TWI390710B (zh) | 鰭式場效電晶體中之分裂閘極記憶體單元 | |

| US8143667B2 (en) | Semiconductor device having non-volatile memory and method of fabricating the same | |

| US20090267127A1 (en) | Single Poly NVM Devices and Arrays | |

| US20160071858A1 (en) | Semiconductor device | |

| KR20070017552A (ko) | 듀얼 폴리를 사용하는 비트라인 임플랜트 | |

| JP4547749B2 (ja) | 不揮発性半導体記憶装置 | |

| US7491600B2 (en) | Nanocrystal bitcell process integration for high density application | |

| US7583542B2 (en) | Memory with charge storage locations | |

| JP2004056071A (ja) | 半導体素子の製造方法及びその素子 | |

| JP2009135214A (ja) | 半導体記憶装置およびその製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070413 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20070413 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20101015 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20101026 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20110126 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20110202 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110228 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20111220 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20120116 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150120 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4909737 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| S533 | Written request for registration of change of name |

Free format text: JAPANESE INTERMEDIATE CODE: R313533 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| EXPY | Cancellation because of completion of term |