JP4908006B2 - 半導体装置 - Google Patents

半導体装置 Download PDFInfo

- Publication number

- JP4908006B2 JP4908006B2 JP2006026782A JP2006026782A JP4908006B2 JP 4908006 B2 JP4908006 B2 JP 4908006B2 JP 2006026782 A JP2006026782 A JP 2006026782A JP 2006026782 A JP2006026782 A JP 2006026782A JP 4908006 B2 JP4908006 B2 JP 4908006B2

- Authority

- JP

- Japan

- Prior art keywords

- comb

- wiring

- mos

- capacitor

- insulating film

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D1/00—Resistors, capacitors or inductors

- H10D1/60—Capacitors

- H10D1/62—Capacitors having potential barriers

- H10D1/66—Conductor-insulator-semiconductor capacitors, e.g. MOS capacitors

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02M—APPARATUS FOR CONVERSION BETWEEN AC AND AC, BETWEEN AC AND DC, OR BETWEEN DC AND DC, AND FOR USE WITH MAINS OR SIMILAR POWER SUPPLY SYSTEMS; CONVERSION OF DC OR AC INPUT POWER INTO SURGE OUTPUT POWER; CONTROL OR REGULATION THEREOF

- H02M3/00—Conversion of DC power input into DC power output

- H02M3/02—Conversion of DC power input into DC power output without intermediate conversion into AC

- H02M3/04—Conversion of DC power input into DC power output without intermediate conversion into AC by static converters

- H02M3/06—Conversion of DC power input into DC power output without intermediate conversion into AC by static converters using resistors or capacitors, e.g. potential divider

- H02M3/07—Conversion of DC power input into DC power output without intermediate conversion into AC by static converters using resistors or capacitors, e.g. potential divider using capacitors charged and discharged alternately by semiconductor devices with control electrode, e.g. charge pumps

- H02M3/073—Charge pumps of the Schenkel-type

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D89/00—Aspects of integrated devices not covered by groups H10D84/00 - H10D88/00

- H10D89/211—Design considerations for internal polarisation

- H10D89/213—Design considerations for internal polarisation in field-effect devices

- H10D89/215—Design considerations for internal polarisation in field-effect devices comprising arrangements for charge pumping or biasing substrates

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W20/00—Interconnections in chips, wafers or substrates

- H10W20/40—Interconnections external to wafers or substrates, e.g. back-end-of-line [BEOL] metallisations or vias connecting to gate electrodes

- H10W20/495—Capacitive arrangements or effects of, or between wiring layers

- H10W20/496—Capacitor integral with wiring layers

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Semiconductor Integrated Circuits (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

Description

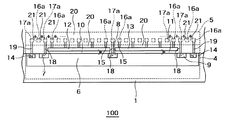

MOS構造のドレイン領域とソース領域とが共通に接続され、この共通に接続された前記ドレイン領域、前記ソース領域と前記MOS構造のゲート電極との間に静電容量を形成するMOSキャパシタと、

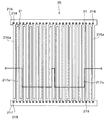

前記MOSキャパシタ上に層間絶縁膜を介して形成され前記MOSキャパシタのゲート電極と接続されるとともに櫛歯状に延出した延出部を有する第1の櫛型配線、および、前記MOSキャパシタ上に層間絶縁膜を介して形成されるとともに前記第1の櫛型配線と線間絶縁膜を介して配置され前記ドレイン領域および前記ソース領域に接続されるとともに櫛歯状に延出した延出部を有する第2の櫛型配線、を有する配線キャパシタと、を備え、

前記第2の櫛型配線の延出部は、前記第1の櫛型配線の延出部と交互に並んで配置されているとともに、前記MOSキャパシタの前記ドレイン領域と前記ソース領域を結ぶチャネル方向に対して垂直に配置されていることを特徴とする。

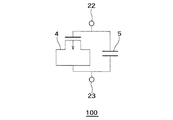

MOS構造のドレイン領域とソース領域とが共通に接続され、この共通に接続された前記ドレイン領域、ソース領域と前記MOS構造のゲート電極との間に静電容量を形成するMOSキャパシタと、前記MOSキャパシタ上に層間絶縁膜を介して形成され前記MOSキャパシタのゲート電極と接続されるとともに櫛歯状に延出した延出部を有する第1の櫛型配線、および、前記MOSキャパシタ上に層間絶縁膜を介して形成されるとともに前記第1の櫛型配線と線間絶縁膜を介して配置され前記ドレイン領域および前記ソース領域に接続されるとともに櫛歯状に延出した延出部を有する第2の櫛型配線、を有する配線キャパシタと、を備え、前記第2の櫛型配線の延出部は、前記第1の櫛型配線の延出部と交互に並んで配置されているとともに、前記MOSキャパシタの前記ドレイン領域と前記ソース領域を結ぶチャネル方向に対して垂直に配置された半導体装置と、

電源電圧が印加される入力端子にソース領域が接続された入力MOSトランジスタと、

前記入力MOSトランジスタのドレイン領域と昇圧された電圧が出力される出力端子との間で直列に接続された複数の昇圧MOSトランジスタと、を備え、

前記昇圧MOSトランジスタのソース領域に各々前記第1の櫛型配線が接続され、

隣接する前記半導体装置の前記第2の櫛型配線には、それぞれ互いに相補的なパルス信号が入力されることを特徴とする。

4 MOSキャパシタ

5 配線キャパシタ

6 n型ウェル

7、8、9 p+拡散層

10、11 ゲート絶縁膜

12、13 ゲート電極

14 n+拡散層

15 コンタクト

16 第1の櫛型配線

16a 延出部

17 第2の櫛型配線

17a 延出部

18、19 コンタクト

20 層間絶縁膜

21 線間絶縁膜

22、23 端子

25 配線キャパシタ

25a 多層配線層

30 入力端子

31 入力MOSトランジスタ

32 出力端子

33 昇圧MOSトランジスタ

100、200 半導体装置

216 第3の櫛型配線

216a 延出部

217 第4の櫛型配線

217a 延出部

218、219 コンタクト

300 チャージポンプ回路

Claims (5)

- MOS構造のドレイン領域とソース領域とが共通に接続され、この共通に接続された前記ドレイン領域、前記ソース領域と前記MOS構造のゲート電極との間に静電容量を形成するMOSキャパシタと、

前記MOSキャパシタ上に層間絶縁膜を介して形成され前記MOSキャパシタのゲート電極と接続されるとともに櫛歯状に延出した延出部を有する第1の櫛型配線、および、前記MOSキャパシタ上に層間絶縁膜を介して形成されるとともに前記第1の櫛型配線と線間絶縁膜を介して配置され前記ドレイン領域および前記ソース領域に接続されるとともに櫛歯状に延出した延出部を有する第2の櫛型配線、を有する配線キャパシタと、を備え、

前記第2の櫛型配線の延出部は、前記第1の櫛型配線の延出部と交互に並んで配置されているとともに、前記MOSキャパシタの前記ドレイン領域と前記ソース領域を結ぶチャネル方向に対して垂直に配置されていることを特徴とする半導体装置。 - 前記第1の櫛型配線と前記第2の櫛型配線とは、同じ配線層内に配置されていることを特徴とする請求項1に記載の半導体装置。

- 前記配線キャパシタは、前記第1の櫛型配線上に層間絶縁膜を介して形成され前記第1の櫛型配線とコンタクトで接続されるとともに櫛歯状に延出した延出部を有する第3の櫛型配線と、前記第2の櫛型配線上に層間絶縁膜を介して形成されるとともに前記第3の櫛型配線と線間絶縁膜を介して配置され、前記第2の櫛型配線とコンタクトで接続されるとともに櫛歯状に延出した延出部を有する第4の櫛型配線と、が層間絶縁膜を介して積層された、多層配線層をさらに有し、

前記第4の櫛型配線の延出部は、前記第3の櫛型配線の延出部と交互に並んで配置されていることを特徴とする請求項2に記載の半導体装置。 - 前記第2の櫛型配線の延出部は、前記ドレイン領域および前記ソース領域と複数のコンタクトで接続されていることを特徴とする請求項1ないし3の何れかに記載の半導体装置。

- MOS構造のドレイン領域とソース領域とが共通に接続され、この共通に接続された前記ドレイン領域、ソース領域と前記MOS構造のゲート電極との間に静電容量を形成するMOSキャパシタと、前記MOSキャパシタ上に層間絶縁膜を介して形成され前記MOSキャパシタのゲート電極と接続されるとともに櫛歯状に延出した延出部を有する第1の櫛型配線、および、前記MOSキャパシタ上に層間絶縁膜を介して形成されるとともに前記第1の櫛型配線と線間絶縁膜を介して配置され前記ドレイン領域および前記ソース領域に接続されるとともに櫛歯状に延出した延出部を有する第2の櫛型配線、を有する配線キャパシタと、を備え、前記第2の櫛型配線の延出部は、前記第1の櫛型配線の延出部と交互に並んで配置されているとともに、前記MOSキャパシタの前記ドレイン領域と前記ソース領域を結ぶチャネル方向に対して垂直に配置された半導体装置と、

電源電圧が印加される入力端子にソース領域が接続された入力MOSトランジスタと、

前記入力MOSトランジスタのドレイン領域と昇圧された電圧が出力される出力端子との間で直列に接続された複数の昇圧MOSトランジスタと、を備え、

前記昇圧MOSトランジスタのソース領域に各々前記第1の櫛型配線が接続され、

隣接する前記半導体装置の前記第2の櫛型配線には、それぞれ互いに相補的なパルス信号が入力されることを特徴とするチャージポンプ回路。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2006026782A JP4908006B2 (ja) | 2006-02-03 | 2006-02-03 | 半導体装置 |

| US11/670,605 US7557400B2 (en) | 2006-02-03 | 2007-02-02 | Semiconductor device in which capacitance of a MOS capacitor is complemented with the capacitance of a wiring capacitor |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2006026782A JP4908006B2 (ja) | 2006-02-03 | 2006-02-03 | 半導体装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2007208101A JP2007208101A (ja) | 2007-08-16 |

| JP4908006B2 true JP4908006B2 (ja) | 2012-04-04 |

Family

ID=38333164

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2006026782A Expired - Fee Related JP4908006B2 (ja) | 2006-02-03 | 2006-02-03 | 半導体装置 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US7557400B2 (ja) |

| JP (1) | JP4908006B2 (ja) |

Families Citing this family (18)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2008226998A (ja) * | 2007-03-09 | 2008-09-25 | Matsushita Electric Ind Co Ltd | 半導体集積回路 |

| JP5072731B2 (ja) | 2008-06-23 | 2012-11-14 | 株式会社東芝 | 定電圧昇圧電源 |

| US20110168782A1 (en) * | 2010-01-12 | 2011-07-14 | Nxp B.V. | Capacitance under a fringe capacitor of a radio frquency integrated circuit |

| FR2965942B1 (fr) * | 2010-10-08 | 2013-02-22 | Commissariat Energie Atomique | Afficheur a cristal liquide de type transmissif en technologie cmos avec capacite de stockage auxiliaire |

| US8916919B2 (en) * | 2011-06-23 | 2014-12-23 | International Business Machines Corporation | Interdigitated vertical native capacitor |

| TWI463674B (zh) * | 2011-09-06 | 2014-12-01 | 群聯電子股份有限公司 | 適於應用於積體電路的電容結構 |

| CN103000624B (zh) * | 2011-09-19 | 2015-07-01 | 群联电子股份有限公司 | 适于应用于集成电路的电容结构 |

| JP5947580B2 (ja) * | 2012-03-23 | 2016-07-06 | ローム株式会社 | デカップルキャパシタセル、セルベースic、セルベースicのレイアウトシステムおよびレイアウト方法 |

| JP6161267B2 (ja) * | 2012-11-28 | 2017-07-12 | ルネサスエレクトロニクス株式会社 | コンデンサ、およびチャージポンプ回路 |

| US20150137201A1 (en) * | 2013-11-20 | 2015-05-21 | Qualcomm Incorporated | High density linear capacitor |

| US9640532B2 (en) * | 2014-02-14 | 2017-05-02 | Qualcomm Incorporated | Stacked metal oxide semiconductor (MOS) and metal oxide metal (MOM) capacitor architecture |

| US10338632B2 (en) * | 2014-10-20 | 2019-07-02 | Ambiq Micro, Inc. | Adaptive voltage converter |

| US9583479B1 (en) * | 2016-01-14 | 2017-02-28 | Globalfoundries Inc. | Semiconductor charge pump with imbedded capacitor |

| JP7103780B2 (ja) * | 2017-11-27 | 2022-07-20 | ラピスセミコンダクタ株式会社 | 半導体装置 |

| US10763263B2 (en) * | 2019-01-30 | 2020-09-01 | Micron Technology, Inc. | Semiconductor device having equivalent series resistance unit |

| JP7645240B2 (ja) * | 2020-03-30 | 2025-03-13 | ソニーセミコンダクタソリューションズ株式会社 | 半導体装置及び電子機器 |

| CN115528024A (zh) * | 2021-06-25 | 2022-12-27 | 瑞昱半导体股份有限公司 | 紧凑的电容结构 |

| CN115275010A (zh) * | 2022-07-25 | 2022-11-01 | 圣邦微电子(北京)股份有限公司 | Mom电容和电荷泵电路 |

Family Cites Families (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS61263251A (ja) * | 1985-05-17 | 1986-11-21 | Nec Corp | 半導体装置 |

| JPH03293759A (ja) * | 1990-04-12 | 1991-12-25 | Fuji Electric Co Ltd | Mos集積回路装置内組み込み用キャパシタ |

| JPH0473960A (ja) * | 1990-07-16 | 1992-03-09 | Nec Ic Microcomput Syst Ltd | 半導体集積回路 |

| KR0183739B1 (ko) * | 1995-09-19 | 1999-03-20 | 김광호 | 감결합 커패시터를 포함하는 반도체 장치 및 그 제조방법 |

| TW393655B (en) * | 1997-03-24 | 2000-06-11 | Seiko Epson Corp | Semiconductor capacitance device and semiconductor device for made by using the same |

| JP2000057790A (ja) * | 1998-08-05 | 2000-02-25 | Ricoh Co Ltd | 電圧発生回路 |

| EP1057217A1 (de) * | 1998-12-16 | 2000-12-06 | Infineon Technologies AG | Integrierte schaltung mit kapazitiven elementen |

| US6037622A (en) * | 1999-03-29 | 2000-03-14 | Winbond Electronics Corporation | Charge pump circuits for low supply voltages |

| JP2002217304A (ja) * | 2000-11-17 | 2002-08-02 | Rohm Co Ltd | 半導体装置 |

| JP2004241762A (ja) * | 2003-01-16 | 2004-08-26 | Nec Electronics Corp | 半導体装置 |

| JP4751035B2 (ja) * | 2004-06-09 | 2011-08-17 | 株式会社東芝 | 半導体集積回路及び昇圧回路 |

| US7768044B2 (en) * | 2004-07-30 | 2010-08-03 | Agere Systems Inc. | Metal capacitor stacked with a MOS capacitor to provide increased capacitance density |

-

2006

- 2006-02-03 JP JP2006026782A patent/JP4908006B2/ja not_active Expired - Fee Related

-

2007

- 2007-02-02 US US11/670,605 patent/US7557400B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| US7557400B2 (en) | 2009-07-07 |

| JP2007208101A (ja) | 2007-08-16 |

| US20070181918A1 (en) | 2007-08-09 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US7557400B2 (en) | Semiconductor device in which capacitance of a MOS capacitor is complemented with the capacitance of a wiring capacitor | |

| US7436015B2 (en) | Driver for driving a load using a charge pump circuit | |

| US5598029A (en) | Power supply wiring for semiconductor device | |

| US7834377B2 (en) | Semiconductor integrated circuit device | |

| US9496403B2 (en) | Semiconductor device and method of manufacturing the same | |

| US4635088A (en) | High speed-low power consuming IGFET integrated circuit | |

| CN104183628A (zh) | 半导体装置 | |

| JP6983905B2 (ja) | 半導体装置 | |

| JP5058644B2 (ja) | ニューロンmosトランジスタ | |

| JP2013143446A (ja) | 容量素子、半導体装置及び電子機器 | |

| JPH02228063A (ja) | 高周波集積回路チヤンネル・キヤパシタ | |

| JPS61180475A (ja) | 電荷転送装置 | |

| JP2001358335A (ja) | 半導体装置 | |

| KR100257641B1 (ko) | 차동회로를 구비한 반도체 집적회로 | |

| JP4110792B2 (ja) | 容量素子及び容量素子を用いた半導体集積回路 | |

| KR101162771B1 (ko) | 고전압 작동 전계 효과 트랜지스터, 및 그것을 위한 바이어스 회로 및 고전압 회로 | |

| JPWO2013018589A1 (ja) | 半導体集積回路装置 | |

| JP2005072233A (ja) | 半導体装置 | |

| JP2003060042A (ja) | 半導体装置 | |

| JP2000150789A (ja) | 半導体集積回路 | |

| TW518697B (en) | Production-method of field-effect-transistors in integrated semiconductor-circuits and an integrated semiconductor-circuit produced with such a field-effect-transistor | |

| TW200414433A (en) | LSI alleviating hysteresis of delay time | |

| JP2001068552A (ja) | 半導体集積回路装置 | |

| JP2000101022A (ja) | 半導体集積回路装置 | |

| JPS6114760A (ja) | 高耐圧半導体スイツチ |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20080805 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20111212 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20111216 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20120112 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150120 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150120 Year of fee payment: 3 |

|

| LAPS | Cancellation because of no payment of annual fees |