JP4871590B2 - トランスコンダクタを用いた積分器及びフィルタ回路 - Google Patents

トランスコンダクタを用いた積分器及びフィルタ回路 Download PDFInfo

- Publication number

- JP4871590B2 JP4871590B2 JP2005378685A JP2005378685A JP4871590B2 JP 4871590 B2 JP4871590 B2 JP 4871590B2 JP 2005378685 A JP2005378685 A JP 2005378685A JP 2005378685 A JP2005378685 A JP 2005378685A JP 4871590 B2 JP4871590 B2 JP 4871590B2

- Authority

- JP

- Japan

- Prior art keywords

- transconductor

- current

- output

- voltage

- differential

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03H—IMPEDANCE NETWORKS, e.g. RESONANT CIRCUITS; RESONATORS

- H03H11/00—Networks using active elements

- H03H11/02—Multiple-port networks

- H03H11/04—Frequency selective two-port networks

- H03H11/0422—Frequency selective two-port networks using transconductance amplifiers, e.g. gmC filters

- H03H11/0433—Two integrator loop filters

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F3/00—Amplifiers with only discharge tubes or only semiconductor devices as amplifying elements

- H03F3/45—Differential amplifiers

- H03F3/45071—Differential amplifiers with semiconductor devices only

- H03F3/45076—Differential amplifiers with semiconductor devices only characterised by the way of implementation of the active amplifying circuit in the differential amplifier

- H03F3/45475—Differential amplifiers with semiconductor devices only characterised by the way of implementation of the active amplifying circuit in the differential amplifier using IC blocks as the active amplifying circuit

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03H—IMPEDANCE NETWORKS, e.g. RESONANT CIRCUITS; RESONATORS

- H03H11/00—Networks using active elements

- H03H11/02—Multiple-port networks

- H03H11/04—Frequency selective two-port networks

- H03H2011/0494—Complex filters

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Amplifiers (AREA)

- Networks Using Active Elements (AREA)

Description

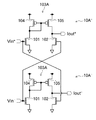

図1は、第1の参考例に係るトランスコンダクタの構成を示す。本トランスコンダクタは、差動電圧信号を受け、シングルエンドの電流信号を出力するトランスコンダクタ10A+及び10A−からなる。トランスコンダクタ10A+及び10A−の一方の反転入力端と他方の非反転入力端とは互いに接続されている。トランスコンダクタ10A+及び10A−には、それぞれ、差動電圧信号(Vin+−Vin−)及び(Vin−−Vin+)が入力される。そして、トランスコンダクタ10A+及び10A−のシングルエンド出力端からは、それぞれ、電流信号Iout+及びIout−が出力される。

第1の参考例に係るトランスコンダクタでは、例えば、図1に示したように疑似差動構成のトランジスタ101及び102によって電圧電流変換が行われる。したがって、これらトランジスタ101及び102のgm値がそのままトランスコンダクタのgm値となる。すなわち、第1の参考例に係るトランスコンダクタのgm値は差動電圧信号(Vin+−Vin−)の同相動作点に影響される。さらに言うと、第1の参考例に係るトランスコンダクタの差動出力の動作点は、入力動作点以外にも、環境温度、電源電圧及びプロセスばらつき等により変動する。出力動作点の変動は、特に、複数のトランスコンダクタが縦続接続されるアプリケーション、例えば、図11に示したようなGm−Cフィルタなどでは特性劣化の要因となる。したがって、第1の参考例に係るトランスコンダクタについてさらに出力動作点を安定化させることが求められる。以下に説明する第2の参考例に係るトランスコンダクタは出力動作点をより正確に制御可能にするものである。

上記の各参考例に係るトランスコンダクタに容量を付加することで積分器が構成される。例えば、図4に示したトランスコンダクタの場合、容量を接続する箇所は、差動出力端間、差動出力端と同相帰還回路22の出力端との間、及びカレントミラー回路103の入出力端間の3箇所である。図6は、本発明の実施形態に係る積分器の構成を示す。本積分器は、図4に示したトランスコンダクタにおける上記3箇所に、容量31、32+及び32−、及び33+及び33−を付加したものである。容量31は、当該トランスコンダクタの差動出力端間に接続されている。容量32+及び32−は、差動出力端と同相帰還回路22の出力端との間に接続されている。容量33+及び33−は、カレントミラー回路103の入出力端間に接続されている。本積分器は、容量31の両端電圧を差動電圧信号(Vout+−Vout−)として出力する。

差動出力端と同相帰還回路22の出力端との間の容量32は、フィルタ容量以外に同相帰還を安定させるための位相補償容量としても機能する。換言すると、容量32は、同相モードでは同相帰還回路22の位相補償容量として機能し、差動モードではトランスコンダクタ20の差動出力端に接続された接地容量として機能するといった二つの機能を併せ持つ。したがって、容量32は、フィルタ容量としては容量31に比べて4倍の大きさを必要とするため面積の点では不利であるが、上記の二つの機能を併せ持つため使用効率はよい。なお、もし容量32を設けるとしても、本積分器における同相帰還ループのゲインは小さいため、その容量値はごく小さなものでよい。また、同相帰還ループのゲインが十分に小さい場合には、容量32は特に省略してもよい。

本積分器の差動出力は、トランスコンダクタ20におけるカレントミラー回路103の出力側から出力されるため、その同相動作点は電源電圧とグランド電圧との間の適当なところで安定する。しかし、入出力間にカレントミラー回路103が介在するため、その分遅延が生じてしまい伝達特性が劣化するという欠点がある。特に、本積分器を用いて構成したGm−Cフィルタにおいて入力周波数が高い場合、フィルタの高周波のゲイン特性がカレントミラー回路による遅延の影響を受けて理想値からずれてしまうおそれがある。

10A−,10B−,10C− トランスコンダクタ(第2のトランスコンダクタ)

101 トランジスタ(第1の電圧電流変換回路、電圧電流変換回路)

102 トランジスタ(第2の電圧電流変換回路、電圧電流変換回路)

103A,103B カレントミラー回路

108,109 トランジスタ(電圧電流変換回路)

21+ 可変電流源(第1の可変電流源)

21− 可変電流源(第2の可変電流源)

22 同相帰還回路

23+ 定電流源(第1の定電流源)

23− 定電流源(第1の定電流源)

31,32+、32−、33+、33− 容量

Claims (3)

- 差動電圧信号を受け、差動電流信号を出力するトランスコンダクタと、第1および第2の容量とを備えた積分器であって、

前記トランスコンダクタは、前記差動電圧信号を受け、シングルエンドの電流信号を出力する第1及び第2のトランスコンダクタを備えており、

前記第1及び第2のトランスコンダクタの一方の反転入力端と他方の非反転入力端とは互いに接続されており、

前記第1及び第2のトランスコンダクタのそれぞれは、前記差動電圧信号の正側及び負側のそれぞれが入力される第1及び第2の電圧電流変換回路と、入力側及び出力側に前記第1及び第2の電圧電流変換回路のそれぞれが接続されたカレントミラー回路とを有し、前記第2の電圧電流変換回路と前記カレントミラー回路との接続点から前記シングルエンドの電流信号を出力するものであり、

前記トランスコンダクタは、前記第1及び第2のトランスコンダクタのそれぞれから出力された電流信号を前記差動電流信号として出力するものであり、

前記第1の容量が、前記第1のトランスコンダクタにおけるカレントミラー回路の入出力端間に接続され、

前記第2の容量が、前記第2のトランスコンダクタにおけるカレントミラー回路の入出力端間に接続されている

ことを特徴とする積分器。 - 差動電圧信号を受け、差動電流信号を出力するトランスコンダクタと、第1、第2、第3、第4および第5の容量とを備えた積分器であって、

前記トランスコンダクタは、前記差動電圧信号を受け、シングルエンドの電流信号を出力する第1及び第2のトランスコンダクタを備えており、

前記第1及び第2のトランスコンダクタの一方の反転入力端と他方の非反転入力端とは互いに接続されており、

前記第1及び第2のトランスコンダクタのそれぞれは、前記差動電圧信号の正側及び負側のそれぞれが入力される第1及び第2の電圧電流変換回路と、入力側及び出力側に前記第1及び第2の電圧電流変換回路のそれぞれが接続されたカレントミラー回路とを有し、前記第2の電圧電流変換回路と前記カレントミラー回路との接続点から前記シングルエンドの電流信号を出力するものであり、

前記トランスコンダクタは、前記第1及び第2のトランスコンダクタのそれぞれにおけるカレントミラー回路の入力側及び出力側のいずれか一方に接続された第1及び第2の可変電流源と、当該トランスコンダクタの差動出力の動作点電圧と基準電圧との差に基づいて、前記第1及び第2の可変電流源を制御する同相帰還回路とを備え、前記第1及び第2のトランスコンダクタのそれぞれから出力された電流信号を前記差動電流信号として出力するものであり、

前記第1の容量が、前記トランスコンダクタの差動出力端間に接続され、

前記第2の容量が、前記第1のトランスコンダクタの出力端と前記同相帰還回路の出力端との間に接続され、

前記第3の容量が、前記第2のトランスコンダクタの出力端と前記同相帰還回路の出力端との間に接続され、

前記第4の容量が、前記第1のトランスコンダクタにおけるカレントミラー回路の入出力端間に接続され、

前記第5の容量が、前記第2のトランスコンダクタにおけるカレントミラー回路の入出力端間に接続されている

ことを特徴とする積分器。 - 請求項1および2のいずれか一つに記載の積分器を備えた

ことを特徴とするフィルタ回路。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005378685A JP4871590B2 (ja) | 2005-12-28 | 2005-12-28 | トランスコンダクタを用いた積分器及びフィルタ回路 |

| US11/643,704 US7605645B2 (en) | 2005-12-28 | 2006-12-22 | Transconductor, integrator, and filter circuit |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005378685A JP4871590B2 (ja) | 2005-12-28 | 2005-12-28 | トランスコンダクタを用いた積分器及びフィルタ回路 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2007181032A JP2007181032A (ja) | 2007-07-12 |

| JP2007181032A5 JP2007181032A5 (ja) | 2008-08-28 |

| JP4871590B2 true JP4871590B2 (ja) | 2012-02-08 |

Family

ID=38192905

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2005378685A Expired - Fee Related JP4871590B2 (ja) | 2005-12-28 | 2005-12-28 | トランスコンダクタを用いた積分器及びフィルタ回路 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US7605645B2 (ja) |

| JP (1) | JP4871590B2 (ja) |

Families Citing this family (17)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7719343B2 (en) | 2003-09-08 | 2010-05-18 | Peregrine Semiconductor Corporation | Low noise charge pump method and apparatus |

| JP4711092B2 (ja) * | 2005-07-05 | 2011-06-29 | 日本電気株式会社 | 電流変換方法、トランスコンダクタンスアンプおよびこれを用いたフィルタ回路 |

| US7405625B1 (en) * | 2007-04-25 | 2008-07-29 | Analog Devices, Inc. | Common-mode control structures and signal converter systems for use therewith |

| US8816659B2 (en) | 2010-08-06 | 2014-08-26 | Peregrine Semiconductor Corporation | Low-noise high efficiency bias generation circuits and method |

| US9660590B2 (en) | 2008-07-18 | 2017-05-23 | Peregrine Semiconductor Corporation | Low-noise high efficiency bias generation circuits and method |

| US9030248B2 (en) | 2008-07-18 | 2015-05-12 | Peregrine Semiconductor Corporation | Level shifter with output spike reduction |

| EP2346169A3 (en) * | 2008-07-18 | 2013-11-20 | Peregrine Semiconductor Corporation | Low-noise high efficiency bias generation circuits and method |

| US9264053B2 (en) | 2011-01-18 | 2016-02-16 | Peregrine Semiconductor Corporation | Variable frequency charge pump |

| US8686787B2 (en) | 2011-05-11 | 2014-04-01 | Peregrine Semiconductor Corporation | High voltage ring pump with inverter stages and voltage boosting stages |

| US8633764B2 (en) * | 2011-06-10 | 2014-01-21 | International Business Machines Corporation | Restoring output common-mode of amplifier via capacitive coupling |

| CN104604141A (zh) * | 2012-09-07 | 2015-05-06 | 旭化成微电子株式会社 | 采样保持电路、a/d转换器、采样保持电路的校准方法以及电路 |

| JP2019041155A (ja) | 2017-08-22 | 2019-03-14 | 富士通株式会社 | Ota回路及びフィルタ |

| KR101982209B1 (ko) * | 2018-06-14 | 2019-05-24 | 고려대학교 산학협력단 | 연속 시간 델타-시그마 변조기 |

| US10637441B1 (en) | 2018-11-30 | 2020-04-28 | Nxp B.V. | Polyphase Gm-C filter using Gm cells |

| EP3672073B1 (en) | 2018-12-20 | 2023-02-08 | ams AG | Transconductor circuitry with adaptive biasing |

| CN109873614A (zh) * | 2019-01-03 | 2019-06-11 | 重庆邮电大学 | 一种高共模抑制比的电流反馈型仪表放大器 |

| CN114448384B (zh) * | 2022-02-09 | 2023-07-21 | 深圳市九天睿芯科技有限公司 | 一种滤波电路 |

Family Cites Families (19)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS61214810A (ja) * | 1985-03-20 | 1986-09-24 | Toshiba Corp | カレントミラ−回路 |

| JPH0618308B2 (ja) * | 1985-04-08 | 1994-03-09 | ソニー株式会社 | 平衡型差動増幅器 |

| NL8801412A (nl) * | 1988-06-02 | 1990-01-02 | Philips Nv | Asymmetrisch polyfase filter. |

| JPH03119597A (ja) * | 1989-09-29 | 1991-05-21 | Fujitsu Ltd | 差電圧増幅回路 |

| JPH0785682A (ja) * | 1993-09-20 | 1995-03-31 | Fujitsu Ltd | 差動増幅回路 |

| US5489872A (en) * | 1994-01-25 | 1996-02-06 | Texas Instruments Incorporated | Transconductance-capacitor filter circuit with current sensor circuit |

| US5912583A (en) * | 1997-01-02 | 1999-06-15 | Texas Instruments Incorporated | Continuous time filter with programmable bandwidth and tuning loop |

| US5856757A (en) * | 1997-06-11 | 1999-01-05 | Philips Electronics North America Corporation | gm-C cell with two stage common mode control and current boost |

| JP3490648B2 (ja) * | 1998-09-08 | 2004-01-26 | 株式会社東芝 | トランスコンダクタ及びこれを用いたフィルタ回路 |

| JP2001209901A (ja) * | 2000-01-25 | 2001-08-03 | Hitachi Ltd | 磁気ディスクメモリ装置 |

| JP2001274641A (ja) * | 2000-03-27 | 2001-10-05 | Toshiba Corp | 差動増幅器及びこれを用いたフィルタ回路 |

| US6456158B1 (en) * | 2000-10-13 | 2002-09-24 | Oki America, Inc. | Digitally programmable transconductor |

| JP3584893B2 (ja) * | 2001-03-14 | 2004-11-04 | ソニー株式会社 | フィルタ回路 |

| JP4572481B2 (ja) * | 2001-04-09 | 2010-11-04 | ソニー株式会社 | トランスコンダクタ回路 |

| JP3874649B2 (ja) * | 2001-11-19 | 2007-01-31 | 株式会社東芝 | 平衡回路 |

| US6727757B1 (en) * | 2003-01-02 | 2004-04-27 | Texas Instruments Incoporated | Biasing circuit for transconductors |

| US7091785B2 (en) * | 2003-06-09 | 2006-08-15 | Microchip Technology Inc. | Load and line regulation using operational transconductance amplifier and operational amplifier in tandem |

| JP3805769B2 (ja) * | 2003-12-17 | 2006-08-09 | 株式会社東芝 | 差動対回路及び演算増幅回路 |

| US7279974B2 (en) * | 2005-06-10 | 2007-10-09 | Texas Instruments Incorporated | Fully differential large swing variable gain amplifier |

-

2005

- 2005-12-28 JP JP2005378685A patent/JP4871590B2/ja not_active Expired - Fee Related

-

2006

- 2006-12-22 US US11/643,704 patent/US7605645B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| JP2007181032A (ja) | 2007-07-12 |

| US20070146064A1 (en) | 2007-06-28 |

| US7605645B2 (en) | 2009-10-20 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4871590B2 (ja) | トランスコンダクタを用いた積分器及びフィルタ回路 | |

| US7414468B2 (en) | Amplifier, filter using the same, and radio communication device | |

| Sutula et al. | Variable-mirror amplifier: A new family of process-independent class-AB single-stage OTAs for low-power SC circuits | |

| JPH10173482A (ja) | フィルタ回路 | |

| US6919768B2 (en) | Balanced amplifier and filter using the same | |

| CN107294497B (zh) | 转换电路、心跳电流信号转换装置及方法、心跳检测系统 | |

| JP5239451B2 (ja) | 差動単相変換回路 | |

| JP6488674B2 (ja) | Dcオフセットキャンセル回路 | |

| JP2008294682A (ja) | 可変インピーダンス回路、それを用いた可変インピーダンスシステム、フィルタ回路、増幅器、通信システム | |

| JP5109895B2 (ja) | 増幅回路及び受信装置 | |

| JP6336217B1 (ja) | ポリフェーズフィルタ | |

| WO2018116825A1 (ja) | 単相差動変換回路およびその信号処理方法、並びに、受信装置 | |

| US7323931B2 (en) | System and method for operating a feedback network | |

| US7425868B2 (en) | Apparatus and method for canceling DC output offset | |

| JP5065280B2 (ja) | トランスコンダクタンス段の構成 | |

| JP2007505585A (ja) | トランスコンダクタ回路における改良およびトランスコンダクタ回路に関連する改良 | |

| JP2008124647A (ja) | 増幅器およびそれを搭載した通信システム | |

| KR20190021947A (ko) | 엔벨로프 트래킹 바이어스 회로 | |

| US7345527B2 (en) | Ultra wideband filter based on a pair of cross-coupled transistors | |

| CN101174821B (zh) | 一种与温度及电源电压无关的可调有源电感 | |

| KR20060099976A (ko) | 전류싱크를 이용한 연산 트랜스컨덕턴스 증폭기 | |

| JP3917571B2 (ja) | 差動回路とそれを用いたトランスコンダクタ | |

| US6700445B2 (en) | Filter circuits based on trans-conductor circuits | |

| US20040257153A1 (en) | Continuous-time filter | |

| JP2001339275A (ja) | フィルタ回路とこれを用いた検波回路 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080714 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20080714 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20100602 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100608 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100806 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110315 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110426 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20111025 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20111121 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4871590 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20141125 Year of fee payment: 3 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313113 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |