JP4822572B2 - 半導体記憶装置 - Google Patents

半導体記憶装置 Download PDFInfo

- Publication number

- JP4822572B2 JP4822572B2 JP24858099A JP24858099A JP4822572B2 JP 4822572 B2 JP4822572 B2 JP 4822572B2 JP 24858099 A JP24858099 A JP 24858099A JP 24858099 A JP24858099 A JP 24858099A JP 4822572 B2 JP4822572 B2 JP 4822572B2

- Authority

- JP

- Japan

- Prior art keywords

- voltage

- circuit

- supply node

- node

- signal

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C5/00—Details of stores covered by group G11C11/00

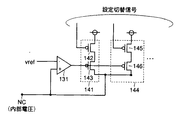

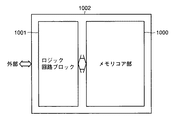

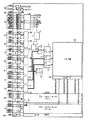

- G11C5/14—Power supply arrangements, e.g. power down, chip selection or deselection, layout of wirings or power grids, or multiple supply levels

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/21—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements

- G11C11/34—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices

- G11C11/40—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors

- G11C11/401—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming cells needing refreshing or charge regeneration, i.e. dynamic cells

- G11C11/4063—Auxiliary circuits, e.g. for addressing, decoding, driving, writing, sensing or timing

- G11C11/407—Auxiliary circuits, e.g. for addressing, decoding, driving, writing, sensing or timing for memory cells of the field-effect type

- G11C11/4074—Power supply or voltage generation circuits, e.g. bias voltage generators, substrate voltage generators, back-up power, power control circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C5/00—Details of stores covered by group G11C11/00

- G11C5/14—Power supply arrangements, e.g. power down, chip selection or deselection, layout of wirings or power grids, or multiple supply levels

- G11C5/143—Detection of memory cassette insertion or removal; Continuity checks of supply or ground lines; Detection of supply variations, interruptions or levels ; Switching between alternative supplies

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C5/00—Details of stores covered by group G11C11/00

- G11C5/14—Power supply arrangements, e.g. power down, chip selection or deselection, layout of wirings or power grids, or multiple supply levels

- G11C5/147—Voltage reference generators, voltage or current regulators; Internally lowered supply levels; Compensation for voltage drops

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Computer Hardware Design (AREA)

- Dram (AREA)

- For Increasing The Reliability Of Semiconductor Memories (AREA)

- Static Random-Access Memory (AREA)

- Stabilization Of Oscillater, Synchronisation, Frequency Synthesizers (AREA)

Priority Applications (6)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP24858099A JP4822572B2 (ja) | 1999-09-02 | 1999-09-02 | 半導体記憶装置 |

| US09/514,364 US6201754B1 (en) | 1999-09-02 | 2000-02-28 | Semiconductor memory device having function of supplying stable power supply voltage |

| TW089115797A TW456106B (en) | 1999-09-02 | 2000-08-05 | Semiconductor memory device |

| KR10-2000-0051515A KR100381492B1 (ko) | 1999-09-02 | 2000-09-01 | 안정된 전원 전압을 공급하는 기능을 구비한 반도체 기억장치 |

| US09/764,134 US6337828B2 (en) | 1999-09-02 | 2001-01-19 | Semiconductor memory device having function of supplying stable power supply voltage |

| US10/036,512 US6606274B2 (en) | 1999-09-02 | 2002-01-07 | Semiconductor memory device having function of supplying stable power supply voltage |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP24858099A JP4822572B2 (ja) | 1999-09-02 | 1999-09-02 | 半導体記憶装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2001076484A JP2001076484A (ja) | 2001-03-23 |

| JP2001076484A5 JP2001076484A5 (enExample) | 2006-09-21 |

| JP4822572B2 true JP4822572B2 (ja) | 2011-11-24 |

Family

ID=17180251

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP24858099A Expired - Fee Related JP4822572B2 (ja) | 1999-09-02 | 1999-09-02 | 半導体記憶装置 |

Country Status (4)

| Country | Link |

|---|---|

| US (3) | US6201754B1 (enExample) |

| JP (1) | JP4822572B2 (enExample) |

| KR (1) | KR100381492B1 (enExample) |

| TW (1) | TW456106B (enExample) |

Families Citing this family (21)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6487648B1 (en) * | 1999-12-15 | 2002-11-26 | Xilinx, Inc. | SDRAM controller implemented in a PLD |

| US6675330B1 (en) * | 2000-01-07 | 2004-01-06 | National Seminconductor Corporation | Testing the operation of integrated circuits by simulating a switching-mode of their power supply inputs |

| KR100374641B1 (ko) * | 2000-11-24 | 2003-03-04 | 삼성전자주식회사 | 스탠바이 모드에서 지연동기 루프회로의 전력소모를감소시키기 위한 제어회로를 구비하는 반도체 메모리장치및 이의 파우워 다운 제어방법 |

| US20040085845A1 (en) * | 2002-10-31 | 2004-05-06 | Mitsubishi Denki Kabushiki Kaisha | Semiconductor device and semiconductor memory device provided with internal current setting adjustment circuit |

| US6940777B2 (en) * | 2002-10-31 | 2005-09-06 | Renesas Technology Corp. | Semiconductor device and semiconductor memory device provided with internal current setting adjustment circuit |

| KR100576453B1 (ko) * | 2004-03-06 | 2006-05-08 | 주식회사 하이닉스반도체 | 병렬 테스트 회로를 포함하는 메모리 장치 |

| US7142477B1 (en) * | 2004-06-18 | 2006-11-28 | Cypress Semiconductor Corp. | Memory interface system and method for reducing cycle time of sequential read and write accesses using separate address and data buses |

| US7154794B2 (en) * | 2004-10-08 | 2006-12-26 | Lexmark International, Inc. | Memory regulator system with test mode |

| US7170810B1 (en) * | 2005-06-16 | 2007-01-30 | Altera Corporation | Stable programming circuitry for programmable integrated circuits |

| US7248531B2 (en) * | 2005-08-03 | 2007-07-24 | Mosaid Technologies Incorporated | Voltage down converter for high speed memory |

| US20070171735A1 (en) * | 2006-01-25 | 2007-07-26 | Jong-Hoon Oh | Latency circuit for semiconductor memories |

| KR100855969B1 (ko) * | 2007-01-10 | 2008-09-02 | 삼성전자주식회사 | 반도체 메모리장치의 내부 전원전압 발생기 |

| US8264906B2 (en) * | 2007-05-29 | 2012-09-11 | Rambus Inc. | Adjusting clock error across a circuit interface |

| EP2006696A1 (en) * | 2007-06-20 | 2008-12-24 | Nxp B.V. | Testable integrated circuit and test method |

| KR20080113969A (ko) * | 2007-06-26 | 2008-12-31 | 주식회사 하이닉스반도체 | 동시 테스트 모드를 지원하는 테스트 회로 |

| US8014214B2 (en) * | 2007-11-08 | 2011-09-06 | Hynix Semiconductor Inc. | Semiconductor memory device |

| US8149643B2 (en) | 2008-10-23 | 2012-04-03 | Cypress Semiconductor Corporation | Memory device and method |

| US8188786B2 (en) * | 2009-09-24 | 2012-05-29 | International Business Machines Corporation | Modularized three-dimensional capacitor array |

| US9230690B2 (en) * | 2012-11-07 | 2016-01-05 | Apple Inc. | Register file write ring oscillator |

| KR102032230B1 (ko) * | 2013-08-01 | 2019-10-16 | 에스케이하이닉스 주식회사 | 반도체 장치 |

| KR20240067516A (ko) * | 2022-11-09 | 2024-05-17 | 삼성전자주식회사 | 메모리 장치 및 그의 동작 방법 |

Family Cites Families (21)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR100209449B1 (ko) * | 1990-05-21 | 1999-07-15 | 가나이 쓰토무 | 반도체 집적회로 장치 |

| JP2785548B2 (ja) * | 1991-10-25 | 1998-08-13 | 日本電気株式会社 | 半導体メモリ |

| US5329168A (en) * | 1991-12-27 | 1994-07-12 | Nec Corporation | Semiconductor integrated circuit device equipped with substrate biasing system selectively powered from internal and external power sources |

| US5400343A (en) * | 1992-02-28 | 1995-03-21 | Intel Corporation | Apparatus and method for defective column detection for semiconductor memories |

| JP3166281B2 (ja) * | 1992-04-14 | 2001-05-14 | 株式会社日立製作所 | 半導体集積回路及びその製造方法 |

| FR2690751B1 (fr) * | 1992-04-30 | 1994-06-17 | Sgs Thomson Microelectronics | Procede et circuit de detection de fuites de courant dans une ligne de bit. |

| JP3583482B2 (ja) * | 1994-10-04 | 2004-11-04 | 株式会社ルネサステクノロジ | 半導体集積回路装置 |

| JPH08153400A (ja) * | 1994-11-29 | 1996-06-11 | Mitsubishi Electric Corp | Dram |

| JP3542649B2 (ja) * | 1994-12-28 | 2004-07-14 | 株式会社ルネサステクノロジ | 半導体記憶装置およびその動作方法 |

| JP3523718B2 (ja) | 1995-02-06 | 2004-04-26 | 株式会社ルネサステクノロジ | 半導体装置 |

| JPH0969300A (ja) * | 1995-06-23 | 1997-03-11 | Mitsubishi Electric Corp | 半導体記憶装置 |

| JP3612634B2 (ja) * | 1996-07-09 | 2005-01-19 | 富士通株式会社 | 高速クロック信号に対応した入力バッファ回路、集積回路装置、半導体記憶装置、及び集積回路システム |

| JPH10171774A (ja) * | 1996-12-13 | 1998-06-26 | Fujitsu Ltd | 半導体集積回路 |

| US6208567B1 (en) * | 1997-01-31 | 2001-03-27 | Matsushita Electric Industrial Co., Ltd. | Semiconductor device capable of cutting off a leakage current in a defective array section |

| JPH10247398A (ja) * | 1997-03-05 | 1998-09-14 | Matsushita Electric Ind Co Ltd | 半導体記憶装置及びその検査方法 |

| JP3967002B2 (ja) * | 1997-09-11 | 2007-08-29 | 株式会社ルネサステクノロジ | 半導体集積回路 |

| JP4074697B2 (ja) * | 1997-11-28 | 2008-04-09 | 株式会社ルネサステクノロジ | 半導体装置 |

| KR100245411B1 (ko) * | 1997-12-20 | 2000-02-15 | 윤종용 | 반도체 장치의 병렬 테스트 회로 |

| US6005812A (en) * | 1998-02-27 | 1999-12-21 | Micron Technology, Inc. | Device and method for supplying current to a semiconductor memory to support a boosted voltage within the memory during testing |

| ITMI981124A1 (it) * | 1998-05-21 | 1999-11-21 | Sgs Thomson Microelectronics | Metodo processo e dispositivo per l'individuazione di difetti puntuali che provocano correnti di leakage in un dispositivo di memoria non |

| JP3587702B2 (ja) * | 1998-10-20 | 2004-11-10 | 富士通株式会社 | Dll回路を内蔵する集積回路装置 |

-

1999

- 1999-09-02 JP JP24858099A patent/JP4822572B2/ja not_active Expired - Fee Related

-

2000

- 2000-02-28 US US09/514,364 patent/US6201754B1/en not_active Expired - Lifetime

- 2000-08-05 TW TW089115797A patent/TW456106B/zh not_active IP Right Cessation

- 2000-09-01 KR KR10-2000-0051515A patent/KR100381492B1/ko not_active Expired - Fee Related

-

2001

- 2001-01-19 US US09/764,134 patent/US6337828B2/en not_active Expired - Lifetime

-

2002

- 2002-01-07 US US10/036,512 patent/US6606274B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| KR20010030218A (ko) | 2001-04-16 |

| TW456106B (en) | 2001-09-21 |

| US6606274B2 (en) | 2003-08-12 |

| US20020054532A1 (en) | 2002-05-09 |

| US6337828B2 (en) | 2002-01-08 |

| KR100381492B1 (ko) | 2003-04-23 |

| JP2001076484A (ja) | 2001-03-23 |

| US6201754B1 (en) | 2001-03-13 |

| US20010002175A1 (en) | 2001-05-31 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4822572B2 (ja) | 半導体記憶装置 | |

| JP4632114B2 (ja) | 半導体集積回路装置 | |

| KR100529033B1 (ko) | 동기식 반도체 메모리 소자 | |

| US8923082B2 (en) | Semiconductor device on which wafer-level burn-in test is performed and manufacturing method thereof | |

| JP5119795B2 (ja) | 半導体メモリ、半導体メモリのテスト方法およびシステム | |

| US6794678B2 (en) | Semiconductor integrated circuit device, method of testing semiconductor integrated circuit device and method of manufacturing semiconductor integrated circuit device | |

| US5956278A (en) | Semiconductor circuit device with internal power supply circuit | |

| US7602656B2 (en) | Power supply control circuit and controlling method thereof | |

| KR20000006546A (ko) | 로우디코더를갖는메모리장치 | |

| JP4962301B2 (ja) | 半導体集積回路およびシステム | |

| US7649790B2 (en) | Semiconductor memory device | |

| US7068083B2 (en) | Synchronous output buffer, synchronous memory device and method of testing access time | |

| US6894942B2 (en) | Refresh control circuit and method for semiconductor memory device | |

| US7898884B2 (en) | Semiconductor device and test method therefor | |

| JP5592238B2 (ja) | 半導体装置及びその制御方法 | |

| US7679969B2 (en) | Semiconductor memory device utilizing data mask signal for sharing an input/output channel in a test mode and data output method using the same | |

| KR100649059B1 (ko) | 반도체 집적 회로 | |

| KR0172351B1 (ko) | 셀프 번-인 테스트 회로를 가지는 반도체 메모리장치 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20060803 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20060803 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20090601 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20090609 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090730 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100216 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100414 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20100519 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20101102 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20101224 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20110830 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20110906 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140916 Year of fee payment: 3 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| LAPS | Cancellation because of no payment of annual fees |