JP4804497B2 - 半導体装置 - Google Patents

半導体装置 Download PDFInfo

- Publication number

- JP4804497B2 JP4804497B2 JP2008075930A JP2008075930A JP4804497B2 JP 4804497 B2 JP4804497 B2 JP 4804497B2 JP 2008075930 A JP2008075930 A JP 2008075930A JP 2008075930 A JP2008075930 A JP 2008075930A JP 4804497 B2 JP4804497 B2 JP 4804497B2

- Authority

- JP

- Japan

- Prior art keywords

- lead

- resin sealing

- sealing body

- semiconductor chip

- exposed

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

Images

Classifications

-

- H10W72/60—

-

- H10W72/016—

-

- H10W72/07336—

-

- H10W72/07636—

-

- H10W72/5522—

-

- H10W72/877—

-

- H10W72/884—

-

- H10W72/926—

-

- H10W74/00—

-

- H10W90/726—

-

- H10W90/736—

-

- H10W90/756—

Landscapes

- Wire Bonding (AREA)

- Cooling Or The Like Of Semiconductors Or Solid State Devices (AREA)

Description

本発明の他の目的は、放熱性が高く、実装時の半田付け良否を目視検査で確認可能な新規の半導体装置を提供することにある。

本発明の他の目的は、放熱性及び信頼性が高い新規な半導体装置を提供することにある。

本発明の他の目的は、放熱性が高い新規な半導体装置を提供することにある。

本発明の他の目的は、放熱性が高い電子装置を提供することにある。

本発明の前記並びにその他の目的と新規な特徴は、本明細書の記述及び添付図面によって明らかになるであろう。

(1)本発明の半導体装置は、互いに反対側に位置する第1及び第2の主面と、前記第1の主面に形成された第1の電極と、前記第2の主面に形成された第2の電極とを有する半導体チップと、

前記半導体チップを封止する樹脂封止体であって、互いに反対側に位置する第1及び第2の主面を有し、前記第1の主面が前記半導体チップの第1の主面側に位置し、前記第2の主面が前記半導体チップの第2の主面側に位置する樹脂封止体と、

一端側が前記半導体チップの第1の電極上に位置し、かつ前記半導体チップの第1の電極に第1の接続手段を介在して接続され、前記一端側と反対側の他端側が前記一端側よりも前記樹脂封止体の第2の主面側に位置し、かつ前記樹脂封止体から露出する第1の導電部材と、

前記半導体チップの第2の電極に第2の接続手段を介在して接続された第2の導電部材とを有し、

前記第1の導電部材の一端側は、前記樹脂封止体の第1の主面から露出し、

前記第2の導電部材は、前記樹脂封止体の第2の主面及び側面から露出している。

前記第1の導電部材の他端側は、前記樹脂封止体の第1の側面側に位置し、

前記第2の導電部材は、前記樹脂封止体の第1の側面と反対側の第2の側面から露出している。

前記半導体チップの第1の電極は、ソース電極であり、前記半導体チップの第2の電極は、ドレイン電極である。

若しくは、前記半導体チップの第1の電極は、ドレイン電極であり、前記半導体チップの第2の電極は、ソース電極である。

前記半導体チップを封止する樹脂封止体であって、互いに反対側に位置する第1及び第2の主面を有し、前記第1の主面が前記半導体チップの第1の主面側に位置し、前記第2の主面が前記半導体チップの第2の主面側に位置する樹脂封止体と、

前記前記半導体チップの第1の電極上に位置し、かつ半導体チップの第1の電極に第1の接続手段を介在して接続され、更に前記樹脂封止体の第1の主面から露出する第1の部分と、前記第1の部分と一体に形成され、かつ前記樹脂封止体の内部に位置する第2の部分と、前記第2の部分と一体に形成され、かつ前記樹脂封止体の第2の主面から露出する第3の部分とを有する第1の導電部材と、

前記半導体チップの第2の電極に第2の接続手段を介在して接続され、かつ前記樹脂封止体の第2の主面から露出する第2の導電部材とを有する。

前記第1の導電部材の第3の部分は、前記樹脂封止体の第1の側面から露出し、

前記第2の導電部材は、前記樹脂封止体の第1の側面と反対側の第2の側面から露出している。

前記半導体チップの第1の電極は、ソース電極であり、前記半導体チップの第2の電極は、ドレイン電極である

若しくは、前記半導体チップの第1の電極は、ドレイン電極であり、前記半導体チップの第2の電極は、ソース電極である。

前記半導体チップを封止する樹脂封止体であって、互いに反対側に位置する第1及び第2の主面を有し、前記第1の主面が前記半導体チップの第1の主面側に位置し、前記第2の主面が前記半導体チップの第2の主面側に位置する樹脂封止体と、

前記半導体チップの第1の電極に第1の接続手段を介在して接続された第1の部分と、前記第1の部分と一体に形成された第2の部分と、前記第2の部分と一体に形成され、かつ前記第1の部分よりも前記樹脂封止体の第2の主面側に位置する第3の部分とを有する第1の導電部材と、

前記半導体チップの第2の電極に第2の接続手段を介在して接続された第1の部分と、前記第1の部分と一体に形成された第2の部分と、前記第2の部分と一体に形成され、かつ前記第1の部分よりも前記樹脂封止体の第2の主面側に位置する第3の部分とを有する第2の導電部材と、

前記半導体チップの第3の電極に第3の接続手段を介在して接続され、かつ前記樹脂封止体の第2の主面から露出する第3の導電部材とを有し、

前記第1の導電部材の第1の部分は、前記樹脂封止体の第1の主面から露出し、

前記第2の導電部材の第1の部分は、前記樹脂封止体の内部に位置している。

前記第2の導電部材の第1の部分は、前記第1の導電部材の第1の部分よりも厚さが薄くなっている。

前記第1及び第2の導電部材の夫々の第2の部分は、前記樹脂封止体の内部に位置し、

前記第1及び第2の導電部材の夫々の第3の部分は、前記樹脂封止体の第2の主面から露出している。

前記第1及び第2の導電部材の夫々の第3の部分は、前記樹脂封止体の第1の側面から露出し、

前記第3の導電部材は、前記樹脂封止体の第1の側面と反対側の第2の側面から露出している。

前記半導体チップの第1の電極は、ソース電極であり、前記半導体チップの第2の電極は、ゲート電極であり、前記半導体チップの第3の電極は、ドレイン電極である。

若しくは、前記半導体チップの第1の電極は、ドレイン電極であり、前記半導体チップの第2の電極は、ゲート電極であり、前記半導体チップの第3の電極は、ソース電極である。

前記半導体チップを封止する樹脂封止体であって、互いに反対側に位置する第1及び第2の主面を有し、前記第1の主面が前記半導体チップの第1の主面側に位置し、前記第2の主面が前記半導体チップの第2の主面側に位置する樹脂封止体と、

前記半導体チップの第1の電極に第1の接続手段を介在して接続された第1の部分と、前記第1の部分と一体に形成された第2の部分と、前記第2の部分と一体に形成され、かつ前記第1の部分よりも前記樹脂封止体の第2の主面側に位置する第3の部分とを有する第1の導電部材と、

前記半導体チップの外側に位置し、かつ前記第1の導電部材の第1の部分よりも前記樹脂封止体の第2の主面側に位置する第2の導電部材と、

前記半導体チップの第3の電極に第2の接続手段を介在して接続され、かつ前記樹脂封止体の第2の主面から露出する第3の導電部材とを有し、

前記第1の導電部材の第1の部分は、前記樹脂封止体の第1の主面から露出し、

前記第2の導電部材は、ボンディングワイヤを介して前記半導体チップの第2の電極と電気的に接続されている。

前記第1の導電部材の第2の部分は、前記樹脂封止体の内部に位置し、

前記第1の導電部材の第3の部分、及び前記第2の導電部材は、前記樹脂封止体の第2の主面から露出している。

前記半導体チップを封止する樹脂封止体であって、互いに反対側に位置する第1及び第2の主面を有し、前記第1の主面が前記半導体チップの第1の主面側に位置し、前記第2の主面が前記半導体チップの第2の主面側に位置する樹脂封止体と、

前記半導体チップの第1の電極に第1の接続手段を介在して接続された第1の部分と、前記第1の部分と一体に形成された第2の部分と、前記第2の部分と一体に形成され、かつ前記第1の部分よりも前記樹脂封止体の第2の主面側に位置する第3の部分とを有する第1の導電部材と、

前記半導体チップの第2の電極に第2の接続手段を介在して接続された第1の部分と、前記第1の部分と一体に形成され、かつ前記第1の部分よりも厚さが厚い第2の部分とを有する第2の導電部材とを有し、

前記第2の導電部材の第1の部分は、前記樹脂封止体の第2の主面から露出し、

前記第2の導電部材の第2の部分は、前記樹脂封止体の第1及び第2の主面から露出している。

前記第2導電部材の第2の部分は、前記樹脂封止体の側面から露出している。

前記半導体チップの第1の電極は、ソース電極であり、前記半導体チップの第2の電極は、ドレイン電極である。

若しくは、前記半導体チップの第1の電極は、ドレイン電極であり、前記半導体チップの第2の電極は、ソース電極である。

前記半導体チップを封止する樹脂封止体であって、互いに反対側に位置する第1及び第2の主面を有し、前記第1の主面が前記半導体チップの第1の主面側に位置し、前記第2の主面が前記半導体チップの第2の主面側に位置する樹脂封止体と、

前記半導体チップの第1の電極に第1の接続手段を介在して接続された第1の部分と、前記第1の部分と一体に形成され、かつ前記第1の部分よりも厚さが厚い第2の部分とを有する第1の導電部材と、

前記半導体チップの第2の電極に第2の接続手段を介在して接続された第1の部分と、前記第1の部分と一体に形成され、かつ前記第1の部分よりも厚さが厚い第2の部分とを有する第2の導電部材とを備え、

前記第1の導電部材の第1の部分及び第2の部分は、前記樹脂封止体の第1の主面から露出し、

前記第1の導電部材の第2の部分は、前記樹脂封止体の第2の主面から露出し、

前記第2の導電部材の第1の部分は、前記樹脂封止体の内部に位置し、

前記第2の導電部材の第2の部分は、前記樹脂封止体の第2の主面から露出していることを特徴とする半導体装置。

前記第1導電部材の第2の部分は、前記樹脂封止体の側面から露出している。

前記半導体チップの第1の電極は、ドレイン電極であり、前記半導体チップの第2の電極は、ソース電極である。

若しくは、前記半導体チップの第1の電極は、ソース電極であり、前記半導体チップの第2の電極は、ドレイン電極である。

前記半導体装置は、互いに反対側に位置する第1及び第2の主面と、前記第1の主面に形成された第1及び第2の電極と、前記第2の主面に形成された第3の電極とを有する半導体チップと、

前記半導体チップを封止する樹脂封止体であって、互いに反対側に位置する第1及び第2の主面を有し、前記第1の主面が前記半導体チップの第1の主面側に位置し、前記第2の主面が前記半導体チップの第2の主面側に位置する樹脂封止体と、

前記半導体チップの第1の電極に第1の接続手段を介在して接続され、かつ前記樹脂封止体の第1の主面から露出する第1の部分と、前記第1の部分と一体に形成された第2の部分と、前記第2の部分と一体に形成され、かつ前記樹脂封止体の第2の主面から露出する第3の部分とを有する第1の導電部材と、

前記半導体チップの第2の電極に第2の接続手段を介在して接続され、かつ前記樹脂封止体の内部に位置する第1の部分と、前記第1の部分と一体に形成された第2の部分と、前記第2の部分と一体に形成され、かつ前記樹脂封止体の第2の主面から露出する第3の部分とを有する第2の導電部材と、

前記半導体チップの第3の電極に第3の接続手段を介在して接続され、かつ前記樹脂封止体の第2の主面から露出する第3の導電部材とを有し、

前記第1及び第2の導電部材の夫々の第3部分、並びに前記第3の導電部材は、前記配線基板の電極に半田付けされ、

前記第1の導電部材の第1の部分は、熱伝導部材を介在して前記放熱部材に連結されている。

本発明によれば、放熱性が高く、実装時の接続信頼性が高い新規な半導体装置を提供することができる。

本発明によれば、放熱性が高く、実装時の半田付け良否を目視検査で確認可能な新規の半導体装置を提供することができる。

本発明によれば、放熱性及び信頼性が高い新規の半導体装置を提供することができる。

本発明によれば、放熱性が高い新規の半導体装置を提供することができる。

本発明によれば、信頼性の高い電子装置を提供することができる。

(実施形態1)

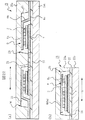

図1は、本発明の実施形態1であるパワートランジスタの外観を示す平面図(上面図)であり、

図2は、実施形態1のパワートランジスタ(半導体装置)の外観を示す底面図(下面図)であり、

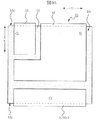

図3は、実施形態1のパワートランジスタの内部構造を示す平面図であり、

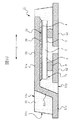

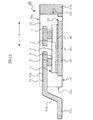

図4は、図3のa−a線に沿う拡大断面図であり、

図5は、図3のb−b線に沿う拡大断面図である。

図7は、図6(b)の一部を拡大した断面図であり、

図8は、図6(a)のb−b線に沿う拡大断面図であり、

図9は、図6のレギュレータの概略構成を示す等価回路図である。

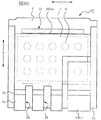

図11は、図10のリードフレームの一部を拡大した図((a)は平面図、(b)は(a)のa−a線に沿う断面図)であり、

図12は、図1のパワートランジスタの製造に使用されるヘッダの平面図である。

なお、図11(a)において、符号23は、半導体チップ2の搭載領域であり、符号24は、樹脂封止体11の形成領域である。

図14は、図13の半導体チップの底面図(下面図)である。

図17は、パワートランジスタの製造工程中における図((a)は平面図、(b)は(a)のa−a線に沿う断面図)であり、

図18は、パワートランジスタの製造工程中における図((a)は平面図、(b)は(a)のa−a線に沿う断面図)であり、

図19は、図18(b)の一部を拡大した断面図であり、

図20は、パワートランジスタの製造工程中における平面図であり、

図21は、パワートランジスタの製造工程中における図((a)は図20のa−a線に対応する位置での断面図、(b)は図20のb−b線に対応する位置での断面図)であり、

図22は、パワートランジスタの製造工程中における図((a)は図20のa−a線に対応する位置での断面図、(b)は図20のb−b線に対応する位置での断面図)であり、

図23は、パワートランジスタの製造工程中における平面図であり、

図24は、パワートランジスタの製造工程中における図((a)は平面図、(b)は(a)のa−a線に沿う断面図)である。

放熱性が高く、実装時の接続信頼性が高い新規なパワートランジスタ1Aを提供することができる。

放熱性が高く、実装時の半田付け良否を目視検査で確認可能な新規のパワートランジスタ1Aを提供することができる。

放熱性及び信頼性が高い新規のパワートランジスタ1Aを提供することができる。

放熱性が高く、薄型に好適な新規のパワートランジスタ1Aを提供することができる。

放熱性が高く、小型化に好適な新規のパワートランジスタ1Aを提供することができる。

熱に対する信頼性の高い新規のレギュレータ40Aを提供することができる。

図25は、本発明の実施形態1の変形例1であるレギュレータの概略構成を示す要部断面図である。

本変形例1のレギュレータ40Bは、図25に示すように、熱伝導部材として例えば半田材44aを使用し、パワートランジスタ1Aの樹脂封止体11の主面11xから露出するリード6の第1の部分6aが半田材44aによって放熱部材43に固着されている。

このように、半田材44aによってリード6の第1の部分6aと放熱部材43とを連結する時、リード8の第1の部分8aが樹脂封止体11の内部に位置しているため、マスクを用いて半田接続する必要がない。従って、レギュレータ40Bの製造コストを低くすることができる。

図26は、本発明の実施形態1の変形例2であるパワートランジスタの内部構造を示す図((a)は平面図、(b)は(a)のa−a線に沿う断面図)である。

本変形例2のパワートランジスタ1Bは、図26に示すように、リード6の第1の部分6aにスリット13を設けた構成になっている。スリット13は、リード6の第1の部分6aの上面からその反対側の下面に亘って貫通し、突起状電極9が接続される領域以外の部分に設けられている。本変形例2では、X方向に延びるストライプ状のスリット13が複数設けられている。

また、樹脂封止体11を形成する時、半導体チップ2の主面とリード6の第1の部分6aとの間に樹脂が入り込み易くなるため、ボイドの発生を抑制することができる。

図27は、本発明の実施形態1の変形例3であるパワートランジスタの内部構造を示す図((a)は平面図、(b)は(a)のa−a線に沿う断面図)である。

本変形例3のパワートランジスタ1Cは、リード6の第1の部分6aに溝14を設けた構成になっている。溝14は、リード6の第1の部分6aの下面(チップと向かい合う面)からその反対側の上面に向かって窪み、バンプ9が接続される領域以外の部分に設けられている。本変形例3では、X方向に延びるストライプ状の溝14が複数設けられている。

図28は、本発明の実施形態1の変形例4であるパワートランジスタの内部構造を示す図((a)は平面図、(b)は(a)のa−a線に沿う断面図)である。

本変形例4のパワートランジスタ1Dは、半導体チップ2のソース電極3とリード6の第1の部分6aと接続する接続手段として、導電性の接着材15(例えば半田材)を用いている。このような構成にすることにより、半導体チップ2のソース電極3とリード6の第1の部分6aとの間に樹脂封止体11の樹脂が介在される量が少なくなるため、更に放熱性を高めることができる。

図29は、本発明の実施形態1の変形例5であるパワートランジスタの内部構造を示す図((a)は平面図、(b)は(a)のa−a線に沿う断面図)である。

本変形例5のパワートランジスタ1Eは、リード16が半導体チップ2の外側に位置し、半導体チップ2のゲート電極5とリード16との電気的な接続がボンディングワイヤ17によって行われている。

リード16は、樹脂封止体11の主面11xよりもその裏面11y側に位置し、ワイヤが接続される面側が樹脂封止体11の樹脂によって覆われている。また、リード16は、リード6の第3の部分6cと同様に、樹脂封止体11の裏面11y及び第1の側面11zから露出している。

本変形例5においても、前述の実施形態1と同様の効果が得られる。

図30は、本発明の実施形態1の変形例6であるパワートランジスタの内部構造を示す平面図である。

本変形例6のパワートランジスタ1Fは、リード6に、その第3の部分6cの先端部からその第1の部分6aに向かって延びるスリット18が設けられている。本変形例6において、スリット18は2つ設けられ、第3の部分6cの先端部から第1の部分6aまで延びている。

このような構成にすることにより、低オン抵抗化及び放熱性の向上を図るため、リード6の幅を広くしても、リード6を折り曲げ成形する時の難易度を低くするこどできるため、リードの折り曲げ加工における生産性を高めることができる。

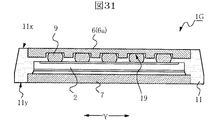

図31は、本発明の実施形態1の変形例7であるパワートランジスタの内部構造を示す断面図である。

本変形例7のパワートランジスタ1Gは、図31に示すように、リード6の第1の部分6aに溝19を設けた構成になっている。溝19は、リード6の第1の部分6aの下面(チップと向かい合う面)からその反対側の上面に向かって窪み、突起状電極9が接続される領域に設けられている。

本変形例7においても、前述の変形例3と同様の効果が得られる。また、突起状電極9の高さを溝19で相殺することができるため、パワートランジスタ1Gの薄型化を図ることができる。

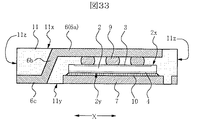

図32は、本発明の実施形態2であるパワートランジスタの外観を示す図((a)は平面図(上面図)、(b)は底面図(下面図))であり、

図33は、図32(a)のa−a線に沿う断面図である。

本実施形態2のパワートランジスタ1Hは、図32及び図33に示すように、樹脂封止体11の主面11xとその裏面11yとの大きさ及び形状がほぼ同一になっており、樹脂封止体11の側面11zがその主面11x及び裏面11yに対してほぼ直角となっている。このようなパワートランジスタ1Hは、複数の半導体チップ2を1つの樹脂封止体で一括して封止し、その後、半導体チップ2毎に樹脂封止体、リードフレーム及びヘッダをダイシングによって分割することで形成することができる。この場合においても、図32及び図33に示すように、リード6の第1の部分6aは樹脂封止体11の主面(上面)11xから露出し、リード6及び8の夫々の第3の部分(6c,8c)は樹脂封止体11の裏面(下面、実装面)11y及び第1の側面11zから露出し、ヘッダ7は、樹脂封止体11の裏面11y及び第2の側面11zから露出する。

このような本実施形態2のパワートランジスタ1Hにおいても、本発明を適用することができ、前述の実施形態1と同様の効果が得られる。

図34は、本発明の実施形態3であるパワートランジスタの外観を示す平面図(上面図)であり、

図35は、本発明の実施形態3であるパワートランジスタの外観を示す底面図(下面図)であり、

図36は、図34のa−a線に沿う拡大断面図であり、

図37は、図34のb−b線に沿う拡大断面図である。

また、実質上の活性領域となるソース及びゲート領域が形成された面側が下向きになっており、かつ、リード51によりチップ全面が覆われる構造になっているので、外部からの電磁波ノイズに対して強い構成になっている。

図38は、本発明の実施形態4であるパワートランジスタの外観を示す平面図(上面図)であり、

図39は、本発明の実施形態4であるパワートランジスタの外観を示す底面図(下面図)であり、

図40は、本発明の実施形態4であるパワートランジスタの内部構造を示す平面図であり、

図41は、図40のa−a線に沿う拡大断面図であり、

図42は、図40のb−b線に沿う拡大断面図である。

図38乃至図42に示すように、本実施形態4のパワートランジスタ1Kは、基本的に前述の実施形態1と同様の構成になっており、以下の構成が異なっている。

また、本実施形態4のヘッダ62は、第1の部分62aが樹脂封止体11の第1の側面11zを除いて樹脂封止体11の3つの側面(第2〜第4の側面)から露出しているため、更に放熱性を高めることができる。

図43は、本発明の実施形態5であるパワートランジスタの内部構造を示す平面図であり、

図44は、本発明の実施形態5であるパワートランジスタの内部構造を示す図((a)は図43のa−a線に沿う断面図、(b)は図43のb−b線に沿う断面図)である。

本実施形態5のパワートランジスタ1Lは、基本的に前述の実施形態4と同様の構成になっており、以下の構成が異なっている。

このような実施形態5のパワートランジスタ1Lにおいても、前述の実施形態1と同様の効果が得られる。

図45は、本発明の実施形態6であるパワートランジスタの外観を示す平面図であり、

図46は、本発明の実施形態6であるパワートランジスタの外観を示す底面図であり、

図47は、本発明の実施形態6であるパワートランジスタの内部構造を示す図((a)は図45のa−a線に沿う断面図、(b)は図45のb−b線に沿う断面図)である。

このように本実施形態6のパワートランジスタ1Mにおいても、前述の実施形態1と同様の効果が得られる。

2…半導体チップ、3…ソース電極、4…ドレイン電極、5…ゲート電極、

6,8…リード、7…ヘッダ、9…突起状電極、10…接着材、11…樹脂封止体、

12,13…スリット、14…溝、15…接着材、16…リード、17…ボンディングワイヤ、18…スリット、19…溝、

20…リードフレーム、21…フレーム本体、22…製品形成領域、

30…半導体ウエハ、31…チップ形成領域、32…ダイシング領域、33…溝、

40A,40B…レギュレータ(電子装置)、41…配線基板、42…半田材、42a…フィレット、43…放熱部材、44…熱伝導部材、

51,52,53,61,63…リード、62…ヘッダ。

Claims (14)

- (a)MISFETを含み、互いに反対側に位置する第1及び第2の主面と、前記第1の主面に形成された前記MISFETのドレイン電極と、前記第2の主面に形成された前記MISFETのゲート電極およびソース電極を有する半導体チップと、

(b)前記半導体チップを封止する樹脂封止体であって、上面、下面、前記上面と下面とに交差する第1の側面、および前記上面と下面とに交差し、前記第1の側面とは反対側に位置する第2の側面を有し、前記上面が前記半導体チップの第1の主面側に位置し、前記下面が前記半導体チップの第2の主面側に位置する樹脂封止体と、

(c)表面、前記表面とは反対側に位置する裏面、前記表面と裏面と交差する側面、を備え、その裏面が前記ドレイン電極と電気的に接続されたドレインリードと、

(d)表面、前記表面とは反対側に位置する裏面、前記表面と裏面と交差する側面、を備え、その表面が前記ゲート電極と電気的に接続されたゲートリードと、

(e)表面、前記表面とは反対側に位置する裏面、前記表面と裏面と交差する側面、を備え、その表面が前記ソース電極と電気的に接続されたソースリードと、を有し、

(f)前記ドレインリードは第1の部分、第2の部分、および第3の部分からなり、前記第1の部分の裏面は前記ドレイン電極上に位置し、かつ前記ドレイン電極と電気的に接続されており、前記第3の部分は前記半導体チップの第2の主面より下に位置し、前記第2の部分は前記第1の部分と第3の部分とを接続し、前記第1の部分の表面は、前記樹脂封止体の上面から露出し、前記第3の部分の裏面は、前記樹脂封止体の下面から一部が露出し、

(g)前記ゲートリードは前記ゲート電極の下に位置し、かつ前記ゲートリードの裏面は、前記樹脂封止体の下面から一部が露出し、

(h)前記ソースリードは前記ソース電極の下に位置し、前記ソースリードの裏面は、前記樹脂封止体の下面から一部が露出し、かつ前記ソースリードの裏面の一部、側面の一部、および上面の一部は、前記樹脂封止体の第2の側面から露出し、

(i)前記樹脂封止体の下面から露出した前記ドレインリードの第3の部分の裏面、前記ゲートリードの裏面、前記ソースリードの裏面、および前記樹脂封止体の前記第2の側面から露出した前記ソースリードの裏面は同一平面内にあって、平面視において前記半導体チップと重なっている前記樹脂封止体の下面から露出した前記ソースリードの裏面と前記樹脂封止体の前記第2の側面から露出した前記ソースリードの裏面とは、連続した一平面で構成されていることを特徴とする半導体装置。 - 請求項1に記載の半導体装置であって、

前記樹脂封止体の前記第2の側面から露出した前記ソースリードの裏面は、前記樹脂封止体の下面から露出した前記ソースリードの裏面が延在した面の一部であることを特徴とする半導体装置。 - 請求項1に記載の半導体装置であって、

前記ドレインリードの前記第3の部分の裏面の一部、側面の一部、および上面の一部は、前記樹脂封止体の前記第1の側面から露出していることを特徴とする半導体装置。 - 請求項1に記載の半導体装置であって、

前記ゲートリードの裏面の一部、側面の一部、および上面の一部は、前記樹脂封止体の前記第2の側面から露出していることを特徴とする半導体装置。 - 請求項1に記載の半導体装置であって、

前記ドレインリードの裏面は、導電性接着材を介して前記半導体チップの前記ドレイン電極と電気的に接続されていることを特徴とする半導体装置。 - 請求項1に記載の半導体装置であって、

前記ゲートリードの表面および前記ソースリードの表面は、突起状電極を介してそれぞれ前記半導体チップの前記ゲート電極および前記ソース電極に接続されていることを特徴とする半導体装置。 - 請求項6に記載の半導体装置であって、

前記突起状電極は金からなることを特徴とする半導体装置。 - 請求項1に記載の半導体装置であって、

前記ドレインリード、前記ゲートリード、および前記ソースリードは、銅からなることを特徴とする半導体装置。 - 請求項1に記載の半導体装置であって、

前記ドレインリードの前記第2の部分は前記樹脂封止体の内部に位置し、前記第1の側面からは露出していないことを特徴とする半導体装置。 - (a)MISFETを含み、互いに反対側に位置する第1及び第2の主面と、前記第1の主面に形成された前記MISFETのゲート電極およびソース電極と、前記第2の主面に形成された前記MISFETのドレイン電極を有する半導体チップと、

(b)前記半導体チップを封止する樹脂封止体であって、上面、下面、前記上面と下面とに交差する第1の側面、および前記上面と下面とに交差し、前記第1の側面とは反対側に位置する第2の側面を有し、前記上面が前記半導体チップの第1の主面側に位置し、前記下面が前記半導体チップの第2の主面側に位置する樹脂封止体と、

(c)表面、前記表面とは反対側に位置する裏面、前記表面と裏面と交差する側面、を備え、その表面が前記ドレイン電極と電気的に接続されたドレインリードと、

(d)表面、前記表面とは反対側に位置する裏面、前記表面と裏面と交差する側面、を備え、その裏面が前記ゲート電極と電気的に接続されたゲートリードと、

(e)表面、前記表面とは反対側に位置する裏面、前記表面と裏面と交差する側面、を備え、その裏面が前記ソース電極と電気的に接続されたソースリードと、を有し、

(f)前記ソースリードは第1の部分、第2の部分、および第3の部分からなり、前記第1の部分の裏面は前記ソース電極上に位置し、かつ前記ソース電極と電気的に接続されており、前記第3の部分は前記半導体チップの第2の主面より下に位置し、前記第2の部分は前記第1の部分と第3の部分とを接続し、前記第1の部分の表面は、前記樹脂封止体の上面から露出し、前記第3の部分の裏面は、前記樹脂封止体の下面から一部が露出し、

(g)前記ゲートリードは第1の部分、第2の部分、および第3の部分からなり、前記第1の部分の裏面は前記ゲート電極上に位置し、かつ前記ゲート電極と電気的に接続されており、前記第3の部分は前記半導体チップの第2の主面より下に位置し、前記第2の部分は前記第1の部分と第3の部分とを接続し、前記第1の部分の表面は、前記樹脂封止体により覆われており、前記第3の部分の裏面は、前記樹脂封止体の下面から一部が露出し、

(h)前記ドレインリードは前記ドレイン電極の下に位置し、前記ドレインリードの裏面は、前記樹脂封止体の下面から一部が露出し、かつ前記ドレインリードの裏面の一部、側面の一部、および上面の一部は、前記樹脂封止体の第2の側面から露出し、

(i)前記樹脂封止体の下面から露出した前記ドレインリードの裏面、前記ゲートリードの前記第3の部分の裏面、前記ソースリードの第3の部分の裏面、および前記樹脂封止体の前記第2の側面から露出した前記ドレインリードの裏面は同一平面内にあって、平面視において前記半導体チップと重なっている前記樹脂封止体の下面から露出した前記ドレインリードの裏面と前記樹脂封止体の前記第2の側面から露出した前記ドレインリードの裏面とは、連続した一平面で構成されていることを特徴とする半導体装置。 - 請求項10に記載の半導体装置であって、

前記樹脂封止体の前記第2の側面から露出した前記ドレインリードの裏面は、前記樹脂封止体の下面から露出した前記ドレインリードの裏面が延在した面の一部であることを特徴とする半導体装置。 - 請求項10に記載の半導体装置であって、

前記ソースリードの前記第3の部分の裏面の一部、側面の一部、および上面の一部は、前記樹脂封止体の前記第1の側面から露出していることを特徴とする半導体装置。 - 請求項10に記載の半導体装置であって、

前記ゲートリードの前記第3の部分の裏面の一部、側面の一部、および上面の一部は、前記樹脂封止体の前記第1の側面から露出していることを特徴とする半導体装置。 - 請求項10に記載の半導体装置であって、

前記ソースリードおよび前記ゲートリードの前記第2の部分は前記樹脂封止体の内部に位置し、前記第1の側面からは露出していないことを特徴とする半導体装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008075930A JP4804497B2 (ja) | 2008-03-24 | 2008-03-24 | 半導体装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008075930A JP4804497B2 (ja) | 2008-03-24 | 2008-03-24 | 半導体装置 |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2003054638A Division JP4173751B2 (ja) | 2003-02-28 | 2003-02-28 | 半導体装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2008160163A JP2008160163A (ja) | 2008-07-10 |

| JP2008160163A5 JP2008160163A5 (ja) | 2008-09-04 |

| JP4804497B2 true JP4804497B2 (ja) | 2011-11-02 |

Family

ID=39660648

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008075930A Expired - Lifetime JP4804497B2 (ja) | 2008-03-24 | 2008-03-24 | 半導体装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4804497B2 (ja) |

Families Citing this family (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN101752358B (zh) * | 2008-12-08 | 2012-07-04 | 万国半导体有限公司 | 带有整合旁路电容器的紧密半导体封装及其方法 |

| JP2010165923A (ja) * | 2009-01-16 | 2010-07-29 | Renesas Electronics Corp | 半導体装置、及びその製造方法 |

| JP5921072B2 (ja) * | 2011-03-05 | 2016-05-24 | 新電元工業株式会社 | 樹脂封止型半導体装置 |

| JP2017050489A (ja) * | 2015-09-04 | 2017-03-09 | 株式会社東芝 | 半導体パッケージおよび半導体パッケージの製造方法 |

| JP6967335B2 (ja) * | 2016-03-15 | 2021-11-17 | ローム株式会社 | 半導体装置 |

| JP6884723B2 (ja) * | 2018-03-23 | 2021-06-09 | 株式会社東芝 | 半導体装置 |

| JP7150461B2 (ja) * | 2018-04-24 | 2022-10-11 | ローム株式会社 | 半導体装置 |

| JP7419781B2 (ja) * | 2019-12-10 | 2024-01-23 | 富士電機株式会社 | 半導体モジュール |

| JP7337034B2 (ja) * | 2020-09-15 | 2023-09-01 | 三菱電機株式会社 | 半導体パッケージおよび半導体装置 |

| JP2025014423A (ja) * | 2023-07-18 | 2025-01-30 | 株式会社東芝 | 半導体装置 |

| JP2025086224A (ja) * | 2023-11-27 | 2025-06-06 | 株式会社日立製作所 | 電力変換装置 |

Family Cites Families (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6249041B1 (en) * | 1998-06-02 | 2001-06-19 | Siliconix Incorporated | IC chip package with directly connected leads |

| JP4260263B2 (ja) * | 1999-01-28 | 2009-04-30 | 株式会社ルネサステクノロジ | 半導体装置 |

| JP3639515B2 (ja) * | 2000-09-04 | 2005-04-20 | 三洋電機株式会社 | Mosfetの実装構造の製造方法 |

| JP3650008B2 (ja) * | 2000-09-04 | 2005-05-18 | 三洋電機株式会社 | Mosfetを用いた保護回路装置およびその製造方法 |

-

2008

- 2008-03-24 JP JP2008075930A patent/JP4804497B2/ja not_active Expired - Lifetime

Also Published As

| Publication number | Publication date |

|---|---|

| JP2008160163A (ja) | 2008-07-10 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4173751B2 (ja) | 半導体装置 | |

| JP4804497B2 (ja) | 半導体装置 | |

| US6521982B1 (en) | Packaging high power integrated circuit devices | |

| US8471373B2 (en) | Resin-sealed semiconductor device and method for fabricating the same | |

| US6479888B1 (en) | Semiconductor device and a method of manufacturing the same | |

| US8203848B2 (en) | Circuit device and method of manufacturing the same | |

| JP2005191240A (ja) | 半導体装置及びその製造方法 | |

| JP2009534869A (ja) | マルチプルダイおよび共通ノード構造を含む半導体ダイパッケージ | |

| JP2005051130A (ja) | リードレスパッケージ型半導体装置とその製造方法 | |

| JP2001332687A (ja) | 半導体装置及びその製造方法 | |

| JP2022143169A (ja) | 半導体装置 | |

| JP2022143166A (ja) | 半導体装置 | |

| JP4100332B2 (ja) | 電子装置およびその製造方法 | |

| JP2008153432A (ja) | 半導体装置およびその製造方法 | |

| JP7594950B2 (ja) | 半導体装置 | |

| JP2019091922A (ja) | 半導体装置 | |

| CN110892526B (zh) | 半导体装置的制造方法 | |

| JP2022143167A (ja) | 半導体装置 | |

| JP5444299B2 (ja) | 半導体装置 | |

| JP4353935B2 (ja) | リードレスパッケージ型半導体装置 | |

| JP2013187268A (ja) | 半導体モジュール | |

| JP5017228B2 (ja) | 半導体装置 | |

| JP2019110278A (ja) | 半導体装置 | |

| JP2004172448A (ja) | 半導体装置 | |

| JP2003188335A (ja) | 半導体装置及びその製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080723 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20100511 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20101116 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110117 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20110809 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20110809 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4804497 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140819 Year of fee payment: 3 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| EXPY | Cancellation because of completion of term |