JP4771535B2 - 撮像装置及び制御方法 - Google Patents

撮像装置及び制御方法 Download PDFInfo

- Publication number

- JP4771535B2 JP4771535B2 JP2006122532A JP2006122532A JP4771535B2 JP 4771535 B2 JP4771535 B2 JP 4771535B2 JP 2006122532 A JP2006122532 A JP 2006122532A JP 2006122532 A JP2006122532 A JP 2006122532A JP 4771535 B2 JP4771535 B2 JP 4771535B2

- Authority

- JP

- Japan

- Prior art keywords

- signal

- photoelectric conversion

- unit

- clamp circuit

- circuit

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

- H04N25/50—Control of the SSIS exposure

- H04N25/53—Control of the integration time

- H04N25/531—Control of the integration time by controlling rolling shutters in CMOS SSIS

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

- H04N25/60—Noise processing, e.g. detecting, correcting, reducing or removing noise

- H04N25/616—Noise processing, e.g. detecting, correcting, reducing or removing noise involving a correlated sampling function, e.g. correlated double sampling [CDS] or triple sampling

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

- H04N25/60—Noise processing, e.g. detecting, correcting, reducing or removing noise

- H04N25/67—Noise processing, e.g. detecting, correcting, reducing or removing noise applied to fixed-pattern noise, e.g. non-uniformity of response

Description

102、802 フォトダイオード

103、803 転送スイッチ

104、804 蓄積領域

105、805 増幅MOSアンプ

106、806 選択スイッチ

107、807 リセットスイッチ

108、808 信号線

109、809 定電流源

110、810 水平走査回路

111、811 読み出し回路

112、812 出力線

113、813 垂直走査回路

201 レンズ部

202 レンズ駆動装置

203 シャッタ

204 シャッタ駆動装置

205 撮像素子

206 撮像信号処理回路

207 タイミング発生部

208 メモリ部

209 制御回路

210 記録媒体制御I/F部

211 記録媒体

212 外部I/F部

213 測光装置

214 測距装置

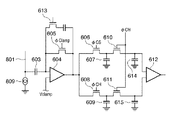

603 クランプ容量

604 増幅アンプ

605 クランプスイッチ

606 光信号選択スイッチ

607 光信号保持容量

608 リセットレベル選択スイッチ

609 リセットレベル保持容量

610、611 列選択スイッチ

612 差動アンプ

613 ゲイン切り替えスイッチ

614、615 寄生容量

814 ダミー画素

901 ダミー画素フォトダイオード

902 ダミー画素転送スイッチ

903 ダミー画素蓄積領域

904 ダミー画素増幅MOSアンプ

905 ダミー画素選択スイッチ

906 ダミー画素リセットスイッチ

Claims (9)

- それぞれが、受光量に応じて光電変換信号を出力する光電変換部を含む、2次元に配置された複数の画素と、

クランプ回路を含む出力部と、

前記クランプ回路に基準信号を出力する信号供給回路と、

前記画素からの前記光電変換信号を含む信号を前記クランプ回路へ出力するのに先だって、前記基準信号をクランプし、その後、前記光電変換信号を含む信号を前記クランプ回路に出力し、その後、前記画素のノイズ信号を前記クランプ回路へ出力する第1の制御を行う制御部と、

前記クランプ回路によって処理された前記光電変換信号を含む信号と前記ノイズ信号との差分処理を行う差分回路と

を有することを特徴とする撮像装置。 - 前記撮像装置は、第1の走査方法と第2の走査方法とを含む複数の走査方法により駆動可能であって、

前記制御部は、前記第1の走査方法では、前記画素からのノイズ信号を前記クランプ回路でクランプし、その後、前記光電変換信号を前記クランプ回路に出力する第2の制御を行い、前記第2の走査方法では、前記第1の制御を行うことを特徴とする請求項1に記載の撮像装置。 - 前記出力部は、前記クランプ回路の出力を増幅して出力するアンプを更に有することを特徴とする請求項1または2に記載の撮像装置。

- 前記複数の画素の各々は、さらに、信号を保持する保持部と、前記光電変換部から前記光電変換信号を前記保持部に転送する転送スイッチと、前記保持部に保持された信号を増幅して出力する増幅部と、前記保持部をリセットするためのリセットスイッチとを有し、

前記ノイズ信号は、前記保持部をリセットした時に、前記増幅部を介して読み出された信号であることを特徴とする請求項1乃至3のいずれか1項に記載の撮像装置。 - 前記複数の画素の各々は、さらに、信号を保持する保持部と、前記光電変換部から前記光電変換信号を前記保持部に転送する転送スイッチとを有し、

前記制御部は、さらに、前記複数の画素の前記光電変換信号を前記保持部に同じタイミングで転送し、その後、予め設定された数のライン毎に前記保持部に保持された信号を前記画素から順次読み出すように駆動するか、若しくは、前記光電変換信号を予め設定された数のライン毎に前記保持部に第1周期で順次転送し、その後、予め設定された数のライン毎に前記保持部に保持された信号を前記画素から第2周期で順次読み出すように制御し、

前記第1周期は、前記第2周期よりも短いことを特徴とする請求項1に記載の撮像装置。 - 静止画撮影を行う場合には前記第1の走査方法により、動画撮影を行う場合には、前記第2の走査方法により駆動されることを特徴とする請求項2に記載の撮像装置。

- 前記複数の画素の各々は、さらに、信号を保持する保持部と、前記光電変換部から前記光電変換信号を前記保持部に転送する転送スイッチとを有し、

前記制御部は、さらに、前記第1の走査方法では、前記光電変換信号を前記保持部に転送し、その後、前記保持部に保持された信号を前記画素から読み出す動作を、予め設定された数のライン毎に順次行い、前記第2の走査方法では、前記複数の画素の前記光電変換信号を前記保持部に同じタイミングで転送し、その後、予め設定された数のライン毎に前記保持部に保持された信号を前記画素から順次読み出すように駆動するか、若しくは、前記光電変換信号を予め設定された数の所定ライン毎に前記保持部に第1周期で順次転送し、その後予め設定された数のライン毎に前記保持部に保持された信号を前記画素から第2周期で順次読み出すように制御し、

前記第1周期は、前記第2周期よりも短いことを特徴とする請求項2に記載の撮像装置。 - メカシャッタと、

静止画撮影の際に前記第1の走査方法を行い、動画撮影の際に前記第2の走査方法を行うように駆動を切り替える切り替え部とを有し、

前記制御部は、前記第1の走査方法では、前記メカシャッタが閉じられた後に制御を行い、前記第2の走査方法では、前記メカシャッタを開いたまま、制御を行うことを特徴とする請求項7に記載の撮像装置。 - それぞれが、受光量に応じて光電変換信号を出力する光電変換部を含む、2次元に配置された複数の画素と、クランプ回路を含む出力部と、前記クランプ回路に基準信号を出力する信号供給回路とを有する撮像装置の制御方法であって、

前記画素からの前記光電変換信号を含む信号を前記クランプ回路へ出力するのに先だって、前記基準信号をクランプするステップと、

前記光電変換信号を含む信号を前記クランプ回路に出力するステップと、

前記ノイズ信号を前記クランプ回路へ出力するステップと、

前記クランプ回路によって処理された前記光電変換信号を含む信号と前記ノイズ信号との差分処理を行うステップと

を有することを特徴とする制御方法。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2006122532A JP4771535B2 (ja) | 2005-05-17 | 2006-04-26 | 撮像装置及び制御方法 |

| US11/436,795 US8115837B2 (en) | 2005-05-17 | 2006-05-17 | Image sensing device using a photoelectric converter and a control method therefor |

| US13/359,002 US8982252B2 (en) | 2005-05-17 | 2012-01-26 | Image sensing device using a photoelectric converter and a control method therefor |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005144539 | 2005-05-17 | ||

| JP2005144539 | 2005-05-17 | ||

| JP2006122532A JP4771535B2 (ja) | 2005-05-17 | 2006-04-26 | 撮像装置及び制御方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2006352843A JP2006352843A (ja) | 2006-12-28 |

| JP2006352843A5 JP2006352843A5 (ja) | 2009-06-18 |

| JP4771535B2 true JP4771535B2 (ja) | 2011-09-14 |

Family

ID=37447951

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2006122532A Expired - Fee Related JP4771535B2 (ja) | 2005-05-17 | 2006-04-26 | 撮像装置及び制御方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (2) | US8115837B2 (ja) |

| JP (1) | JP4771535B2 (ja) |

Families Citing this family (38)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4243870B2 (ja) * | 2007-02-08 | 2009-03-25 | ソニー株式会社 | 固体撮像装置及び撮像装置 |

| US8289430B2 (en) * | 2007-02-09 | 2012-10-16 | Gentex Corporation | High dynamic range imaging device |

| JP5105907B2 (ja) | 2007-03-06 | 2012-12-26 | キヤノン株式会社 | 撮像システム |

| JP4958666B2 (ja) * | 2007-07-12 | 2012-06-20 | キヤノン株式会社 | 撮像装置及びその制御方法 |

| JP5142749B2 (ja) * | 2008-02-14 | 2013-02-13 | キヤノン株式会社 | 撮像装置、撮像装置の制御方法及び撮像システム |

| JP5089514B2 (ja) * | 2008-07-11 | 2012-12-05 | キヤノン株式会社 | 撮像装置、及び撮像システム |

| JP2010062639A (ja) | 2008-09-01 | 2010-03-18 | Canon Inc | 撮像装置 |

| JPWO2010023903A1 (ja) * | 2008-09-01 | 2012-01-26 | 株式会社ニコン | 撮像素子および撮像装置 |

| JP2010093498A (ja) * | 2008-10-07 | 2010-04-22 | Olympus Corp | 固体撮像装置 |

| JP5355026B2 (ja) * | 2008-10-09 | 2013-11-27 | キヤノン株式会社 | 撮像装置 |

| JP5402349B2 (ja) | 2009-07-23 | 2014-01-29 | ソニー株式会社 | 固体撮像装置とその駆動方法、及び電子機器 |

| US8169526B2 (en) * | 2009-08-28 | 2012-05-01 | Naoki Ozawa | Low noise signal reproducing method for a solid state imaging device |

| JP5434485B2 (ja) | 2009-11-02 | 2014-03-05 | ソニー株式会社 | 固体撮像素子、固体撮像素子の駆動方法、およびカメラシステム |

| JP5403369B2 (ja) | 2010-03-31 | 2014-01-29 | ソニー株式会社 | 固体撮像素子および駆動方法、並びに電子機器 |

| JP2011259407A (ja) * | 2010-05-13 | 2011-12-22 | Sony Corp | 信号処理回路、固体撮像素子およびカメラシステム |

| JP5721405B2 (ja) * | 2010-11-22 | 2015-05-20 | キヤノン株式会社 | 撮像システム、その制御方法及びプログラム |

| KR101241704B1 (ko) * | 2011-04-14 | 2013-03-19 | 엘지이노텍 주식회사 | 픽셀, 픽셀 어레이, 이를 포함하는 이미지센서 및 그 구동방법 |

| CN103137026B (zh) * | 2011-11-29 | 2015-06-03 | 联想(北京)有限公司 | 一种电子设备及其成像方法 |

| JP5963448B2 (ja) * | 2012-01-13 | 2016-08-03 | キヤノン株式会社 | 撮像装置 |

| US8890996B2 (en) * | 2012-05-17 | 2014-11-18 | Panasonic Corporation | Imaging device, semiconductor integrated circuit and imaging method |

| JP2014039159A (ja) * | 2012-08-16 | 2014-02-27 | Sony Corp | 固体撮像装置および駆動方法、並びに電子機器 |

| JP6261162B2 (ja) * | 2012-10-02 | 2018-01-17 | キヤノン株式会社 | 撮像装置、撮像装置の駆動方法 |

| WO2014068837A1 (ja) * | 2012-10-30 | 2014-05-08 | パナソニック株式会社 | 撮像装置及びその駆動方法 |

| JP5726244B2 (ja) * | 2013-07-23 | 2015-05-27 | キヤノン株式会社 | 撮像装置及び撮像方法 |

| JP5886806B2 (ja) | 2013-09-17 | 2016-03-16 | キヤノン株式会社 | 固体撮像装置 |

| JP5652532B2 (ja) * | 2013-10-31 | 2015-01-14 | ソニー株式会社 | 固体撮像素子および駆動方法、並びに電子機器 |

| JP5672363B2 (ja) * | 2013-12-12 | 2015-02-18 | ソニー株式会社 | 固体撮像素子およびカメラシステム |

| JP2016201649A (ja) * | 2015-04-09 | 2016-12-01 | キヤノン株式会社 | 撮像装置、撮像システム、および撮像装置の駆動方法 |

| JP6439563B2 (ja) * | 2015-04-16 | 2018-12-19 | ソニー株式会社 | 撮像装置、撮像方法、プログラム |

| WO2017169883A1 (ja) * | 2016-03-31 | 2017-10-05 | ソニー株式会社 | 固体撮像素子、および電子機器 |

| JP2018013422A (ja) * | 2016-07-21 | 2018-01-25 | ソニーセミコンダクタソリューションズ株式会社 | 検出装置及び電子機器 |

| WO2018124044A1 (ja) * | 2016-12-27 | 2018-07-05 | パナソニックIpマネジメント株式会社 | 撮像素子、撮像装置、カメラ、及び撮像方法 |

| JP6887856B2 (ja) * | 2017-04-11 | 2021-06-16 | ソニーセミコンダクタソリューションズ株式会社 | 固体撮像装置 |

| US10165210B1 (en) * | 2017-12-22 | 2018-12-25 | Omnivision Technologies, Inc. | Bitline settling improvement by using dummy pixels for clamp |

| US10623728B2 (en) * | 2018-07-06 | 2020-04-14 | Stmicroelectronics (Grenoble 2) Sas | Image sensors for advanced driver assistance systems utilizing safety pixels to detect malfunctions |

| CN110501691B (zh) * | 2019-08-13 | 2022-03-08 | Oppo广东移动通信有限公司 | Tof模组的噪声滤除方法、tof模组及装置 |

| CN110809883B (zh) * | 2019-09-25 | 2021-12-21 | 深圳市汇顶科技股份有限公司 | 电子装置、图像传感器及其像素阵列和操作方法 |

| CN115004689A (zh) * | 2020-01-31 | 2022-09-02 | 索尼半导体解决方案公司 | 固态成像元件和成像装置 |

Family Cites Families (14)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3612803B2 (ja) * | 1995-07-10 | 2005-01-19 | ソニー株式会社 | 固体撮像装置及び固体撮像素子の出力信号処理方法 |

| JP3774499B2 (ja) * | 1996-01-24 | 2006-05-17 | キヤノン株式会社 | 光電変換装置 |

| US6850278B1 (en) * | 1998-11-27 | 2005-02-01 | Canon Kabushiki Kaisha | Solid-state image pickup apparatus |

| JP2001024949A (ja) * | 1999-07-08 | 2001-01-26 | Canon Inc | 固体撮像装置及びそれを用いた撮像システム |

| JP4011818B2 (ja) * | 2000-02-29 | 2007-11-21 | キヤノン株式会社 | 半導体固体撮像装置 |

| EP1143706A3 (en) * | 2000-03-28 | 2007-08-01 | Fujitsu Limited | Image sensor with black level control and low power consumption |

| JP3667214B2 (ja) * | 2000-08-25 | 2005-07-06 | キヤノン株式会社 | 固体撮像装置およびその駆動方法 |

| US7586526B2 (en) * | 2001-03-29 | 2009-09-08 | Canon Kabushiki Kaisha | Image sensing apparatus with at least two transfer speeds and its control method |

| JP2003017677A (ja) | 2001-06-28 | 2003-01-17 | Canon Inc | 撮像装置 |

| US7365785B2 (en) * | 2002-10-11 | 2008-04-29 | Olympus Corporation | Electronic camera |

| JP4154268B2 (ja) * | 2003-03-27 | 2008-09-24 | キヤノン株式会社 | 撮像装置 |

| US20050243193A1 (en) * | 2004-04-30 | 2005-11-03 | Bob Gove | Suppression of row-wise noise in an imager |

| US7701493B2 (en) * | 2005-02-28 | 2010-04-20 | Micron Technology, Inc. | Imager row-wise noise correction |

| JP2006352758A (ja) * | 2005-06-20 | 2006-12-28 | Pentax Corp | 画像信号処理装置 |

-

2006

- 2006-04-26 JP JP2006122532A patent/JP4771535B2/ja not_active Expired - Fee Related

- 2006-05-17 US US11/436,795 patent/US8115837B2/en not_active Expired - Fee Related

-

2012

- 2012-01-26 US US13/359,002 patent/US8982252B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| US8982252B2 (en) | 2015-03-17 |

| JP2006352843A (ja) | 2006-12-28 |

| US20060262209A1 (en) | 2006-11-23 |

| US8115837B2 (en) | 2012-02-14 |

| US20120126097A1 (en) | 2012-05-24 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4771535B2 (ja) | 撮像装置及び制御方法 | |

| JP4455215B2 (ja) | 撮像装置 | |

| US10038868B2 (en) | Solid-state image sensing device and electronic device | |

| JP5458582B2 (ja) | 固体撮像装置、固体撮像装置の駆動方法および電子機器 | |

| JP6120091B2 (ja) | 固体撮像素子および駆動方法、並びに電子機器 | |

| JP4609092B2 (ja) | 物理情報取得方法および物理情報取得装置 | |

| JP5630991B2 (ja) | 撮像装置 | |

| JP3814609B2 (ja) | 撮像装置、及び撮像装置の駆動方法 | |

| JP2012257095A (ja) | 固体撮像装置、撮像装置、および信号読み出し方法 | |

| JP6872956B2 (ja) | 撮像システム及び撮像システムの制御方法 | |

| JP2010062638A (ja) | 撮像装置 | |

| US8629923B2 (en) | Solid-state imaging element and camera system that determine in which horizontal read period a dummy pixel section is to be shuttered | |

| JP2007243731A (ja) | シフトレジスタ、固体撮像素子及び制御方法 | |

| JP2006203775A (ja) | 固体撮像素子の駆動方法、その撮像素子を用いた撮像装置およびシステム | |

| JP2008300898A (ja) | 固体撮像装置とそれを用いた撮像システム | |

| JP2006033381A (ja) | 撮像装置及び制御方法 | |

| JP2006108889A (ja) | 固体撮像装置 | |

| JP6049304B2 (ja) | 固体撮像装置および撮像装置 | |

| JP2007143067A (ja) | 撮像装置及び撮像システム | |

| JP2006093815A (ja) | 撮像装置 | |

| JP2013197697A (ja) | 固体撮像装置及び電子機器 | |

| JP6053321B2 (ja) | 固体撮像装置 | |

| JP2013106231A (ja) | 撮像装置 | |

| JP5306906B2 (ja) | 固体撮像装置、固体撮像装置の駆動方法および電子機器 | |

| JP2009124239A (ja) | 撮像装置及びそのフリッカ検出方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090424 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20090424 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20110610 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20110617 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20110620 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140701 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| LAPS | Cancellation because of no payment of annual fees |