JP4546117B2 - 不揮発性半導体記憶装置 - Google Patents

不揮発性半導体記憶装置 Download PDFInfo

- Publication number

- JP4546117B2 JP4546117B2 JP2004066767A JP2004066767A JP4546117B2 JP 4546117 B2 JP4546117 B2 JP 4546117B2 JP 2004066767 A JP2004066767 A JP 2004066767A JP 2004066767 A JP2004066767 A JP 2004066767A JP 4546117 B2 JP4546117 B2 JP 4546117B2

- Authority

- JP

- Japan

- Prior art keywords

- film

- gate

- side wall

- insulating film

- potential barrier

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000004065 semiconductor Substances 0.000 title claims description 79

- 239000000758 substrate Substances 0.000 claims description 78

- 238000005036 potential barrier Methods 0.000 claims description 60

- 238000002347 injection Methods 0.000 claims description 18

- 239000007924 injection Substances 0.000 claims description 18

- 230000005641 tunneling Effects 0.000 claims description 4

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 claims description 2

- 229910052710 silicon Inorganic materials 0.000 claims description 2

- 239000010703 silicon Substances 0.000 claims description 2

- 229910052581 Si3N4 Inorganic materials 0.000 claims 8

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 claims 8

- 239000010408 film Substances 0.000 description 433

- 150000004767 nitrides Chemical class 0.000 description 123

- 238000000034 method Methods 0.000 description 63

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 39

- 230000003647 oxidation Effects 0.000 description 33

- 238000007254 oxidation reaction Methods 0.000 description 33

- 239000004020 conductor Substances 0.000 description 31

- 239000010410 layer Substances 0.000 description 28

- 238000004519 manufacturing process Methods 0.000 description 24

- LPQOADBMXVRBNX-UHFFFAOYSA-N ac1ldcw0 Chemical compound Cl.C1CN(C)CCN1C1=C(F)C=C2C(=O)C(C(O)=O)=CN3CCSC1=C32 LPQOADBMXVRBNX-UHFFFAOYSA-N 0.000 description 18

- 238000004544 sputter deposition Methods 0.000 description 15

- 230000014759 maintenance of location Effects 0.000 description 14

- 238000009792 diffusion process Methods 0.000 description 11

- 239000007789 gas Substances 0.000 description 11

- 239000002784 hot electron Substances 0.000 description 11

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 9

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 8

- 230000015572 biosynthetic process Effects 0.000 description 8

- 238000000151 deposition Methods 0.000 description 8

- 229910052698 phosphorus Inorganic materials 0.000 description 8

- 239000011574 phosphorus Substances 0.000 description 8

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 7

- 230000007423 decrease Effects 0.000 description 7

- 238000001312 dry etching Methods 0.000 description 7

- 230000008569 process Effects 0.000 description 7

- 230000008021 deposition Effects 0.000 description 6

- 230000005684 electric field Effects 0.000 description 6

- 150000002500 ions Chemical class 0.000 description 6

- 238000010586 diagram Methods 0.000 description 5

- 238000004518 low pressure chemical vapour deposition Methods 0.000 description 5

- 238000005546 reactive sputtering Methods 0.000 description 5

- 230000002441 reversible effect Effects 0.000 description 5

- 238000002230 thermal chemical vapour deposition Methods 0.000 description 5

- QGZKDVFQNNGYKY-UHFFFAOYSA-N Ammonia Chemical compound N QGZKDVFQNNGYKY-UHFFFAOYSA-N 0.000 description 4

- KRHYYFGTRYWZRS-UHFFFAOYSA-N Fluorane Chemical compound F KRHYYFGTRYWZRS-UHFFFAOYSA-N 0.000 description 4

- MWUXSHHQAYIFBG-UHFFFAOYSA-N Nitric oxide Chemical compound O=[N] MWUXSHHQAYIFBG-UHFFFAOYSA-N 0.000 description 4

- 230000005284 excitation Effects 0.000 description 4

- 230000006872 improvement Effects 0.000 description 4

- 238000003860 storage Methods 0.000 description 4

- 238000011282 treatment Methods 0.000 description 4

- 238000009279 wet oxidation reaction Methods 0.000 description 4

- 238000005229 chemical vapour deposition Methods 0.000 description 3

- 230000007547 defect Effects 0.000 description 3

- 230000006866 deterioration Effects 0.000 description 3

- 230000000694 effects Effects 0.000 description 3

- 238000002955 isolation Methods 0.000 description 3

- 229910052757 nitrogen Inorganic materials 0.000 description 3

- 238000000059 patterning Methods 0.000 description 3

- 238000004904 shortening Methods 0.000 description 3

- 125000006850 spacer group Chemical group 0.000 description 3

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 2

- GQPLMRYTRLFLPF-UHFFFAOYSA-N Nitrous Oxide Chemical compound [O-][N+]#N GQPLMRYTRLFLPF-UHFFFAOYSA-N 0.000 description 2

- CBENFWSGALASAD-UHFFFAOYSA-N Ozone Chemical compound [O-][O+]=O CBENFWSGALASAD-UHFFFAOYSA-N 0.000 description 2

- BLRPTPMANUNPDV-UHFFFAOYSA-N Silane Chemical compound [SiH4] BLRPTPMANUNPDV-UHFFFAOYSA-N 0.000 description 2

- 229910021529 ammonia Inorganic materials 0.000 description 2

- BUMGIEFFCMBQDG-UHFFFAOYSA-N dichlorosilicon Chemical compound Cl[Si]Cl BUMGIEFFCMBQDG-UHFFFAOYSA-N 0.000 description 2

- 238000005530 etching Methods 0.000 description 2

- 239000012535 impurity Substances 0.000 description 2

- 238000005468 ion implantation Methods 0.000 description 2

- 238000001459 lithography Methods 0.000 description 2

- 230000001590 oxidative effect Effects 0.000 description 2

- 238000002294 plasma sputter deposition Methods 0.000 description 2

- 238000000926 separation method Methods 0.000 description 2

- 239000000126 substance Substances 0.000 description 2

- 239000010409 thin film Substances 0.000 description 2

- 229910007991 Si-N Inorganic materials 0.000 description 1

- 229910006294 Si—N Inorganic materials 0.000 description 1

- 230000002411 adverse Effects 0.000 description 1

- 239000007864 aqueous solution Substances 0.000 description 1

- 229910052786 argon Inorganic materials 0.000 description 1

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 1

- 229910001873 dinitrogen Inorganic materials 0.000 description 1

- PZPGRFITIJYNEJ-UHFFFAOYSA-N disilane Chemical compound [SiH3][SiH3] PZPGRFITIJYNEJ-UHFFFAOYSA-N 0.000 description 1

- 238000009826 distribution Methods 0.000 description 1

- 230000009977 dual effect Effects 0.000 description 1

- 230000006870 function Effects 0.000 description 1

- 238000010438 heat treatment Methods 0.000 description 1

- 238000011065 in-situ storage Methods 0.000 description 1

- 238000009413 insulation Methods 0.000 description 1

- 230000010354 integration Effects 0.000 description 1

- 239000011229 interlayer Substances 0.000 description 1

- 238000005259 measurement Methods 0.000 description 1

- 239000012528 membrane Substances 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 229910021421 monocrystalline silicon Inorganic materials 0.000 description 1

- 239000001272 nitrous oxide Substances 0.000 description 1

- 239000001301 oxygen Substances 0.000 description 1

- 229910052760 oxygen Inorganic materials 0.000 description 1

- 230000002093 peripheral effect Effects 0.000 description 1

- 239000002994 raw material Substances 0.000 description 1

- 230000003252 repetitive effect Effects 0.000 description 1

- 230000004044 response Effects 0.000 description 1

- 239000000243 solution Substances 0.000 description 1

- 238000003892 spreading Methods 0.000 description 1

- 230000007480 spreading Effects 0.000 description 1

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B43/00—EEPROM devices comprising charge-trapping gate insulators

- H10B43/30—EEPROM devices comprising charge-trapping gate insulators characterised by the memory core region

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/401—Multistep manufacturing processes

- H01L29/4011—Multistep manufacturing processes for data storage electrodes

- H01L29/40117—Multistep manufacturing processes for data storage electrodes the electrodes comprising a charge-trapping insulator

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/792—Field effect transistors with field effect produced by an insulated gate with charge trapping gate insulator, e.g. MNOS-memory transistors

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Physics & Mathematics (AREA)

- Ceramic Engineering (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Manufacturing & Machinery (AREA)

- Semiconductor Memories (AREA)

- Non-Volatile Memory (AREA)

- Read Only Memory (AREA)

Description

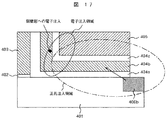

すなわち、本発明の第1の構造例による不揮発性半導体記憶装置の特徴は、

(a)半導体基板501中に形成された第1半導体領域(ソース)506aおよび第2半導体領域(ドレイン)506bと、

(b)前記第1半導体領域506aおよび第2半導体領域506b間上の前記半導体基板501の上部に形成された第1導電体(選択ゲートSG)503および第2導電体(メモリゲートMG)505と、

(c)前記第1導電体503と前記半導体基板501との間に形成された第1絶縁膜502と、

(d)前記第2導電体505と前記半導体基板501との間に形成された3層の第2絶縁膜(Si酸化膜504a/Si窒化膜504b/Si酸化膜504c)504と、

(e)前記第1導電体503と前記第2導電体との間に形成された2層の第2絶縁膜(Si酸化膜504a/Si酸化膜504c)504を有し、

(f)前記第2導電体505と前記半導体基板501との間に形成された3層の第2絶縁膜504は、前記半導体基板501上の電位障壁膜(Si酸化膜)504aと、その上部のSi窒化膜504bと、その上部の電位障壁膜(Si酸化膜)504cよりなり、

(g)前記第1導電体(SG)503と前記第2導電体(MG)505との間に形成された2層の第2絶縁膜504は、電位障壁膜(Si酸化膜)504aと、その上部の電位障壁膜(Si酸化膜)504cとからなる構造としたことである。

すなわち、本発明の第2の構造例による不揮発性半導体記憶装置の特徴は、

(a)半導体基板601中に形成された第1半導体領域(ソース)606aおよび第2半導体領域(ドレイン)606bと、

(b)前記第1半導体領域606aおよび第2半導体領域606b間上の前記半導体基板601の上部に形成された第1導電体(選択ゲートSG)603および第2導電体(メモリゲートMG)605と、

(c)前記第1導電体603と前記半導体基板601との間に形成された第1絶縁膜602と、

(d)前記第2導電体605と前記半導体基板601との間、及び前記第1導電体(SG)603と前記第2導電体(MG)605との間に形成された3層の第2絶縁膜(Si酸化膜604a/Si窒化膜604b及び604'b/Si酸化膜604c)604を有し、

前記第2導電体605と前記半導体基板601との間の前記第2絶縁膜604は、電位障壁膜(Si酸化膜)604aと、その上部のSi窒化膜(電荷保持膜)604bと、その上部の電位障壁膜(Si酸化膜)604cとよりなり、

前記第1導電体(SG)603の側壁部に位置するSi窒化膜604'bのSi基板601に近い側の少なくとも一部が、上記Si窒化膜604bの上部に位置する電位障壁膜(Si酸化膜)604cによって切断されている構造としたことにある。

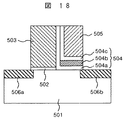

すなわち、本発明の第3の構造例による不揮発性半導体記憶装置の特徴は、

(a)半導体基板701中に形成された第1半導体領域(ソース)706aおよび第2半導体領域(ドレイン)706bと、

(b)前記第1半導体領域706aおよび第2半導体領域706b間上の前記半導体基板701の上部に形成された第1導電体(選択ゲートSG)703および第2導電体(メモリゲートMG)705と、

(c)前記第1導電体703と前記半導体基板701との間に形成された第1絶縁膜702と、

(d)前記第2導電体705と前記半導体基板701との間、及び前記第1導電体(SG)703と前記第2導電体(MG)705との間に形成された3層の第2絶縁膜(Si酸化膜704a/Si窒化膜704b及び704'b/Si酸化膜704c)704を有し、

前記第2導電体705と前記半導体基板701との間の前記第2絶縁膜704は、電位障壁膜(Si酸化膜)704aと、その上部のSi窒化膜(電荷保持膜)704bと、その上部の電位障壁膜(Si酸化膜)704cとからなり、

前記第1導電体(SG)703と前記第2導電体(MG)705との間に位置するSi窒化膜704'bの膜厚が、前記第2導電体705と前記半導体基板701との間に位置するSi窒化膜704の膜厚に比べ薄い構造としたことにある。

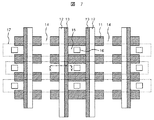

まず、本発明の中で共通なメモリアレーの構成を図7に示す。各メモリセルは溝型素子分離領域(STI)11で分離されており、ソース線14を共通として、MONOS型不揮発メモリの選択ゲート電極となるワード線12、及びメモリMOS型トランジスタのゲート配線13を平行に配置し、上記ゲート配線12、13を挟んでソース領域14と対称の位置にドレイン15を形成している。図中の16は、ドレイン15とビット線17を接続するための開口部である。ビット線17は、不図示の層間絶縁膜を介してワード線12と直交するように配置されている。

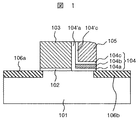

図1は、本発明の第1の実施例の断面図であり、図7に示したX−Y断面に相当する。図7にはビット線17を示しているが、図1には図示していない。

まず、図2の断面工程図に示したように、Si基板101上に、周知の技術を用いて不図示の溝形素子分離領域を形成した。この溝型素子分離領域は、図7に示した符合11に相当する。

これにより、ホットホール消去電流を約30%低減できた。また、繰り返し書込み/消去特性においては電子の消し残りが観測されず、1e5回以上の書き換え耐性が得られた。更に、1e4回の書き込み/消去動作後に150℃の放置リテンション特性(しきい電圧の変動量で定義では)を評価した結果、従来構造に比べ約2桁の改善があった。

次に、図21〜図26を用いて本発明の第2の実施例を説明する。この実施例では、実施例1と同様に、選択ゲート電極側底部に電荷保持膜であるSi窒化膜を形成しない、他の3つの方法について検討した。その結果について以下に順次説明する。

(1)第1の方法について:

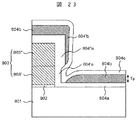

図21と図22とを用いて説明する。先ず、図21の断面図に示したように、実施例1と同様にSi基板801上に選択MOS型トランジスタQ2のゲート絶縁膜802を形成した後、ノンドープ多結晶Si膜803を200nm堆積した。

(2)第2の方法について:

次に、図25を用いて第2の方法の説明を行う。上記第1の方法と同様に、Si基板901上に選択MOS型トランジスタQ2のゲート酸化膜902を形成した後、リンを5e20 atms/cm3含んだ150nmの多結晶Si膜903を堆積した。

(3)第3の方法について:

次に、図26を用いて第3の方法の説明を行う。上記第1の方法と同様に、Si基板111上に選択MOS型トランジスタQ2のゲート酸化膜112を形成した後、リンを5e20 atms/cm3含んだ150nmの多結晶Si膜113を堆積した。続いて、減圧CVD法により、厚さ50nmのSi酸化膜117を堆積した後、周知の技術を用いて、上記Si酸化膜117を所定の形状に加工し、下地の多結晶Si膜113を露出させた。

これにより、ホットホール消去電流を約30%低減できた。

次に、本発明の第3の実施例を説明する。この実施例は先に図19で概説した第2の構造例に該当するものであり、図9〜図13の断面工程図にしたがって説明する。本実施例でも、メモリアレーの構成(図7参照)、及び各電圧の設定(図8参照)は実施例1と同様である。

次に、図14を用いて、本発明の第4の実施例を説明する。この実施例は先に図20で概説した第3の構造例に該当するものであり、本実施例でも、メモリアレーの構成、及び各電圧の設定は実施例1と同様である。本実施例では、実施例1に示した方法を用いて、図14に示すメモリセルを作製した。

(1)SiH2Cl2とNH3を原料ガスとしたSi窒化膜は、温度;780℃、圧力;60Pa〜200Pa、SiH2Cl2流量;20cc/min、NH3流量;220cc/minとした。

(2)SiH4とNH3を原料ガスとしたSi窒化膜は、温度;700℃、圧力;100Pa〜400Pa、SiH4流量;30cc/min、NH3流量;220cc/minとした。

(3)Si2H6とNH3を原料ガスとしたSi窒化膜は、温度;650℃、圧力;200Pa〜400Pa、Si2H6流量;10cc/min、NH3流量;400cc/minとした。

また、本発明の不揮発性メモリは、マイクロコンピュータに用いるなど、種々の装置に搭載可能である。また、本発明は、Si窒化膜に代表される電荷保持機能を有する絶縁膜を用いた不揮発性半導体装置全般に適用可能である。

102…ゲート絶縁膜(選択MOS型トランジスタ)、

103…選択ゲート電極(選択MOS型トランジスタ)、

104a…下層電位障壁膜(Si酸化膜)、

104b…Si窒化膜(電荷保持膜)、

104c…上層電位障壁膜(Si酸化膜)、

104'a…選択ゲート電極側壁部の下層電位障壁膜(Si酸化膜)、

104'b…選択ゲート電極側壁部のSi窒化膜(電荷保持膜)、

104'c…選択ゲート電極側壁部の上層電位障壁膜(Si酸化膜)、

105… メモリゲート電極(メモリMOS型トランジスタ)、

106a…ソース領域、

106b…ドレイン領域

201…p型ウエル領域(Si基板)、

202…ゲート絶縁膜(選択MOS型トランジスタ)、

203…選択ゲート電極(選択MOS型トランジスタ)、

204a…下層電位障壁膜(Si酸化膜)、

204b…Si窒化膜(電荷保持膜)、

204c…上層電位障壁膜(Si酸化膜)、

204'a…選択ゲート電極側壁部の下層電位障壁膜(Si酸化膜)、

204'b…選択ゲート電極側壁部のSi窒化膜(電荷保持膜)、

204'c…選択ゲート電極側壁部の上層電位障壁膜(Si酸化膜)、

205…メモリゲート電極(メモリMOS型トランジスタ)、

206a…ソース領域、

206b…ドレイン領域、

301…p型ウエル領域(Si基板)、

302…ゲート絶縁膜(選択MOS型トランジスタ)、

303…選択ゲート電極(選択MOS型トランジスタ)、

304a…下層電位障壁膜(Si酸化膜)、

304b…Si窒化膜(電荷保持膜)、

304c…上層電位障壁膜(Si酸化膜)、

304'a…選択ゲート電極側壁部の下層電位障壁膜(Si酸化膜)、

304'b…選択ゲート電極側壁部のSi窒化膜(電荷保持膜)、

304'c…選択ゲート電極側壁部の上層電位障壁膜(Si酸化膜)、

305… メモリゲート電極(メモリMOS型トランジスタ)、

306a…ソース領域、

306b…ドレイン領域、

401…p型ウエル領域(Si基板)、

402…ゲート絶縁膜(選択MOS型トランジスタ)、

403…選択ゲート電極(選択MOS型トランジスタ)、

404a…下層電位障壁膜(Si酸化膜)、

404b…Si窒化膜(電荷保持膜)、

404c…上層電位障壁膜(Si酸化膜)、

405…メモリゲート電極(メモリMOS型トランジスタ)、

406a…ソース領域、

406b…ドレイン領域、

501…p型ウエル領域(Si基板)、

502…ゲート絶縁膜(選択MOS型トランジスタ)、

503…選択ゲート電極(選択MOS型トランジスタ)、

504a…下層電位障壁膜(Si酸化膜)、

504b…Si窒化膜(電荷保持膜)、

504c…上層電位障壁膜(Si酸化膜)、

505…メモリゲート電極(メモリMOS型トランジスタ)、

506a…ソース領域、

506b…ドレイン領域、

601…p型ウエル領域(Si基板)、

602…ゲート絶縁膜(選択MOS型トランジスタ)、

603…選択ゲート電極(選択MOS型トランジスタ)、

604a…下層電位障壁膜(Si酸化膜)、

604b…Si窒化膜(電荷保持膜)、

604'b…選択ゲート電極側壁部のSi窒化膜(電荷保持膜)、

604c…上層電位障壁膜(Si酸化膜)、

605…ゲート電極(メモリゲート電極)、

606a…ソース領域、

606b…ドレイン領域、

701…p型ウエル領域(Si基板)、

702…ゲート絶縁膜(選択MOS型トランジスタ)、

703…選択ゲート電極(選択MOS型トランジスタ)、

704a…下層電位障壁膜(Si酸化膜)、

704b…Si窒化膜(電荷保持膜)、

704'b…選択ゲート電極側壁部のSi窒化膜(電荷保持膜)、

704c…上層電位障壁膜(Si酸化膜)、

705…ゲート電極(メモリゲート電極)、

706a…ソース領域、

706b…ドレイン領域、

801…p型ウエル領域(Si基板)、

802…ゲート絶縁膜(選択MOS型トランジスタ)、

803'…選択ゲート電極(ノンドープ多結晶Si)、

803''…選択ゲート電極(リンドープ多結晶Si、

804a…下層電位障壁膜(Si酸化膜)、

804'a…選択ゲート電極側壁部の下層電位障壁膜(Si酸化膜)、

804''a…選択ゲート電極側壁部の下層電位障壁膜(Si酸化膜)、

804b…Si窒化膜(電荷保持膜)、

804'b…選択ゲート電極側壁部のSi窒化膜(電荷保持膜)、

804c…上層電位障壁膜(Si酸化膜)、

804'c…選択ゲート電極側壁部の上層電位障壁膜(Si酸化膜)、

901…p型ウエル領域(Si基板)、

902…ゲート絶縁膜(選択MOS型トランジスタ)、

903…選択ゲート電極、

904a…下層電位障壁膜(Si酸化膜)、

904'a…選択ゲート電極側壁部の下層電位障壁膜(Si酸化膜)、

904b…Si窒化膜(電荷保持膜)、

904'b…Si酸化膜側壁部のSi窒化膜、

907…Si酸化膜、

111…p型ウエル領域(Si基板)、

112…ゲート絶縁膜(選択MOS型トランジスタ)、

113…選択ゲート電極、

114a…下層電位障壁膜(Si酸化膜)、

114'a…選択ゲート電極側壁部の下層電位障壁膜(Si酸化膜)、

114b…Si窒化膜(電荷保持膜)、

114'b…Si酸化膜側壁部のSi窒化膜、

117…Si酸化膜、

Claims (7)

- ソースサイドインジェクションを用いた電子注入、バンド間トンネリングを用いた正孔注入を行うスプリット構造のメモリセルを備えた不揮発性半導体記憶装置であって、前記メモリセルは、

(a)半導体基板中に形成された第1および第2半導体領域と、

(b)前記第1および第2半導体領域間上の前記半導体基板の上部に形成された選択ゲートおよび前記選択ゲート形成後に形成されたメモリゲートと、

(c)前記選択ゲートと前記半導体基板との間に形成された第1絶縁膜と、

(d)前記メモリゲートと前記半導体基板との間に形成された第2絶縁膜と、

(e)前記選択ゲートとメモリゲートとの間の前記選択ゲート側壁部に形成された第3絶縁膜とを備え、

前記第2絶縁膜は、前記半導体基板上の第1の電位障壁膜と、その上部に形成されたシリコン窒化膜と、その上部に形成された第2の電位障壁膜から成り、

前記第3絶縁膜は、前記選択ゲート側壁部上の前記第1の電位障壁膜と、その上部に形成された前記第2の電位障壁膜から成り、

前記第1の電位障壁膜と前記第2の電位障壁膜の間に前記シリコン窒化膜が存在せず、

前記選択ゲートの側壁の一面が、その断面において逆テーパ形状を有していることを特徴とする不揮発性半導体記憶装置。 - 請求項1記載の不揮発性半導体記憶装置において、前記選択ゲートの側壁の一面がメモリゲートに隣接する側の側壁であり、前記選択ゲート側壁の延長線とSi基板の作る角度が75°〜90°未満であることを特徴とする不揮発性半導体記憶装置。

- 請求項1に記載の不揮発性半導体記憶装置において、前記選択ゲートの一方の側壁に形成された第1の電位障壁膜の膜厚が、シリコン基板側に近い部分で薄くなっていることを特徴とする不揮発性半導体記憶装置。

- 請求項1に記載の不揮発性半導体記憶装置において、前記選択ゲートの上に絶縁膜パターンが形成されており、前記絶縁膜の一方のパターンエッジより前記選択ゲートのパターンエッジが内側に配置されていることを特徴とする不揮発性半導体記憶装置。

- 請求項4に記載の不揮発性半導体記憶装置において、前記選択ゲートの側壁の一面がメモリゲートに隣接する側の側壁であり、前記選択ゲート上に形成された絶縁膜のパターンエッジと前記絶縁膜パターンより内側に配置された選択ゲートのパターンエッジとの長さが、40nm以下であることを特徴とする不揮発性半導体記憶装置。

- ソースサイドインジェクションを用いた電子注入、バンド間トンネリングを用いた正孔注入を行うスプリット構造のメモリセルを備えた不揮発性半導体記憶装置であって、前記メモリセルは、

(a)半導体基板中に形成された第1および第2半導体領域と、

(b)前記第1および第2半導体領域間上の前記半導体基板の上部に形成された選択ゲートおよび前記選択ゲート形成後に形成されたメモリゲートと、

(c)前記選択ゲートと前記半導体基板との間に形成された第1絶縁膜と、

(d)前記メモリゲートと前記半導体基板との間に形成された第2絶縁膜と、

(e)前記選択ゲートとメモリゲートとの間の前記選択ゲート側壁部に形成された第3絶縁膜とを備え、

前記第2絶縁膜は、前記半導体基板上の第1の電位障壁膜と、その上部に形成されたシリコン窒化膜と、その上部に形成された第2の電位障壁膜から成り、

前記第3絶縁膜は、前記選択ゲート側壁部上の前記第1の電位障壁膜と、その上部に形成されたシリコン窒化膜と、その上部に形成された前記第2の電位障壁膜から成り、

前記第3絶縁膜の前記シリコン窒化膜の膜厚が、前記第2絶縁膜の前記シリコン窒化膜の膜厚よりも薄いことを特徴とする不揮発性半導体記憶装置。 - 請求項6に記載の不揮発性半導体記憶装置において、前記半導体基板からソースサイドインジェクションにより前記第2絶縁膜の前記シリコン窒化膜に電子を注入する書き込み手段と、前記半導体基板からバンド間トンネリングにより前記第2絶縁膜の前記シリコン窒化膜に正孔を注入して電子を消去する消去手段とを備えたことを特徴とする不揮発性半導体記憶装置。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004066767A JP4546117B2 (ja) | 2004-03-10 | 2004-03-10 | 不揮発性半導体記憶装置 |

| US11/013,406 US7115943B2 (en) | 2004-03-10 | 2004-12-17 | Nonvolatile semiconductor memory device and manufacturing method thereof |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004066767A JP4546117B2 (ja) | 2004-03-10 | 2004-03-10 | 不揮発性半導体記憶装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2005259843A JP2005259843A (ja) | 2005-09-22 |

| JP2005259843A5 JP2005259843A5 (ja) | 2007-04-12 |

| JP4546117B2 true JP4546117B2 (ja) | 2010-09-15 |

Family

ID=34918355

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004066767A Expired - Fee Related JP4546117B2 (ja) | 2004-03-10 | 2004-03-10 | 不揮発性半導体記憶装置 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US7115943B2 (ja) |

| JP (1) | JP4546117B2 (ja) |

Families Citing this family (33)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4584736B2 (ja) * | 2005-02-18 | 2010-11-24 | Okiセミコンダクタ株式会社 | 半導体装置及び半導体装置の製造方法 |

| JP4659527B2 (ja) * | 2005-06-20 | 2011-03-30 | ルネサスエレクトロニクス株式会社 | 半導体装置の製造方法 |

| JP2007194511A (ja) * | 2006-01-23 | 2007-08-02 | Renesas Technology Corp | 不揮発性半導体記憶装置およびその製造方法 |

| US7387972B2 (en) * | 2006-03-01 | 2008-06-17 | Promos Technologies Pte. Ltd. | Reducing nitrogen concentration with in-situ steam generation |

| JP4799217B2 (ja) * | 2006-03-03 | 2011-10-26 | Okiセミコンダクタ株式会社 | 半導体装置の製造方法 |

| JP5086558B2 (ja) * | 2006-04-04 | 2012-11-28 | ルネサスエレクトロニクス株式会社 | 半導体装置およびその製造方法 |

| JP2007311695A (ja) * | 2006-05-22 | 2007-11-29 | Renesas Technology Corp | 半導体装置の製造方法 |

| JP5086626B2 (ja) * | 2006-12-15 | 2012-11-28 | ルネサスエレクトロニクス株式会社 | 不揮発性半導体記憶装置及びその製造方法 |

| JP2009076188A (ja) | 2007-08-24 | 2009-04-09 | Renesas Technology Corp | 不揮発性半導体記憶装置 |

| US8320191B2 (en) | 2007-08-30 | 2012-11-27 | Infineon Technologies Ag | Memory cell arrangement, method for controlling a memory cell, memory array and electronic device |

| JP2009094170A (ja) * | 2007-10-04 | 2009-04-30 | Nec Electronics Corp | 不揮発性半導体メモリ及びその製造方法 |

| US7923328B2 (en) * | 2008-04-15 | 2011-04-12 | Freescale Semiconductor, Inc. | Split gate non-volatile memory cell with improved endurance and method therefor |

| US7939880B2 (en) * | 2008-04-15 | 2011-05-10 | Freescale Semiconductor, Inc. | Split gate non-volatile memory cell |

| KR20090126520A (ko) * | 2008-06-04 | 2009-12-09 | 삼성전자주식회사 | 반도체 장치의 제조 방법 및 이에 의해 제조된 반도체 장치 |

| US8173505B2 (en) * | 2008-10-20 | 2012-05-08 | Freescale Semiconductor, Inc. | Method of making a split gate memory cell |

| US8252653B2 (en) * | 2008-10-21 | 2012-08-28 | Applied Materials, Inc. | Method of forming a non-volatile memory having a silicon nitride charge trap layer |

| JP5592214B2 (ja) * | 2010-09-22 | 2014-09-17 | ルネサスエレクトロニクス株式会社 | 半導体装置の製造方法 |

| US9263132B2 (en) | 2011-08-10 | 2016-02-16 | Globalfoundries Singapore Pte. Ltd. | Double gated flash memory |

| US10014380B2 (en) | 2012-12-14 | 2018-07-03 | Cypress Semiconductor Corporation | Memory first process flow and device |

| US20140167142A1 (en) | 2012-12-14 | 2014-06-19 | Spansion Llc | Use Disposable Gate Cap to Form Transistors, and Split Gate Charge Trapping Memory Cells |

| US9966477B2 (en) | 2012-12-14 | 2018-05-08 | Cypress Semiconductor Corporation | Charge trapping split gate device and method of fabricating same |

| US8816438B2 (en) * | 2012-12-14 | 2014-08-26 | Spansion Llc | Process charging protection for split gate charge trapping flash |

| US9209197B2 (en) | 2012-12-14 | 2015-12-08 | Cypress Semiconductor Corporation | Memory gate landing pad made from dummy features |

| US20140167141A1 (en) | 2012-12-14 | 2014-06-19 | Spansion Llc | Charge Trapping Split Gate Embedded Flash Memory and Associated Methods |

| US8822289B2 (en) | 2012-12-14 | 2014-09-02 | Spansion Llc | High voltage gate formation |

| US20140167220A1 (en) | 2012-12-14 | 2014-06-19 | Spansion Llc | Three dimensional capacitor |

| US9368606B2 (en) | 2012-12-14 | 2016-06-14 | Cypress Semiconductor Corporation | Memory first process flow and device |

| US8836006B2 (en) | 2012-12-14 | 2014-09-16 | Spansion Llc | Integrated circuits with non-volatile memory and methods for manufacture |

| US20140210012A1 (en) | 2013-01-31 | 2014-07-31 | Spansion Llc | Manufacturing of FET Devices Having Lightly Doped Drain and Source Regions |

| CN103579324B (zh) * | 2013-11-18 | 2016-04-06 | 北京大学 | 一种三面源隧穿场效应晶体管及其制备方法 |

| US9368644B2 (en) * | 2013-12-20 | 2016-06-14 | Cypress Semiconductor Corporation | Gate formation memory by planarization |

| US20150200279A1 (en) * | 2014-01-12 | 2015-07-16 | United Microelectronics Corp. | Method of manufacturing memory cell |

| JP6556567B2 (ja) * | 2015-09-09 | 2019-08-07 | ルネサスエレクトロニクス株式会社 | 半導体装置の製造方法 |

Citations (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5408115A (en) * | 1994-04-04 | 1995-04-18 | Motorola Inc. | Self-aligned, split-gate EEPROM device |

| JP2002026149A (ja) * | 2000-05-02 | 2002-01-25 | Sony Corp | 不揮発性半導体記憶装置およびその動作方法 |

| JP2003046002A (ja) * | 2001-07-26 | 2003-02-14 | Sony Corp | 不揮発性半導体メモリ装置およびその動作方法 |

| JP2003051558A (ja) * | 2001-06-01 | 2003-02-21 | Sony Corp | 不揮発性半導体メモリ装置およびその電荷注入方法 |

| JP2003318290A (ja) * | 2002-04-25 | 2003-11-07 | Nec Electronics Corp | 不揮発性半導体記憶装置およびその製造方法 |

| JP2004503113A (ja) * | 2000-07-12 | 2004-01-29 | コーニンクレッカ フィリップス エレクトロニクス エヌ ヴィ | 半導体不揮発性メモリデバイス |

| JP2004111749A (ja) * | 2002-09-19 | 2004-04-08 | Renesas Technology Corp | 半導体装置およびその製造方法 |

| JP2004343014A (ja) * | 2003-05-19 | 2004-12-02 | Sharp Corp | 半導体記憶装置、半導体装置、及びそれらの製造方法、並びに携帯電子機器、並びにicカード |

Family Cites Families (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5969383A (en) * | 1997-06-16 | 1999-10-19 | Motorola, Inc. | Split-gate memory device and method for accessing the same |

| JP3930256B2 (ja) * | 2001-02-07 | 2007-06-13 | スパンション エルエルシー | 半導体装置及びその製造方法 |

-

2004

- 2004-03-10 JP JP2004066767A patent/JP4546117B2/ja not_active Expired - Fee Related

- 2004-12-17 US US11/013,406 patent/US7115943B2/en active Active

Patent Citations (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5408115A (en) * | 1994-04-04 | 1995-04-18 | Motorola Inc. | Self-aligned, split-gate EEPROM device |

| JP2002026149A (ja) * | 2000-05-02 | 2002-01-25 | Sony Corp | 不揮発性半導体記憶装置およびその動作方法 |

| JP2004503113A (ja) * | 2000-07-12 | 2004-01-29 | コーニンクレッカ フィリップス エレクトロニクス エヌ ヴィ | 半導体不揮発性メモリデバイス |

| JP2003051558A (ja) * | 2001-06-01 | 2003-02-21 | Sony Corp | 不揮発性半導体メモリ装置およびその電荷注入方法 |

| JP2003046002A (ja) * | 2001-07-26 | 2003-02-14 | Sony Corp | 不揮発性半導体メモリ装置およびその動作方法 |

| JP2003318290A (ja) * | 2002-04-25 | 2003-11-07 | Nec Electronics Corp | 不揮発性半導体記憶装置およびその製造方法 |

| JP2004111749A (ja) * | 2002-09-19 | 2004-04-08 | Renesas Technology Corp | 半導体装置およびその製造方法 |

| JP2004343014A (ja) * | 2003-05-19 | 2004-12-02 | Sharp Corp | 半導体記憶装置、半導体装置、及びそれらの製造方法、並びに携帯電子機器、並びにicカード |

Also Published As

| Publication number | Publication date |

|---|---|

| US20050199940A1 (en) | 2005-09-15 |

| JP2005259843A (ja) | 2005-09-22 |

| US7115943B2 (en) | 2006-10-03 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4546117B2 (ja) | 不揮発性半導体記憶装置 | |

| JP5466421B2 (ja) | ポリ間電荷トラップ構造体を有する浮遊ゲートメモリ素子 | |

| US7737488B2 (en) | Blocking dielectric engineered charge trapping memory cell with high speed erase | |

| US9082656B2 (en) | NAND flash with non-trapping switch transistors | |

| US8860124B2 (en) | Depletion-mode charge-trapping flash device | |

| TWI408800B (zh) | 非揮發性記憶體單元及其製造方法 | |

| US20080258205A1 (en) | Non-volatile semiconductor memory device | |

| US9406813B2 (en) | Semiconductor device and method of manufacturing same | |

| TW200915545A (en) | Semiconductor memory device and method of manufacturing the same | |

| CN106558588A (zh) | 半导体装置 | |

| JP6998267B2 (ja) | 半導体装置およびその製造方法 | |

| US7692233B2 (en) | Semiconductor device and manufacturing method thereof | |

| CN108231561A (zh) | 半导体装置的制造方法和半导体装置 | |

| CN106024889A (zh) | 半导体器件及其制造方法 | |

| US20070205440A1 (en) | Semiconductor device and method for producing the same | |

| TWI390711B (zh) | 非揮發性半導體記憶裝置及其製造方法 | |

| JPH07226449A (ja) | 電気的に情報の書込および消去が可能な半導体記憶装置およびその製造方法ならびにその記憶認識方法 | |

| JP2004022575A (ja) | 半導体装置 | |

| TW201826501A (zh) | 半導體裝置及其製造方法 | |

| JP5351274B2 (ja) | 不揮発性半導体記憶装置 | |

| JP2009147135A (ja) | 不揮発性半導体記憶装置およびその製造方法 | |

| JP2007103640A (ja) | 不揮発性半導体メモリデバイス | |

| JP2009283731A (ja) | 半導体装置およびその製造方法 | |

| KR20090069933A (ko) | 비휘발성 메모리 소자, 그 제조방법 및 그 구동방법 | |

| KR20090110806A (ko) | 인터폴리 전하 트래핑 구조를 갖는 플로팅 게이트 메모리 디바이스 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070228 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20070228 |

|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20070228 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20090826 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20090908 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20091106 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20091208 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100204 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20100510 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20100615 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20100701 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130709 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4546117 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| LAPS | Cancellation because of no payment of annual fees |