JP4466735B2 - 信号線駆動回路および表示装置、並びに電子機器 - Google Patents

信号線駆動回路および表示装置、並びに電子機器 Download PDFInfo

- Publication number

- JP4466735B2 JP4466735B2 JP2007338996A JP2007338996A JP4466735B2 JP 4466735 B2 JP4466735 B2 JP 4466735B2 JP 2007338996 A JP2007338996 A JP 2007338996A JP 2007338996 A JP2007338996 A JP 2007338996A JP 4466735 B2 JP4466735 B2 JP 4466735B2

- Authority

- JP

- Japan

- Prior art keywords

- output

- operational amplifier

- negative

- output buffer

- positive

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

- G09G3/3611—Control of matrices with row and column drivers

- G09G3/3685—Details of drivers for data electrodes

- G09G3/3688—Details of drivers for data electrodes suitable for active matrices only

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2310/00—Command of the display device

- G09G2310/02—Addressing, scanning or driving the display screen or processing steps related thereto

- G09G2310/0264—Details of driving circuits

- G09G2310/0281—Arrangement of scan or data electrode driver circuits at the periphery of a panel not inherent to a split matrix structure

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2310/00—Command of the display device

- G09G2310/02—Addressing, scanning or driving the display screen or processing steps related thereto

- G09G2310/0264—Details of driving circuits

- G09G2310/0297—Special arrangements with multiplexing or demultiplexing of display data in the drivers for data electrodes, in a pre-processing circuitry delivering display data to said drivers or in the matrix panel, e.g. multiplexing plural data signals to one D/A converter or demultiplexing the D/A converter output to multiple columns

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

- G09G3/3611—Control of matrices with row and column drivers

- G09G3/3614—Control of polarity reversal in general

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Physics & Mathematics (AREA)

- Theoretical Computer Science (AREA)

- Computer Hardware Design (AREA)

- Crystallography & Structural Chemistry (AREA)

- Chemical & Material Sciences (AREA)

- Nonlinear Science (AREA)

- Mathematical Physics (AREA)

- Optics & Photonics (AREA)

- Liquid Crystal Display Device Control (AREA)

- Control Of Indicators Other Than Cathode Ray Tubes (AREA)

- Liquid Crystal (AREA)

Description

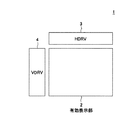

近年、液晶表示装置の開発、性能の発展はめざましく、テレビジョンや、携帯電話機やPDA(Personal Digital Assistants)などの携帯端末、デジタルカメラ、ノート型パーソナルコンピュータ、ビデオカメラなど、電子機器に入力された映像信号、若しくは、電子機器内で生成した映像信号を、画像若しくは映像として表示するあらゆる分野の電子機器の表示装置に適用することが可能である。

また、有効表示部2には、信号線駆動回路3、並びにゲート線駆動回路4により駆動される信号線およびゲート線(垂直走査線)がマトリクス状に配線されている。

この場合、対向電極の電圧が高レベルのときに画素電極にはこの高レベルを基準として負の極性を有する電圧が印加され、対向電極の電圧が低レベルのときに画素電極にはこの低レベルの基準として正の極性を有する電圧が印加されることになる。

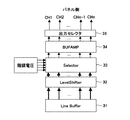

信号線駆動回路3において、極性反転動作を行わせるため、出力バッファ部にレイルトゥレイル(Rail to Rail)の出力アナログバッファ回路を用いたり(非特許文献1参照)、スイッチを有する出力セレクタを用いた構成が採用されてきた(特許文献1参照)。

図3においては、隣接する2チャネル分に対応する信号線駆動回路の出力バッファ段を示している。実際には、アナログバッファのチャネル数は数100以上あり、これらのチャネルに対応する信号線が駆動される。

OTA34−11の反転入力端子(−)が前段のDACの出力線に接続され、非反転入力端子(+)がOAMP34−12の出力に接続されている。

OTA34−21の反転入力端子(−)が前段のDACの出力線に接続され、非反転入力端子(+)がOAMP34−22の出力に接続されている。

スイッチSW11の端子aが第1の増幅回路34−1のOAMP34−12の出力に接続され、端子bがチャネルCH1の信号線SGL1に接続されている。

スイッチSW12の端子aが第1の増幅回路34−1のOAMP34−12の出力に接続され、端子bがチャネルCH2の信号線SGL2に接続されている。

スイッチSW21の端子aが第2の増幅回路34−2のOAMP34−22の出力に接続され、端子bがチャネルCH2の信号線SGL2に接続されている。

スイッチSW22の端子aが第2の増幅回路34−2のOAMP34−22の出力に接続され、端子bがチャネルCH1の信号線SGL1に接続されている。

一方、出力セレクタ35のスイッチSW12とスイッチSW22がオン状態、スイッチSW11とスイッチSW21がオフ状態に制御されると、第1の増幅回路34−1による正極性の信号電圧が信号線SGL2に供給され、第2の増幅回路34−2により負極性の信号電圧が信号線SGL1に供給される。

CMOS, Circuit Design, layout and Simulation P661 Figure 25.49, R.Jacob、 Baker Harry、 W.LI David E.Boyce 著

すなわち、回路構成が複雑になり、消費電力が大きく、レイアウト面積が大きい。

ON抵抗を小さくするため、出力セレクタサイズと出力段のサイズが大きくなる。その結果、レイアウト面積の増加を招く。

また、出力セレクタのON抵抗によるセトリングの低下を招く。

一方、第2のモード時には、正極性側演算増幅器による正極性の信号電圧が第2の出力バッファを介して第2の信号線に供給され、負極性側演算増幅器による負極性の信号電圧が第1の出力バッファを介して第1の信号線に供給される。

また、本発明において出力段増幅器のオフセットキャンセル効果も発生するため、画質向上にも貢献することになる。

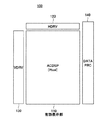

ここでは、たとえば、各画素の電気光学素子として液晶セルを用いたアクティブマトリクス型液晶表示装置に適用した場合を例に採って説明する。

そして、有効表示部110は、信号線駆動回路120、並びにゲート線駆動回路130により駆動される信号線(データ線)およびゲート線(垂直走査線)がマトリクス状(格子状)に配線されている。

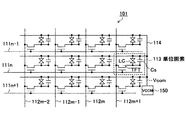

ここでは、図面の簡略化のために、3行(n−1行〜n+1行)4列(m−2列〜m+1列)の画素配列の場合を例に採って示している。

ここで、液晶セルLCは、薄膜トランジスタTFTで形成される画素電極(一方の電極)とこれに対向して形成される対向電極(他方の電極)との間で発生する容量を意味する。

液晶セルLCは、画素電極が薄膜トランジスタTFTのドレイン電極に接続され、対向電極が共通線114に接続されている。保持容量Csは、薄膜トランジスタTFTのドレイン電極と共通線114との間に接続されている。

共通線114には、コモン電圧供給回路(VCOM回路)150により所定の交流電圧がコモン電圧Vcomとして与えられる。

ゲート線駆動回路130は、たとえばシフトレジスタを含んで構成され、垂直転送クロックVCK(図示せず)に同期して順次垂直選択パルスを発生してゲート線(垂直走査線)…,111n−1,111n,111n+1,…に与えることによって垂直走査を行う。

なお、図6において、符号141で示すシリアル・パラレルコンバータ(SPC)は、データ処理回路141に含まれる。

以下の説明では、出力バッファ部124に符号200を付して説明する。

負極性側OTA221の出力は、スイッチSW233を介して第2のOAMP222の入力に供給され、スイッチSW234を介して第1のOAMP212の入力に供給される。

第2のOAMP222の出力端子は、チャネルCH2の第2の信号線112m+1に接続される出力端子TO2に接続されている。

また、スイッチSW232、SW234、SW236、SW238は共通の信号CRSでオン、オフが制御され、これらスイッチにより第2のスイッチ群が構成される。

第1のスイッチ群のスイッチSW231、SW233、SW235、SW237と第2のスイッチ群のスイッチSW232、SW234、SW236、SW238は相補的にオン、オフされる。

図示しない制御系により、信号STRがハイレベルのとき、信号CRSはローレベルに制御され、信号STRがローレベルのとき、信号CRSはハイレベルに制御される。

たとえば、第1のスイッチ群のスイッチSW231、SW233、SW235、SW237は信号STRがハイレベルのときオンし、ローレベルのときオフする。

第2のスイッチ群のスイッチSW232、SW234、SW236、SW238は信号CRSがハイレベルのときオンし、ローレベルのときオフする。

本実施形態では、信号STRがハイレベルのときを第1のモードとし、信号CRSがハイレベルのときを第2のモードとする。

スイッチSW232の端子aが正極性側OTA211の出力端子に接続され、端子bが第2のOAMP222の第1入力端子に接続されている。

スイッチSW233の端子aが負極性側OTA221の出力端子に接続され、端子bが第2のOAMP222の第2入力端子に接続されている。

スイッチSW234の端子aが負極性側OTA221の出力端子に接続され、端子bが第1のOAMP212の第2入力端子に接続されている。

スイッチSW236の端子aが第2のOAMP222の出力端子に接続され、端子bが正極性側OTA211の非反転入力端子(+)に接続されている。

スイッチSW237の端子aが負極性側OTA221の非反転入力端子(+)に接続され、端子bが第2のOAMP222の出力端子に接続されている。

スイッチSW238の端子aが負極性側OTA221の非反転入力端子(+)に接続され、端子bが第1のOAMP212の出力端子に接続されている。

PMOSトランジスタPT211のドレインがNMOSトランジスタNT211のドレインに接続され、その接続点によりノードND211が形成されている。また、PMOSトランジスタPT211のドレインとゲートが接続され、その接続点がPMOSトランジスタPT212のゲートに接続されている。

PMOSトランジスタPT212のドレインがNMOSトランジスタNT212のドレインに接続され、その接続点により正極性側OTA211の出力ノード(出力端子)ND212が形成されている。

NMOSトランジスタNT211とNMOSトランジスタNT212のソース同士が接続され、その接続点が電流源I211のドレインに接続されている。

したがって、NMOSトランジスタNT211のゲートがスイッチSW235,SW236の端子bに接続されている。また、NMOSトランジスタNT212のゲートがDAC123の出力の入力端子TI1に接続されている。

そして、OTA211の出力ノードND212がスイッチSW231,SW232の端子aに接続されている。

電流源I212は電源電位VDDに接続され、また、この電流源I212とPMOSトランジスタPT213のゲートと転送ゲートTMG211の一方の入出力端子T211が接続されて第1のOAMP212の第1の入力ノード(第1入力端子)ND214が形成されている。

電流源I213は接地電位GNDに接続され、また、この電流源I213とNMOSトランジスタNT213のゲートと転送ゲートTMG211の他方の入出力端子T212が接続されて第1のOAMP212の第2の入力ノード(第2入力端子)ND215が形成されている。

また、転送ゲートTMG211を構成するPMOSトランジスタPT214にゲートには第1のバイアス信号BIAS1が供給され、NMOSトランジスタNT214のゲートには第2のバイアス信号BIAS2が供給される。

第1のバイアス信号BIAS1と第2のバイアス信号BIAS2は出力段の第1のOAMP212にながれるDC電流を設定する電圧として印加される。

PMOSトランジスタPT221のドレインがNMOSトランジスタNT221のドレインに接続され、その接続点によりノードND221が形成されている。また、NMOSトランジスタNT221のドレインとゲートが接続され、その接続点がNMOSトランジスタNT222のゲートに接続されている。

PMOSトランジスタPT222のドレインがNMOSトランジスタNT222のドレインに接続され、その接続点により第2のOTA221の出力ノード(出力端子)ND222が形成されている。

NMOSトランジスタNT221とNMOSトランジスタNT222のソース同士が接続され、その接続点が接地電位GNDに接続されている。

したがって、PMOSトランジスタPT221のゲートがスイッチSW237,SW238の端子aに接続されている。また、PMOSトランジスタPT222のゲートがDAC123の出力の入力端子TI2に接続されている。

そして、第2のOTA221の出力ノードND222がスイッチSW233,SW234の端子aに接続されている。

電流源I222は電源電位VDDに接続され、また、この電流源I222とPMOSトランジスタPT223のゲートと転送ゲートTMG221の一方の入出力端子T221が接続されて第2のOAMP222の第1の入力ノード(第1入力端子)ND224が形成されている。

電流源I223は接地電位GNDに接続され、また、この電流源I223とNMOSトランジスタNT223のゲートと転送ゲートTMG221の他方の入出力端子T222が接続されて第2のOAMP222の第2の入力ノード(第2入力端子)ND225が形成されている。

また、転送ゲートTMG221を構成するPMOSトランジスタPT224にゲートには第1のバイアス信号BIAS1が供給され、NMOSトランジスタNT224のゲートには第2のバイアス信号BIAS2が供給される。

第1のバイアス信号BIAS1と第2のバイアス信号BIAS2は出力段の第2のOAMP222にながれるDC電流を設定する電圧として印加される。

出力段バッファである第1のOAMP212および第2のOAMP222は、AB級プッシュプル動作をしており、正極性側OTA211と負極性側OTA222の出力は動作点が異なるため、出力段の第1のOAMP212および第2のOAMP222の入力は2入力となり別ノードへ接続している。

また、帰還経路もそれにあわせて、相補的にSW235〜SW238で、正極性側OTA211と負極性側OTA222への入力を切り替える。

これにより、正極性側OTA211による正極性の信号電圧が第1のOAMP212を介して第1の信号線122mに供給され、負極性側OTA221による負極性の信号電圧が第2のOAMP222を介して第2の信号線112m+1に供給される。

一方、たとえば信号CRSがハイレベル、信号STRがローレベルで供給される第2のモード時には、スイッチ群230における第2のスイッチ群SW232,SW234,SW236,SW238がオン状態となり、第1のスイッチ群のスイッチSW231,SW233,SW235,SW237がオフ状態に保持される。

これにより、正極性側OTA211による正極性の信号電圧が第2のOAMP222を介して第2の信号線122m+1に供給され、負極性側OTA221による負極性の信号電圧が第1のOAMP212を介して第1の信号線112mに供給される。

出力経路にスイッチ(SW)がないため、出力セレクタ方式に比べてセトリングが早い。

この構成において、各出力段の第1のOAMP212と第2のOAMP222とは共通のものとなる。

なお、図7および図8の例では、出力段の第1のOAMP212と第2のOAMP222の入力が2入力となっているがこれに限定しているわけではない。1入力でも構わない。)

図10に示すように、スイッチ(SW)サイズは、スイッチが出力経路に接続されないためON抵抗を小さくする必要がなく、サイズを削減できる。

この出力セレクタ方式の場合、コモン電圧Vcomの中心電圧からの平均電圧はVa+(Δ1+Δ2)/2となり、オフセットがキャンセルされることはない。

この場合、コモン電圧Vcomの中心電圧からの平均電圧はオフセット値Δ1、Δ2の値にかかわらずΔaである。

出力経路にスイッチ(SW)をいれることなく、出力バッファ部の内部へ切り替えスイッチ(SW)を配置するため、スイッチ(SW)サイズの削減ができ、レイアウト面積を削減することが可能となる。

出力経路にスイッチ(SW)がないため、出力段のMOSサイズが削減でき、レイアウト面積を削減することが可能となる。

同様に、出力経路のスイッチ(SW)がないため、セトリングが改善され、特性の改善を図ることができる。

また、出力段の増幅器に起因のオフセット成分が、極性反転により光学的にキャンセルでき、特性改善を図れ、ひいては画質の向上を図ることができる。

以下に、本実施形態が適用される電子機器の一例について説明する。

本適用例に係るテレビジョン300は、フロントパネル320やフィルターガラス330等から構成される映像表示画面部310を含み、その映像表示画面部310として本実施形態に係る表示装置を用いることにより作製される。

本適用例に係るデジタルカメラ300Aは、フラッシュ用の発光部311、表示部312、メニュースイッチ313、シャッターボタン314等を含み、その表示部312として本実施形態に係る表示装置を用いることにより作製される。

本適用例に係るノート型パーソナルコンピュータ300Bは、本体321に、文字等を入力するとき操作されるキーボード322、画像を表示する表示部323等を含み、その表示部323として本実施形態に係る表示装置を用いることにより作製される。

本適用例に係るビデオカメラ300Cは、本体部331、前方を向いた側面に被写体撮影用のレンズ332、撮影時のスタート/ストップスイッチ333、表示部334等を含み、その表示部334として本実施形態に係る表示装置を用いることにより作製される。

本適用例に係る携帯電話機300Dは、上側筐体341、下側筐体342、連結部(ここではヒンジ部)343、ディスプレイ344、サブディスプレイ345、ピクチャーライト346、カメラ347等を含み、そのディスプレイ344やサブディスプレイ345として本実施形態に係る表示装置を用いることにより作製される。

Claims (7)

- 極性反転駆動される表示セルがマトリクス状に配置され、当該極性反転に対応して上記表示セルに接続される信号線に正極性の信号電圧または負極性の信号電圧を供給する信号線駆動回路であって、

信号線を駆動する入力データを増幅し、正極性の信号電圧および負極性の信号電圧を生成し、対をなす第1の信号線および第2の信号線に正極性の信号電圧および負極性の信号電圧を選択的に供給する出力バッファ部を有し、

上記出力バッファ部は、

入力データを増幅し、正極性の信号電圧を生成する正極性側演算増幅器と、

入力データを増幅し、負極性の信号電圧を生成する負極性側演算増幅器と、

上記第1の信号線に正極性または負極性の信号電圧を供給する第1の出力バッファと、

上記第2の信号線に負極性または正極性の信号電圧を供給する第2の出力バッファと、

上記正極性側演算増幅器の出力および上記負極性側演算増幅器の出力の各々と、上記第1の出力バッファの入力および上記第2の出力バッファの入力の各々との間、並びに、上記正極性側演算増幅器および上記負極性側演算増幅器の帰還入力段に配置されたスイッチ群と、を含み、

上記スイッチ群は、

第1のモード時は、

上記正極性側演算増幅器で生成された正極性の信号電圧を上記第1の出力バッファに入力し、当該第1の出力バッファの出力を上記正極性側演算増幅器に帰還させ、

上記負極性側演算増幅器で生成された負極性の信号電圧を上記第2の出力バッファに入力し、当該第2の出力バッファの出力を上記負極性側演算増幅器に帰還させ、

第2のモード時は、

上記正極性側演算増幅器で生成された正極性の信号電圧を上記第2の出力バッファに入力し、当該第2の出力バッファの出力を上記正極性側演算増幅器に帰還させ、

上記負極性側演算増幅器で生成された負極性の信号電圧を上記第1の出力バッファに入力し、当該第1の出力バッファの出力を上記負極性側演算増幅器に帰還させ、

上記第1の出力バッファの出力と上記第1の信号線との間、並びに上記第2の出力バッファの出力と上記第2の信号線との間には、スイッチが介在しない

信号線駆動回路。 - 上記正極性側演算増幅器は、

第1導電型トランジスタの差動対を有し、

上記負極性側演算増幅器は、

第2導電型トランジスタの差動対を有し、

上記第1および第2の出力バッファは、

AB級プシュプル動作機能を有する

請求項1記載の信号線駆動回路。 - 上記第1および第2の出力バッファは、2つの入力端子を有する

請求項2記載の信号線駆動回路。 - 極性反転駆動される表示セルがマトリクス状に配置される表示部と、

上記極性反転に対応して上記表示セルに接続される信号線に正極性の信号電圧または負極性の信号電圧を供給する信号線駆動回路と、を有し、

上記信号線駆動回路は、

信号線を駆動する入力データを増幅し、正極性の信号電圧および負極性の信号電圧を生成し、対をなす第1の信号線および第2の信号線に正極性の信号電圧および負極性の信号電圧を選択的に供給する出力バッファ部を含み、

上記出力バッファ部は、

入力データを増幅し、正極性の信号電圧を生成する正極性側演算増幅器と、

入力データを増幅し、負極性の信号電圧を生成する負極性側演算増幅器と、

上記第1の信号線に正極性または負極性の信号電圧を供給する第1の出力バッファと、

上記第2の信号線に負極性または正極性の信号電圧を供給する第2の出力バッファと、

上記正極性側演算増幅器の出力および上記負極性側演算増幅器の出力の各々と、上記第1の出力バッファの入力および上記第2の出力バッファの入力の各々との間、並びに、上記正極性側演算増幅器および上記負極性側演算増幅器の帰還入力段に配置されたスイッチ群と、を含み、

上記スイッチ群は、

第1のモード時は、

上記正極性側演算増幅器で生成された正極性の信号電圧を上記第1の出力バッファに入力し、当該第1の出力バッファの出力を上記正極性側演算増幅器に帰還させ、

上記負極性側演算増幅器で生成された負極性の信号電圧を上記第2の出力バッファに入力し、当該第2の出力バッファの出力を上記負極性側演算増幅器に帰還させ、

第2のモード時は、

上記正極性側演算増幅器で生成された正極性の信号電圧を上記第2の出力バッファに入力し、当該第2の出力バッファの出力を上記正極性側演算増幅器に帰還させ、

上記負極性側演算増幅器で生成された負極性の信号電圧を上記第1の出力バッファに入力し、当該第1の出力バッファの出力を上記負極性側演算増幅器に帰還させ、

上記第1の出力バッファの出力と上記第1の信号線との間、並びに上記第2の出力バッファの出力と上記第2の信号線との間には、スイッチが介在しない

表示装置。 - 上記正極性側演算増幅器は、

第1導電型トランジスタの差動対を有し、

上記負極性側演算増幅器は、

第2導電型トランジスタの差動対を有し、

上記第1および第2の出力バッファは、

AB級プシュプル動作機能を有する

請求項4記載の表示装置。 - 上記第1および第2の出力バッファは、2つの入力端子を有する

請求項5記載の表示装置。 - 表示装置を有する電子機器であって、

上記表示装置は、

極性反転駆動される表示セルがマトリクス状に配置される表示部と、

上記極性反転に対応して上記表示セルに接続される信号線に正極性の信号電圧または負極性の信号電圧を供給する信号線駆動回路と、を有し、

上記信号線駆動回路は、

信号線を駆動する入力データを増幅し、正極性の信号電圧および負極性の信号電圧を生成し、対をなす第1の信号線および第2の信号線に正極性の信号電圧および負極性の信号電圧を選択的に供給する出力バッファ部を含み、

上記出力バッファ部は、

入力データを増幅し、正極性の信号電圧を生成する正極性側演算増幅器と、

入力データを増幅し、負極性の信号電圧を生成する負極性側演算増幅器と、

上記第1の信号線に正極性または負極性の信号電圧を供給する第1の出力バッファと、

上記第2の信号線に負極性または正極性の信号電圧を供給する第2の出力バッファと、

上記正極性側演算増幅器の出力および上記負極性側演算増幅器の出力の各々と、上記第1の出力バッファの入力および上記第2の出力バッファの入力の各々との間、並びに、上記正極性側演算増幅器および上記負極性側演算増幅器の帰還入力段に配置されたスイッチ群と、を含み、

上記スイッチ群は、

第1のモード時は、

上記正極性側演算増幅器で生成された正極性の信号電圧を上記第1の出力バッファに入力し、当該第1の出力バッファの出力を上記正極性側演算増幅器に帰還させ、

上記負極性側演算増幅器で生成された負極性の信号電圧を上記第2の出力バッファに入力し、当該第2の出力バッファの出力を上記負極性側演算増幅器に帰還させ、

第2のモード時は、

上記正極性側演算増幅器で生成された正極性の信号電圧を上記第2の出力バッファに入力し、当該第2の出力バッファの出力を上記正極性側演算増幅器に帰還させ、

上記負極性側演算増幅器で生成された負極性の信号電圧を上記第1の出力バッファに入力し、当該第1の出力バッファの出力を上記負極性側演算増幅器に帰還させ、

上記第1の出力バッファの出力と上記第1の信号線との間、並びに上記第2の出力バッファの出力と上記第2の信号線との間には、スイッチが介在しない

電子機器。

Priority Applications (6)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007338996A JP4466735B2 (ja) | 2007-12-28 | 2007-12-28 | 信号線駆動回路および表示装置、並びに電子機器 |

| US12/271,622 US9275596B2 (en) | 2007-12-28 | 2008-11-14 | Signal-line driving circuit, display device and electronic equipments |

| KR1020080117644A KR101531325B1 (ko) | 2007-12-28 | 2008-11-25 | 신호선구동 회로 및 표시장치 및 전자기기 |

| TW097148955A TWI405173B (zh) | 2007-12-28 | 2008-12-16 | 信號線驅動電路、顯示裝置及電子機器 |

| EP08022293.8A EP2075788B1 (en) | 2007-12-28 | 2008-12-22 | Signal-line driving circuit, display device and electronic equipments |

| CN2008101873141A CN101504816B (zh) | 2007-12-28 | 2008-12-26 | 信号线驱动电路、显示装置和电子设备 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007338996A JP4466735B2 (ja) | 2007-12-28 | 2007-12-28 | 信号線駆動回路および表示装置、並びに電子機器 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2009162789A JP2009162789A (ja) | 2009-07-23 |

| JP4466735B2 true JP4466735B2 (ja) | 2010-05-26 |

Family

ID=40377395

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2007338996A Expired - Fee Related JP4466735B2 (ja) | 2007-12-28 | 2007-12-28 | 信号線駆動回路および表示装置、並びに電子機器 |

Country Status (6)

| Country | Link |

|---|---|

| US (1) | US9275596B2 (ja) |

| EP (1) | EP2075788B1 (ja) |

| JP (1) | JP4466735B2 (ja) |

| KR (1) | KR101531325B1 (ja) |

| CN (1) | CN101504816B (ja) |

| TW (1) | TWI405173B (ja) |

Families Citing this family (29)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5236434B2 (ja) * | 2008-11-21 | 2013-07-17 | ラピスセミコンダクタ株式会社 | 表示パネルの駆動電圧出力回路 |

| KR101581723B1 (ko) * | 2008-12-26 | 2015-12-31 | 주식회사 동부하이텍 | 액정 패널 소스 드라이버를 위한 앰프 출력 보호회로 및 이의 동작 방법 |

| JP5172748B2 (ja) * | 2009-03-11 | 2013-03-27 | ルネサスエレクトロニクス株式会社 | 表示パネルドライバ及びそれを用いた表示装置 |

| CN102044204B (zh) * | 2009-10-13 | 2013-01-02 | 瑞鼎科技股份有限公司 | 驱动电路,应用其的电子显示装置与其驱动方法 |

| US8830155B2 (en) * | 2009-10-30 | 2014-09-09 | Au Optronics Corporation | Method and source driver for driving liquid crystal display |

| CN102081896B (zh) * | 2009-11-26 | 2013-02-13 | 奇景光电股份有限公司 | 源极驱动器、显示装置及显示面板的驱动方法 |

| KR101579839B1 (ko) * | 2009-12-23 | 2015-12-23 | 삼성전자주식회사 | 높은 슬루 레이트를 가지는 출력버퍼, 출력버퍼 제어방법 및 이를 구비하는 디스플레이 구동장치 |

| JP5374356B2 (ja) * | 2009-12-28 | 2013-12-25 | ラピスセミコンダクタ株式会社 | 駆動回路及び表示装置 |

| CN102195635A (zh) * | 2010-03-04 | 2011-09-21 | 联咏科技股份有限公司 | 可提高稳定性的输出缓冲电路 |

| TW201241815A (en) * | 2011-04-01 | 2012-10-16 | Fitipower Integrated Tech Inc | Source driver of LCD panel |

| CN102768824A (zh) * | 2011-05-05 | 2012-11-07 | 天钰科技股份有限公司 | 液晶显示器面板的源极驱动器 |

| CN103325346A (zh) * | 2012-03-22 | 2013-09-25 | 联咏科技股份有限公司 | 驱动控制方法及相关源极驱动器 |

| CN102721453B (zh) * | 2012-07-13 | 2014-09-03 | 广州市浩云安防科技股份有限公司 | 一种枪弹分离感知装置 |

| SG10201609410PA (en) * | 2015-11-30 | 2017-06-29 | Semiconductor Energy Lab | Semiconductor device, display panel, and electronic device |

| WO2018150290A1 (en) * | 2017-02-16 | 2018-08-23 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device, display panel, display device, input/output device, and data processing device |

| TWI630791B (zh) * | 2017-09-22 | 2018-07-21 | 奇景光電股份有限公司 | 通道放大器與應用於通道放大器的方法 |

| CN107610633B (zh) * | 2017-09-28 | 2020-12-04 | 惠科股份有限公司 | 一种显示面板的驱动装置及驱动方法 |

| KR102755209B1 (ko) * | 2018-06-15 | 2025-01-17 | 엘지디스플레이 주식회사 | 터치 디스플레이 장치, 데이터 구동 회로 및 컨트롤러의 구동 방법 |

| US10802636B2 (en) * | 2018-06-15 | 2020-10-13 | Lg Display Co., Ltd. | Touch display device, data driver circuit, and method of driving controller |

| CN111312182B (zh) * | 2018-12-12 | 2022-03-11 | 咸阳彩虹光电科技有限公司 | 一种源极驱动电路、液晶显示器及源极驱动方法 |

| KR102611010B1 (ko) * | 2018-12-24 | 2023-12-07 | 주식회사 엘엑스세미콘 | 소스 구동 회로 |

| TWI674757B (zh) * | 2019-02-13 | 2019-10-11 | 奕力科技股份有限公司 | 緩衝電路 |

| CN109903730B (zh) * | 2019-02-13 | 2021-04-06 | 奕力科技(开曼)股份有限公司 | 缓冲电路 |

| CN110728960A (zh) * | 2019-10-21 | 2020-01-24 | 湖南国科微电子股份有限公司 | Lcd驱动电路和显示设备 |

| US11196397B2 (en) * | 2019-12-31 | 2021-12-07 | Novatek Microelectronics Corp. | Current integrator for OLED panel |

| US11393375B2 (en) * | 2020-09-30 | 2022-07-19 | Himax Technologies Limited | Source driver and polarity inversion control circuit |

| JP7544624B2 (ja) * | 2021-02-19 | 2024-09-03 | ラピステクノロジー株式会社 | 出力回路、表示ドライバ及び表示装置 |

| CN113889043B (zh) * | 2021-09-30 | 2023-04-14 | 晟合微电子(肇庆)有限公司 | 显示驱动电路和显示面板 |

| CN113903316B (zh) * | 2021-10-19 | 2023-08-01 | 上海新相微电子股份有限公司 | 一种tft lcd驱动芯片对显示屏源极寄生电容电荷回收电路 |

Family Cites Families (22)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH10153986A (ja) | 1996-09-25 | 1998-06-09 | Toshiba Corp | 表示装置 |

| JP3369875B2 (ja) | 1996-11-12 | 2003-01-20 | 株式会社東芝 | 液晶駆動回路 |

| US6480178B1 (en) * | 1997-08-05 | 2002-11-12 | Kabushiki Kaisha Toshiba | Amplifier circuit and liquid-crystal display unit using the same |

| JP3550016B2 (ja) | 1998-03-03 | 2004-08-04 | 株式会社 日立ディスプレイズ | 液晶表示装置の駆動方法および映像信号電圧の出力方法 |

| US6304241B1 (en) | 1998-06-03 | 2001-10-16 | Fujitsu Limited | Driver for a liquid-crystal display panel |

| JP3481166B2 (ja) | 1999-07-16 | 2003-12-22 | 松下電器産業株式会社 | 液晶駆動装置 |

| JP4806481B2 (ja) | 1999-08-19 | 2011-11-02 | 富士通セミコンダクター株式会社 | Lcdパネル駆動回路 |

| JP3506235B2 (ja) | 2000-08-18 | 2004-03-15 | シャープ株式会社 | 液晶表示装置の駆動装置および駆動方法 |

| JP4744686B2 (ja) | 2000-12-06 | 2011-08-10 | ルネサスエレクトロニクス株式会社 | 演算増幅器 |

| JP4437378B2 (ja) * | 2001-06-07 | 2010-03-24 | 株式会社日立製作所 | 液晶駆動装置 |

| JP2003115729A (ja) | 2001-10-02 | 2003-04-18 | Seiko Epson Corp | Ab級アンプ |

| JP3908013B2 (ja) * | 2001-11-19 | 2007-04-25 | Necエレクトロニクス株式会社 | 表示制御回路及び表示装置 |

| JP3991306B2 (ja) | 2001-11-20 | 2007-10-17 | ソニー株式会社 | 増幅回路 |

| US6970152B1 (en) * | 2002-11-05 | 2005-11-29 | National Semiconductor Corporation | Stacked amplifier arrangement for graphics displays |

| KR100517734B1 (ko) * | 2003-12-12 | 2005-09-29 | 삼성전자주식회사 | 감마보정 디지털 아날로그 변환기 및 그 변환방법과, 이를사용한 소스구동 집적회로 및 평판표시장치 |

| JP4502207B2 (ja) | 2005-12-28 | 2010-07-14 | ルネサスエレクトロニクス株式会社 | 差動増幅器とデータドライバ及び表示装置 |

| TWI342000B (en) | 2006-01-03 | 2011-05-11 | Sunplus Technology Co Ltd | Driving circuit for tft liquid crystal display |

| KR100790977B1 (ko) * | 2006-01-13 | 2008-01-03 | 삼성전자주식회사 | 출력편차가 개선된 출력버퍼 및 이를 구비한평판표시장치용 소오스 드라이버 |

| JP4637077B2 (ja) * | 2006-10-17 | 2011-02-23 | パナソニック株式会社 | 駆動電圧出力回路、表示装置 |

| JP2008102345A (ja) | 2006-10-19 | 2008-05-01 | Nec Electronics Corp | 半導体集積回路装置 |

| JP4861791B2 (ja) * | 2006-10-27 | 2012-01-25 | ルネサスエレクトロニクス株式会社 | 演算増幅器及び表示装置 |

| KR100883030B1 (ko) * | 2007-02-28 | 2009-02-09 | 매그나칩 반도체 유한회사 | 평판 디스플레이의 구동 회로 및 방법 |

-

2007

- 2007-12-28 JP JP2007338996A patent/JP4466735B2/ja not_active Expired - Fee Related

-

2008

- 2008-11-14 US US12/271,622 patent/US9275596B2/en active Active

- 2008-11-25 KR KR1020080117644A patent/KR101531325B1/ko not_active Expired - Fee Related

- 2008-12-16 TW TW097148955A patent/TWI405173B/zh not_active IP Right Cessation

- 2008-12-22 EP EP08022293.8A patent/EP2075788B1/en not_active Not-in-force

- 2008-12-26 CN CN2008101873141A patent/CN101504816B/zh not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| TW200947408A (en) | 2009-11-16 |

| EP2075788A3 (en) | 2010-08-25 |

| EP2075788B1 (en) | 2013-06-19 |

| TWI405173B (zh) | 2013-08-11 |

| US9275596B2 (en) | 2016-03-01 |

| EP2075788A2 (en) | 2009-07-01 |

| KR101531325B1 (ko) | 2015-06-24 |

| CN101504816B (zh) | 2011-07-06 |

| CN101504816A (zh) | 2009-08-12 |

| JP2009162789A (ja) | 2009-07-23 |

| US20090167667A1 (en) | 2009-07-02 |

| KR20090072952A (ko) | 2009-07-02 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4466735B2 (ja) | 信号線駆動回路および表示装置、並びに電子機器 | |

| CN101930706B (zh) | 信号线驱动电路、显示装置和电子装置 | |

| JP3605829B2 (ja) | 電気光学装置の駆動回路、電気光学装置の駆動方法、電気光学装置及びこれを用いた電子機器 | |

| US7071669B2 (en) | Reference voltage generation circuit, display driver circuit, display device, and method of generating reference voltage | |

| US7079127B2 (en) | Reference voltage generation circuit, display driver circuit, display device, and method of generating reference voltage | |

| US7586504B2 (en) | Amplifier circuit, driving circuit of display apparatus, portable telephone and portable electronic apparatus | |

| JP4449189B2 (ja) | 画像表示装置およびその駆動方法 | |

| US7443239B2 (en) | Differential amplifier, data driver and display device | |

| US7907136B2 (en) | Voltage generation circuit | |

| US7495512B2 (en) | Differential amplifier, data driver and display device | |

| US20090040165A1 (en) | Amplifying circuit and display unit | |

| US20090096816A1 (en) | Data driver, integrated circuit device, and electronic instrument | |

| US20130342520A1 (en) | Digital-to-analog-conversion circuit and data driver for display device | |

| US20100013686A1 (en) | Sample and hold circuit and digital-to-analog converter circuit | |

| KR100607772B1 (ko) | 구동 파워가 높은 전압 폴로워형 연산 증폭기를 포함하는드라이버와 그것을 이용한 표시 장치 | |

| JP5017871B2 (ja) | 差動増幅器及びデジタルアナログ変換器 | |

| US8237649B2 (en) | Liquid crystal driving device | |

| KR100930154B1 (ko) | 타이밍 발생 회로, 표시 장치 및 휴대 단말기 | |

| JP2013218021A (ja) | データドライバと表示装置 | |

| US8823687B2 (en) | Signal line drive circuit, display device and electronic apparatus | |

| JP5086010B2 (ja) | Lcdパネル駆動回路 | |

| JP2009168842A (ja) | 基準電圧生成回路、ドライバ、電気光学装置及び電子機器 | |

| JP4962402B2 (ja) | 電気光学装置の駆動回路、電気光学装置および電子機器 | |

| JP2011013491A (ja) | 出力回路、信号線駆動回路および表示装置、並びに電子機器 | |

| JP2009169387A (ja) | 集積回路装置、電気光学装置及び電子機器 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20091110 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20091117 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100112 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20100202 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20100215 |

|

| R151 | Written notification of patent or utility model registration |

Ref document number: 4466735 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R151 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130305 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130305 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140305 Year of fee payment: 4 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |