JP4355202B2 - 受信機 - Google Patents

受信機 Download PDFInfo

- Publication number

- JP4355202B2 JP4355202B2 JP2003405024A JP2003405024A JP4355202B2 JP 4355202 B2 JP4355202 B2 JP 4355202B2 JP 2003405024 A JP2003405024 A JP 2003405024A JP 2003405024 A JP2003405024 A JP 2003405024A JP 4355202 B2 JP4355202 B2 JP 4355202B2

- Authority

- JP

- Japan

- Prior art keywords

- amplitude

- signal

- error component

- unit

- intermediate frequency

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03J—TUNING RESONANT CIRCUITS; SELECTING RESONANT CIRCUITS

- H03J1/00—Details of adjusting, driving, indicating, or mechanical control arrangements for resonant circuits in general

- H03J1/0008—Details of adjusting, driving, indicating, or mechanical control arrangements for resonant circuits in general using a central processing unit, e.g. a microprocessor

- H03J1/0058—Details of adjusting, driving, indicating, or mechanical control arrangements for resonant circuits in general using a central processing unit, e.g. a microprocessor provided with channel identification means

- H03J1/0066—Details of adjusting, driving, indicating, or mechanical control arrangements for resonant circuits in general using a central processing unit, e.g. a microprocessor provided with channel identification means with means for analysing the received signal strength

Landscapes

- Engineering & Computer Science (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Circuits Of Receivers In General (AREA)

- Superheterodyne Receivers (AREA)

- Noise Elimination (AREA)

Description

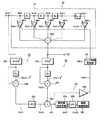

自動選局を行っていない受信時では、局部発信器12がユーザーから指定された放送局等の局発信号fcを出力し、混合検波器13が上述の混合検波を行うことによって、A/D変換器15からデジタルデータ列の中間周波信号DIFが出力される。

15…A/D変換器

18…振幅調整部

19…振幅監視部

20…マルチパス除去フィルタ

200…制御部

Claims (1)

- 受信アンテナで受信された高周波の受信信号を局発信号に基づいて混合検波することにより中間周波信号を出力するフロントエンド部と、

前記中間周波信号をアナログデジタル変換して、デジタルの中間周波信号を出力するA/D変換器と、

前記デジタルの中間周波信号の振幅を一定振幅にすべく調整して出力する振幅調整部と、

前記振幅調整部から出力される信号のマルチパス歪を除去して出力するマルチパス除去フィルタと、

前記局発信号の周波数を連続的に変化させて自動選局を行う制御部とを備え、

前記制御部は、自動選局に際し前記マルチパス除去フィルタのタップ係数を固定することを特徴とする受信機。

Priority Applications (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003405024A JP4355202B2 (ja) | 2003-12-03 | 2003-12-03 | 受信機 |

| DE602004027457T DE602004027457D1 (de) | 2003-12-03 | 2004-11-25 | Empfänger |

| EP04028089A EP1538750B1 (en) | 2003-12-03 | 2004-11-25 | Receiver |

| US11/000,977 US20050123079A1 (en) | 2003-12-03 | 2004-12-02 | Receiver |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003405024A JP4355202B2 (ja) | 2003-12-03 | 2003-12-03 | 受信機 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2005167719A JP2005167719A (ja) | 2005-06-23 |

| JP2005167719A5 JP2005167719A5 (ja) | 2006-02-16 |

| JP4355202B2 true JP4355202B2 (ja) | 2009-10-28 |

Family

ID=34463986

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2003405024A Expired - Fee Related JP4355202B2 (ja) | 2003-12-03 | 2003-12-03 | 受信機 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US20050123079A1 (ja) |

| EP (1) | EP1538750B1 (ja) |

| JP (1) | JP4355202B2 (ja) |

| DE (1) | DE602004027457D1 (ja) |

Families Citing this family (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN100530984C (zh) * | 2004-04-27 | 2009-08-19 | 三菱电机株式会社 | 无线装置 |

| JP4230470B2 (ja) * | 2005-03-31 | 2009-02-25 | 富士通テン株式会社 | 軽減装置および方法、ならびに受信装置 |

| WO2009075100A1 (ja) * | 2007-12-12 | 2009-06-18 | Panasonic Corporation | 無線回路装置 |

| JP2009165112A (ja) * | 2007-12-12 | 2009-07-23 | Panasonic Corp | 無線回路装置 |

| JP5393412B2 (ja) * | 2009-11-18 | 2014-01-22 | 三菱電機株式会社 | 受信装置および復調方法 |

| JP5691186B2 (ja) * | 2010-02-10 | 2015-04-01 | アイコム株式会社 | 自動周波数制御装置および無線通信機 |

| US9774364B2 (en) * | 2015-09-04 | 2017-09-26 | Futurewei Technologies, Inc. | Interference phase estimate system and method |

| US10097214B2 (en) * | 2015-11-30 | 2018-10-09 | Metal Industries Research & Development Centre | Error correcting method |

Family Cites Families (20)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH02170626A (ja) * | 1988-12-22 | 1990-07-02 | Clarion Co Ltd | マルチパス歪抑圧方式 |

| JPH0831820B2 (ja) * | 1989-11-17 | 1996-03-27 | 日本電気株式会社 | 判定帰還形等化器 |

| US5640698A (en) * | 1995-06-06 | 1997-06-17 | Stanford University | Radio frequency signal reception using frequency shifting by discrete-time sub-sampling down-conversion |

| US5701600A (en) * | 1995-07-17 | 1997-12-23 | Motorola, Inc. | Radio receiver and method of calibrating same |

| US5758274A (en) * | 1996-03-13 | 1998-05-26 | Symbol Technologies, Inc. | Radio frequency receiver with automatic gain control |

| JPH09284808A (ja) * | 1996-04-11 | 1997-10-31 | Sony Corp | データ伝送装置 |

| JPH09321559A (ja) * | 1996-05-24 | 1997-12-12 | Oki Electric Ind Co Ltd | 自動利得制御回路 |

| KR100242665B1 (ko) * | 1997-08-01 | 2000-02-01 | 김영환 | 데이터 변환부를 구비한 칼라 액정표시 구동장치 |

| KR100239413B1 (ko) * | 1997-10-14 | 2000-01-15 | 김영환 | 액정표시소자의 구동장치 |

| US6324228B1 (en) * | 1998-12-30 | 2001-11-27 | International Business Machines Corporation | Method and apparatus for robust frequency tracking in strong channel interference using carrier signal relative strength and frequency error |

| US6363127B1 (en) * | 1999-06-23 | 2002-03-26 | At&T Wireless Services, Inc. | Automatic gain control methods and apparatus suitable for use in OFDM receivers |

| KR100617778B1 (ko) * | 1999-07-07 | 2006-08-28 | 삼성전자주식회사 | 수신신호 열화 보상장치 및 방법 |

| JP3518430B2 (ja) * | 1999-07-12 | 2004-04-12 | 三菱電機株式会社 | デジタルfm復調器 |

| US6795494B1 (en) * | 2000-05-12 | 2004-09-21 | National Semiconductor Corporation | Receiver architecture using mixed analog and digital signal processing and method of operation |

| DE10060425A1 (de) * | 2000-12-05 | 2002-06-13 | Infineon Technologies Ag | Empfängerschaltung |

| US7405732B2 (en) * | 2000-12-07 | 2008-07-29 | Renesas Technology Corp. | Semiconductor integrated circuit, liquid crystal drive device, and liquid crystal display system |

| JP3533187B2 (ja) * | 2001-01-19 | 2004-05-31 | Necエレクトロニクス株式会社 | カラー液晶ディスプレイの駆動方法、その回路及び携帯用電子機器 |

| US7346134B2 (en) * | 2001-05-15 | 2008-03-18 | Finesse Wireless, Inc. | Radio receiver |

| JP3981539B2 (ja) * | 2001-08-28 | 2007-09-26 | Necエレクトロニクス株式会社 | 半導体集積回路装置 |

| US7085334B2 (en) * | 2002-09-30 | 2006-08-01 | Lsi Logic Corporation | Automatic gain control with analog and digital gain |

-

2003

- 2003-12-03 JP JP2003405024A patent/JP4355202B2/ja not_active Expired - Fee Related

-

2004

- 2004-11-25 DE DE602004027457T patent/DE602004027457D1/de active Active

- 2004-11-25 EP EP04028089A patent/EP1538750B1/en not_active Expired - Fee Related

- 2004-12-02 US US11/000,977 patent/US20050123079A1/en not_active Abandoned

Also Published As

| Publication number | Publication date |

|---|---|

| EP1538750A3 (en) | 2009-04-29 |

| EP1538750A2 (en) | 2005-06-08 |

| JP2005167719A (ja) | 2005-06-23 |

| US20050123079A1 (en) | 2005-06-09 |

| DE602004027457D1 (de) | 2010-07-15 |

| EP1538750B1 (en) | 2010-06-02 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| EP1018803B1 (en) | Automatic gain control method and device | |

| JP4355202B2 (ja) | 受信機 | |

| JP4205509B2 (ja) | マルチパスひずみ除去フィルタ | |

| JP4294455B2 (ja) | 受信機 | |

| US20040087287A1 (en) | Automatic gain control system | |

| JP4263586B2 (ja) | マルチパス除去フィルタ | |

| JP2015115680A (ja) | 信号処理装置、信号処理方法、並びにプログラム | |

| JP4274408B2 (ja) | 自動利得制御装置、受信装置及び利得制御方法 | |

| US7054395B2 (en) | Automatic gain control for digital demodulation apparatus | |

| JP4281260B2 (ja) | Fm復調器および受信機 | |

| JP2011166191A (ja) | 放送受信装置 | |

| JP4489321B2 (ja) | デジタル復調装置 | |

| JP2003152540A (ja) | 信号レベル制御装置 | |

| JP3165520B2 (ja) | 受信機 | |

| JP2003318679A (ja) | 受信装置及び通信装置 | |

| JP5179975B2 (ja) | 信号処理装置 | |

| JP4469515B2 (ja) | ディジタルフィルタ | |

| JP4532568B2 (ja) | 適応ディジタルフィルタ及び受信装置 | |

| US7734268B2 (en) | Method and apparatus for leveling an increasing or decreasing slope of an AM modulated receiving signal | |

| JP4929041B2 (ja) | ノイズ除去装置、その方法、ノイズ除去プログラム及びその記録媒体 | |

| JP2003209450A (ja) | 自動利得制御回路及び自動利得制御方法 | |

| JPH1141068A (ja) | ディジタル自動周波数制御回路 | |

| JP2000261340A (ja) | デジタル放送受信機 | |

| JP2009213096A (ja) | 自動利得制御装置 | |

| JPH0969790A (ja) | マルチパス歪低減回路 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20051221 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20061101 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20090324 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20090327 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090521 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20090612 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090706 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20090728 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20090731 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120807 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130807 Year of fee payment: 4 |

|

| LAPS | Cancellation because of no payment of annual fees |