JP4041663B2 - 半導体装置及びその検査装置 - Google Patents

半導体装置及びその検査装置 Download PDFInfo

- Publication number

- JP4041663B2 JP4041663B2 JP2001276530A JP2001276530A JP4041663B2 JP 4041663 B2 JP4041663 B2 JP 4041663B2 JP 2001276530 A JP2001276530 A JP 2001276530A JP 2001276530 A JP2001276530 A JP 2001276530A JP 4041663 B2 JP4041663 B2 JP 4041663B2

- Authority

- JP

- Japan

- Prior art keywords

- semiconductor device

- pads

- inspection

- substrate

- pad

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P74/00—Testing or measuring during manufacture or treatment of wafers, substrates or devices

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P74/00—Testing or measuring during manufacture or treatment of wafers, substrates or devices

- H10P74/27—Structural arrangements therefor

- H10P74/273—Interconnections for measuring or testing, e.g. probe pads

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C29/00—Checking stores for correct operation ; Subsequent repair; Testing stores during standby or offline operation

- G11C29/04—Detection or location of defective memory elements, e.g. cell constructio details, timing of test signals

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C29/00—Checking stores for correct operation ; Subsequent repair; Testing stores during standby or offline operation

- G11C29/04—Detection or location of defective memory elements, e.g. cell constructio details, timing of test signals

- G11C29/08—Functional testing, e.g. testing during refresh, power-on self testing [POST] or distributed testing

- G11C29/12—Built-in arrangements for testing, e.g. built-in self testing [BIST] or interconnection details

- G11C29/1201—Built-in arrangements for testing, e.g. built-in self testing [BIST] or interconnection details comprising I/O circuitry

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C29/00—Checking stores for correct operation ; Subsequent repair; Testing stores during standby or offline operation

- G11C29/04—Detection or location of defective memory elements, e.g. cell constructio details, timing of test signals

- G11C29/08—Functional testing, e.g. testing during refresh, power-on self testing [POST] or distributed testing

- G11C29/12—Built-in arrangements for testing, e.g. built-in self testing [BIST] or interconnection details

- G11C2029/1206—Location of test circuitry on chip or wafer

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P74/00—Testing or measuring during manufacture or treatment of wafers, substrates or devices

- H10P74/27—Structural arrangements therefor

- H10P74/277—Circuits for electrically characterising or monitoring manufacturing processes, e.g. circuits in tested chips or circuits in testing wafers

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/90—Bond pads, in general

- H10W72/931—Shapes of bond pads

- H10W72/932—Plan-view shape, i.e. in top view

Landscapes

- Testing Or Measuring Of Semiconductors Or The Like (AREA)

- Semiconductor Integrated Circuits (AREA)

- Tests Of Electronic Circuits (AREA)

- Measuring Leads Or Probes (AREA)

Description

【発明の属する技術分野】

本発明は、半導体装置及びその検査装置に関する。

【0002】

【従来の技術】

半導体装置を用いた電子機器等の高密度実装、高機能化等を反映して、半導体装置自体の高集積化の要求が増加している。

【0003】

一般に、半導体装置の高集積化は、半導体装置を構成する回路素子の微細化により達成される。すなわち、回路素子を構成する配線あるいは接続孔等の微細加工により高集積化が図られる。

【0004】

一方、半導体装置のコスト削減、歩留まりの向上を図るためには、1枚のウエハ内に形成される半導体チップの数をできるだけ増加させる技術が必要とされる。すなわち、同一機能を実現できる回路をできるだけ小さなチップ面積で実現するように設計及び製造プロセスを最適化して微細化する技術が必要となる。

【0005】

例えば、DRAM(Dynamic Random Access Memory)のように、同一機能が実現される同一世代の製品群では、市場投入の初期の段階では比較的設計ルールの緩い条件で設計が行われる。このため、チップサイズは比較的大きくなり、コストもそれに対応して幾分高くなる。

【0006】

ところが、市場投入の中期あるいは後期の段階では、微細化の努力の結果、チップサイズが縮小され、チップ1個あたりのコストの削減と歩留まりの向上とが同時に達成されるようになる。

【0007】

このようなチップサイズの縮小は、同一世代の製品群で数次にわたって実施され、また、製品の世代が変わるごとにチップサイズの縮小が繰り返される。この結果、チップ表面に形成される配線パターンも同時に縮小され、それに従い、半導体装置を検査するための検査用パッドのサイズ及びパッドピッチも必然的に縮小される。

【0008】

このように、パッドピッチの縮小、1ウエハ当たりのチップ数の増加による検査パッドの増加により、これまでの検査方式では検査すること自体が困難となっている。

【0009】

そこで、特開平11−274251号公報に記載されているように、半導体装置と同じシリコン基板にプローブ、梁、配線、2次電極パッドが検査用基板に形成され、複数の梁のそれぞれに形成された突起状のプローブが、半導体装置に形成された所定のパッドに接触されて、検査を行う方法などが開発されている。

【0010】

また、特開2000−227459号公報に記載されているように、半導体チップにBIST(Built-In Self Test)回路を組み込んで、簡単な検査を行えるような工夫がされているものも有る。

【0011】

【発明が解決しようとする課題】

しかしながら、さらに半導体装置における高集積化が望まれており、パッド数の増加と配置領域の縮小化に伴い、パッドピッチのさらなる縮小化が必要となっているが、半導体装置のパッドピッチの縮小化に対応可能な検査装置の検査用基板の製作が困難となる恐れがある。

【0012】

つまり、上述したように、半導体装置の検査装置は、シリコン基板にプローブ、梁、配線、2次電極パッドが形成されるが、プローブ半導体装置のパッドピッチに縮小化に伴い、複数の梁も、その幅を狭くする必要があり、従来と同様なパッドの配置のままであると、それに対応させて形成する複数の梁は強度的に問題があり、制作困難となる。

【0013】

本発明の目的は、チップサイズが縮小化され、パッドピッチが縮小化された半導体装置であっても、検査装置により有効に検査可能な半導体装置及びその検査装置を実現することである。

【0014】

【課題を解決するための手段】

上記目的を達成するため、本発明は、次のように構成される。

(1)半導体基板の主面上に複数の入出力用のパッドを有する半導体装置において、BIST回路を備え、上記複数の入出力用のパッドは、上記主面の両端部に分割して、少なくとも一列に配置され、これら複数のパッドは半導体装置の電気的検査に用いられる複数の検査用パッドを含み、これら検査用パッドは2つの群に分割され、上記主面を、この主面の四隅のうちの一つをそれぞれ含む4つの領域に分割したとき、対角配置となる領域に形成された複数のパッドに、上記2つに分割された検査用パッドのそれぞれが含まれ、かつ、上記対角配置となる領域のいずれか一方の領域に形成された検査用パッドは上記BIST回路専用のパッドである。

【0015】

(2)複数の梁と、これら複数の梁のそれぞれに形成され、半導体装置に形成される電気的検査用のパッドに接触されるプローブと、これらのプローブに接続線を介して電気的に接続され、信号の入出力用の複数の2次電極パッドとを有する基板を備え、上記(1)に記載の半導体装置の検査を行う検査装置において、上記複数の梁は、2つの群に分割され、上記基板を、この基板の四隅のうちの一つをそれぞれ含む4つの領域に分割したとき、対角配置となる領域であって、上記プローブが基板の端部領域に位置するように形成される。

【0016】

(3)複数の梁と、これら複数の梁のそれぞれに形成され、半導体装置に形成される電気的検査用のパッドに接触されるプローブと、これらのプローブに接続線を介して電気的に接続され、信号の入出力用の複数の2次電極パッドとを有する基板を備え、上記( 1 )に記載の半導体装置の検査を行う検査装置において、上記複数の梁は、2つの群に分割され、上記基板を、この基板の四隅のうちの一つをそれぞれ含む4つの領域に分割したとき、対角配置となる領域であって、上記プローブが基板の中央領域の近辺に位置するように形成される。

【0019】

検査用パッドが半導体装置の、対角配置となる領域に形成されると、これら検査用パッドに接触するための検査装置のプローブが形成される複数の梁が、対角領域に二分割することができる。上記複数の梁を、対角配置ではなく、対向配置とすると、強度的に問題があり、検査装置の制作が困難となる。

【0020】

対角配置の領域に梁を形成することにより、検査装置における基板の強度的な問題は解消し、検査装置の制作上の困難性も解消することができる。

【0021】

【発明の実施の形態】

以下、本発明に係る実施の形態を添付図面を参照して説明する。

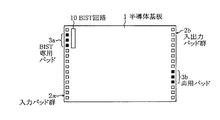

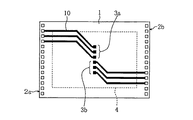

図1は、本発明の一実施形態である半導体装置のパッド位置の説明図である。図1において、半導体基板1の主面上の両端部には、複数のパッド2a、2bが一列に形成されている。これは、半導体装置の縮小化、回路素子の増加に伴い、パッドの増加及びパッドピッチが縮小化され、これに対処すべく、複数のパッドを両端部に分離して配置したものである。

【0022】

そして、入力パッド群2aが図1の半導体装置1の左端に配置され、入出力パッド群2bが図1の半導体装置1の右端に配置される。

【0023】

また、BIST(Built-In Self Test)回路10は、図1の半導体装置1の左端上側部分に配置され、このBIST回路10の近辺に位置されたパッドがBIST専用パッド3aとなる。

【0024】

ここで、BIST用のパッドは、多数必要であるが、上述したように、入力パッド等の増加に伴い、BIST用のパッドを配置する領域が制限され、全てのBIST用のパッドを半導体装置1の一端側に一列に配置することはできない。

【0025】

このため、BIST用のパッドの配置領域を半導体装置の両端部に分割し、かつ、BIST回路10の近辺に配置されたものを、BIST専用パッド3aとし、他の領域に配置されるものをBIST用と他の用途の共用パッド3bとする。

【0026】

さらに、BIST専用パッド3aと3bとは、半導体装置1の上領域と下領域とに分割して配置する。したがって、BIST専用パッド3aは、半導体装置1の左端上領域に配置され、共用パッド3bは、半導体装置1の右端下領域に配置される。

【0027】

その理由は、BIST専用パッド3aを半導体装置1の左端上領域に配置し、共用パッド3bを半導体装置1の右端上領域に配置すると、パッド3aに接触するための検査装置のプローブが形成される梁と、パッド3b接触するためのプローブが形成される梁とは、共にシリコン基板からなる検査装置の上領域に形成されることとなる。

【0028】

上記多数の梁を全て、検査装置の上領域に形成すると、強度的に問題があり、検査装置の制作が困難となる。

【0029】

そこで、BIST専用パッド3aを半導体装置1の左端上領域に配置し、共用パッド3bを半導体装置1の右端下領域に配置することにより、検査装置の多数の梁を、そのシリコン基板の左端上領域と、右端下領域とに分けて配置する。これにより、検査装置のシリコン基板の上領域のみ、又は下領域のみに、多数の梁を形成する必要はないので、強度的な問題は解消し、検査装置の制作上の困難性も解消することができる。

【0030】

ここで、左端上領域とは、半導体基板1の図1上の左端面から測定して、1パッド分の寸法の距離の位置から1〜2パッド分の寸法までの端部側領域であって、半導体基板1を図1上の上下方向に二分割したときの上領域とする。

【0031】

また、右端下領域とは、半導体基板1の図1上の右端面から測定して、1パッド分の寸法の距離の位置から1〜2パッド分の寸法までの端部側領域であって、半導体基板1を図1上の上下方向に二分割したときの下領域とする。

【0032】

したがって、パッド3aと3bとは、半導体装置1の主面を、この主面の四隅のうちの一つをそれぞれ含む4つの領域に分割したとき、対角配置となる領域に形成されたパッド群に含まれることとなる。

【0033】

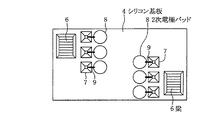

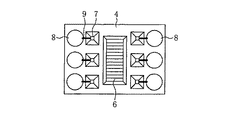

図2は、本発明の一実施形態である検査装置の一方の面からみた平面図である。また、図3は、本発明の一実施形態である検査装置の他方の面からみた平面図である。

図3において、シリコン基板4の他方の面の左端上領域と、右端下領域とに分割して複数の梁6が形成されている。そして、これら複数の梁のそれぞれにプローブ5が形成されている。これら複数のプローブ5が、半導体装置のBIST専用パッド3a及び共用パッド3bに接触するように、これらパッド3a及び3bの位置に対応する位置に配置されている。

【0034】

プローブ5は、金属配線9と接続され、この金属配線9は、貫通孔7を介して、シリコン基板4の一方の面に延びている。

【0035】

そして、図2に示すように、金属配線9は、2次電極パッド8に接続される。この2次電極パッド8には、検査信号発生回路(図示せず)からの検査信号が供給される。

【0036】

さて、一般に半導体装置は次のような検査を受けるが、この検査は、半導体基板上に形成された複数の検査用パッド3a、3bと、テスタとの導通を得ることにより行われる。

【0037】

P検と呼ばれる各素子の電気信号の導通を検査するものや、バーンインと呼ばれる、回路に熱的、電気的ストレスを付与して不良を加速選別するものなどがある。P検は通常、プローブ装置を用いて各プローブを回路中の電極パッドに一つずつ接触させて行われる。

【0038】

一方、バーンイン検査では、BIST回路10を用いることにより、検査に必要なパッドを1チップあたり6個程度に抑えることができる。BIST回路とは、半導体装置自体に予め作り込まれた、検査を行うための回路のことをいい、ここでは最低限検査に必要な電源線と信号線のみをまとめて引き出すための回路である。

【0039】

上述したような検査が図2及び図3に示した検査装置により行われる。

【0040】

以上のように、本発明の一実施形態である半導体装置によれば、入出力用の多数のパッドを半導体装置の両端部に分割して配列し、これら多数のパッドのうち、BIST用のパッドの配置領域を半導体装置の一方端の上領域と他方端の下領域とに分割して配置し、一方の領域に配置されるBIST用のパッドを、他の用途と共用とされる。

【0041】

これにより、チップサイズが縮小化され、パッドピッチが縮小化された半導体装置であっても、検査装置により有効に検査可能な半導体装置を実現することができる。

【0042】

また、半導体装置の検査装置において、多数の梁を、シリコン基板の左端上領域と、右端下領域とに分けて配置することにより、つまり、多数の梁を、2つの群に分割し、上記シリコン基板を、このシリコン基板の四隅のうちの一つをそれぞれ含む4つの領域に分割したとき、対角配置となる領域であって、プローブがシリコン基板の端部領域に位置するように形成することにより、シリコン基板の上領域のみ、又は下領域のみに多数の梁を形成する必要はなく、強度的な問題は解消し、検査装置の制作上の困難性も解消することができる。

【0043】

したがって、チップサイズが縮小化され、パッドピッチが縮小化された半導体装置であっても、有効に検査可能な検査装置を実現することができる。

【0044】

さて、複数の半導体装置を複数の検査装置により、一括して検査する方式、つまり、チップ単位に切断される前の、ウエハ上の複数の半導体装置を複数の検査装置により検査する方式が近年採用されている。

【0045】

この場合の、本発明の他の実施形態である検査装置について説明する。

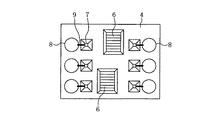

図4は、本発明の一実施形態である半導体装置1が複数個配置されて、検査される場合の状態の説明図である。

【0046】

複数の半導体装置1は互いに隣接して配置され、一つの検査装置により、一方の半導体装置1の共用パッド3bと隣接する他方の半導体装置1のBIST専用パッド3aとが検査される。

【0047】

図5は、本発明の他の実施形態である検査装置の一方の面の平面図であり、図6は、本発明の上記他の実施形態である検査装置の他方の面の平面図である。

【0048】

図6において、シリコン基板4の他方の面の中央左側上領域と、中央右側下領域とに分割して複数の梁6が形成されている。そして、これら複数の梁6のそれぞれにプローブ5が形成されている。これら複数のプローブ5が、一方の半導体装置1のBIST専用パッド3a及び他方の半導体装置1の共用パッド3bに接触するように、これらパッド3a及び3bの位置に対応する位置に配置されている。

【0049】

つまり、多数の梁6は、2つの群に分割され、基板4を、この基板4の四隅のうちの一つをそれぞれ含む4つの領域に分割したとき、対角配置となる領域であって、プローブ5が基板の中央領域の近辺に位置するように形成される。

【0050】

プローブ5は、金属配線9と接続され、この金属配線9は、貫通孔7を介して、シリコン基板4の一方の面に延びている。

【0051】

そして、図5に示すように、金属配線9は、シリコン基板4の両端側に配置された2次電極パッド8に接続される。この2次電極パッド8には、検査信号発生回路(図示せず)からの検査信号が供給される。

【0052】

以上のように、本発明の他の実施形態である検査装置によれば、チップサイズが縮小化され、パッドピッチが縮小化された半導体装置であっても、有効に検査可能な検査装置を実現することができる。

【0053】

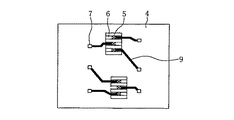

図7は、本発明の他の実施形態である半導体装置のパッド位置の説明図である。図7において、半導体基板1の両端部には、複数のパッド2a、2bが形成されている。

【0054】

そして、半導体装置1の中央部には、BIST専用パッド3a(プローブ接触用パッド)と、共用パッド3b(プローブ接触用パッド)とが形成されており、BIST専用パッド3aは、半導体装置1の左端上領域のパッド2aに配線10により接続され、共用パッド3bは、半導体装置1の右端下領域のパッド2bに配線10により接続されている。

【0055】

この図7の例は、半導体装置1の中央領域にパッド3a、3bを形成可能な空き領域が存在する場合やWPP(Wafer Process Package)のように、半導体装置上にさらに一層再配線層を形成し、半導体装置の中央領域にパッドを形成可能な場合の例である。

【0056】

図8は、図7に示した半導体装置1を検査するための検査装置であって、本発明のさらに他の実施形態である検査装置の一方の面の平面図であり、図9は、図8に示した検査装置の他方の面の平面図である。

【0057】

図9において、シリコン基板4の他方の面の中央領域に複数の梁6が形成されている。そして、これら複数の梁6のそれぞれにプローブ5が形成されている。これら複数のプローブ5が、半導体装置1のBIST専用パッド3a及び共用パッド3bに接触するように、これらパッド3a及び3bの位置に対応する位置に配置されている。

【0058】

プローブ5は、金属配線9と接続され、この金属配線9は、貫通孔7を介して、シリコン基板4の一方の面に延びている。

【0059】

そして、図8に示すように、金属配線9は、シリコン基板4の両端側に配置された2次電極パッド8に接続される。この2次電極パッド8には、検査信号発生回路(図示せず)からの検査信号が供給される。

【0060】

以上のように、本発明の他の実施形態である半導体装置によれば、チップサイズが縮小化され、パッドピッチが縮小化された半導体装置であっても、有効に検査可能な検査装置を実現することができる。

【0061】

また、チップサイズが縮小化され、パッドピッチが縮小化された半導体装置であっても、有効に検査可能な検査装置を実現することができる。

【0062】

また、本発明のさらに他の実施形態である検査装置によれば、多数の梁6が2箇所に分割されず形成されるので、検査装置全体の面積を小さくすることができ、検査のための位置決めスペースを多く確保することができる。

【0063】

なお、本発明の実施形態である半導体装置において、入出力パッド群2a、2bは、半導体基板2の端面からどの位の位置まで形成し得るかにより、パッドの形成領域が決定され、形成し得るパッドの数も決定される。本発明の実子形態においては、半導体基板2の端面から1パッド分の寸法まで、パッドを形成し得る領域とすることができる。

【0064】

【発明の効果】

本発明によれば、チップサイズが縮小化され、パッドピッチが縮小化された半導体装置であっても、検査装置により有効に検査可能な半導体装置及びその検査装置を実現することができる。

【図面の簡単な説明】

【図1】本発明の一実施形態である半導体装置のパッド位置の説明図である。

【図2】本発明の一実施形態である検査装置の一方の面からみた平面図である。

【図3】本発明の一実施形態である検査装置の他方の面からみた平面図である。

【図4】本発明の他の実施形態である検査装置の説明図である。

【図5】本発明の他の実施形態である検査装置の一方の面からみた平面図である。

【図6】本発明の他の実施形態である検査装置の他方の面からみた平面図である。

【図7】本発明の他の実施形態である半導体装置のパッド位置の説明図である。

【図8】本発明のさらに他の実施形態である検査装置の一方の面からみた平面図である。

【図9】本発明のさらに他の実施形態である検査装置の他方の面からみた平面図である。

【符号の説明】

1 半導体装置基板

2a、2b パッド群

3a BIST専用パッド

3b 共用パッド

4 シリコン基板

5 プローブ

6 梁

7 貫通孔

8 2次電極パッド

9 配線

10 BIST回路

Claims (3)

- 半導体基板の主面上に複数の入出力用のパッドを有する半導体装置において、

BIST回路を備え、

上記複数の入出力用のパッドは、上記主面の両端部に分割して、少なくとも一列に配置され、これら複数のパッドは半導体装置の電気的検査に用いられる複数の検査用パッドを含み、これら検査用パッドは2つの群に分割され、上記主面を、この主面の四隅のうちの一つをそれぞれ含む4つの領域に分割したとき、対角配置となる領域に形成された複数のパッドに、上記2つに分割された検査用パッドのそれぞれが含まれ、かつ、上記対角配置となる領域のいずれか一方の領域に形成された検査用パッドは上記BIST回路専用のパッドであることを特徴とする半導体装置。 - 複数の梁と、これら複数の梁のそれぞれに形成され、半導体装置に形成される電気的検査用のパッドに接触されるプローブと、これらのプローブに接続線を介して電気的に接続され、信号の入出力用の複数の2次電極パッドとを有する基板を備え、請求項 1 に記載の半導体装置の検査を行う検査装置において、

上記複数の梁は、2つの群に分割され、上記基板を、この基板の四隅のうちの一つをそれぞれ含む4つの領域に分割したとき、対角配置となる領域であって、上記プローブが基板の端部領域に位置するように形成されることを特徴とする半導体装置の検査装置。 - 複数の梁と、これら複数の梁のそれぞれに形成され、半導体装置に形成される電気的検査用のパッドに接触されるプローブと、これらのプローブに接続線を介して電気的に接続され、信号の入出力用の複数の2次電極パッドとを有する基板を備え、請求項 1 に記載の半導体装置の検査を行う検査装置において、

上記複数の梁は、2つの群に分割され、上記基板を、この基板の四隅のうちの一つをそれぞれ含む4つの領域に分割したとき、対角配置となる領域であって、上記プローブが基板の中央領域の近辺に位置するように形成されることを特徴とする半導体装置の検査装置。

Priority Applications (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2001276530A JP4041663B2 (ja) | 2001-09-12 | 2001-09-12 | 半導体装置及びその検査装置 |

| TW091113300A TW546756B (en) | 2001-09-12 | 2002-06-18 | Semiconductor device and test device thereof |

| US10/218,596 US6885208B2 (en) | 2001-09-12 | 2002-08-15 | Semiconductor device and test device for same |

| CNB021421846A CN1213470C (zh) | 2001-09-12 | 2002-08-29 | 半导体器件及其检查装置 |

| KR10-2002-0054725A KR100467913B1 (ko) | 2001-09-12 | 2002-09-10 | 반도체장치 및 그 검사장치 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2001276530A JP4041663B2 (ja) | 2001-09-12 | 2001-09-12 | 半導体装置及びその検査装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2003084042A JP2003084042A (ja) | 2003-03-19 |

| JP4041663B2 true JP4041663B2 (ja) | 2008-01-30 |

Family

ID=19101212

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2001276530A Expired - Fee Related JP4041663B2 (ja) | 2001-09-12 | 2001-09-12 | 半導体装置及びその検査装置 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US6885208B2 (ja) |

| JP (1) | JP4041663B2 (ja) |

| KR (1) | KR100467913B1 (ja) |

| CN (1) | CN1213470C (ja) |

| TW (1) | TW546756B (ja) |

Families Citing this family (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2004102653A1 (ja) * | 2003-05-15 | 2004-11-25 | Shinko Electric Industries Co., Ltd. | 半導体装置およびインターポーザー |

| KR20050011082A (ko) * | 2003-07-21 | 2005-01-29 | 매그나칩 반도체 유한회사 | 확장된 내부 프로빙 패드를 갖는 반도체 칩 |

| JP2005136246A (ja) * | 2003-10-31 | 2005-05-26 | Renesas Technology Corp | 半導体集積回路装置の製造方法 |

| CA2634131C (en) * | 2005-12-21 | 2014-02-11 | Wyeth | Protein formulations with reduced viscosity and uses thereof |

| US8399973B2 (en) | 2007-12-20 | 2013-03-19 | Mosaid Technologies Incorporated | Data storage and stackable configurations |

| KR101212723B1 (ko) * | 2010-05-31 | 2012-12-14 | 에스케이하이닉스 주식회사 | 반도체 장치 |

| KR102107147B1 (ko) | 2013-02-01 | 2020-05-26 | 삼성전자주식회사 | 패키지 온 패키지 장치 |

| CN108206140B (zh) * | 2016-12-19 | 2020-11-24 | 中芯国际集成电路制造(上海)有限公司 | 半导体器件及其制作方法、电子装置 |

Family Cites Families (19)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CA954635A (en) * | 1972-06-06 | 1974-09-10 | Microsystems International Limited | Mounting leads and method of fabrication |

| JPS61148829A (ja) * | 1984-12-24 | 1986-07-07 | Toshiba Seiki Kk | ワイヤボンデイング方法 |

| JPS63148829A (ja) * | 1986-12-11 | 1988-06-21 | 古河電池株式会社 | 定電流回路 |

| JPH04174538A (ja) * | 1990-08-02 | 1992-06-22 | Hitachi Ltd | 半導体集積回路装置の製造方法 |

| JPH04278560A (ja) * | 1991-03-07 | 1992-10-05 | Nec Yamagata Ltd | 半導体装置の製造方法 |

| JPH09107048A (ja) * | 1995-03-30 | 1997-04-22 | Mitsubishi Electric Corp | 半導体パッケージ |

| US5929650A (en) * | 1997-02-04 | 1999-07-27 | Motorola, Inc. | Method and apparatus for performing operative testing on an integrated circuit |

| JPH1154562A (ja) * | 1997-08-05 | 1999-02-26 | Shinko Electric Ind Co Ltd | 半導体パッケージ |

| US6427222B1 (en) * | 1997-09-30 | 2002-07-30 | Jeng-Jye Shau | Inter-dice wafer level signal transfer methods for integrated circuits |

| JPH11243120A (ja) * | 1998-02-25 | 1999-09-07 | Matsushita Electron Corp | 半導体装置およびその製造方法 |

| JP4006081B2 (ja) | 1998-03-19 | 2007-11-14 | 株式会社ルネサステクノロジ | 半導体装置の製造方法 |

| JPH11281757A (ja) * | 1998-03-30 | 1999-10-15 | Fujitsu Ltd | 大気汚染物質測定システム |

| US6061814A (en) * | 1998-04-21 | 2000-05-09 | Lsi Logic Corporation | Test circuitry for determining the defect density of a semiconductor process as a function of individual metal layers |

| US6456099B1 (en) * | 1998-12-31 | 2002-09-24 | Formfactor, Inc. | Special contact points for accessing internal circuitry of an integrated circuit |

| JP2000227459A (ja) | 1999-02-05 | 2000-08-15 | Sharp Corp | 半導体集積回路とそのテスト方法、及びそのテストに使用するプローブ治具 |

| JP2000332077A (ja) | 1999-05-17 | 2000-11-30 | Sony Corp | 半導体集積回路の配線欠陥検査方法および構造 |

| JP2001091543A (ja) * | 1999-09-27 | 2001-04-06 | Hitachi Ltd | 半導体検査装置 |

| JP2002110751A (ja) * | 2000-10-03 | 2002-04-12 | Hitachi Ltd | 半導体集積回路装置の検査装置および製造方法 |

| JP2003208686A (ja) * | 2002-01-10 | 2003-07-25 | Moritoshi Sato | 大気汚染観測データ送受信システム |

-

2001

- 2001-09-12 JP JP2001276530A patent/JP4041663B2/ja not_active Expired - Fee Related

-

2002

- 2002-06-18 TW TW091113300A patent/TW546756B/zh not_active IP Right Cessation

- 2002-08-15 US US10/218,596 patent/US6885208B2/en not_active Expired - Fee Related

- 2002-08-29 CN CNB021421846A patent/CN1213470C/zh not_active Expired - Fee Related

- 2002-09-10 KR KR10-2002-0054725A patent/KR100467913B1/ko not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| US6885208B2 (en) | 2005-04-26 |

| KR100467913B1 (ko) | 2005-01-24 |

| KR20030023510A (ko) | 2003-03-19 |

| US20030047731A1 (en) | 2003-03-13 |

| JP2003084042A (ja) | 2003-03-19 |

| CN1404123A (zh) | 2003-03-19 |

| TW546756B (en) | 2003-08-11 |

| CN1213470C (zh) | 2005-08-03 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP3135825B2 (ja) | プローブカードおよびそのプローブカードを使用した半導体集積回路のプロービング試験方法 | |

| US5262719A (en) | Test structure for multi-layer, thin-film modules | |

| JP4041663B2 (ja) | 半導体装置及びその検査装置 | |

| US4778771A (en) | Process of forming input/output wiring areas for semiconductor integrated circuit | |

| JP2008527328A (ja) | プローブヘッドアレイ | |

| EP0374466B1 (en) | In-line process monitors for thin film wiring | |

| JP3453526B2 (ja) | 半導体素子検査用ソケット、半導体装置、半導体装置の製造方法及び半導体装置の検査方法 | |

| US9069015B2 (en) | Interface board of a testing head for a test equipment of electronic devices and corresponding probe head | |

| US20070035318A1 (en) | Donut-type parallel probe card and method of testing semiconductor wafer using same | |

| KR100798724B1 (ko) | 웨이퍼 테스트 방법 및 이를 위한 프로브 카드 | |

| CN1249534A (zh) | 在晶片阶段内测试集成电路的方法和系统 | |

| JP5333829B2 (ja) | プローブ組立体 | |

| JP2012023278A (ja) | 半導体装置および半導体装置の製造方法 | |

| KR20050029066A (ko) | 프로브 카드 | |

| KR100519658B1 (ko) | 프로브 카드 | |

| JPH05206383A (ja) | 半導体ウエハー及びその検査方法 | |

| CN222994543U (zh) | 探针组件结构 | |

| JP2007086044A (ja) | プローバ装置及びこれに用いるプローブ組立体 | |

| KR100794629B1 (ko) | 전기 검사 장치와 그 제조 방법 | |

| JP2006278374A (ja) | 半導体装置及びその実装構造 | |

| JP7488492B2 (ja) | 半導体ウエハ | |

| EP2872906B1 (en) | Interface board of a testing head for a test equipment of electronic devices and corresponding testing head | |

| KR200423446Y1 (ko) | 프로브 카드 | |

| KR100679167B1 (ko) | 동축케이블을 이용한 반도체 웨이퍼 테스트용 프로브 카드 | |

| JP2001077162A (ja) | 半導体集積回路のプロービング試験方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20041026 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20050822 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20070731 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070927 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20071106 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20071112 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20101116 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111116 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111116 Year of fee payment: 4 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111116 Year of fee payment: 4 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111116 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121116 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121116 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131116 Year of fee payment: 6 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| LAPS | Cancellation because of no payment of annual fees |