JP2008527328A - プローブヘッドアレイ - Google Patents

プローブヘッドアレイ Download PDFInfo

- Publication number

- JP2008527328A JP2008527328A JP2007549436A JP2007549436A JP2008527328A JP 2008527328 A JP2008527328 A JP 2008527328A JP 2007549436 A JP2007549436 A JP 2007549436A JP 2007549436 A JP2007549436 A JP 2007549436A JP 2008527328 A JP2008527328 A JP 2008527328A

- Authority

- JP

- Japan

- Prior art keywords

- probe

- dut

- array

- pattern

- wafer

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

- 239000000523 sample Substances 0.000 title claims abstract description 243

- 238000012360 testing method Methods 0.000 claims abstract description 62

- 238000003491 array Methods 0.000 claims abstract description 42

- 239000004065 semiconductor Substances 0.000 claims abstract description 18

- 238000000034 method Methods 0.000 claims description 8

- 238000010998 test method Methods 0.000 claims description 3

- 229910003460 diamond Inorganic materials 0.000 claims 1

- 239000010432 diamond Substances 0.000 claims 1

- 235000012431 wafers Nutrition 0.000 description 105

- 238000010586 diagram Methods 0.000 description 15

- 238000013459 approach Methods 0.000 description 4

- 230000006870 function Effects 0.000 description 3

- 239000000758 substrate Substances 0.000 description 2

- 241000270295 Serpentes Species 0.000 description 1

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 1

- 239000000919 ceramic Substances 0.000 description 1

- 230000001427 coherent effect Effects 0.000 description 1

- 230000007423 decrease Effects 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 238000004519 manufacturing process Methods 0.000 description 1

- 239000012528 membrane Substances 0.000 description 1

- 230000015654 memory Effects 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 238000004806 packaging method and process Methods 0.000 description 1

- 238000012545 processing Methods 0.000 description 1

- 238000005201 scrubbing Methods 0.000 description 1

- 229910052710 silicon Inorganic materials 0.000 description 1

- 239000010703 silicon Substances 0.000 description 1

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 1

- 229910052721 tungsten Inorganic materials 0.000 description 1

- 239000010937 tungsten Substances 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L22/00—Testing or measuring during manufacture or treatment; Reliability measurements, i.e. testing of parts without further processing to modify the parts as such; Structural arrangements therefor

-

- G—PHYSICS

- G01—MEASURING; TESTING

- G01R—MEASURING ELECTRIC VARIABLES; MEASURING MAGNETIC VARIABLES

- G01R1/00—Details of instruments or arrangements of the types included in groups G01R5/00 - G01R13/00 and G01R31/00

- G01R1/02—General constructional details

- G01R1/06—Measuring leads; Measuring probes

- G01R1/067—Measuring probes

- G01R1/073—Multiple probes

- G01R1/07307—Multiple probes with individual probe elements, e.g. needles, cantilever beams or bump contacts, fixed in relation to each other, e.g. bed of nails fixture or probe card

- G01R1/07357—Multiple probes with individual probe elements, e.g. needles, cantilever beams or bump contacts, fixed in relation to each other, e.g. bed of nails fixture or probe card with flexible bodies, e.g. buckling beams

Landscapes

- Physics & Mathematics (AREA)

- General Physics & Mathematics (AREA)

- Engineering & Computer Science (AREA)

- Manufacturing & Machinery (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Testing Or Measuring Of Semiconductors Or The Like (AREA)

- Testing Of Individual Semiconductor Devices (AREA)

- Measuring Leads Or Probes (AREA)

Abstract

Description

本発明は、半導体ウェハ上のデバイスをテストするプローブヘッドアレイに関する。

マイクロプロセッサ、DRAM、およびフラッシュメモリのような半導体デバイスは、半導体ウェハ上に、周知の方法で作成される。ウェハのサイズと、そのウェハの上に形成される各デバイスのサイズとに依存して、1枚のウェハ上に、わずかに数個のデバイスが存在することも、あるいは千個を超えるデバイスが存在することもあり得る。これらのデバイスは、典型的には、互いに同一であり得、それぞれが、その表面に複数の導電性のパッドを含む。これらの導電性のパッドは、電源への接続と、入力信号、出力信号、制御信号などのようなデバイスへの他の接続とのためである。

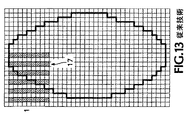

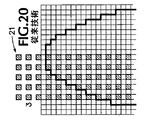

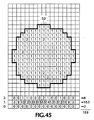

ここで、図1および図2を参照すると、プローブヘッド12を含むプローブカード10が、図1の10に概略的に示される。プローブカード10は、従来技術のプローブヘッドを運ぶためにも、本発明に従って作成されるプローブヘッドを運ぶためにも、使用され得る。プローブヘッドは、プローブアレイ14を含む。プローブアレイ14は、複数のプローブDUTアレイから構成され、このプローブDUTアレイは、プローブDUTアレイ16のように、プローブアレイ14の中に形成された正方形で模式的に示される。

Claims (30)

- 半導体ウェハ上に形成されたデバイスをテストする接触器であって、

該接触器は、該デバイス上に形成されるパッドと接触するプローブアレイを備え、

該プローブアレイは、該プローブアレイの開口部の周りに配置された連続的なDUTアレイを含み、

該開口部は、該プローブが該パッドに接触するとき、少なくとも1つのデバイスの上にある、接触器。 - 前記プローブアレイは、前記DUTアレイに、少なくとも1つの追加的な開口部を含み、該追加的な開口部は、該プローブアレイが前記パッドと接触するとき、少なくとも1つのデバイスと相対する、請求項1に記載の接触器。

- 前記連続的なDUTアレイは、概ね環状のパターンを形成する、請求項1に記載の接触器。

- 前記DUTアレイの前記開口部は、4つのDUTアレイと境する、請求項1に記載の接触器。

- 半導体ウェハ上で、実質的に均一なグリッドに配置されるデバイスをテストするプローブヘッドであって、該プローブヘッドは、

DUTアレイに形成された複数のプローブであって、該複数のプローブは、実質的に、該デバイスのグリッドと同じ構成を有するグリッドに配置される、複数のプローブと、

該DUTアレイに形成された空間であって、該空間は、該プローブが該デバイスにタッチするとき、少なくとも1つのデバイスと相対する、空間と

を備える、プローブヘッド。 - 前記プローブヘッドは、少なくとも1つの追加的な空間を含み、該追加的な空間は、前記プローブが前記デバイスとタッチするとき、少なくとも1つのデバイスと相対する、請求項5に記載のプローブヘッド。

- 前記DUTアレイは、概ね環状のパターンを形成する、請求項5に記載のプローブヘッド。

- 前記空間は、4つのDUTアレイと境する、請求項5に記載のプローブヘッド。

- 半導体ウェハ上に形成されるデバイスをテストする装置であって、実質的に環状のパターンに配置されたプローブDUTアレイを備える、装置。

- 前記環状のパターンは、開口部を含み、該パターンは、少なくとも1つの追加的な開口部を含む、請求項9に記載の装置。

- 半導体ウェハ上に形成されるデバイスをテストする装置であって、

該装置は、少なくとも1つの開口部を含むパターンに配置されたプローブDUTアレイを備え、

該少なくとも1つの開口部は、プローブDUTアレイがない該パターンの周囲内に含まれる、装置。 - 前記プローブアレイパターンは、少なくとも1つの追加的な開口部を含み、

該追加的な開口部は、プローブDUTアレイがない該パターンの周囲内に含まれる、請求項11に記載の装置。 - 前記パターンは、概ね環状である、請求項11に記載の装置。

- 前記開口部は、4つのDUTアレイと境する、請求項11に記載の装置。

- 半導体ウェハ上に形成されたデバイスをテストする装置であって、

該装置は、パターンに配置されたプローブDUTアレイを備え、

該パターンは、少なくとも1つの局所的な不連続性を有する周囲を有する、装置。 - 前記局所的な不連続性は、少なくとも1つのDUTアレイの隆起である、請求項15に記載の装置。

- 前記隆起は、単一のDUTアレイによって形成される、請求項16に記載の装置。

- 前記隆起は、最小幅を有し、該周囲から外向きに、該最小幅の2倍よりも長く延びる、請求項16に記載の装置。

- 前記周囲は、少なくとも1つの追加的な隆起を含む、請求項16に記載の装置。

- 前記局所的な不連続性は、少なくとも1つのDUTアレイの湾入である、請求項15に記載の装置。

- 前記湾入は、単一のDUTアレイによって形成される、請求項20に記載の装置。

- 前記湾入は、最小幅を有し、該周囲から内向きに、該最小幅の2倍よりも長く延びる、請求項20に記載の装置。

- 前記周囲は、少なくとも1つの追加的な湾入を含む、請求項20に記載の装置。

- 前記パターンは、対称的である、請求項15に記載の装置。

- 前記パターンは、実質的に平行四辺形の形状である、請求項24に記載の装置。

- 前記パターンは、実質的に菱形の形状である、請求項25に記載の装置。

- 半導体ウェハ上で、実質的に平行な水平線と平行な垂直線とを形成するパターンに配置されたデバイスをテストする装置であって、

該装置は、対称的なパターンに配置されたプローブDUTアレイを備え、

該パターンは、該プローブDUTアレイが該デバイスにタッチするとき、デバイスの該線のいずれとも平行でない少なくとも1つの周囲を有する、装置。 - 前記パターンは、実質的に平行四辺形の形状である、請求項27に記載の装置。

- 前記パターンは、実質的に菱形の形状である、請求項28に記載の装置。

- ウェハ上の半導体デバイスをテストする方法であって、該方法は、

プローブのアレイを提供するステップであって、該プローブのアレイは、該プローブのアレイに少なくとも1つの不連続性を有する、ステップと、

テストされるべき該半導体デバイスの第一の部分が、該プローブの一部によって接触され、該デバイスの第二の部分が、該プローブによって接触されないが、位置的に該少なくとも1つの不連続性と相対するように、該アレイを該ウェハと接触させるステップと、

該ウェハを該プローブのアレイとの接触しないように移動させるステップと、

該ウェハを該プローブのアレイに対してラテラルに移動させるステップと、

該デバイスの該第二の部分の少なくとも一部が、該プローブの一部によって接触されるように、該アレイを該ウェハと接触させるステップと

を含む、方法。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US11/028,940 US7282933B2 (en) | 2005-01-03 | 2005-01-03 | Probe head arrays |

| PCT/US2005/045582 WO2006073736A2 (en) | 2005-01-03 | 2005-12-15 | Probe head arrays |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2008527328A true JP2008527328A (ja) | 2008-07-24 |

| JP2008527328A5 JP2008527328A5 (ja) | 2009-02-19 |

Family

ID=36639659

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2007549436A Pending JP2008527328A (ja) | 2005-01-03 | 2005-12-15 | プローブヘッドアレイ |

Country Status (7)

| Country | Link |

|---|---|

| US (1) | US7282933B2 (ja) |

| EP (1) | EP1842073A2 (ja) |

| JP (1) | JP2008527328A (ja) |

| KR (1) | KR20070112125A (ja) |

| CN (1) | CN101095057B (ja) |

| TW (1) | TW200634313A (ja) |

| WO (1) | WO2006073736A2 (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP7498677B2 (ja) | 2021-02-25 | 2024-06-12 | ルネサスエレクトロニクス株式会社 | テスト装置、テスト方法および記録媒体 |

Families Citing this family (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR100652421B1 (ko) * | 2005-08-09 | 2006-12-01 | 삼성전자주식회사 | 도넛형 병렬 프로브 카드 및 이를 이용한 웨이퍼 검사방법 |

| JP2007250691A (ja) * | 2006-03-14 | 2007-09-27 | Elpida Memory Inc | プローブカード、プローブカードの設計方法及びテスト方法 |

| US7649366B2 (en) | 2006-09-01 | 2010-01-19 | Formfactor, Inc. | Method and apparatus for switching tester resources |

| US7852094B2 (en) * | 2006-12-06 | 2010-12-14 | Formfactor, Inc. | Sharing resources in a system for testing semiconductor devices |

| US7535239B1 (en) * | 2006-12-14 | 2009-05-19 | Xilinx, Inc. | Probe card configured for interchangeable heads |

| KR100850274B1 (ko) * | 2007-01-04 | 2008-08-04 | 삼성전자주식회사 | 반도체 칩 테스트를 위한 프로브 카드 및 이를 이용한반도체 칩 테스트 방법 |

| US7893700B2 (en) * | 2008-07-28 | 2011-02-22 | Formfactor, Inc. | Configuration of shared tester channels to avoid electrical connections across die area boundary on a wafer |

| KR101534163B1 (ko) * | 2009-04-01 | 2015-07-06 | 삼성전자주식회사 | 실장 테스트에 적합한 메인 보드 및 이를 포함하는 메모리 실장 테스트 시스템 |

| CN104204818B (zh) | 2012-03-23 | 2017-05-24 | 爱德万测试公司 | 用于半导体测试的横向驱动探针 |

| US9678108B1 (en) | 2014-02-06 | 2017-06-13 | Advantest America, Inc. | Methods to manufacture semiconductor probe tips |

| CN106597037B (zh) | 2015-10-20 | 2019-07-16 | 创意电子股份有限公司 | 探针卡与测试方法 |

| CN107367678B (zh) * | 2016-05-11 | 2020-03-10 | 中芯国际集成电路制造(上海)有限公司 | 测试结构、测试探针卡、测试系统及测试方法 |

| CN107422242A (zh) * | 2016-05-23 | 2017-12-01 | 北大方正集团有限公司 | 一种vdmos芯片的测试装置及方法 |

Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2001291750A (ja) * | 2000-04-06 | 2001-10-19 | Seiko Epson Corp | プローブカード及びそれを用いたチップ領域ソート方法 |

Family Cites Families (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4837622A (en) * | 1985-05-10 | 1989-06-06 | Micro-Probe, Inc. | High density probe card |

| US5210485A (en) * | 1991-07-26 | 1993-05-11 | International Business Machines Corporation | Probe for wafer burn-in test system |

| JPH0653299A (ja) * | 1992-07-31 | 1994-02-25 | Tokyo Electron Yamanashi Kk | バーンイン装置 |

| US6246247B1 (en) * | 1994-11-15 | 2001-06-12 | Formfactor, Inc. | Probe card assembly and kit, and methods of using same |

| EP0707214A3 (en) * | 1994-10-14 | 1997-04-16 | Hughes Aircraft Co | Multiport membrane probe to test complete semiconductor plates |

| US5642054A (en) * | 1995-08-08 | 1997-06-24 | Hughes Aircraft Company | Active circuit multi-port membrane probe for full wafer testing |

| JP3135825B2 (ja) * | 1995-09-27 | 2001-02-19 | 株式会社東芝 | プローブカードおよびそのプローブカードを使用した半導体集積回路のプロービング試験方法 |

| CN2444311Y (zh) * | 2000-08-15 | 2001-08-22 | 陈文杰 | 晶片测试装置 |

| US6729019B2 (en) * | 2001-07-11 | 2004-05-04 | Formfactor, Inc. | Method of manufacturing a probe card |

| US6714828B2 (en) * | 2001-09-17 | 2004-03-30 | Formfactor, Inc. | Method and system for designing a probe card |

| TWI236723B (en) * | 2002-10-02 | 2005-07-21 | Renesas Tech Corp | Probe sheet, probe card, semiconductor inspection device, and manufacturing method for semiconductor device |

-

2005

- 2005-01-03 US US11/028,940 patent/US7282933B2/en not_active Expired - Fee Related

- 2005-12-15 EP EP05854328A patent/EP1842073A2/en not_active Withdrawn

- 2005-12-15 CN CN2005800457196A patent/CN101095057B/zh not_active Expired - Fee Related

- 2005-12-15 JP JP2007549436A patent/JP2008527328A/ja active Pending

- 2005-12-15 WO PCT/US2005/045582 patent/WO2006073736A2/en active Application Filing

- 2005-12-15 KR KR1020077017753A patent/KR20070112125A/ko not_active Application Discontinuation

- 2005-12-27 TW TW094146763A patent/TW200634313A/zh unknown

Patent Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2001291750A (ja) * | 2000-04-06 | 2001-10-19 | Seiko Epson Corp | プローブカード及びそれを用いたチップ領域ソート方法 |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP7498677B2 (ja) | 2021-02-25 | 2024-06-12 | ルネサスエレクトロニクス株式会社 | テスト装置、テスト方法および記録媒体 |

Also Published As

| Publication number | Publication date |

|---|---|

| CN101095057A (zh) | 2007-12-26 |

| US7282933B2 (en) | 2007-10-16 |

| US20060145713A1 (en) | 2006-07-06 |

| TW200634313A (en) | 2006-10-01 |

| KR20070112125A (ko) | 2007-11-22 |

| CN101095057B (zh) | 2010-06-23 |

| WO2006073736A3 (en) | 2006-08-10 |

| EP1842073A2 (en) | 2007-10-10 |

| WO2006073736A2 (en) | 2006-07-13 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP2008527328A (ja) | プローブヘッドアレイ | |

| KR100712561B1 (ko) | 웨이퍼 형태의 프로브 카드 및 그 제조방법과 웨이퍼형태의 프로브 카드를 구비한 반도체 검사장치 | |

| US3746973A (en) | Testing of metallization networks on insulative substrates supporting semiconductor chips | |

| KR20080058343A (ko) | 싱귤레이션된 다이를 테스트하는 장치 및 방법 | |

| US20210102974A1 (en) | Hybrid probe card for testing component mounted wafer | |

| KR100548103B1 (ko) | 반도체 제품 다이 테스트용 테스트 다이를 포함하는테스트 장치 및 반도체 제품 다이 테스트 방법 | |

| US6836130B2 (en) | Method and apparatus for wafer scale testing | |

| US20070035318A1 (en) | Donut-type parallel probe card and method of testing semiconductor wafer using same | |

| US7535239B1 (en) | Probe card configured for interchangeable heads | |

| JP2764854B2 (ja) | プローブカード及び検査方法 | |

| JP4041663B2 (ja) | 半導体装置及びその検査装置 | |

| JP2000106257A (ja) | 半導体素子検査用ソケット、半導体装置、半導体装置の製造方法及び半導体装置の検査方法 | |

| KR20130019602A (ko) | 프로브카드 | |

| KR100798724B1 (ko) | 웨이퍼 테스트 방법 및 이를 위한 프로브 카드 | |

| US7157923B2 (en) | Method for full wafer contact probing, wafer design and probe card device with reduced probe contacts | |

| JP3858244B2 (ja) | 半導体検査装置及び半導体の検査方法 | |

| JP3135135B2 (ja) | 半導体装置,その製造方法,その試験方法及びその試験装置 | |

| JP3178424B2 (ja) | 集積回路試験装置及び集積回路試験方法 | |

| JPS6047433A (ja) | 多品種搭載ウエハ試験装置 | |

| JP3763258B2 (ja) | プローブカード及びそれを用いたチップ領域ソート方法 | |

| JP2001291749A (ja) | プローブカード及びそれを用いたチップ領域ソート方法 | |

| KR20240080483A (ko) | 프로브 카드, 프로브 카드를 포함한 테스트 장치, 그 프로브 카드를 이용한 테스트 방법 | |

| JP2891908B2 (ja) | 半導体集積回路の試験装置およびその試験方法 | |

| JP2007157955A (ja) | プローブカードおよびこれを用いた測定方法および検査装置 | |

| JPH0945740A (ja) | 半導体基板の評価方法及びそれに用いるチェック用ボード |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20081215 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20081222 |

|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20100526 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20110114 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110713 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20111212 |