JP4031329B2 - 半導体装置及びその製造方法 - Google Patents

半導体装置及びその製造方法 Download PDFInfo

- Publication number

- JP4031329B2 JP4031329B2 JP2002273409A JP2002273409A JP4031329B2 JP 4031329 B2 JP4031329 B2 JP 4031329B2 JP 2002273409 A JP2002273409 A JP 2002273409A JP 2002273409 A JP2002273409 A JP 2002273409A JP 4031329 B2 JP4031329 B2 JP 4031329B2

- Authority

- JP

- Japan

- Prior art keywords

- cavity

- region

- semiconductor

- semiconductor substrate

- semiconductor device

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/01—Manufacture or treatment

- H10B12/09—Manufacture or treatment with simultaneous manufacture of the peripheral circuit region and memory cells

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/76—Making of isolation regions between components

- H01L21/762—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers

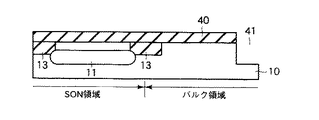

- H01L21/7624—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers using semiconductor on insulator [SOI] technology

- H01L21/76264—SOI together with lateral isolation, e.g. using local oxidation of silicon, or dielectric or polycristalline material refilled trench or air gap isolation regions, e.g. completely isolated semiconductor islands

- H01L21/76283—Lateral isolation by refilling of trenches with dielectric material

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/76—Making of isolation regions between components

- H01L21/762—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers

- H01L21/7624—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers using semiconductor on insulator [SOI] technology

- H01L21/76264—SOI together with lateral isolation, e.g. using local oxidation of silicon, or dielectric or polycristalline material refilled trench or air gap isolation regions, e.g. completely isolated semiconductor islands

- H01L21/76289—Lateral isolation by air gap

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/76—Making of isolation regions between components

- H01L21/764—Air gaps

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/50—Peripheral circuit region structures

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/711—Insulated-gate field-effect transistors [IGFET] having floating bodies

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D62/00—Semiconductor bodies, or regions thereof, of devices having potential barriers

- H10D62/10—Shapes, relative sizes or dispositions of the regions of the semiconductor bodies; Shapes of the semiconductor bodies

- H10D62/113—Isolations within a component, i.e. internal isolations

- H10D62/115—Dielectric isolations, e.g. air gaps

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/01—Manufacture or treatment

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/201—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates the substrates comprising an insulating layer on a semiconductor body, e.g. SOI

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B10/00—Static random access memory [SRAM] devices

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/01—Manufacture or treatment

- H10B12/02—Manufacture or treatment for one transistor one-capacitor [1T-1C] memory cells

- H10B12/03—Making the capacitor or connections thereto

- H10B12/038—Making the capacitor or connections thereto the capacitor being in a trench in the substrate

- H10B12/0387—Making the trench

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/30—DRAM devices comprising one-transistor - one-capacitor [1T-1C] memory cells

- H10B12/37—DRAM devices comprising one-transistor - one-capacitor [1T-1C] memory cells the capacitor being at least partially in a trench in the substrate

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/30—DRAM devices comprising one-transistor - one-capacitor [1T-1C] memory cells

- H10B12/48—Data lines or contacts therefor

- H10B12/482—Bit lines

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B53/00—Ferroelectric RAM [FeRAM] devices comprising ferroelectric memory capacitors

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B69/00—Erasable-and-programmable ROM [EPROM] devices not provided for in groups H10B41/00 - H10B63/00, e.g. ultraviolet erasable-and-programmable ROM [UVEPROM] devices

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D1/00—Resistors, capacitors or inductors

- H10D1/01—Manufacture or treatment

- H10D1/045—Manufacture or treatment of capacitors having potential barriers, e.g. varactors

- H10D1/047—Manufacture or treatment of capacitors having potential barriers, e.g. varactors of conductor-insulator-semiconductor capacitors, e.g. trench capacitors

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D89/00—Aspects of integrated devices not covered by groups H10D84/00 - H10D88/00

- H10D89/211—Design considerations for internal polarisation

- H10D89/213—Design considerations for internal polarisation in field-effect devices

Landscapes

- Engineering & Computer Science (AREA)

- Manufacturing & Machinery (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Element Separation (AREA)

- Thin Film Transistor (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2002273409A JP4031329B2 (ja) | 2002-09-19 | 2002-09-19 | 半導体装置及びその製造方法 |

| US10/665,614 US7009273B2 (en) | 2002-09-19 | 2003-09-19 | Semiconductor device with a cavity therein and a method of manufacturing the same |

| US11/315,796 US7145215B2 (en) | 2002-09-19 | 2005-12-22 | Semiconductor device with a cavity therein and a method of manufacturing the same |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2002273409A JP4031329B2 (ja) | 2002-09-19 | 2002-09-19 | 半導体装置及びその製造方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2004111721A JP2004111721A (ja) | 2004-04-08 |

| JP2004111721A5 JP2004111721A5 (OSRAM) | 2005-08-25 |

| JP4031329B2 true JP4031329B2 (ja) | 2008-01-09 |

Family

ID=32270175

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2002273409A Expired - Fee Related JP4031329B2 (ja) | 2002-09-19 | 2002-09-19 | 半導体装置及びその製造方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (2) | US7009273B2 (OSRAM) |

| JP (1) | JP4031329B2 (OSRAM) |

Families Citing this family (60)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4074051B2 (ja) * | 1999-08-31 | 2008-04-09 | 株式会社東芝 | 半導体基板およびその製造方法 |

| US7173841B2 (en) * | 2004-12-03 | 2007-02-06 | Taiwan Semiconductor Manufacturing Company, Ltd. | Magnetic memory array |

| US7071047B1 (en) * | 2005-01-28 | 2006-07-04 | International Business Machines Corporation | Method of forming buried isolation regions in semiconductor substrates and semiconductor devices with buried isolation regions |

| DE602005007235D1 (de) * | 2005-09-28 | 2008-07-10 | St Microelectronics Srl | Verfahren zum Herstellen von dicken hängenden Strukturen aus Halbleitermaterial |

| US8395199B2 (en) * | 2006-03-25 | 2013-03-12 | 4D-S Pty Ltd. | Systems and methods for fabricating self-aligned memory cell |

| US7285480B1 (en) * | 2006-04-07 | 2007-10-23 | International Business Machines Corporation | Integrated circuit chip with FETs having mixed body thicknesses and method of manufacture thereof |

| US7932548B2 (en) | 2006-07-14 | 2011-04-26 | 4D-S Pty Ltd. | Systems and methods for fabricating self-aligned memory cell |

| US8305829B2 (en) * | 2009-02-23 | 2012-11-06 | Taiwan Semiconductor Manufacturing Company, Ltd. | Memory power gating circuit for controlling internal voltage of a memory array, system and method for controlling the same |

| US8305790B2 (en) * | 2009-03-16 | 2012-11-06 | Taiwan Semiconductor Manufacturing Company, Ltd. | Electrical anti-fuse and related applications |

| US8957482B2 (en) * | 2009-03-31 | 2015-02-17 | Taiwan Semiconductor Manufacturing Company, Ltd. | Electrical fuse and related applications |

| US8912602B2 (en) * | 2009-04-14 | 2014-12-16 | Taiwan Semiconductor Manufacturing Company, Ltd. | FinFETs and methods for forming the same |

| US8461015B2 (en) * | 2009-07-08 | 2013-06-11 | Taiwan Semiconductor Manufacturing Company, Ltd. | STI structure and method of forming bottom void in same |

| US8440517B2 (en) | 2010-10-13 | 2013-05-14 | Taiwan Semiconductor Manufacturing Company, Ltd. | FinFET and method of fabricating the same |

| US8264032B2 (en) | 2009-09-01 | 2012-09-11 | Taiwan Semiconductor Manufacturing Company, Ltd. | Accumulation type FinFET, circuits and fabrication method thereof |

| US8472227B2 (en) * | 2010-01-27 | 2013-06-25 | Taiwan Semiconductor Manufacturing Company, Ltd. | Integrated circuits and methods for forming the same |

| US8264021B2 (en) * | 2009-10-01 | 2012-09-11 | Taiwan Semiconductor Manufacturing Company, Ltd. | Finfets and methods for forming the same |

| US8623728B2 (en) * | 2009-07-28 | 2014-01-07 | Taiwan Semiconductor Manufacturing Company, Ltd. | Method for forming high germanium concentration SiGe stressor |

| US8629478B2 (en) * | 2009-07-31 | 2014-01-14 | Taiwan Semiconductor Manufacturing Company, Ltd. | Fin structure for high mobility multiple-gate transistor |

| US9484462B2 (en) * | 2009-09-24 | 2016-11-01 | Taiwan Semiconductor Manufacturing Company, Ltd. | Fin structure of fin field effect transistor |

| US8980719B2 (en) | 2010-04-28 | 2015-03-17 | Taiwan Semiconductor Manufacturing Company, Ltd. | Methods for doping fin field-effect transistors |

| US8497528B2 (en) | 2010-05-06 | 2013-07-30 | Taiwan Semiconductor Manufacturing Company, Ltd. | Method for fabricating a strained structure |

| US8298925B2 (en) | 2010-11-08 | 2012-10-30 | Taiwan Semiconductor Manufacturing Company, Ltd. | Mechanisms for forming ultra shallow junction |

| US8482073B2 (en) * | 2010-03-25 | 2013-07-09 | Taiwan Semiconductor Manufacturing Company, Ltd. | Integrated circuit including FINFETs and methods for forming the same |

| US8759943B2 (en) | 2010-10-08 | 2014-06-24 | Taiwan Semiconductor Manufacturing Company, Ltd. | Transistor having notched fin structure and method of making the same |

| US8187928B2 (en) | 2010-09-21 | 2012-05-29 | Taiwan Semiconductor Manufacturing Company, Ltd. | Methods of forming integrated circuits |

| US9343463B2 (en) * | 2009-09-29 | 2016-05-17 | Headway Technologies, Inc. | Method of high density memory fabrication |

| US20110097867A1 (en) * | 2009-10-22 | 2011-04-28 | Taiwan Semiconductor Manufacturing Company, Ltd. | Method of controlling gate thicknesses in forming fusi gates |

| US9040393B2 (en) | 2010-01-14 | 2015-05-26 | Taiwan Semiconductor Manufacturing Company, Ltd. | Method of forming semiconductor structure |

| US8674472B2 (en) * | 2010-08-10 | 2014-03-18 | International Business Machines Corporation | Low harmonic RF switch in SOI |

| US8603924B2 (en) | 2010-10-19 | 2013-12-10 | Taiwan Semiconductor Manufacturing Company, Ltd. | Methods of forming gate dielectric material |

| US9048181B2 (en) | 2010-11-08 | 2015-06-02 | Taiwan Semiconductor Manufacturing Company, Ltd. | Mechanisms for forming ultra shallow junction |

| US8769446B2 (en) | 2010-11-12 | 2014-07-01 | Taiwan Semiconductor Manufacturing Company, Ltd. | Method and device for increasing fin device density for unaligned fins |

| US8877602B2 (en) | 2011-01-25 | 2014-11-04 | Taiwan Semiconductor Manufacturing Company, Ltd. | Mechanisms of doping oxide for forming shallow trench isolation |

| US8592915B2 (en) | 2011-01-25 | 2013-11-26 | Taiwan Semiconductor Manufacturing Company, Ltd. | Doped oxide for shallow trench isolation (STI) |

| US8431453B2 (en) | 2011-03-31 | 2013-04-30 | Taiwan Semiconductor Manufacturing Company, Ltd. | Plasma doping to reduce dielectric loss during removal of dummy layers in a gate structure |

| JP5891597B2 (ja) * | 2011-04-07 | 2016-03-23 | 富士電機株式会社 | 半導体基板または半導体装置の製造方法 |

| CN102842615B (zh) * | 2011-06-20 | 2016-02-17 | 中国科学院微电子研究所 | 一种半导体结构及其制造方法 |

| CN102856360B (zh) * | 2011-06-27 | 2015-09-16 | 中国科学院微电子研究所 | 一种半导体结构及其制造方法 |

| CN102856375B (zh) * | 2011-06-27 | 2015-05-20 | 中国科学院微电子研究所 | 一种半导体结构及其制造方法 |

| US8994127B2 (en) | 2011-11-24 | 2015-03-31 | Infineon Technologies Ag | Method of fabricating isolating semiconductor structures using a layout of trenches and openings |

| CN103377925A (zh) * | 2012-04-13 | 2013-10-30 | 中国科学院微电子研究所 | 一种半导体结构及其制造方法 |

| CN103730361B (zh) * | 2012-10-10 | 2018-02-13 | 中国科学院微电子研究所 | 半导体器件制造方法 |

| US9437470B2 (en) | 2013-10-08 | 2016-09-06 | Cypress Semiconductor Corporation | Self-aligned trench isolation in integrated circuits |

| CN104681556B (zh) * | 2013-11-28 | 2017-12-05 | 中芯国际集成电路制造(上海)有限公司 | 一种集成电路及其制造方法和电子装置 |

| US9252026B2 (en) | 2014-03-12 | 2016-02-02 | Cypress Semiconductor Corporation | Buried trench isolation in integrated circuits |

| DE102016119799B4 (de) * | 2016-10-18 | 2020-08-06 | Infineon Technologies Ag | Integrierte schaltung, die einen vergrabenen hohlraum enthält, und herstellungsverfahren |

| US10461152B2 (en) | 2017-07-10 | 2019-10-29 | Globalfoundries Inc. | Radio frequency switches with air gap structures |

| US10833153B2 (en) | 2017-09-13 | 2020-11-10 | Globalfoundries Inc. | Switch with local silicon on insulator (SOI) and deep trench isolation |

| US10109638B1 (en) * | 2017-10-23 | 2018-10-23 | Globalfoundries Singapore Pte. Ltd. | Embedded non-volatile memory (NVM) on fully depleted silicon-on-insulator (FD-SOI) substrate |

| US10446643B2 (en) | 2018-01-22 | 2019-10-15 | Globalfoundries Inc. | Sealed cavity structures with a planar surface |

| US10156676B1 (en) | 2018-02-26 | 2018-12-18 | Globalfoundries Inc. | Waveguides with multiple airgaps arranged in and over a silicon-on-insulator substrate |

| US10393960B1 (en) | 2018-02-26 | 2019-08-27 | Globalfoundries Inc. | Waveguides with multiple-level airgaps |

| US11056382B2 (en) * | 2018-03-19 | 2021-07-06 | Globalfoundries U.S. Inc. | Cavity formation within and under semiconductor devices |

| CN108682649B (zh) * | 2018-04-17 | 2021-02-05 | 中芯集成电路(宁波)有限公司 | Soi衬底、半导体器件及其形成方法 |

| US11410872B2 (en) | 2018-11-30 | 2022-08-09 | Globalfoundries U.S. Inc. | Oxidized cavity structures within and under semiconductor devices |

| US10923577B2 (en) | 2019-01-07 | 2021-02-16 | Globalfoundries U.S. Inc. | Cavity structures under shallow trench isolation regions |

| CN109935628B (zh) * | 2019-03-27 | 2021-01-19 | 中国科学院上海微系统与信息技术研究所 | 基于图形化soi衬底的抗辐照晶体管及其制作方法 |

| US11127816B2 (en) | 2020-02-14 | 2021-09-21 | Globalfoundries U.S. Inc. | Heterojunction bipolar transistors with one or more sealed airgap |

| KR102859088B1 (ko) * | 2021-07-20 | 2025-09-11 | 삼성전자주식회사 | 반도체 장치 |

| US11650382B1 (en) * | 2021-10-26 | 2023-05-16 | Globalfoundries U.S. Inc. | Optical components undercut by a sealed cavity |

Family Cites Families (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5227658A (en) | 1991-10-23 | 1993-07-13 | International Business Machines Corporation | Buried air dielectric isolation of silicon islands |

| US5567982A (en) * | 1994-09-30 | 1996-10-22 | Bartelink; Dirk J. | Air-dielectric transmission lines for integrated circuits |

| JPH08288381A (ja) | 1995-04-19 | 1996-11-01 | Nissan Motor Co Ltd | 半導体装置の製造方法 |

| JP3762136B2 (ja) | 1998-04-24 | 2006-04-05 | 株式会社東芝 | 半導体装置 |

| JP4074051B2 (ja) | 1999-08-31 | 2008-04-09 | 株式会社東芝 | 半導体基板およびその製造方法 |

| JP3571989B2 (ja) | 2000-03-13 | 2004-09-29 | 株式会社東芝 | 半導体装置及びその製造方法 |

| JP3946406B2 (ja) | 2000-03-30 | 2007-07-18 | 株式会社東芝 | 熱型赤外線センサの製造方法 |

| US6670234B2 (en) * | 2001-06-22 | 2003-12-30 | International Business Machines Corporation | Method of integrating volatile and non-volatile memory cells on the same substrate and a semiconductor memory device thereof |

| US6630714B2 (en) * | 2001-12-27 | 2003-10-07 | Kabushiki Kaisha Toshiba | Semiconductor device formed in semiconductor layer arranged on substrate with one of insulating film and cavity interposed between the substrate and the semiconductor layer |

| JP2003243528A (ja) * | 2002-02-13 | 2003-08-29 | Toshiba Corp | 半導体装置 |

| JP4277481B2 (ja) | 2002-05-08 | 2009-06-10 | 日本電気株式会社 | 半導体基板の製造方法、半導体装置の製造方法 |

| US6830987B1 (en) * | 2003-06-13 | 2004-12-14 | Advanced Micro Devices, Inc. | Semiconductor device with a silicon-on-void structure and method of making the same |

-

2002

- 2002-09-19 JP JP2002273409A patent/JP4031329B2/ja not_active Expired - Fee Related

-

2003

- 2003-09-19 US US10/665,614 patent/US7009273B2/en not_active Expired - Fee Related

-

2005

- 2005-12-22 US US11/315,796 patent/US7145215B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2004111721A (ja) | 2004-04-08 |

| US20060157789A1 (en) | 2006-07-20 |

| US20040129998A1 (en) | 2004-07-08 |

| US7009273B2 (en) | 2006-03-07 |

| US7145215B2 (en) | 2006-12-05 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4031329B2 (ja) | 半導体装置及びその製造方法 | |

| KR100671876B1 (ko) | 반도체 장치 및 그 제조 방법 | |

| JP3825688B2 (ja) | 半導体装置の製造方法 | |

| JP3934507B2 (ja) | 半導体記憶装置および半導体記憶装置の製造方法 | |

| US6376316B2 (en) | Method for manufacturing semiconductor integrated circuit device having deposited layer for gate insulation | |

| JP3963970B2 (ja) | Dramセルおよびその形成方法 | |

| KR100525331B1 (ko) | 반도체 장치 | |

| US9202921B2 (en) | Semiconductor device and method of making the same | |

| US10062581B2 (en) | Methods of forming an isolation structure and methods of manufacturing a semiconductor device including the same | |

| KR0163759B1 (ko) | 반도체장치 및 반도체기억장치 | |

| JP2004214379A (ja) | 半導体装置、ダイナミック型半導体記憶装置及び半導体装置の製造方法 | |

| JP2004281782A (ja) | 半導体装置及びその製造方法 | |

| JP2006049413A (ja) | 半導体装置及びその製造方法 | |

| JP2008010503A (ja) | 半導体記憶装置およびその製造方法 | |

| JP5583315B2 (ja) | 半導体装置及びその製造方法 | |

| KR101287733B1 (ko) | 반도체 장치 및 그 제조 방법과 반도체 기억 장치 | |

| US6872629B2 (en) | Method of forming a memory cell with a single sided buried strap | |

| JP2013069770A (ja) | 半導体装置及びその製造方法 | |

| JPH05190795A (ja) | メモリセルアレイ | |

| US20050184326A1 (en) | Deep-trench 1t-sram with buried out diffusion well merged with an ion implantation well | |

| JPH11284146A (ja) | 半導体記憶装置及びその製造方法 | |

| CN1319154C (zh) | 存储电容器的埋入式带接触的制造方法 | |

| JP3798659B2 (ja) | メモリ集積回路 | |

| US20080230838A1 (en) | Semiconductor memory device and manufacturing process therefore | |

| US20080157162A1 (en) | Method of combining floating body cell and logic transistors |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20050208 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20050208 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20060814 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20060829 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20061030 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20070710 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070906 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20071016 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20071018 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20101026 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111026 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111026 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121026 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131026 Year of fee payment: 6 |

|

| LAPS | Cancellation because of no payment of annual fees |