JP3702166B2 - チャージポンプ回路 - Google Patents

チャージポンプ回路 Download PDFInfo

- Publication number

- JP3702166B2 JP3702166B2 JP2000331879A JP2000331879A JP3702166B2 JP 3702166 B2 JP3702166 B2 JP 3702166B2 JP 2000331879 A JP2000331879 A JP 2000331879A JP 2000331879 A JP2000331879 A JP 2000331879A JP 3702166 B2 JP3702166 B2 JP 3702166B2

- Authority

- JP

- Japan

- Prior art keywords

- circuit

- clock signal

- charge pump

- transistor

- transistors

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

Images

Classifications

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02M—APPARATUS FOR CONVERSION BETWEEN AC AND AC, BETWEEN AC AND DC, OR BETWEEN DC AND DC, AND FOR USE WITH MAINS OR SIMILAR POWER SUPPLY SYSTEMS; CONVERSION OF DC OR AC INPUT POWER INTO SURGE OUTPUT POWER; CONTROL OR REGULATION THEREOF

- H02M3/00—Conversion of dc power input into dc power output

- H02M3/02—Conversion of dc power input into dc power output without intermediate conversion into ac

- H02M3/04—Conversion of dc power input into dc power output without intermediate conversion into ac by static converters

- H02M3/06—Conversion of dc power input into dc power output without intermediate conversion into ac by static converters using resistors or capacitors, e.g. potential divider

- H02M3/07—Conversion of dc power input into dc power output without intermediate conversion into ac by static converters using resistors or capacitors, e.g. potential divider using capacitors charged and discharged alternately by semiconductor devices with control electrode, e.g. charge pumps

- H02M3/073—Charge pumps of the Schenkel-type

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C5/00—Details of stores covered by group G11C11/00

- G11C5/14—Power supply arrangements, e.g. power down, chip selection or deselection, layout of wirings or power grids, or multiple supply levels

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02M—APPARATUS FOR CONVERSION BETWEEN AC AND AC, BETWEEN AC AND DC, OR BETWEEN DC AND DC, AND FOR USE WITH MAINS OR SIMILAR POWER SUPPLY SYSTEMS; CONVERSION OF DC OR AC INPUT POWER INTO SURGE OUTPUT POWER; CONTROL OR REGULATION THEREOF

- H02M3/00—Conversion of dc power input into dc power output

- H02M3/02—Conversion of dc power input into dc power output without intermediate conversion into ac

- H02M3/04—Conversion of dc power input into dc power output without intermediate conversion into ac by static converters

- H02M3/06—Conversion of dc power input into dc power output without intermediate conversion into ac by static converters using resistors or capacitors, e.g. potential divider

- H02M3/07—Conversion of dc power input into dc power output without intermediate conversion into ac by static converters using resistors or capacitors, e.g. potential divider using capacitors charged and discharged alternately by semiconductor devices with control electrode, e.g. charge pumps

- H02M3/073—Charge pumps of the Schenkel-type

- H02M3/075—Charge pumps of the Schenkel-type including a plurality of stages and two sets of clock signals, one set for the odd and one set for the even numbered stages

Description

【発明の属する技術分野】

この発明は、キャパシタを用いて電圧を変換するチャージポンプ回路に関する。

【0002】

【従来の技術】

図10に、従来のチャージポンプ回路の構成の概要を示す。ここで、同図10(a)に示す回路は、2個のダイオードD1,D2、キャパシタC1、及び出力キャパシタCout等を備えて構成される。また、図10(b)には、前記ダイオードD1,D2をPチャネル型MOSトランジスタT1,T2にて構成した例を示す。

【0003】

これらチャージポンプ回路はいずれも、キャパシタC1を介してノードN1にクロック信号CLKが供給されることにより、同クロック信号CLKの論理「H(ハイ)」レベル値である電源電圧VDDに基づきその出力電圧Voutとして負の電圧「−VDD」を出力する(負側に昇圧する)タイプのチャージポンプ回路である。

【0004】

次に、図11を参照して同回路の電圧変換動作の概要を説明する。

同図11に示す時刻t1以前のクロック信号CLKが論理「H」レベルにある状態においては、ダイオードD1(あるいはトランジスタTR1)がオンしてノードN1の電圧Vn1はほぼ「0」ボルト(グランド電圧GND)にあるとする。

またこのとき、出力電圧Voutもほぼグランド電圧GNDであるとする。

【0005】

そして図1に示す時刻t1において、クロック信号CLKが論理「L(ロー)」レベル(0ボルト)に低下すると、キャパシタC1によってノード電圧Vn1はほぼ「−VDD」まで引っ張られる。このときダイオードD1(トランジスタTR1)はオフし、ダイオードD2(トランジスタTR2)がオンするため、出力電圧Voutもほぼ「−VDD」となり(図11(c)参照)、出力キャパシタCoutは「−VDD」に充電されることとなる。

【0006】

続いて、時刻t2においてクロック信号CLKが再び論理「H」レベルになると、キャパシタC1によって、ノード電圧Vn1はほぼグランド電圧GNDに引き上げられる。そのため、ダイオードD2(トランジスタTR2)はオフし、出力電圧Voutは出力キャパシタCoutの充電電圧「−VDD」近傍に保持される。

【0007】

次に、時刻t3においてクロック信号CLKが再び論理「L」レベルになると、ノード電圧Vn1は再びほぼ「−VDD」まで引っ張られる。このときダイオードD1(トランジスタTR1)はオフし、ダイオードD2(トランジスタTR2)がオンするため、出力電圧Voutは再び「−VDD」となり、出力キャパシタCoutは−VDDに充電されることとなる。このような出力キャパシタCoutへの充電が繰り返されることによって、出力電圧Voutはほぼ「−VDD」に保持されるようになる。

【0008】

なお、このようなチャージポンプ回路は、キャパシタC1,Coutを外付けするだけでIC(集積回路)化が可能なため、IC内において所望の電圧値を得るための電圧変換手段として、例えばCCD(電荷移送素子)ドライバの電源回路やメモリIC等に使用されている。

【0009】

【発明が解決しようとする課題】

ところで、こうしたチャージポンプ回路においては、簡単な構成にて電圧変換を行うことができる、すなわち電圧を昇圧したり降圧したりすることができるものの、上記ダイオードD1,D2(あるいはトランジスタT1,T2)のしきい値電圧Vthによる電圧降下の影響によって、その出力電圧の絶対値が減少してしまうという不都合が生じる。例えば、上記従来のチャージポンプ回路にあっては、その出力電圧の絶対値の理論値は(VDD−2Vth)となり、その最大理論値VDDより2Vthだけ低下することとなる。そして、このような出力電圧の絶対値の低下が、チャージポンプ回路としての電圧変換効率の低下を招いている。

【0010】

なお、このしきい値電圧Vthによる出力電圧(絶対値)の低下を回避すべく、例えば先の図(b)に示したPチャネル型MOSトランジスタT1,T2をダイオード結線とせずトランジスタ結線とすることも考えられるが、その場合には、それらトランジスタのオン・オフ制御時の貫通電流等による電圧変換効率の低下や、トランジスタ自身の信頼性の低下が無視できないものとなる。

【0011】

本発明は上記実情に鑑みてなされたものであり、その目的とするところは、高い信頼性を保ちつつ、その電圧変換効率を向上することの可能なチャージポンプ回路を提供することにある。

【0012】

【課題を解決するための手段】

以下、上記目的を達成するための手段及びその作用効果について記載する。

請求項1記載の発明は、出力端と基準電位端との間に直列接続される複数のスイッチングトランジスタと、互いに隣接するトランジスタ間のノードに一方の端子が接続され、それら隣接するトランジスタのうちの前記基準電位端側のトランジスタの導通制御端子に他方の端子が接続されるキャパシタとを有し、前記複数のトランジスタの各導通制御端子に対して、奇数段と偶数段とで互いに位相の反転するクロック信号を印加して前記出力端に所定の出力電位を発生するチャージポンプ回路において、前記キャパシタの他方の端子とこれに接続されるトランジスタ導通制御端子との間に遅延回路を設け、当該トランジスタの導通制御端子に印加されるクロック信号を所定期間遅延させて前記キャパシタの他方の端子に印加するようにしたことをその要旨とする。

【0013】

請求項2記載の発明は、請求項1記載のチャージポンプ回路において、前記クロック信号は、所定の電源電位と前記ノードの電位との間で動作するバッファ回路を介して前記スイッチングトランジスタの導通制御端子に印加されることをその要旨とする。

【0014】

請求項3記載の発明は、請求項1または2に記載のチャージポンプ回路において、前記複数のスイッチングトランジスタの奇数段と偶数段とが同時に非導通状態となる期間を設定するように前記互いに位相の反転したクロック信号のタイミングを調整するタイミング調整回路をさらに備えることをその要旨とする。

【0015】

請求項4記載の発明は、請求項3記載のチャージポンプ回路において、前記タイミング調整回路は、前記隣接するトランジスタの一方のトランジスタの導通制御端子に印加されるクロック信号を受けてその位相を反転する第1のインバータ回路と、当該チャージポンプ回路に入力されるクロック信号とこの第1のインバータ回路の出力クロック信号とを入力してそのNAND条件をとる第1のNAND回路と、当該チャージポンプ回路に入力されるクロック信号を反転する第2のインバータ回路と、前記隣接するトランジスタの他方のトランジスタの導通制御端子に印加されるクロック信号を受けてその位相を反転する第3のインバータ回路と、これら第2及び第3のインバータ回路の出力クロック信号を入力してそのNAND条件をとる第2のNAND回路とを備え、前記第1及び第2のNAND回路の出力をもって前記タイミングの調整されたクロック信号とすることをその要旨とする。

【0016】

請求項5記載の発明は、請求項3記載のチャージポンプ回路において、前記タイミング調整回路は、当該チャージポンプ回路に入力されるクロック信号を反転する第1のインバータ回路と、前記隣接するトランジスタの一方のトランジスタの導通制御端子に印加されるクロック信号と前記第1のインバータ回路の出力クロック信号とを入力してそのNOR条件をとる第1のNOR回路と、同第1のNOR回路の出力クロック信号を反転する第2のインバータ回路と、当該チャージポンプ回路に入力されるクロック信号と前記隣接するトランジスタの他方のトランジスタの導通制御端子に印加されるクロック信号とを入力してそのNOR条件をとる第2のNOR回路と、同第2のNOR回路の出力クロック信号を反転する第3のインバータ回路とを備え、前記第2及び第3のインバータ回路の出力をもって前記タイミングの調整されたクロック信号とすることをその要旨とする。

【0017】

請求項6記載の発明は、請求項1〜3のいずれか一項に記載のチャージポンプ回路において、前記遅延回路は、前記キャパシタの他方の端子を開放して一旦ハイインピーダンス状態とし、前記トランジスタの導通制御端子に印加される前記クロック信号が反転した後、所定の遅延期間を経過して前記キャパシタの他方の端子に所定の電位を与えることをその要旨とする。

【0018】

請求項7記載の発明は、請求項6記載のチャージポンプ回路において、前記遅延回路は、一対の電源端子の間に直列に接続される一対のトランジスタと、前記一対のトランジスタの導通制御端子を駆動する一対の論理回路と、を備え、前記一対の論理回路の一方が他方の出力と前記クロック信号とを合成して前記一対のトランジスタが同時に非導通状態となる期間を設定し、前記一対のトランジスタの間の電位を前記キャパシタに与えることをその要旨とする。

【0019】

請求項8記載の発明は、請求項7記載のチャージポンプ回路において、前記一対のトランジスタは、高電位側の電源端子と前記キャパシタとの間の導通を制御するPチャネル型トランジスタ及び、低電位側の電源端子と前記キャパシタとの間の導通を制御するNチャネル型トランジスタからなると共に、前記一対の論理回路は、AND回路及びNOR回路からなり、前記AND回路は、入力されるクロック信号と前記Pチャネル型トランジスタの導通制御端子に印加される信号との論理積信号を前記Nチャネル型トランジスタの導通制御端子に印加し、前記NOR回路は、当該遅延回路に入力されるクロック信号と前記AND回路の出力信号とのNOR条件信号を前記スイッチングトランジスタの導通制御端子に印加し、前記NOR回路の出力信号を反転させて前記Pチャネル型トランジスタの導通制御端子に印加することをその要旨とする。

【0020】

【発明の実施の形態】

(第1の実施の形態)

以下、本発明にかかるチャージポンプ回路の第1の実施の形態について、図1及び図2を参照して説明する。なお、本実施の形態にかかるチャージポンプ回路も、電源電圧VDDから出力電圧として負電圧「−VDD」を出力するタイプのチャージポンプ回路である。

【0021】

図1は、本実施の形態にかかるチャージポンプ回路の構成を示すもので、同図1に示すように、この回路は、基本的には先の従来のチャージポンプ回路と同様に、2個のスイッチングトランジスタTR1,TR2、キャパシタC1、及び出力キャパシタCout等を備えて構成される。なお、同トランジスタTR1,TR2は、ここではNチャネル型MOSトランジスタにて構成される

これらチャージポンプ回路としての基本構成に加え、本実施の形態のチャージポンプ回路はさらに、タイミング調整回路10、CMOSインバータ1,2、及びバッファ回路B1を備えている。

【0022】

ここで、タイミング調整回路10は、インバータ11,12,13、NAND回路14,15を備えて構成され、クロック信号CLKを入力し、同クロック信号CLKに基づいて、上記スイッチングトランジスタTR1,TR2をオン・オフさせる制御クロック信号φT1,φT2を生成するとともにそのタイミングを調整する。

【0023】

また、CMOSインバータ1,2は、それぞれそのNチャネル型MOSトランジスタ1a,2aのソース端子Sが上記スイッチングトランジスタTR1,TR2のソース端子S(ノード)に接続される。これは、スイッチングトランジスタTR1,TR2のソースが負電圧となるときに、上記制御クロック信号φT1,φT2の論理「L」レベルの電圧値も負電圧として、同トランジスタTR1,TR2を確実にオフに維持するためである。

【0024】

また、上記バッファ回路B1が上記CMOSインバータ1の出力とキャパシタC1間に設けられている。同バッファ回路B1は、上記制御クロック信号φT1の信号レベルを変換するとともに、同クロック信号φT1を所定時間遅延させ、その遅延されたクロック信号φT1をキャパシタクロック信号φC1としてキャパシタC1に入力する。なお、このバッファ回路は、例えば複数のCMOSインバータ等により形成される。

【0025】

このように、本実施の形態においては上記キャパシタクロック信号φC1を生成することにより、スイッチングトランジスタTR1のゲートにそのオン・オフ信号を印加した後に、同キャパシタクロック信号φC1をキャパシタC1に印加することにより同トランジスタTR1のソース電圧(ノードN1の電圧)Vn1を変化させるようにしている。

【0026】

そのため、スイッチングトランジスタTR1のオン時にあっては、同トランジスタTR1の半導体基板内に形成される寄生トランジスタを導通させる等の不具合が防止され、一方、トランジスタTR1のオフ時にあっては、同トランジスタTR1を介してノード電圧Vn1が変動することも防止されるようになる。

【0027】

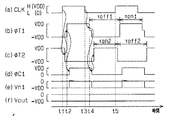

次に、このように構成される本実施の形態のチャージポンプ回路による負電圧の発生動作の概要を図2のタイミングチャートを参照して説明する。なお、同図2においては本チャージポンプ回路の定常的な推移が示され、電源投入時等の過渡的な推移は割愛されている。

【0028】

同図2に示す時刻t1においてクロック信号CLKが論理「H」レベル(VDD)に変化すると(図2(a))、まず上記インバータ12の出力が論理「L」レベル(0ボルト)となり、それに伴ってNAND回路15の出力が論理「H」レベルとなる。それがCMOSインバータ2に入力され、同インバータ2の出力である制御クロック信号φT2が論理「L」レベル「−VDD」となる(図2(c)参照)。

【0029】

このとき、スイッチングトランジスタTR2はオフするとともに、インバータ11の出力が論理「H」レベルとなり、それに伴ってNAND回路14の出力が論理「L」レベル(0ボルト)となる。それがCMOSインバータ1に入力され、同図2に示す時刻t2において、同インバータ1の出力である制御クロック信号φT1が論理「H」レベル(VDD)となる(図2(b)参照)。続いてバッファ回路B1の遅延による所定時間後、キャパシタクロック信号φC1が論理「H」レベル(VDD)となる(図2(d)参照)。この上昇に伴なって、ノード電圧Vn1は「−VDD」から上昇し、その後ほぼ0ボルトとなる(図2(e)参照)。

【0030】

一方、時刻t3においてクロック信号CLKが論理「L」レベル(0ボルト)に変化すると、まず上記NAND回路14の出力が論理「H」レベルとなり、それがCMOSインバータ1に入力され、同図2に示す時刻t4において、同インバータ1の出力である制御クロック信号φT1が「L」レベル「−VDD」となる(図2(b)参照)。このとき、スイッチングトランジスタTR1はオフする。続いてバッファ回路B1の遅延による所定時間後、キャパシタクロック信号φC1が論理「L」レベル(0ボルト)となる(図2(d)参照)。また、このとき、インバータ13の出力が論理「H」レベル(VDD)となり、それに伴ってNAND回路15の出力が論理「L」レベル(0ボルト)となる。それがCMOSインバータ2に入力され、同インバータ2の出力である制御クロック信号φT2が論理「H」レベル(VDD)となる(図2(c)参照)。このときスイッチングトランジスタTR2はオンする。その後、時刻t5においてクロック信号CLKが再び論理「H」レベルに変化すると、上記時刻t1と同様な動作が行われる。

【0031】

本実施の形態のチャージポンプ回路においては、このような動作が繰り返されることによって、スイッチングトランジスタTR1,TR2のしきい電圧Vthの影響がなくなり、ほぼ理論値「−VDD」に近い出力電圧Voutが得られるようになる(図2(f)参照)。

【0032】

また、本実施の形態のチャージポンプ回路においては上述したように、スイッチングトランジスタTR1,TR2が同時にオンされることはない。すなわち、同図2に示されるように、スイッチングトランジスタTR1のオフ期間τoff1内においてスイッチングトランジスタTR2のオン期間τon2が設定され、一方スイッチングトランジスタTR2のオフ期間τoff2内においてスイッチングトランジスタTR1のオン期間τon1が設定される。そのため、効率よく所望の出力電圧Voutが得られるようになるとともに、スイッチングトランジスタTR1,TR2に大きな貫通電流が流れることも防止される。その結果、同トランジスタTR1,TR2の信頼性が向上し、チャージポンプ回路としての信頼性も向上することとなる。

【0033】

以上説明したように、本実施の形態のチャージポンプ回路によれば、以下のような効果を得ることができる。

(1)スイッチングトランジスタTR1のゲート電圧を先に確定してから同トランジスタTR1のソース電圧(ノードN1の電圧)Vn1を変化させるようにしている。そのため、スイッチングトランジスタTR1のスイッチング時における寄生トランジスタの影響、及びノード電圧Vn1の変動等が防止されるようになる。その結果、チャージポンプ回路としての動作がより確実になるとともに、その信頼性も向上するようになる。

【0034】

(2)CMOSインバータ1,2のNチャネル型MOSトランジスタのソース端子SをスイッチングトランジスタTR1,TR2のソース端子Sに接続する構成としている。そのため簡易な構成により、同トランジスタTR1,TR2のオフ動作の維持を確実とするゲート電圧(制御クロック信号φT1,φT2)を得ることができる。

【0035】

(3)タイミング調整回路10によって、スイッチングトランジスタTR1,TR2が同時にオンすることのない制御クロック信号φT1,φT2が形成される。そのため、同トランジスタTR1,TR2に大きな貫通電流の流れることが防止され、同トランジスタTR1,TR2の信頼性が向上するとともに、チャージポンプ回路としての消費電力を低減することができる。

【0036】

(4)電圧変換に際してスイッチングトランジスタTR1,TR2のしきい値電圧Vthの影響を受けない構成としたため、高い到達出力電圧値(絶対値)が得られる。

【0037】

(第2の実施の形態)

次に、本発明にかかるチャージポンプ回路の第2の実施の形態を、前記第1の実施の形態との相違点を中心に図3及び図4を参照して説明する。

【0038】

図3に示されるように、この第2の実施の形態のチャージポンプ回路においては、タイミング調整回路の構成が前記第1の実施の形態のタイミング調整回路10の構成と相違する。また、本実施の形態においては、スイッチングトランジスタを4個、キャパシタを3個備え、電源電圧VDDから出力電圧として負電圧「−3VDD」(理論値)を出力する。

【0039】

さて、本実施の形態のタイミング調整回路20は、3個のインバータ21,22,23、及び2個のNOR回路24,25を備えて構成される。先のタイミング調整回路10と同様に、互いに位相の反転したクロック信号が印加されるスイッチングトランジスタが同時に導通状態となることのないよう、それらクロック信号のタイミングを調整する。

【0040】

また、スイッチングトランジスタTR1,TR2,TR3に対してそれぞれCMOSインバータ1,2,3、バッファ回路B1,B2,B3、及びキャパシタC1,C2,C3がそれぞれ設けられている。また、スイッチングトランジスタTR4にはCMOSインバータ4が設けられている。そして、ここでは制御クロック信号φT1,φT3、制御クロック信号φT2,φT4、及びキャパシタクロック信号φC1,φC3は共通化されている。

【0041】

次に図4のタイミングチャートを参照して、このように構成される本実施の形態のチャージポンプ回路の動作の概要を説明する。

ここでも先の図2に示した場合と同様に、制御クロック信号φT1,φT3をバッファ回路B1,B3を介して遅延させてキャパシタクロック信号φC1,φC3が形成されている(図4(b),(d)参照)。また制御クロック信号φT2をバッファ回路B2を介して遅延させてキャパシタクロック信号φC2が形成されている(図4(c),(e)参照)。

【0042】

また、制御クロック信号φT1,φT3及び制御クロック信号φT2,φT4は、互いに一方の論理レベル「L」(トランジスタ「オフ」)期間内に他方の論理レベル「H」(トランジスタ「オン」)期間が来るように形成されている(図4(b),(c)参照)。すなわち、同図4に示されるように、スイッチングトランジスタTR2,TR4のオフ期間τoff2内においてスイッチングトランジスタTR1,TR3のオン期間τon1が設定され、一方スイッチングトランジスタTR1,TR3のオフ期間τoff1内においてスイッチングトランジスタTR2,TR4のオン期間τon2が設定される。

【0043】

図5に、本実施の形態のチャージポンプ回路がIC(集積回路)内に適用された例として、CCDドライバの構成を示す。同ドライバはフレームトランスファ型CCDを駆動するものである。詳しくは同CCDの撮像部に発生した電荷を蓄積部に一挙に転送する、いわゆる電荷の垂直転送駆動を実現するもので、1チップのIC(集積回路)として形成される。そして、同図5に示すように、負電圧発生用チャージポンプ回路31、高電圧発生用チャージポンプ回路32、及び垂直ドライブ回路33等を備えて構成される。なお、ポンピングキャパシタC1,C2,C3,出力キャパシタCout等は、当該ドライバに外付けされる。

【0044】

そしてここでは、本実施の形態のチャージポンプ回路31によって、理論値出力電圧Voutとしてほぼ−3VDDが得られ、同出力電圧Voutは高電圧発生用チャージポンプ回路32及び垂直ドライブ回路33に出力される。

【0045】

また、高電圧発生用チャージポンプ回路32は、例えば先の図1に示したような回路構成に基づき形成される。なお、同チャージポンプ回路32にあっては、前記スイッチングトランジスタTR1,TR2はPチャネル型MOSトランジスタにて構成されるとともに、同トランジスタTR1のドレイン端子は電源電圧VDDに接続される。また、前記CMOSインバータ1,2を構成するPチャネル型MOSトランジスタのソース(電源側端子)は電源電圧VDDに接続され、一方、そのNチャネル型MOSトランジスタのソースは上記ノードN1に接続される。また、クロック信号CLKは、上記チャージポンプ回路32の出力電圧Voutに基づきレベル変換される。

【0046】

このように構成される本実施の形態のチャージポンプ回路によっても、先の第1の実施の形態の回路と同様に、以下のような効果を得ることができる。

(1)スイッチングトランジスタTR1,TR2,TR3のゲート電圧を先に確定してから各トランジスタTR1,TR2,TR3のソース電圧(ノードN1,N2,N3の電圧)Vn1,Vn2,Vn3を変化させるようにしている。そのため、スイッチングトランジスタTR1,TR2,TR3のスイッチング時における寄生トランジスタの影響、及びノード電圧Vn1,Vn2,Vn3の変動等が防止されるようになる。その結果、チャージポンプ回路としての動作がより確実になるとともに、その信頼性も向上するようになる。

【0047】

(2)CMOSインバータ1,2,3,4のNチャネル型MOSトランジスタのソース端子SをスイッチングトランジスタTR1,TR2,TR3,TR4のソース端子Sに接続する構成としている。そのため簡易な構成により、それらトランジスタTR1,TR2,TR3,TR4のオフ動作の維持を確実とするゲート電圧(制御クロック信号φT1,φT2,φT3,φT4)を得ることができる。

【0048】

(3)タイミング調整回路20によって、スイッチングトランジスタTR1,TR2,TR3,TR4の各隣接するトランジスタが同時にオンすることのない制御クロック信号φT1,φT2,φT3,φT4が形成される。そのため、それらトランジスタTR1,TR2,TR3,TR4に大きな貫通電流の流れることが防止され、同トランジスタTR1,TR2,TR3,TR4の信頼性が向上するとともに、チャージポンプ回路としての消費電力を低減することができる。

【0049】

(4)電圧変換に際してスイッチングトランジスタTR1,TR2,TR3,TR4のしきい値電圧Vthの影響を受けない構成としたため、高い到達出力電圧値(絶対値)が得られる。

【0050】

(第3の実施の形態)

以下、本発明にかかるチャージポンプ回路の第3の実施の形態について、上記第1の実施の形態との相違点を中心に図6及び図7を参照して説明する。

【0051】

図1に示した第1の実施形態においては、スイッチングトランジスタTR1をオン・オフ制御させる制御クロック信号φ1を所定時間遅延させたキャパシタクロックCφ1を生成すべく、バッファ回路B1が設けられた。このように、バッファ回路B1を設けることで、スイッチングトランジスタTR1のゲート電圧を確定してから同トランジスタTR1のソース電圧(ノードN1の電圧)Vn1を変化させることができ、ひいては寄生トランジスタの影響等を防止することができるようになる。

【0052】

ただしこの場合、トランジスタTR1がオンしてからバッファ回路B1が論理「H」レベルの信号を出力するまでの期間において、バッファ回路B1内で無駄な電流が消費される懸念がある。すなわち、トランジスタTR1がオンして、そのドレイン及びソース間が導通されることで、GNDからノードN1へ電流が流れ、ノードN1の電位Vn1が上昇する。そして、これに伴ってバッファ回路B1の出力端子側の電位が変化する。しかし、この時点においては、例えばバッファ回路B1が2段のCMOSインバータで構成される場合、出力側のインバータ内のNチャネル型MOSトランジスタがオンしているために、このMOSトランジスタを介してキャパシタC1から同MOSトランジスタの論理「L」レベル側の給電端子(接地端子)に電流が流れるようになる。

【0053】

このように、バッファ回路B1内において、キャパシタC1への蓄電と関係のない電流が消費されると、チャージポンプ回路としてもその昇圧変換効率が低下する要因となる。特に、バッファ回路B1の出力がキャパシタC1への入力となる関係上、その出力側のMOSトランジスタの駆動電力が大きく設定されているために、上記消費される電力も大きなものとなり、チャージポンプ回路としてのこうした昇圧変換効率の低下が無視できないものとなる。

【0054】

そこで本実施の形態においては、前記制御クロック信号φT1を所定時間遅延させてキャパシタクロックφC1を生成するバッファ回路(遅延回路)を、次のように構成するようにしている。すなわち、上記制御クロック信号φT1が論理「H」レベルとなる以前は、キャパシタC1への給電ラインをハイインピーダンス状態としておき、同制御クロック信号φT1が論理「H」レベルとなった後に、このキャパシタC1への給電ラインの電位が論理「H」レベルになる構成としている。

【0055】

図6に、このように構成されたバッファ回路を備える本実施の形態にかかるチャージポンプ回路を示す。

図6に示されるように、この回路も、基本的には先の第1の実施の形態と同様に、2個のスイッチングトランジスタTR1、TR2と、キャパシタC1、出力キャパシタCout、及びトランジスタTR1やTR2へ供給するクロック信号を調整するタイミング調整回路100を備えて構成される。

【0056】

そして、本実施の形態においては、上記構成に加えて、第1の実施の形態におけるバッファ回路B1の代わりとしてバッファ回路(遅延回路)110を備えている。

【0057】

このバッファ回路110は、電源電圧「VDD」が印加される給電端子112と、同端子112及びキャパシタC1間の導通を制御するPチャネル型MOSトランジスタ111と、接地端子114と、同端子114及びキャパシタC1間の導通を制御するNチャネル型MOSトランジスタ113とを備えている。

【0058】

そしてバッファ回路110においては、上記トランジスタTR1がオンされてから、キャパシタC1に論理「H」レベルの信号が供給されるまでの期間における電力の浪費を抑制すべく、次のような手順で上記各トランジスタ111及び113の制御信号を生成する。すなわち、制御クロック信号φT1を論理「H」レベルにすべく指令信号がタイミング調整回路100から入力されると、この指令信号に基づいてまず、トランジスタ113をオフとする制御信号を生成する。そして、このトランジスタ113をオフとする制御信号に基づいて論理「H」レベルの制御クロック信号φT1を生成する。更に、生成された論理「H」レベルの制御クロック信号φT1に基づいて、トランジスタ111をオン状態とする制御信号を生成する。

【0059】

具体的には、図6に示されるように、バッファ回路110は、タイミング調整回路100から供給される制御クロック信号とトランジスタ111のゲート端子へ印加される制御信号S111との論理積信号を制御信号S113としてトランジスタ113のゲート端子に印加するAND回路115を備えている。また、同バッファ回路110は、タイミング調整回路100から供給される制御クロック信号とAND回路115の出力信号との論理和反転信号(NOR条件信号)を制御クロック信号φT1としてトランジスタTR1のゲート端子に印加するNOR回路116を備えている。更に、同バッファ回路110は、NOR回路116の出力信号の論理反転信号S111を上記制御信号S111としてトランジスタ111のゲート端子へ印加するインバータ117を備えている。

【0060】

上記態様にて構成されるバッファ回路110によれば、トランジスタTR1のゲートへ印加される制御クロック信号φT1が論理「H」レベルになる以前には、トランジスタ113がオフ状態に保たれてキャパシタC1への給電ラインがハイインピーダンスとされる。そして、同制御クロック信号φT1が論理「H」レベルになった後に、トランジスタ111がオン状態とされて、このキャパシタC1への給電ラインに論理「H」レベルの電圧が印加される。

【0061】

一方、タイミング調整回路100は、先の第1の実施の形態と同様、クロック信号CLKを入力し、同クロック信号CLKに基づいて、トランジスタTR1及びTR2が同時にオンすることのないように調整されたクロック信号を生成する。このような調整を行うべく、タイミング調整回路100は、クロック信号CLKの論理レベル変化に伴い、制御クロック信号φT2として論理「L」レベルの信号を出力する場合には、同制御クロック信号φT2に基づいて、バッファ回路110に論理「H」レベルの制御クロック信号φT1を生成するように指令する信号を生成する。更に、タイミング調整回路100は、論理「L」レベルの制御クロック信号φT1を生成するよう指令する信号をバッファ回路110に出力する場合には、この出力される信号に基づいて論理「H」レベルの制御クロック信号φT2を生成する。

【0062】

具体的には、これも図6に示されるように、タイミング調整回路100は、クロック信号CLKを反転させる第1のインバータ101、バッファ回路110内のトランジスタ113のゲート端子に印加される制御信号S113とこの第1のインバータ101の出力信号との論理積信号をトランジスタTR2のゲート端子へ印加するAND回路102とを備えている。更に、タイミング調整回路100は、上記トランジスタTR2のゲート端子に印加される論理積信号を反転させる第2のインバータ103,及びこの第2のインバータ103の出力信号とクロック信号CLKとの論理積反転信号を上述した制御クロック信号φT1の生成を指令する信号としてバッファ回路110へ出力するNAND回路を備えている。

【0063】

なお、図6においては便宜上、先の図1に例示したような、トランジスタTR1及びTR2のソースが負電圧となるときに、この電圧値を上記制御クロック信号φT1、φT2の論理「L」レベルの電圧値とする構成については図示しないこととした。これを実現するためには、例えばAND回路102及びNOR回路116の本来接地される側の給電端子を、これらトランジスタTR1及びTR2のソース端子に接続するなどすればよい。以下では、このように構成されていることを前提にその動作を説明する。

【0064】

次に、上記態様にて構成されるチャージポンプ回路の全体の動作について、図7のタイミングチャートを併せ参照して更に詳述する。

いま、図7に示す時刻t1において、クロック信号CLKが論理「H」レベル(VDD)に変化したとすると(図7(a))、まず、第1のインバータ101の出力が論理「L」レベルに変化するのに伴い、時刻t2において、AND回路102からトランジスタTR2のゲート端子へ印加される制御クロック信号φT2が論理「L」レベル(−VDD)となる(図7(c))。これにより、トランジスタTR2がオフ状態となる。

【0065】

一方、このAND回路102の出力は、第2のインバータ103によって反転され、論理「H」レベルのクロック信号CLKとともに、NAND回路104に入力されるようになる。これにより、NAND回路104では、論理「L」レベルの信号を、制御クロック信号φT1の生成を指令する信号としてバッファ回路110へ出力する。

【0066】

このNAND回路104から出力される論理「L」レベルの信号は、バッファ回路110においてAND回路115に入力され、図7に示す時刻t3において、このAND回路115から論理「L」レベルの信号が上記制御信号S113としてトランジスタ113のゲート端子に印加される(図7(e))。また、このAND回路115から出力される論理「L」レベルの信号は、上記タイミング調整回路100のNAND回路104からの出力信号とともに、NOR回路116に入力される。これにより、図7に示す時刻t4において、NOR回路116からトランジスタTR1のゲート端子へ論理「H」レベルの制御クロック信号φT1が出力される(図7(b))。そして、この論理「H」レベルの制御クロック信号φT1の印加によって、トランジスタTR1がオン状態となる。

【0067】

このように、トランジスタTR1のゲート端子へ論理「H」レベルの制御クロック信号φT1が供給される以前に、まずトランジス113がオフ状態へと制御されるために、トランジスタTR1のオンに起因するキャパシタC1の電位変化(図7(f))に伴って流れるキャパシタC1及び接地端子114間に不要な電流が流れてしまうことを防止することができる。

【0068】

また、上記NOR回路116の出力信号は、インバータ117で反転され、論理「L」レベルの信号が制御信号S111としてトランジスタ111のゲート端子へ印加されるため、図7に示す時刻t5において、トランジスタ111がオン状態となる(図7(d))。これにより、キャパシタC1に加えられる電圧の電位は、論理「H」レベルに固定され(図7(f))、また、時刻t4頃から上昇し始めたノードN1の電位は、グランドレベルに固定される(図7(g))。

【0069】

一方、図7に示す時刻t6において、クロック信号CLKが論理「L」レベル(0ボルト)に変化すると、まず、NAND回路104からバッファ回路110へ出力される信号が論理「H」レベルに変化する。これによりバッファ回路110においては、NOR回路116から出力される制御クロック信号φT1が論理「L」レベルとなり、トランジスタTR1がオフとなる(図7(b))。また、このNOR回路116の出力は、インバータ117を介して論理「H」レベルの制御信号S111としてトランジスタ111のゲート端子に加えられる(図7(d))。

【0070】

更に、このインバータ117の出力は、AND回路115に入力される。同AND回路115では、このインバータ117から出力される論理「H」レベルの信号と上述したNAND回路104から出力される論理「H」レベルの信号との論理積条件に基づき、論理「H」レベルの信号を出力する。そして、この論理「H」レベルの信号が制御信号S113として、トランジスタ113のゲートに印加される(図7(e))とともに、AND回路102に入力される。そして、このAND回路102では、この論理「H」レベルの制御信号S113と、クロック信号CLKがインバータ101を介して反転された論理「H」レベルの信号との論理積条件に基づいて、論理「H」レベルの制御クロック信号φT2を生成し、これをトランジスタTR2のゲート端子に印加する(図7(c))。これにより、トランジスタTR2がオンとなり、同トランジスタTR2を介してノード電圧Vn1が出力電圧Voutとして出力される。

【0071】

本実施の形態にかかるチャージポンプ回路においては、このような動作が繰り返されることで、昇圧効率を好適に維持している。

以上説明したように、本実施の形態によれば、第1の実施の形態の前記(1)〜(4)あるいはこれに準じた効果に加えて、以下の効果が得られるようになる。

【0072】

(5)バッファ回路110のトランジスタ113をオフ状態とした後、トランジスタTR1をオン状態とすることで、トランジスタTR1がオンされてからキャパシタクロック信号φC1が論理「H」レベルとなるまでの間に、キャパシタC1と接地端子114との間で電力が消費されることを的確に回避することができる。

【0073】

(6)トランジスタ113をオフ状態としてからトランジスタ111をオン状態とすることで、トランジスタ113及び111間での貫通電流が流れることも回避される。

【0074】

(7)トランジスタ111がオフ状態となってからトランジスタ113をオン状態とすることで、トランジスタ113及び111間での貫通電流が流れることも回避される。

【0075】

(第4の実施の形態)

以下、本発明にかかるチャージポンプ回路の第4の実施の形態について、先の第2及び第3の実施の形態との相違点を中心に図8及び図9を参照して説明する。

【0076】

本実施の形態にかかるチャージポンプ回路は、図8に示されるように、先の第2の実施形態と同様、4個のスイッチングトランジスタTR1〜TR4と、3個のキャパシタC1〜C3とを備え、電源電圧「VDD」から出力電圧として負電圧「−3VDD」(理論値)を出力する回路である。そして、これらトランジスタTR1〜TR4のうち、隣接したトランジスタが同時に導通状態となることがないように、タイミング調整回路200を備えている。

【0077】

更に、本実施の形態にかかるチャージポンプ回路は、前述した寄生トランジスタの影響を回避すべく、先の第2の実施の形態におけるバッファ回路B1〜B3の代わりに、バッファ回路210及び220を備えている。ここで、バッファ回路210は、制御クロック信号φT1及びφT3を生成するとともに、同信号を所定期間遅延させて、キャパシタクロック信号φC1及びφC3を出力する回路である。また、バッファ回路220は、制御クロック信号φT2及びφT4を生成するとともに、同信号を所定期間遅延させて、キャパシタクロックφC2及びφC4を出力する回路である。そして、これらバッファ回路210及び220は、先の第3の実施の形態のバッファ回路110と同様の機能を有して、キャパシタC1〜C3と接地との間で電力が消費されることを防止する。

【0078】

すなわち、これらバッファ回路210及び220では、タイミング調整回路200から供給される信号に基づき、スイッチングトランジスタ(TR1〜TR4)のゲートに論理「H」レベルの制御クロック信号を印加する場合に、まず、接地端子(214,224)及びキャパシタ(C1〜C3)間の導通制御を行うトランジスタ(213,223)をオフとする。そして、これらトランジスタ(213,223)をオフとする論理「L」レベルの制御信号(S213,S223)に基づいて、スイッチングトランジスタ(TR1〜TR4)のゲート端子に印加する論理「H」レベルの制御クロック信号(φT1〜φT4)を生成する。次に、この論理「H」レベルの制御クロック信号(φT1〜φT4)に基づいて電源電圧VDDが印加される給電端子(212,222)及びキャパシタ(C1〜C3)間の導通制御を行うトランジスタ(211,221)をオンとする。

【0079】

そして、こうした機能を得るために、バッファ回路210,220はそれぞれ、先の第3の実施形態と同様、AND回路(215,225)と、NOR回路(216,226)と、インバータ(217,227)とを備えて構成されている。

【0080】

一方、上記タイミング調整回路200は、スイッチングトランジスタTR1〜TR4の各々隣接するものが同時にオンすることのないようにタイミング調整された信号を上記各バッファ回路210,220に供給する回路である。すなわち、クロック信号CLKの変化に伴い、制御クロック信号φT1及びφT3が論理「L」レベルになる場合には、バッファ回路210によって生成される同信号φT1及びφT3に基づいて、論理「H」レベルの制御クロック信号φT2及びφT4を生成するように指令する信号をバッファ回路220に対して出力する。逆に、クロック信号CLKの変化に伴い、制御クロック信号φT2及びφT4が論理「L」レベルになる場合には、バッファ回路220によって生成される同信号φT2及びφT4に基づいて、論理「H」レベルの制御クロック信号φT1及びφT3を生成するように指令する信号をバッファ回路210に対して出力する。

【0081】

具体的には、図8に示されるように、タイミング調整回路200は、クロック信号CLKとバッファ回路220のトランジスタ223のゲート端子に印加される信号との論理積反転信号(NAND条件信号)をバッファ回路210に対して出力する第1のNAND回路202を備えている。また、タイミング調整回路200は、クロック信号CLKを反転させるインバータ201を介して加えられる信号とバッファ回路のトランジスタ213のゲートに印加される信号との論理積反転信号をバッファ回路220に対して出力する第2のNAND回路203を備えている。

【0082】

なお、本実施の形態においても、上記スイッチングトランジスタTR1〜TR4を確実にオフさせるために、先の第2の実施形態と同様、それらトランジスタTR1〜TR2のソースが負電圧となるときに、この電圧を上記制御クロック信号φT1〜φT4の論理「L」レベルの電圧値とする構成を採用しているが、図8でのこの具体構成についての図示は割愛した。

【0083】

図9に、本実施の形態にかかるチャージポンプ回路の動作を示す。

図9に示されるように、本実施の形態のチャージポンプ回路においても、基本的には先の第3の実施の形態と同様、スイッチングトランジスタ(TR1〜TR4)がオン状態となってからキャパシタクロック(φC1〜φT3)がオン状態となるまでの遅延期間にキャパシタ(C1〜C3)と接地端子(214,224)との間で電力が消費されることを回避することができる態様で、各種タイミング信号が生成されている。

【0084】

また、トランジスタ(211,221)がオフしてからトランジスタ(213,223)がオン状態となるため、これらトランジスタ間に貫通電流が流れることもなくなる。

【0085】

このため、この第4の実施の形態によっても、第2の実施形態による(1)〜(4)の効果に加えて、第3の実施の形態による前記(5)〜(7)の効果に準じた効果を得ることができるようになる。

【0086】

なお、上記第3及び第4の実施の形態は、以下のように変更して実施することもできる。

・バッファ回路110、210、220の構成は図6或いは図8に例示したものに限られない。特に、バッファ回路内のAND回路やNOR回路等の組み合わせについては、その変更も極めて容易である。すなわち、バッファ回路内に一対の論理回路を備え、、その一方の論理回路が、他方の出力とバッファ回路への入力信号とを合成して、一対の電源端子間に接続される一対のトランジスタが同時に非導通状態となる期間を設定し、同期間の後にキャパシタに所定の電位を与えるものを極めて容易に構成することができる。

【0087】

また、ここでは上記各実施の形態において例示された、低電位の給電端子及びキャパシタ間を遮断させる制御信号に基づいてトランジスタを導通制御する活性信号を生成したり、同活性信号に基づいて高電位の給電端子及びキャパシタ間を導通させる制御信号を生成する構成にも限られない。例えば、配線遅延を利用するなどしてもよい。

【0088】

その他、上記全ての実施の形態に共通に変更可能な要素としては次のようなものがある。

・タイミング調整回路の回路構成は、先の図1及び図3及び図6及び図8に示したタイミング調整回路10,20,100,200の構成に限られるものではない。要は、タイミング調整回路として、互いに位相の反転したクロック信号が印加されるスイッチングトランジスタが同時に導通状態となることのないよう、それらクロック信号のタイミングを調整するものであれば、いかなる回路構成にて構成されるものであってもよい。

【0089】

・スイッチングトランジスタとしてNチャネル型MOSトランジスタを使用する例を示したがこれに限られず、同スイッチングトランジスタとしてはその他、例えばPチャネル型MOSトランジスタを使用しても、あるいはNチャネル及びPチャネル型MOSトランジスタを併用しても、本発明のチャージポンプ回路を構成することはできる。

【0090】

・また、本発明のチャージポンプ回路は、電源電圧VDDを降圧して負電圧を発生させる適用例に限られず、その他、例えば電源電圧VDDを昇圧したり、あるいは負電圧を利用して正電圧を発生させたりする等、様々な電圧変換の態様に適用することができる。

【0091】

・また、スイッチングトランジスタの個数、同トランジスタ間にその一方の電極が接続されてキャパシタ(ポンピングキャパシタ)の個数は任意であり、それぞれ所望の出力電圧Voutを得るに必要な個数を適宜設けるようにすればよい。

【0092】

・また、上記各実施の形態では便宜上、スイッチングトランジスタTR1,TR2,TR3,TR4のソースS及びドレインDについてこれを図1あるいは図3のごとく定めたが、これらの態様に固定されるものではない。

【0093】

・更に、上記第1又は第2の実施形態におけるバッファ回路B1〜B3や、第3及び第4の実施形態におけるバッファ回路110,210,220においては、キャパシタへの給電を行う給電端子を、電位「VDD」、「0」を有するものにそれぞれ設定したが、これに限定されるものでもない。要は、スイッチングトランジスタの導通制御端子に印加されるクロック信号の2値的な値に対応した異なる2つの電位に設定されるものであればよい。そして、これら電位を適宜変更することで、チャージポンプ回路としての昇圧能力を調整することもできる。

【0094】

【発明の効果】

請求項1記載の発明によれば、遅延回路(バッファ回路)により、先にスイッチングトランジスタの例えばゲート端子(導通制御端子)に電圧を印加してから同トランジスタのソース電圧(ノードの電圧)を変化させることができる。そのため、スイッチングトランジスタのスイッチング時における寄生トランジスタ(当該トランジスタの半導体基板内に擬似形成されるトランジスタ)の影響、及びノード電圧の変動等が防止されるようになる。その結果、チャージポンプ回路としての動作がより確実になるとともに、その信頼性も向上するようになる。

【0095】

請求項2記載の発明によれば、所定の電源電位と前記のノード電位との間で動作するバッファ回路を設けることにより、簡易な構成により、前記スイッチングトランジスタのオフ動作の維持を確実とする同トランジスタのゲート電圧(導通制御端子印加クロック信号)を得ることができる。

【0096】

請求項3記載の発明によれば、タイミング調整回路によって、複数のトランジスタの奇数段と偶数段とが同時に非導通状態となる期間を設けるクロック信号が形成される。そのため、それらトランジスタに大きな貫通電流の流れることが防止され、同トランジスタの信頼性が向上するとともに、チャージポンプ回路としての消費電力を低減することができる。

【0097】

請求項4または5記載の発明によれば、前記タイミング調整回路を簡易な回路構成にて好適に形成することができる。

請求項6記載の発明によれば、キャパシタの他方の端子を開放して一旦ハイインピーダンス状態とすることで、トランジスタが導通制御されるのに伴いキャパシタの他方の端子側の線路の電位が上昇したとしても、この遅延回路内で電力が消費されることを回避することができるようになる。更に、同発明によれば、トランジスタに印加されるクロック信号が反転した後に、キャパシタの他方の端子に所定の電位を与えることで、寄生トランジスタ効果等を回避することができるようになる。

【0098】

請求項7及び8記載の発明によれば、請求項6記載の遅延回路を簡易な回路構成にて好適に形成することができる。

【図面の簡単な説明】

【図1】本発明にかかるチャージポンプ回路についてその第1の実施の形態を示す回路図。

【図2】同実施の形態の回路の動作を示すタイミングチャート。

【図3】本発明にかかるチャージポンプ回路についてその第2の実施の形態を示す回路図。

【図4】同実施の形態の回路の動作を示すタイミングチャート。

【図5】同実施の形態の回路の適用例を示すブロック図。

【図6】本発明にかかるチャージポンプ回路についてその第3の実施の形態を示す回路図。

【図7】同実施の形態の回路の動作を示すタイミングチャート。

【図8】本発明にかかるチャージポンプ回路についてその第4の実施の形態を示す回路図。

【図9】同実施の形態の回路の動作を示すタイミングチャート。

【図10】従来のチャージポンプ回路の構成例を示す回路図。

【図11】同従来のチャージポンプ回路の動作を示すタイミングチャート。

【符号の説明】

1,2,3,4…CMOSインバータ、1a,2a…Nチャネル型MOSトランジスタ、10,20,100,200…タイミング調整回路、B1,B2,B3,B4…バッファ回路、C1,C2,C3,C4…キャパシタ、TR1,TR2,TR3,TR4…スイッチングトランジスタ、110,210,220…遅延回路。

Claims (8)

- 出力端と基準電位端との間に直列接続される複数のスイッチングトランジスタと、互いに隣接するトランジスタ間のノードに一方の端子が接続され、それら隣接するトランジスタのうちの前記基準電位端側のトランジスタの導通制御端子に他方の端子が接続されるキャパシタとを有し、前記複数のトランジスタの各導通制御端子に対して、奇数段と偶数段とで互いに位相の反転するクロック信号を印加して前記出力端に所定の出力電位を発生するチャージポンプ回路において、

前記キャパシタの他方の端子とこれに接続されるトランジスタ導通制御端子との間に遅延回路を設け、当該トランジスタの導通制御端子に印加されるクロック信号を所定期間遅延させて前記キャパシタの他方の端子に印加するようにした

ことを特徴とするチャージポンプ回路。 - 前記クロック信号は、所定の電源電位と前記ノードの電位との間で動作するバッファ回路を介して前記スイッチングトランジスタの導通制御端子に印加される請求項1記載のチャージポンプ回路。

- 請求項1または2に記載のチャージポンプ回路において、

前記複数のスイッチングトランジスタの奇数段と偶数段とが同時に非導通状態となる期間を設定するように前記互いに位相の反転したクロック信号のタイミングを調整するタイミング調整回路をさらに備え、

前記タイミング調整回路は、前記キャパシタの他方の端子に印加されたクロック信号に基づいて位相の反転したクロック信号を生成するようにした

ことを特徴とするチャージポンプ回路。 - 前記タイミング調整回路は、前記隣接するトランジスタの一方のトランジスタの導通制御端子に印加されるクロック信号を受けてその位相を反転する第1のインバータ回路と、当該チャージポンプ回路に入力されるクロック信号とこの第1のインバータ回路の出力クロック信号とを入力してそのNAND条件をとる第1のNAND回路と、当該チャージポンプ回路に入力されるクロック信号を反転する第2のインバータ回路と、前記隣接するトランジスタの他方のトランジスタの導通制御端子に印加されるクロック信号を受けてその位相を反転する第3のインバータ回路と、これら第2及び第3のインバータ回路の出力クロック信号を入力してそのNAND条件をとる第2のNAND回路とを備え、前記第1及び第2のNAND回路の出力をもって前記タイミングの調整されたクロック信号とする請求項3記載のチャージポンプ回路。

- 前記タイミング調整回路は、当該チャージポンプ回路に入力されるクロック信号を反転する第1のインバータ回路と、前記隣接するトランジスタの一方のトランジスタの導通制御端子に印加されるクロック信号と前記第1のインバータ回路の出力クロック信号とを入力してそのNOR条件をとる第1のNOR回路と、同第1のNOR回路の出力クロック信号を反転する第2のインバータ回路と、当該チャージポンプ回路に入力されるクロック信号と前記隣接するトランジスタの他方のトランジスタの導通制御端子に印加されるクロック信号とを入力してそのNOR条件をとる第2のNOR回路と、同第2のNOR回路の出力クロック信号を反転する第3のインバータ回路とを備え、前記第2及び第3のインバータ回路の出力をもって前記タイミングの調整されたクロック信号とする請求項3記載のチャージポンプ回路。

- 前記遅延回路は、前記キャパシタの他方の端子を開放して一旦ハイインピーダンス状態とし、前記トランジスタの導通制御端子に印加される前記クロック信号が反転した後、所定の遅延期間を経過して前記キャパシタの他方の端子に所定の電位を与える請求項1〜3のいずれか一項に記載のチャージポンプ回路。

- 前記遅延回路は、一対の電源端子の間に直列に接続される一対のトランジスタと、前記一対のトランジスタの導通制御端子を駆動する一対の論理回路と、を備え、前記一対の論理回路の一方が他方の出力と前記クロック信号とを合成して前記一対のトランジスタが同時に非導通状態となる期間を設定し、前記一対のトランジスタの間の電位を前記キャパシタに与える請求項6記載のチャージポンプ回路。

- 前記一対のトランジスタは、高電位側の電源端子と前記キャパシタとの間の導通を制御するPチャネル型トランジスタ及び、低電位側の電源端子と前記キャパシタとの間の導通を制御するNチャネル型トランジスタからなると共に、前記一対の論理回路は、AND回路及びNOR回路からなり、前記AND回路は、入力されるクロック信号と前記Pチャネル型トランジスタの導通制御端子に印加される信号との論理積信号を前記Nチャネル型トランジスタの導通制御端子に印加し、前記NOR回路は、当該遅延回路に入力されるクロック信号と前記AND回路の出力信号とのNOR条件信号を前記スイッチングトランジスタの導通制御端子に印加し、前記NOR回路の出力信号を反転させて前記Pチャネル型トランジスタの導通制御端子に印加する請求項7記載のチャージポンプ回路。

Priority Applications (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2000331879A JP3702166B2 (ja) | 2000-02-04 | 2000-10-31 | チャージポンプ回路 |

| TW090101856A TW541449B (en) | 2000-02-04 | 2001-01-31 | Charge pump circuit |

| US09/776,011 US6970035B2 (en) | 2000-02-04 | 2001-02-02 | Charge pump circuit |

| KR10-2001-0005336A KR100381489B1 (ko) | 2000-02-04 | 2001-02-05 | 차지 펌프 회로 |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2000026895 | 2000-02-04 | ||

| JP2000-26895 | 2000-02-04 | ||

| JP2000331879A JP3702166B2 (ja) | 2000-02-04 | 2000-10-31 | チャージポンプ回路 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2001292563A JP2001292563A (ja) | 2001-10-19 |

| JP2001292563A5 JP2001292563A5 (ja) | 2004-10-28 |

| JP3702166B2 true JP3702166B2 (ja) | 2005-10-05 |

Family

ID=26584837

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2000331879A Expired - Lifetime JP3702166B2 (ja) | 2000-02-04 | 2000-10-31 | チャージポンプ回路 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US6970035B2 (ja) |

| JP (1) | JP3702166B2 (ja) |

| KR (1) | KR100381489B1 (ja) |

| TW (1) | TW541449B (ja) |

Families Citing this family (20)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| EP1223663A1 (en) * | 2001-01-10 | 2002-07-17 | Koninklijke Philips Electronics N.V. | Local supply generator for a digital CMOS integrated circuit having an analog signal processing circuitry |

| US6661278B1 (en) * | 2002-07-08 | 2003-12-09 | Impinj, Inc. | High voltage charge pump circuit |

| JP4531343B2 (ja) * | 2003-03-26 | 2010-08-25 | 株式会社半導体エネルギー研究所 | 駆動回路 |

| JP2005151468A (ja) | 2003-11-19 | 2005-06-09 | Sanyo Electric Co Ltd | アンプ |

| JP4440058B2 (ja) * | 2004-09-28 | 2010-03-24 | パナソニック株式会社 | 半導体集積回路 |

| JP4576199B2 (ja) * | 2004-10-19 | 2010-11-04 | パナソニック株式会社 | 降圧電圧出力回路 |

| JP2006129127A (ja) * | 2004-10-29 | 2006-05-18 | Olympus Corp | 電圧供給回路及びそれを用いた固体撮像装置 |

| US7095268B2 (en) * | 2005-01-11 | 2006-08-22 | Stmicroelectronics S.R.L. | Single-stage and modular multi-stage clock-booster |

| JP2006203747A (ja) * | 2005-01-24 | 2006-08-03 | Sanyo Electric Co Ltd | チャージポンプ回路 |

| KR100818703B1 (ko) * | 2005-06-29 | 2008-04-01 | 주식회사 하이닉스반도체 | 전압 펌핑장치 |

| JP2007129828A (ja) * | 2005-11-04 | 2007-05-24 | Sanyo Electric Co Ltd | チャージポンプ回路 |

| JP4849907B2 (ja) * | 2006-02-22 | 2012-01-11 | セイコーインスツル株式会社 | チャージポンプ回路 |

| TW200924358A (en) * | 2007-11-16 | 2009-06-01 | Sitronix Technology Corp | Charge pump capable of enhancing power efficiency and output voltage |

| TW200933562A (en) * | 2008-01-31 | 2009-08-01 | Tpo Displays Corp | Images display system |

| JP5300001B2 (ja) * | 2008-10-07 | 2013-09-25 | ルネサスエレクトロニクス株式会社 | 昇圧回路及び半導体集積回路装置 |

| US8710900B2 (en) * | 2012-03-22 | 2014-04-29 | Fairchild Semiconductor Corporation | Methods and apparatus for voltage selection for a MOSFET switch device |

| US9111601B2 (en) * | 2012-06-08 | 2015-08-18 | Qualcomm Incorporated | Negative voltage generators |

| EP2860865A1 (en) * | 2013-10-11 | 2015-04-15 | Dialog Semiconductor GmbH | High efficiency charge pump circuit |

| US9491151B2 (en) * | 2015-01-07 | 2016-11-08 | Ememory Technology Inc. | Memory apparatus, charge pump circuit and voltage pumping method thereof |

| CN107481745B (zh) * | 2016-06-07 | 2020-08-18 | 中芯国际集成电路制造(上海)有限公司 | 一种负升压电路、半导体器件及电子装置 |

Family Cites Families (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS6460259A (en) * | 1987-08-28 | 1989-03-07 | Nippon Denso Co | Charge pump type booster circuit |

| JP2783044B2 (ja) * | 1992-03-23 | 1998-08-06 | 日本電気株式会社 | 昇圧回路 |

| JPH0828965B2 (ja) * | 1992-09-02 | 1996-03-21 | 日本電気株式会社 | 電圧変換回路 |

| JPH06195971A (ja) * | 1992-10-29 | 1994-07-15 | Mitsubishi Electric Corp | 基板電位発生回路 |

| KR960006378B1 (ko) * | 1993-11-18 | 1996-05-15 | 삼성전자주식회사 | 기판전압발생회로의 차아지펌프회로 |

| JPH09282878A (ja) | 1996-04-09 | 1997-10-31 | Mitsubishi Electric Corp | 電位発生回路 |

| JP3488587B2 (ja) * | 1997-01-09 | 2004-01-19 | 株式会社東芝 | 昇圧回路及びこれを備えたicカード |

| US5790393A (en) * | 1997-01-22 | 1998-08-04 | Exar Corporation | Voltage multiplier with adjustable output level |

| JP3571478B2 (ja) | 1997-01-29 | 2004-09-29 | ローム株式会社 | 昇圧回路 |

| US6107862A (en) * | 1997-02-28 | 2000-08-22 | Seiko Instruments Inc. | Charge pump circuit |

| JP4513138B2 (ja) | 1999-05-19 | 2010-07-28 | 株式会社村田製作所 | 積層コンデンサ |

| US6169444B1 (en) * | 1999-07-15 | 2001-01-02 | Maxim Integrated Products, Inc. | Pulse frequency operation of regulated charge pumps |

-

2000

- 2000-10-31 JP JP2000331879A patent/JP3702166B2/ja not_active Expired - Lifetime

-

2001

- 2001-01-31 TW TW090101856A patent/TW541449B/zh not_active IP Right Cessation

- 2001-02-02 US US09/776,011 patent/US6970035B2/en not_active Expired - Lifetime

- 2001-02-05 KR KR10-2001-0005336A patent/KR100381489B1/ko active IP Right Grant

Also Published As

| Publication number | Publication date |

|---|---|

| US20010011919A1 (en) | 2001-08-09 |

| KR20010078330A (ko) | 2001-08-20 |

| JP2001292563A (ja) | 2001-10-19 |

| TW541449B (en) | 2003-07-11 |

| KR100381489B1 (ko) | 2003-04-26 |

| US6970035B2 (en) | 2005-11-29 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP3702166B2 (ja) | チャージポンプ回路 | |

| US6064227A (en) | Output buffer circuit having low breakdown voltage | |

| US5521547A (en) | Boost voltage generating circuit | |

| US6927986B2 (en) | Power supply and PWM circuits | |

| US5698994A (en) | Data output circuit, intermediate potential setting circuit, and semiconductor integrated circuit | |

| JP3123463B2 (ja) | レベル変換回路 | |

| KR20100125474A (ko) | 강압형 스위칭 조절기 | |

| KR20090023671A (ko) | 저전압 트랜지스터를 이용한 전압 업변환 회로 | |

| US7808301B2 (en) | Multiple-stage charge pump circuit with charge recycle circuit | |

| US6208197B1 (en) | Internal charge pump voltage limit control | |

| US5202588A (en) | Substrate bias circuit | |

| JP2001292563A5 (ja) | ||

| JPH06217527A (ja) | 高効率nチャネルチャージポンプ | |

| US8149632B2 (en) | Output circuit for a semiconductor memory device and data output method | |

| JPH0728207B2 (ja) | Cmos駆動回路 | |

| JPH06311732A (ja) | 昇圧回路 | |

| US20150214837A1 (en) | Charge pump circuit | |

| JP3652793B2 (ja) | 半導体装置の電圧変換回路 | |

| JP3600103B2 (ja) | バッファ回路及びバッファ回路を備えるドライバ | |

| EP0996226A2 (en) | Voltage comparator | |

| US10587267B2 (en) | Level shifter circuit generating bipolar clock signals | |

| US6631081B2 (en) | Capacitive high voltage generator | |

| US4496852A (en) | Low power clock generator | |

| US7224187B2 (en) | CMOS buffer circuits and integrated circuits using the same | |

| JP3170923B2 (ja) | 半導体集積回路 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20040601 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20050330 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20050405 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20050602 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20050628 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20050715 |

|

| R151 | Written notification of patent or utility model registration |

Ref document number: 3702166 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R151 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20080722 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20090722 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20090722 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100722 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100722 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110722 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110722 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120722 Year of fee payment: 7 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120722 Year of fee payment: 7 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130722 Year of fee payment: 8 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| EXPY | Cancellation because of completion of term |