JP3640175B2 - 不揮発性半導体記憶装置 - Google Patents

不揮発性半導体記憶装置 Download PDFInfo

- Publication number

- JP3640175B2 JP3640175B2 JP2001115678A JP2001115678A JP3640175B2 JP 3640175 B2 JP3640175 B2 JP 3640175B2 JP 2001115678 A JP2001115678 A JP 2001115678A JP 2001115678 A JP2001115678 A JP 2001115678A JP 3640175 B2 JP3640175 B2 JP 3640175B2

- Authority

- JP

- Japan

- Prior art keywords

- control gate

- sector

- lines

- memory device

- semiconductor memory

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000004065 semiconductor Substances 0.000 title claims description 42

- 239000012535 impurity Substances 0.000 claims description 16

- 150000004767 nitrides Chemical class 0.000 claims description 3

- LPQOADBMXVRBNX-UHFFFAOYSA-N ac1ldcw0 Chemical compound Cl.C1CN(C)CCN1C1=C(F)C=C2C(=O)C(C(O)=O)=CN3CCSC1=C32 LPQOADBMXVRBNX-UHFFFAOYSA-N 0.000 description 35

- 239000002184 metal Substances 0.000 description 26

- 238000010586 diagram Methods 0.000 description 18

- 230000000052 comparative effect Effects 0.000 description 17

- 102100021792 Gamma-sarcoglycan Human genes 0.000 description 3

- 101000616435 Homo sapiens Gamma-sarcoglycan Proteins 0.000 description 3

- 101000873658 Homo sapiens Secretogranin-3 Proteins 0.000 description 3

- 230000006870 function Effects 0.000 description 3

- 230000004048 modification Effects 0.000 description 3

- 238000012986 modification Methods 0.000 description 3

- 101000735365 Homo sapiens Poly(rC)-binding protein 4 Proteins 0.000 description 2

- 101000716809 Homo sapiens Secretogranin-1 Proteins 0.000 description 2

- 101000873676 Homo sapiens Secretogranin-2 Proteins 0.000 description 2

- 102100034956 Poly(rC)-binding protein 4 Human genes 0.000 description 2

- 102100020867 Secretogranin-1 Human genes 0.000 description 2

- 102100035835 Secretogranin-2 Human genes 0.000 description 2

- 229910052581 Si3N4 Inorganic materials 0.000 description 2

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 2

- 230000000694 effects Effects 0.000 description 2

- 230000010354 integration Effects 0.000 description 2

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 2

- 229910052814 silicon oxide Inorganic materials 0.000 description 2

- 101150016268 BLS1 gene Proteins 0.000 description 1

- 101100256382 Candida albicans (strain SC5314 / ATCC MYA-2876) PGA63 gene Proteins 0.000 description 1

- 101100335694 Oryza sativa subsp. japonica G1L6 gene Proteins 0.000 description 1

- 101150092584 SEC31 gene Proteins 0.000 description 1

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 1

- 238000009825 accumulation Methods 0.000 description 1

- 230000002411 adverse Effects 0.000 description 1

- 238000003491 array Methods 0.000 description 1

- 101150070760 cgs1 gene Proteins 0.000 description 1

- 239000004020 conductor Substances 0.000 description 1

- 230000007423 decrease Effects 0.000 description 1

- 230000005684 electric field Effects 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 239000002784 hot electron Substances 0.000 description 1

- 238000000034 method Methods 0.000 description 1

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 1

- 229920005591 polysilicon Polymers 0.000 description 1

- 229910021332 silicide Inorganic materials 0.000 description 1

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical compound [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 description 1

- 229910052710 silicon Inorganic materials 0.000 description 1

- 239000010703 silicon Substances 0.000 description 1

- 239000000758 substrate Substances 0.000 description 1

- 230000005641 tunneling Effects 0.000 description 1

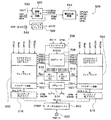

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/34—Determination of programming status, e.g. threshold voltage, overprogramming or underprogramming, retention

- G11C16/3418—Disturbance prevention or evaluation; Refreshing of disturbed memory data

- G11C16/3427—Circuits or methods to prevent or reduce disturbance of the state of a memory cell when neighbouring cells are read or written

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/04—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS

- G11C16/0466—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS comprising cells with charge storage in an insulating layer, e.g. metal-nitride-oxide-silicon [MNOS], silicon-oxide-nitride-oxide-silicon [SONOS]

- G11C16/0475—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS comprising cells with charge storage in an insulating layer, e.g. metal-nitride-oxide-silicon [MNOS], silicon-oxide-nitride-oxide-silicon [SONOS] comprising two or more independent storage sites which store independent data

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C7/00—Arrangements for writing information into, or reading information out from, a digital store

- G11C7/18—Bit line organisation; Bit line lay-out

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/04—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS

- G11C16/0491—Virtual ground arrays

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Non-Volatile Memory (AREA)

- Semiconductor Memories (AREA)

- Read Only Memory (AREA)

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2001115678A JP3640175B2 (ja) | 2001-04-13 | 2001-04-13 | 不揮発性半導体記憶装置 |

| US10/115,956 US6822900B2 (en) | 2001-04-13 | 2002-04-05 | Non-volatile semiconductor memory device |

| CN02122195.2A CN1231921C (zh) | 2001-04-13 | 2002-04-13 | 非易失性半导体存储器件 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2001115678A JP3640175B2 (ja) | 2001-04-13 | 2001-04-13 | 不揮発性半導体記憶装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2002313090A JP2002313090A (ja) | 2002-10-25 |

| JP3640175B2 true JP3640175B2 (ja) | 2005-04-20 |

| JP2002313090A5 JP2002313090A5 (enExample) | 2005-06-02 |

Family

ID=18966541

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2001115678A Expired - Fee Related JP3640175B2 (ja) | 2001-04-13 | 2001-04-13 | 不揮発性半導体記憶装置 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US6822900B2 (enExample) |

| JP (1) | JP3640175B2 (enExample) |

| CN (1) | CN1231921C (enExample) |

Families Citing this family (17)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6532172B2 (en) * | 2001-05-31 | 2003-03-11 | Sandisk Corporation | Steering gate and bit line segmentation in non-volatile memories |

| JP3716914B2 (ja) | 2001-05-31 | 2005-11-16 | セイコーエプソン株式会社 | 不揮発性半導体記憶装置 |

| JP3821032B2 (ja) | 2002-03-20 | 2006-09-13 | セイコーエプソン株式会社 | ファイルストレージ型不揮発性半導体記憶装置 |

| JP3815381B2 (ja) * | 2002-06-06 | 2006-08-30 | セイコーエプソン株式会社 | 不揮発性半導体記憶装置およびその駆動方法 |

| JP3867624B2 (ja) | 2002-06-06 | 2007-01-10 | セイコーエプソン株式会社 | 不揮発性半導体記憶装置およびその駆動方法 |

| JP3871049B2 (ja) | 2002-12-10 | 2007-01-24 | セイコーエプソン株式会社 | 不揮発性半導体記憶装置 |

| JP2004199738A (ja) * | 2002-12-16 | 2004-07-15 | Seiko Epson Corp | 不揮発性記憶装置 |

| JP3985689B2 (ja) * | 2003-02-21 | 2007-10-03 | セイコーエプソン株式会社 | 不揮発性半導体記憶装置 |

| JP3873908B2 (ja) * | 2003-02-28 | 2007-01-31 | セイコーエプソン株式会社 | 不揮発性半導体記憶装置及びその製造方法 |

| JP3786096B2 (ja) * | 2003-02-28 | 2006-06-14 | セイコーエプソン株式会社 | 不揮発性半導体記憶装置 |

| JP3786095B2 (ja) | 2003-02-28 | 2006-06-14 | セイコーエプソン株式会社 | 不揮発性半導体記憶装置 |

| KR100506941B1 (ko) * | 2003-08-19 | 2005-08-05 | 삼성전자주식회사 | 더미 셀들을 갖는 플래쉬 메모리소자 및 그것의 소거방법들 |

| US8233322B2 (en) * | 2003-10-10 | 2012-07-31 | Micron Technology, Inc. | Multi-partition memory with separated read and algorithm datalines |

| FR2871940B1 (fr) * | 2004-06-18 | 2007-06-15 | St Microelectronics Rousset | Transistor mos a grille flottante, a double grille de controle |

| US7130221B1 (en) * | 2005-09-26 | 2006-10-31 | Macronix International Co., Ltd. | Dual gate multi-bit semiconductor memory |

| KR100706789B1 (ko) * | 2005-11-17 | 2007-04-12 | 삼성전자주식회사 | 비휘발성 메모리 소자 |

| US7916551B2 (en) * | 2007-11-06 | 2011-03-29 | Macronix International Co., Ltd. | Method of programming cell in memory and memory apparatus utilizing the method |

Family Cites Families (17)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS63225991A (ja) | 1987-03-16 | 1988-09-20 | Hitachi Ltd | 半導体記憶装置 |

| JPH01300496A (ja) | 1988-05-30 | 1989-12-04 | Hitachi Ltd | 半導体メモリ装置 |

| JPH07161851A (ja) | 1993-12-10 | 1995-06-23 | Sony Corp | 半導体不揮発性記憶装置およびその製造方法 |

| US5408115A (en) | 1994-04-04 | 1995-04-18 | Motorola Inc. | Self-aligned, split-gate EEPROM device |

| US5422504A (en) | 1994-05-02 | 1995-06-06 | Motorola Inc. | EEPROM memory device having a sidewall spacer floating gate electrode and process |

| US5663923A (en) | 1995-04-28 | 1997-09-02 | Intel Corporation | Nonvolatile memory blocking architecture |

| US5969383A (en) | 1997-06-16 | 1999-10-19 | Motorola, Inc. | Split-gate memory device and method for accessing the same |

| JP2978477B1 (ja) | 1998-06-12 | 1999-11-15 | 株式会社日立製作所 | 半導体集積回路装置およびその製造方法 |

| JP3973819B2 (ja) | 1999-03-08 | 2007-09-12 | 株式会社東芝 | 半導体記憶装置およびその製造方法 |

| US6255166B1 (en) | 1999-08-05 | 2001-07-03 | Aalo Lsi Design & Device Technology, Inc. | Nonvolatile memory cell, method of programming the same and nonvolatile memory array |

| US6177318B1 (en) | 1999-10-18 | 2001-01-23 | Halo Lsi Design & Device Technology, Inc. | Integration method for sidewall split gate monos transistor |

| US6248633B1 (en) | 1999-10-25 | 2001-06-19 | Halo Lsi Design & Device Technology, Inc. | Process for making and programming and operating a dual-bit multi-level ballistic MONOS memory |

| JP4899241B2 (ja) * | 1999-12-06 | 2012-03-21 | ソニー株式会社 | 不揮発性半導体記憶装置およびその動作方法 |

| ATE458249T1 (de) * | 2001-03-15 | 2010-03-15 | Halo Inc | Doppelbit monos speicherzellgebrauch für breite programbandbreite |

| JP3780865B2 (ja) * | 2001-04-13 | 2006-05-31 | セイコーエプソン株式会社 | 不揮発性半導体記憶装置 |

| JP4715024B2 (ja) * | 2001-05-08 | 2011-07-06 | セイコーエプソン株式会社 | 不揮発性半導体記憶装置のプログラム方法 |

| US6563736B2 (en) * | 2001-05-18 | 2003-05-13 | Ibm Corporation | Flash memory structure having double celled elements and method for fabricating the same |

-

2001

- 2001-04-13 JP JP2001115678A patent/JP3640175B2/ja not_active Expired - Fee Related

-

2002

- 2002-04-05 US US10/115,956 patent/US6822900B2/en not_active Expired - Fee Related

- 2002-04-13 CN CN02122195.2A patent/CN1231921C/zh not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| CN1231921C (zh) | 2005-12-14 |

| US20030072191A1 (en) | 2003-04-17 |

| JP2002313090A (ja) | 2002-10-25 |

| CN1391232A (zh) | 2003-01-15 |

| US6822900B2 (en) | 2004-11-23 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4715024B2 (ja) | 不揮発性半導体記憶装置のプログラム方法 | |

| JP3659205B2 (ja) | 不揮発性半導体記憶装置及びその駆動方法 | |

| JP3606231B2 (ja) | 不揮発性半導体記憶装置 | |

| JP3640175B2 (ja) | 不揮発性半導体記憶装置 | |

| US6587380B2 (en) | Programming method for non-volatile semiconductor memory device | |

| JP3780865B2 (ja) | 不揮発性半導体記憶装置 | |

| JP3640177B2 (ja) | 不揮発性半導体記憶装置 | |

| JP3640180B2 (ja) | 不揮発性半導体記憶装置 | |

| JP3594001B2 (ja) | 不揮発性半導体記憶装置 | |

| US6707695B2 (en) | Nonvolatile semiconductor memory device | |

| JP3873679B2 (ja) | 半導体容量装置、昇圧回路および不揮発性半導体記憶装置 | |

| JP3640176B2 (ja) | 不揮発性半導体記憶装置 | |

| JP3622697B2 (ja) | 不揮発性半導体記憶装置 | |

| US6650591B2 (en) | Nonvolatile semiconductor memory device | |

| JP3640179B2 (ja) | 不揮発性半導体記憶装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20040811 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20041213 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20041228 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20050110 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20090128 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100128 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110128 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110128 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120128 Year of fee payment: 7 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120128 Year of fee payment: 7 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130128 Year of fee payment: 8 |

|

| LAPS | Cancellation because of no payment of annual fees |