JP2016535487A - ラッチコンパレータ回路および方法 - Google Patents

ラッチコンパレータ回路および方法 Download PDFInfo

- Publication number

- JP2016535487A JP2016535487A JP2016525853A JP2016525853A JP2016535487A JP 2016535487 A JP2016535487 A JP 2016535487A JP 2016525853 A JP2016525853 A JP 2016525853A JP 2016525853 A JP2016525853 A JP 2016525853A JP 2016535487 A JP2016535487 A JP 2016535487A

- Authority

- JP

- Japan

- Prior art keywords

- terminal

- transistor

- coupled

- control terminal

- inverter

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K3/00—Circuits for generating electric pulses; Monostable, bistable or multistable circuits

- H03K3/02—Generators characterised by the type of circuit or by the means used for producing pulses

- H03K3/353—Generators characterised by the type of circuit or by the means used for producing pulses by the use, as active elements, of field-effect transistors with internal or external positive feedback

- H03K3/356—Bistable circuits

- H03K3/356017—Bistable circuits using additional transistors in the input circuit

- H03K3/356034—Bistable circuits using additional transistors in the input circuit the input circuit having a differential configuration

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K3/00—Circuits for generating electric pulses; Monostable, bistable or multistable circuits

- H03K3/02—Generators characterised by the type of circuit or by the means used for producing pulses

- H03K3/027—Generators characterised by the type of circuit or by the means used for producing pulses by the use of logic circuits, with internal or external positive feedback

- H03K3/037—Bistable circuits

- H03K3/0375—Bistable circuits provided with means for increasing reliability; for protection; for ensuring a predetermined initial state when the supply voltage has been applied; for storing the actual state when the supply voltage fails

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K3/00—Circuits for generating electric pulses; Monostable, bistable or multistable circuits

- H03K3/02—Generators characterised by the type of circuit or by the means used for producing pulses

- H03K3/353—Generators characterised by the type of circuit or by the means used for producing pulses by the use, as active elements, of field-effect transistors with internal or external positive feedback

- H03K3/356—Bistable circuits

- H03K3/356069—Bistable circuits using additional transistors in the feedback circuit

Landscapes

- Manipulation Of Pulses (AREA)

- Logic Circuits (AREA)

Abstract

Description

本出願は、すべての目的のために、その内容が全部参照により本明細書に組み込まれる、2013年10月29日に出願された、米国非仮特許出願第14/065,854号の優先権を主張する。

インバータ1の実効相互コンダクタンス:GInv1 = Gm3 + (C2/(C2+Cg5))Gm5

インバータ2の実効相互コンダクタンス:GInv2 = Gm4 + (C1/(C1+Cg6))Gm6

実効容量:Co1 = Cg3 + (C2/(C2+Cg5))Cg5 + CL1

実効容量:Co2 = Cg4 + (C1/(C1+Cg6))Cg6 + CL2

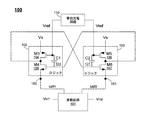

101 差動回路

102 ロジック回路

103 ロジック回路

104 トランジスタ

105 トランジスタ

106 トランジスタ

107 トランジスタ

110 事前充電回路

120 コンデンサ

121 コンデンサ

150 バイアス端子、ノード

151 バイアス端子、ノード

200 ラッチコンパレータ回路

201 トランジスタ

202 トランジスタ

203 トランジスタ

204 トランジスタ

205 トランジスタ

206 トランジスタ

207 トランジスタ

220 事前充電回路

221 事前充電回路

240 トランジスタ

241 トランジスタ

250 トランジスタ

260 抵抗器(R1)

261 抵抗器(R2)

400 ラッチコンパレータ回路

Claims (20)

- 回路であって、

制御端子、第1の端子、および第2の端子を有する第1のトランジスタと、

制御端子、第1の端子、および第2の端子を有する第2のトランジスタであって、前記第1のトランジスタの前記第1の端子が前記第2のトランジスタの前記第1の端子に結合される、第2のトランジスタと、

第1のインバータおよび第2のインバータであって、前記第1のインバータの出力が前記第2のインバータの入力に結合され、前記第2のインバータの出力が前記第1のインバータの入力に結合され、前記第1のインバータのバイアス端子が前記第1のトランジスタの前記第2の端子に結合され、前記第2のインバータのバイアス端子が前記第2のトランジスタの前記第2の端子に結合される、第1のインバータおよび第2のインバータと

を備え、

前記第1のインバータが、

制御端子、第1の端子、および第2の端子を有する第3のトランジスタ、

制御端子、第1の端子、および第2の端子を有する第4のトランジスタ、ならびに

前記第3のトランジスタの前記制御端子と前記第4のトランジスタの前記制御端子との間に結合される第1のコンデンサ

を備え、

前記第2のインバータが、

制御端子、第1の端子、および第2の端子を有する第5のトランジスタ、

制御端子、第1の端子、および第2の端子を有する第6のトランジスタ、ならびに

前記第5のトランジスタの前記制御端子と前記第6のトランジスタの前記制御端子との間に結合される第2のコンデンサ

を備える、回路。 - 前記第1および第2のインバータがディセーブルであるとき、前記第3のトランジスタの前記制御端子上の電圧が、前記第4のトランジスタの前記制御端子上の電圧よりも低く、前記第5のトランジスタの前記制御端子上の電圧が、前記第6のトランジスタの前記制御端子上の電圧よりも低い、請求項1に記載の回路。

- 前記第1および第2のインバータがディセーブルであるとき、前記第3、第4、第5、および第6のトランジスタの前記第1および第2の端子ならびに前記第4および第6のトランジスタの前記制御端子が基準電圧に結合され、前記第3および第5のトランジスタの前記制御端子が前記基準電圧未満の電圧に結合される、請求項1に記載の回路。

- 前記第1および第2のインバータがディセーブルであるとき、前記第3および第5のトランジスタの前記制御端子が電源電圧未満のMOSトランジスタ閾値電圧に結合される、請求項1に記載の回路。

- 前記第3のトランジスタの前記制御端子および前記第5のトランジスタの前記制御端子に結合される事前充電回路をさらに備える、請求項1に記載の回路。

- 前記事前充電回路が、前記第3のトランジスタの前記制御端子に結合される第1の端子、および第2の端子を有する第7のトランジスタ、ならびに前記第5のトランジスタの前記制御端子に結合される第1の端子を有する第8のトランジスタを備える、請求項5に記載の回路。

- 前記第7のトランジスタの前記第2の端子および前記第8のトランジスタの前記第2の端子が基準発生器に結合される、請求項6に記載の回路。

- 前記基準発生器が、前記第7のトランジスタの前記第2の端子および前記第8のトランジスタの前記第2の端子に結合される制御端子を有する第9のトランジスタを備え、前記第9のトランジスタが、基準電圧に結合される第1の端子ならびに前記第9のトランジスタの前記制御端子および負荷に結合される第2の端子をさらに備える、請求項7に記載の回路。

- 前記事前充電回路が、前記第3のトランジスタの前記制御端子に結合される第1の端子および基準発生器に結合される第2の端子を有する第1の抵抗器、ならびに前記第5のトランジスタの前記制御端子に結合される第1の端子および前記基準発生器に結合される第2の端子を有する第2の抵抗器を備える、請求項5に記載の回路。

- 前記基準発生器が、前記第1の抵抗器の前記第2の端子および前記第2の抵抗器の前記第2の端子に結合される制御端子を有する第9のトランジスタを備え、前記第9のトランジスタが、基準電圧に結合される第1の端子ならびに前記第9のトランジスタの前記制御端子および負荷に結合される第2の端子をさらに備える、請求項9に記載の回路。

- 第1のトランジスタの制御端子上に第1の入力電圧を受け取るステップであって、前記第1のトランジスタが第1の端子および第2の端子を有する、ステップと、

第2のトランジスタの制御端子上に第2の入力電圧を受け取るステップであって、前記第2のトランジスタが第1の端子および第2の端子を有し、前記第2のトランジスタの前記第1の端子が前記第1のトランジスタの前記第1の端子に結合され、第1の基準電圧に選択的に結合される、ステップと、

前記第1のトランジスタの前記第2の端子からの差動信号の第1の成分を第1のインバータのバイアス端子に結合するステップと、

前記第2のトランジスタの前記第2の端子からの前記差動信号の第2の成分を第2のインバータのバイアス端子に結合するステップであって、前記第1のインバータの出力が前記第2のインバータの入力に結合され、前記第2のインバータの出力が前記第1のインバータの入力に結合される、ステップと、

前記第2のインバータの前記出力からの出力信号を、前記第1のインバータの前記入力において第4のトランジスタの制御端子および第1のコンデンサの第1の端子に結合して、前記出力信号を前記第1のコンデンサを通して第3のトランジスタの制御端子に結合するステップと、

前記第1のインバータの前記出力からの出力信号を、前記第2のインバータの前記入力において第6のトランジスタの制御端子および第2のコンデンサの第1の端子に結合して、前記出力信号を前記第2のコンデンサを通して第5のトランジスタの制御端子に結合するステップと

を含む、方法。 - 前記第3のトランジスタの前記制御端子および前記第5のトランジスタの前記制御端子を事前充電するステップをさらに含む、請求項11に記載の方法。

- 事前充電するステップが、前記第3のトランジスタの前記制御端子に結合される第1の端子を有する第7のトランジスタ、および前記第5のトランジスタの前記制御端子に結合される第1の端子を有する第8のトランジスタを通して、第2の基準電圧を選択的に結合するステップを含む、請求項12に記載の方法。

- 第3の基準電圧に結合される第1の端子ならびに第9のトランジスタの制御端子および負荷に結合される第2の端子を有する前記第9のトランジスタ中の前記第2の基準電圧を生成するステップをさらに含む、請求項13に記載の方法。

- 事前充電するステップが、前記第3のトランジスタの前記制御端子に結合される第1の端子を有する第1の抵抗器、および前記第5のトランジスタの前記制御端子に結合される第1の端子を有する第2の抵抗器を通して、第2の基準電圧を結合するステップを含む、請求項12に記載の方法。

- 第3の基準電圧に結合される第1の端子ならびに第9のトランジスタの制御端子および負荷に結合される第2の端子を有する前記第9のトランジスタ中の前記第2の基準電圧を生成するステップをさらに含む、請求項15に記載の方法。

- 前記第1および第2のインバータがディセーブルであるとき、前記第3のトランジスタの前記制御端子上の電圧が、前記第4のトランジスタの前記制御端子上の電圧よりも低く、前記第5のトランジスタの前記制御端子上の電圧が、前記第6のトランジスタの前記制御端子上の電圧よりも低い、請求項11に記載の方法。

- 前記第1および第2のインバータがディセーブルであるとき、前記第3、第4、第5、および第6のトランジスタの前記第1および第2の端子ならびに前記第4および第6のトランジスタの前記制御端子が基準電圧に結合され、前記第3および第5のトランジスタの前記制御端子が前記基準電圧未満の電圧に結合される、請求項11に記載の方法。

- 前記第1および第2のインバータがディセーブルであるとき、前記第3および第5のトランジスタの前記制御端子が電源電圧未満のMOSトランジスタ閾値電圧に結合される、請求項11に記載の方法。

- 第1の電圧および第2の電圧を受け取り、差動信号を作り出すための手段と、

直列に構成される第1の対のトランジスタを備え、前記第1の対のトランジスタの制御端子間に構成される第1のコンデンサを有する第1のロジック回路であって、第1のインバータのバイアス端子が前記差動信号の第1の成分を受け取る、第1のロジック回路と、

直列に構成される第2の対のトランジスタを備え、前記第2の対のトランジスタの制御端子間に構成される第2のコンデンサを有する第2のロジック回路であって、第2のインバータのバイアス端子が前記差動信号の第2の成分を受け取る、第2のロジック回路と

を備え、

前記第1のロジック回路の出力が前記第2のロジック回路の入力に結合され、前記第2のロジック回路の出力が前記第1のロジック回路の入力に結合されて双安定な出力を作り出す、回路。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US14/065,854 | 2013-10-29 | ||

| US14/065,854 US9197198B2 (en) | 2013-10-29 | 2013-10-29 | Latch comparator circuits and methods |

| PCT/US2014/062843 WO2015066142A1 (en) | 2013-10-29 | 2014-10-29 | Latch comparator circuits and methods |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2016535487A true JP2016535487A (ja) | 2016-11-10 |

| JP2016535487A5 JP2016535487A5 (ja) | 2017-11-24 |

Family

ID=51904260

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2016525853A Pending JP2016535487A (ja) | 2013-10-29 | 2014-10-29 | ラッチコンパレータ回路および方法 |

Country Status (6)

| Country | Link |

|---|---|

| US (1) | US9197198B2 (ja) |

| EP (1) | EP3063870A1 (ja) |

| JP (1) | JP2016535487A (ja) |

| KR (1) | KR20160079032A (ja) |

| CN (1) | CN105684310A (ja) |

| WO (1) | WO2015066142A1 (ja) |

Families Citing this family (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US10447290B2 (en) * | 2017-12-11 | 2019-10-15 | Texas Instruments Incorporated | Reduced noise dynamic comparator for a successive approximation register analog-to-digital converter |

| FR3076408B1 (fr) * | 2018-01-04 | 2020-02-07 | Commissariat A L'energie Atomique Et Aux Energies Alternatives | Comparateur compense |

| EP3594950A1 (en) * | 2018-07-11 | 2020-01-15 | Stichting IMEC Nederland | Latched comparator and analog-to-digital converter making use thereof |

| CN111371437A (zh) | 2018-12-26 | 2020-07-03 | 恩智浦美国有限公司 | 锁存比较器电路及方法 |

| GB201918211D0 (en) | 2019-12-11 | 2020-01-22 | Nordic Semiconductor Asa | Low power electronic oscillators |

| US11290073B1 (en) * | 2020-11-20 | 2022-03-29 | Synaptics Incorporated | Self-biased differential transmitter |

Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS6065613A (ja) * | 1983-09-21 | 1985-04-15 | Hitachi Ltd | チヨツパタイプコンパレ−タ |

| US5032744A (en) * | 1989-10-31 | 1991-07-16 | Vlsi Technology, Inc. | High speed comparator with offset cancellation |

| JP2007235718A (ja) * | 2006-03-02 | 2007-09-13 | Nec Electronics Corp | 信号増幅器 |

| US7868663B2 (en) * | 2007-09-04 | 2011-01-11 | Hynix Semiconductor Inc. | Receiver circuit for use in a semiconductor integrated circuit |

| US8072244B1 (en) * | 2010-08-31 | 2011-12-06 | National Tsing Hua University | Current sensing amplifier and method thereof |

Family Cites Families (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4412143A (en) | 1981-03-26 | 1983-10-25 | Ncr Corporation | MOS Sense amplifier |

| US6064250A (en) | 1996-07-29 | 2000-05-16 | Townsend And Townsend And Crew Llp | Various embodiments for a low power adaptive charge pump circuit |

| US6377084B2 (en) | 1999-02-22 | 2002-04-23 | Micron Technology, Inc. | Pseudo-differential amplifiers |

| JP3874733B2 (ja) | 2003-02-28 | 2007-01-31 | 富士通株式会社 | 高速入力信号の受信回路 |

| US7116588B2 (en) * | 2004-09-01 | 2006-10-03 | Micron Technology, Inc. | Low supply voltage temperature compensated reference voltage generator and method |

| JP2011211371A (ja) | 2010-03-29 | 2011-10-20 | Panasonic Corp | 逐次比較型ad変換器用クロック生成回路 |

| US8773169B2 (en) | 2010-10-22 | 2014-07-08 | Analog Devices, Inc. | High frequency signal comparator for SHA-less analog-to-digital converters |

| US8274828B2 (en) | 2010-12-15 | 2012-09-25 | Fs Semiconductor Corp., Ltd. | Structures and methods for reading out non-volatile memory using referencing cells |

| US8493092B2 (en) | 2011-04-18 | 2013-07-23 | Rambus, Inc. | Linear equalizer |

| US8624632B2 (en) | 2012-03-29 | 2014-01-07 | International Business Machines Corporation | Sense amplifier-type latch circuits with static bias current for enhanced operating frequency |

-

2013

- 2013-10-29 US US14/065,854 patent/US9197198B2/en active Active

-

2014

- 2014-10-29 KR KR1020167014013A patent/KR20160079032A/ko not_active Application Discontinuation

- 2014-10-29 EP EP14799612.8A patent/EP3063870A1/en not_active Withdrawn

- 2014-10-29 JP JP2016525853A patent/JP2016535487A/ja active Pending

- 2014-10-29 WO PCT/US2014/062843 patent/WO2015066142A1/en active Application Filing

- 2014-10-29 CN CN201480058825.7A patent/CN105684310A/zh active Pending

Patent Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS6065613A (ja) * | 1983-09-21 | 1985-04-15 | Hitachi Ltd | チヨツパタイプコンパレ−タ |

| US5032744A (en) * | 1989-10-31 | 1991-07-16 | Vlsi Technology, Inc. | High speed comparator with offset cancellation |

| JPH05504871A (ja) * | 1989-10-31 | 1993-07-22 | ヴィ エル エス アイ テクノロジー インコーポレイテッド | オフセットを相殺した高速比較器 |

| JP2007235718A (ja) * | 2006-03-02 | 2007-09-13 | Nec Electronics Corp | 信号増幅器 |

| US7868663B2 (en) * | 2007-09-04 | 2011-01-11 | Hynix Semiconductor Inc. | Receiver circuit for use in a semiconductor integrated circuit |

| US8072244B1 (en) * | 2010-08-31 | 2011-12-06 | National Tsing Hua University | Current sensing amplifier and method thereof |

Also Published As

| Publication number | Publication date |

|---|---|

| US20150116020A1 (en) | 2015-04-30 |

| CN105684310A (zh) | 2016-06-15 |

| US9197198B2 (en) | 2015-11-24 |

| KR20160079032A (ko) | 2016-07-05 |

| EP3063870A1 (en) | 2016-09-07 |

| WO2015066142A1 (en) | 2015-05-07 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP2016535487A (ja) | ラッチコンパレータ回路および方法 | |

| KR102122304B1 (ko) | 낮은-레이턴시 전압 부스트 회로를 갖는 전압 레벨 시프터 | |

| US20150263731A1 (en) | Level shift circuit | |

| US20230299756A1 (en) | Latch circuit and method of operating the same | |

| US8324932B2 (en) | High-speed static XOR circuit | |

| US10447251B2 (en) | Power efficient high speed latch circuits and systems | |

| US9203381B2 (en) | Current mode logic latch | |

| US8816749B2 (en) | Level shifter device | |

| JP2007329518A (ja) | チョッパ型コンパレータ | |

| US20200194039A1 (en) | Strong arm latch with wide common mode range | |

| CN109327209B (zh) | 一种高速可再生比较器电路 | |

| Shubhanand et al. | Design and simulation of a high speed CMOS comparator | |

| Shylu et al. | Design of low power dynamic comparator with reduced kickback noise using clocked PMOS technique | |

| Chiwande et al. | Performance analysis of low voltage, low power dynamic double tail comparator for data convertor application | |

| Liu et al. | A new circuit topology for floating high voltage level shifters | |

| CN110391801B (zh) | 用于产生25%工作周期的时钟的装置 | |

| CN106961271B (zh) | 信号接收装置和信号处理设备 | |

| TWI745245B (zh) | 電壓轉換器與使用其的電路系統 | |

| Puvaneswari et al. | Analysis of energy efficient double tail regenerative comparators | |

| TWI606683B (zh) | 零靜功耗高低多端互補式多位準轉換器 | |

| TWI501558B (zh) | 栓鎖裝置及其應用 | |

| Chacko et al. | Analysis and design of low voltage low noise LVDS receiver | |

| CN115085717A (zh) | 电平转换电路 | |

| Agrawal et al. | Vlsi design of low power high speed domino logic | |

| TW201503581A (zh) | 差動轉單端轉換器 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20171012 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20171012 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20180928 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20181005 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20190513 |