JP2016139452A - 半導体装置の動作方法 - Google Patents

半導体装置の動作方法 Download PDFInfo

- Publication number

- JP2016139452A JP2016139452A JP2016009431A JP2016009431A JP2016139452A JP 2016139452 A JP2016139452 A JP 2016139452A JP 2016009431 A JP2016009431 A JP 2016009431A JP 2016009431 A JP2016009431 A JP 2016009431A JP 2016139452 A JP2016139452 A JP 2016139452A

- Authority

- JP

- Japan

- Prior art keywords

- transistor

- electrode

- period

- potential

- terminal

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Withdrawn

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 262

- 238000000034 method Methods 0.000 title claims description 83

- 239000003990 capacitor Substances 0.000 claims abstract description 68

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 claims description 26

- 229910052760 oxygen Inorganic materials 0.000 claims description 26

- 239000001301 oxygen Substances 0.000 claims description 26

- 229910052710 silicon Inorganic materials 0.000 claims description 25

- 239000010703 silicon Substances 0.000 claims description 25

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 claims description 24

- 229910052782 aluminium Inorganic materials 0.000 claims description 10

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 claims description 10

- 229910052735 hafnium Inorganic materials 0.000 claims description 7

- VBJZVLUMGGDVMO-UHFFFAOYSA-N hafnium atom Chemical compound [Hf] VBJZVLUMGGDVMO-UHFFFAOYSA-N 0.000 claims description 6

- 238000003860 storage Methods 0.000 abstract description 39

- 230000002349 favourable effect Effects 0.000 abstract description 3

- 239000010408 film Substances 0.000 description 258

- 239000010410 layer Substances 0.000 description 77

- 239000013078 crystal Substances 0.000 description 52

- 239000011701 zinc Substances 0.000 description 48

- 239000000758 substrate Substances 0.000 description 29

- 230000008569 process Effects 0.000 description 24

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 22

- 238000010586 diagram Methods 0.000 description 22

- 239000012535 impurity Substances 0.000 description 21

- 238000007667 floating Methods 0.000 description 20

- 230000006870 function Effects 0.000 description 19

- 229910052751 metal Inorganic materials 0.000 description 19

- 230000015572 biosynthetic process Effects 0.000 description 17

- 239000002184 metal Substances 0.000 description 17

- 239000000203 mixture Substances 0.000 description 16

- 229910052739 hydrogen Inorganic materials 0.000 description 13

- 239000001257 hydrogen Substances 0.000 description 13

- 238000012545 processing Methods 0.000 description 12

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N silicon dioxide Inorganic materials O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 12

- 230000008859 change Effects 0.000 description 11

- 238000002173 high-resolution transmission electron microscopy Methods 0.000 description 11

- 229910052757 nitrogen Inorganic materials 0.000 description 11

- 230000007547 defect Effects 0.000 description 10

- 230000005669 field effect Effects 0.000 description 9

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 8

- 230000010287 polarization Effects 0.000 description 8

- 229910052581 Si3N4 Inorganic materials 0.000 description 7

- 238000002003 electron diffraction Methods 0.000 description 7

- 238000002955 isolation Methods 0.000 description 7

- 230000014759 maintenance of location Effects 0.000 description 7

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 7

- 238000004544 sputter deposition Methods 0.000 description 7

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 6

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 6

- XLOMVQKBTHCTTD-UHFFFAOYSA-N Zinc monoxide Chemical compound [Zn]=O XLOMVQKBTHCTTD-UHFFFAOYSA-N 0.000 description 6

- 238000004458 analytical method Methods 0.000 description 6

- 229910052802 copper Inorganic materials 0.000 description 6

- 239000010949 copper Substances 0.000 description 6

- 239000000463 material Substances 0.000 description 6

- 238000005259 measurement Methods 0.000 description 6

- 229910052814 silicon oxide Inorganic materials 0.000 description 6

- 229910052719 titanium Inorganic materials 0.000 description 6

- 239000010936 titanium Substances 0.000 description 6

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 6

- 229910052721 tungsten Inorganic materials 0.000 description 6

- 239000010937 tungsten Substances 0.000 description 6

- 125000004429 atom Chemical group 0.000 description 5

- 239000000969 carrier Substances 0.000 description 5

- AJNVQOSZGJRYEI-UHFFFAOYSA-N digallium;oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[Ga+3].[Ga+3] AJNVQOSZGJRYEI-UHFFFAOYSA-N 0.000 description 5

- 229910001195 gallium oxide Inorganic materials 0.000 description 5

- 150000002431 hydrogen Chemical class 0.000 description 5

- 238000004519 manufacturing process Methods 0.000 description 5

- TWNQGVIAIRXVLR-UHFFFAOYSA-N oxo(oxoalumanyloxy)alumane Chemical compound O=[Al]O[Al]=O TWNQGVIAIRXVLR-UHFFFAOYSA-N 0.000 description 5

- 239000000523 sample Substances 0.000 description 5

- 208000005156 Dehydration Diseases 0.000 description 4

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 4

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 4

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 description 4

- 238000009825 accumulation Methods 0.000 description 4

- 230000000903 blocking effect Effects 0.000 description 4

- 230000018044 dehydration Effects 0.000 description 4

- 238000006297 dehydration reaction Methods 0.000 description 4

- 238000006356 dehydrogenation reaction Methods 0.000 description 4

- 238000009826 distribution Methods 0.000 description 4

- 238000005530 etching Methods 0.000 description 4

- 238000013213 extrapolation Methods 0.000 description 4

- -1 for example Chemical compound 0.000 description 4

- 229910000449 hafnium oxide Inorganic materials 0.000 description 4

- WIHZLLGSGQNAGK-UHFFFAOYSA-N hafnium(4+);oxygen(2-) Chemical compound [O-2].[O-2].[Hf+4] WIHZLLGSGQNAGK-UHFFFAOYSA-N 0.000 description 4

- MRELNEQAGSRDBK-UHFFFAOYSA-N lanthanum(3+);oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[La+3].[La+3] MRELNEQAGSRDBK-UHFFFAOYSA-N 0.000 description 4

- 229910052750 molybdenum Inorganic materials 0.000 description 4

- 239000011733 molybdenum Substances 0.000 description 4

- PLDDOISOJJCEMH-UHFFFAOYSA-N neodymium(3+);oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[Nd+3].[Nd+3] PLDDOISOJJCEMH-UHFFFAOYSA-N 0.000 description 4

- SIWVEOZUMHYXCS-UHFFFAOYSA-N oxo(oxoyttriooxy)yttrium Chemical compound O=[Y]O[Y]=O SIWVEOZUMHYXCS-UHFFFAOYSA-N 0.000 description 4

- 230000000717 retained effect Effects 0.000 description 4

- 229910018137 Al-Zn Inorganic materials 0.000 description 3

- 229910018573 Al—Zn Inorganic materials 0.000 description 3

- 229910052684 Cerium Inorganic materials 0.000 description 3

- 238000002441 X-ray diffraction Methods 0.000 description 3

- GPBUGPUPKAGMDK-UHFFFAOYSA-N azanylidynemolybdenum Chemical compound [Mo]#N GPBUGPUPKAGMDK-UHFFFAOYSA-N 0.000 description 3

- 238000009792 diffusion process Methods 0.000 description 3

- 125000005843 halogen group Chemical group 0.000 description 3

- 238000010438 heat treatment Methods 0.000 description 3

- 239000012212 insulator Substances 0.000 description 3

- 229910052746 lanthanum Inorganic materials 0.000 description 3

- 239000011159 matrix material Substances 0.000 description 3

- 229920006395 saturated elastomer Polymers 0.000 description 3

- 239000003381 stabilizer Substances 0.000 description 3

- 238000012916 structural analysis Methods 0.000 description 3

- 239000010409 thin film Substances 0.000 description 3

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 3

- 229910001868 water Inorganic materials 0.000 description 3

- 239000011787 zinc oxide Substances 0.000 description 3

- 229910052726 zirconium Inorganic materials 0.000 description 3

- 229910018120 Al-Ga-Zn Inorganic materials 0.000 description 2

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 2

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 2

- CURLTUGMZLYLDI-UHFFFAOYSA-N Carbon dioxide Chemical compound O=C=O CURLTUGMZLYLDI-UHFFFAOYSA-N 0.000 description 2

- GYHNNYVSQQEPJS-UHFFFAOYSA-N Gallium Chemical compound [Ga] GYHNNYVSQQEPJS-UHFFFAOYSA-N 0.000 description 2

- XEEYBQQBJWHFJM-UHFFFAOYSA-N Iron Chemical compound [Fe] XEEYBQQBJWHFJM-UHFFFAOYSA-N 0.000 description 2

- BPQQTUXANYXVAA-UHFFFAOYSA-N Orthosilicate Chemical compound [O-][Si]([O-])([O-])[O-] BPQQTUXANYXVAA-UHFFFAOYSA-N 0.000 description 2

- 229910000577 Silicon-germanium Inorganic materials 0.000 description 2

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 description 2

- 229910020833 Sn-Al-Zn Inorganic materials 0.000 description 2

- 229910020868 Sn-Ga-Zn Inorganic materials 0.000 description 2

- 229910007541 Zn O Inorganic materials 0.000 description 2

- LEVVHYCKPQWKOP-UHFFFAOYSA-N [Si].[Ge] Chemical compound [Si].[Ge] LEVVHYCKPQWKOP-UHFFFAOYSA-N 0.000 description 2

- 230000005540 biological transmission Effects 0.000 description 2

- 229910052799 carbon Inorganic materials 0.000 description 2

- 238000005229 chemical vapour deposition Methods 0.000 description 2

- 230000000052 comparative effect Effects 0.000 description 2

- 239000004020 conductor Substances 0.000 description 2

- PMHQVHHXPFUNSP-UHFFFAOYSA-M copper(1+);methylsulfanylmethane;bromide Chemical compound Br[Cu].CSC PMHQVHHXPFUNSP-UHFFFAOYSA-M 0.000 description 2

- 230000007423 decrease Effects 0.000 description 2

- 238000007599 discharging Methods 0.000 description 2

- 230000005684 electric field Effects 0.000 description 2

- 238000010894 electron beam technology Methods 0.000 description 2

- 229910052733 gallium Inorganic materials 0.000 description 2

- 239000007789 gas Substances 0.000 description 2

- 229910052732 germanium Inorganic materials 0.000 description 2

- GNPVGFCGXDBREM-UHFFFAOYSA-N germanium atom Chemical compound [Ge] GNPVGFCGXDBREM-UHFFFAOYSA-N 0.000 description 2

- YBMRDBCBODYGJE-UHFFFAOYSA-N germanium oxide Inorganic materials O=[Ge]=O YBMRDBCBODYGJE-UHFFFAOYSA-N 0.000 description 2

- 229910052738 indium Inorganic materials 0.000 description 2

- 229910003437 indium oxide Inorganic materials 0.000 description 2

- PJXISJQVUVHSOJ-UHFFFAOYSA-N indium(iii) oxide Chemical compound [O-2].[O-2].[O-2].[In+3].[In+3] PJXISJQVUVHSOJ-UHFFFAOYSA-N 0.000 description 2

- 238000012905 input function Methods 0.000 description 2

- 239000011810 insulating material Substances 0.000 description 2

- CPLXHLVBOLITMK-UHFFFAOYSA-N magnesium oxide Inorganic materials [Mg]=O CPLXHLVBOLITMK-UHFFFAOYSA-N 0.000 description 2

- 239000000395 magnesium oxide Substances 0.000 description 2

- AXZKOIWUVFPNLO-UHFFFAOYSA-N magnesium;oxygen(2-) Chemical compound [O-2].[Mg+2] AXZKOIWUVFPNLO-UHFFFAOYSA-N 0.000 description 2

- 229910044991 metal oxide Inorganic materials 0.000 description 2

- 150000004706 metal oxides Chemical class 0.000 description 2

- 238000000465 moulding Methods 0.000 description 2

- 229910052759 nickel Inorganic materials 0.000 description 2

- 150000004767 nitrides Chemical class 0.000 description 2

- 230000003647 oxidation Effects 0.000 description 2

- 238000007254 oxidation reaction Methods 0.000 description 2

- PVADDRMAFCOOPC-UHFFFAOYSA-N oxogermanium Chemical compound [Ge]=O PVADDRMAFCOOPC-UHFFFAOYSA-N 0.000 description 2

- BPUBBGLMJRNUCC-UHFFFAOYSA-N oxygen(2-);tantalum(5+) Chemical compound [O-2].[O-2].[O-2].[O-2].[O-2].[Ta+5].[Ta+5] BPUBBGLMJRNUCC-UHFFFAOYSA-N 0.000 description 2

- RVTZCBVAJQQJTK-UHFFFAOYSA-N oxygen(2-);zirconium(4+) Chemical compound [O-2].[O-2].[Zr+4] RVTZCBVAJQQJTK-UHFFFAOYSA-N 0.000 description 2

- 230000000704 physical effect Effects 0.000 description 2

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 2

- 238000000623 plasma-assisted chemical vapour deposition Methods 0.000 description 2

- BASFCYQUMIYNBI-UHFFFAOYSA-N platinum Chemical compound [Pt] BASFCYQUMIYNBI-UHFFFAOYSA-N 0.000 description 2

- 229920005989 resin Polymers 0.000 description 2

- 239000011347 resin Substances 0.000 description 2

- 230000004044 response Effects 0.000 description 2

- 239000002356 single layer Substances 0.000 description 2

- 229910001936 tantalum oxide Inorganic materials 0.000 description 2

- XOLBLPGZBRYERU-UHFFFAOYSA-N tin dioxide Chemical compound O=[Sn]=O XOLBLPGZBRYERU-UHFFFAOYSA-N 0.000 description 2

- 229910001887 tin oxide Inorganic materials 0.000 description 2

- 239000011800 void material Substances 0.000 description 2

- 229910052727 yttrium Inorganic materials 0.000 description 2

- VWQVUPCCIRVNHF-UHFFFAOYSA-N yttrium atom Chemical compound [Y] VWQVUPCCIRVNHF-UHFFFAOYSA-N 0.000 description 2

- 229910001928 zirconium oxide Inorganic materials 0.000 description 2

- 229910000838 Al alloy Inorganic materials 0.000 description 1

- JBRZTFJDHDCESZ-UHFFFAOYSA-N AsGa Chemical compound [As]#[Ga] JBRZTFJDHDCESZ-UHFFFAOYSA-N 0.000 description 1

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 1

- 229910052692 Dysprosium Inorganic materials 0.000 description 1

- 229910052691 Erbium Inorganic materials 0.000 description 1

- 229910052693 Europium Inorganic materials 0.000 description 1

- 229910002601 GaN Inorganic materials 0.000 description 1

- 229910052688 Gadolinium Inorganic materials 0.000 description 1

- 229910001218 Gallium arsenide Inorganic materials 0.000 description 1

- JMASRVWKEDWRBT-UHFFFAOYSA-N Gallium nitride Chemical compound [Ga]#N JMASRVWKEDWRBT-UHFFFAOYSA-N 0.000 description 1

- 229910052689 Holmium Inorganic materials 0.000 description 1

- GPXJNWSHGFTCBW-UHFFFAOYSA-N Indium phosphide Chemical compound [In]#P GPXJNWSHGFTCBW-UHFFFAOYSA-N 0.000 description 1

- 229910052765 Lutetium Inorganic materials 0.000 description 1

- 229910052779 Neodymium Inorganic materials 0.000 description 1

- 229910052777 Praseodymium Inorganic materials 0.000 description 1

- KJTLSVCANCCWHF-UHFFFAOYSA-N Ruthenium Chemical compound [Ru] KJTLSVCANCCWHF-UHFFFAOYSA-N 0.000 description 1

- 229910052772 Samarium Inorganic materials 0.000 description 1

- 229910020944 Sn-Mg Inorganic materials 0.000 description 1

- 229910020994 Sn-Zn Inorganic materials 0.000 description 1

- 229910009069 Sn—Zn Inorganic materials 0.000 description 1

- 238000003917 TEM image Methods 0.000 description 1

- 229910052771 Terbium Inorganic materials 0.000 description 1

- 229910052775 Thulium Inorganic materials 0.000 description 1

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 description 1

- 229910052769 Ytterbium Inorganic materials 0.000 description 1

- QCWXUUIWCKQGHC-UHFFFAOYSA-N Zirconium Chemical compound [Zr] QCWXUUIWCKQGHC-UHFFFAOYSA-N 0.000 description 1

- 229910009369 Zn Mg Inorganic materials 0.000 description 1

- 229910007573 Zn-Mg Inorganic materials 0.000 description 1

- 238000010521 absorption reaction Methods 0.000 description 1

- 230000009471 action Effects 0.000 description 1

- 229910045601 alloy Inorganic materials 0.000 description 1

- 239000000956 alloy Substances 0.000 description 1

- 229910052786 argon Inorganic materials 0.000 description 1

- 238000000231 atomic layer deposition Methods 0.000 description 1

- 238000004364 calculation method Methods 0.000 description 1

- 229910002092 carbon dioxide Inorganic materials 0.000 description 1

- 239000001569 carbon dioxide Substances 0.000 description 1

- GWXLDORMOJMVQZ-UHFFFAOYSA-N cerium Chemical compound [Ce] GWXLDORMOJMVQZ-UHFFFAOYSA-N 0.000 description 1

- 239000000460 chlorine Substances 0.000 description 1

- 229910052801 chlorine Inorganic materials 0.000 description 1

- 229910052804 chromium Inorganic materials 0.000 description 1

- 239000011651 chromium Substances 0.000 description 1

- 150000001875 compounds Chemical class 0.000 description 1

- 239000000470 constituent Substances 0.000 description 1

- 238000002425 crystallisation Methods 0.000 description 1

- 230000008025 crystallization Effects 0.000 description 1

- 238000013461 design Methods 0.000 description 1

- 230000006866 deterioration Effects 0.000 description 1

- 239000006185 dispersion Substances 0.000 description 1

- 239000000428 dust Substances 0.000 description 1

- KBQHZAAAGSGFKK-UHFFFAOYSA-N dysprosium atom Chemical compound [Dy] KBQHZAAAGSGFKK-UHFFFAOYSA-N 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 239000003822 epoxy resin Substances 0.000 description 1

- UYAHIZSMUZPPFV-UHFFFAOYSA-N erbium Chemical compound [Er] UYAHIZSMUZPPFV-UHFFFAOYSA-N 0.000 description 1

- OGPBJKLSAFTDLK-UHFFFAOYSA-N europium atom Chemical compound [Eu] OGPBJKLSAFTDLK-UHFFFAOYSA-N 0.000 description 1

- 239000011737 fluorine Substances 0.000 description 1

- 229910052731 fluorine Inorganic materials 0.000 description 1

- UIWYJDYFSGRHKR-UHFFFAOYSA-N gadolinium atom Chemical compound [Gd] UIWYJDYFSGRHKR-UHFFFAOYSA-N 0.000 description 1

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 1

- 229910001385 heavy metal Inorganic materials 0.000 description 1

- KJZYNXUDTRRSPN-UHFFFAOYSA-N holmium atom Chemical compound [Ho] KJZYNXUDTRRSPN-UHFFFAOYSA-N 0.000 description 1

- 238000003384 imaging method Methods 0.000 description 1

- 230000006872 improvement Effects 0.000 description 1

- APFVFJFRJDLVQX-UHFFFAOYSA-N indium atom Chemical compound [In] APFVFJFRJDLVQX-UHFFFAOYSA-N 0.000 description 1

- 238000003780 insertion Methods 0.000 description 1

- 230000037431 insertion Effects 0.000 description 1

- 238000007689 inspection Methods 0.000 description 1

- 230000010354 integration Effects 0.000 description 1

- 229910052742 iron Inorganic materials 0.000 description 1

- 230000001788 irregular Effects 0.000 description 1

- 229910052747 lanthanoid Inorganic materials 0.000 description 1

- 150000002602 lanthanoids Chemical class 0.000 description 1

- FZLIPJUXYLNCLC-UHFFFAOYSA-N lanthanum atom Chemical compound [La] FZLIPJUXYLNCLC-UHFFFAOYSA-N 0.000 description 1

- 239000004973 liquid crystal related substance Substances 0.000 description 1

- 238000004518 low pressure chemical vapour deposition Methods 0.000 description 1

- OHSVLFRHMCKCQY-UHFFFAOYSA-N lutetium atom Chemical compound [Lu] OHSVLFRHMCKCQY-UHFFFAOYSA-N 0.000 description 1

- 239000011777 magnesium Substances 0.000 description 1

- 238000002488 metal-organic chemical vapour deposition Methods 0.000 description 1

- 239000013081 microcrystal Substances 0.000 description 1

- 229910021421 monocrystalline silicon Inorganic materials 0.000 description 1

- 239000002159 nanocrystal Substances 0.000 description 1

- QEFYFXOXNSNQGX-UHFFFAOYSA-N neodymium atom Chemical compound [Nd] QEFYFXOXNSNQGX-UHFFFAOYSA-N 0.000 description 1

- 230000001590 oxidative effect Effects 0.000 description 1

- 238000006213 oxygenation reaction Methods 0.000 description 1

- 238000007747 plating Methods 0.000 description 1

- 229910052697 platinum Inorganic materials 0.000 description 1

- 229920000647 polyepoxide Polymers 0.000 description 1

- PUDIUYLPXJFUGB-UHFFFAOYSA-N praseodymium atom Chemical compound [Pr] PUDIUYLPXJFUGB-UHFFFAOYSA-N 0.000 description 1

- 238000007639 printing Methods 0.000 description 1

- 239000010453 quartz Substances 0.000 description 1

- 230000009467 reduction Effects 0.000 description 1

- 229910052707 ruthenium Inorganic materials 0.000 description 1

- 229910001925 ruthenium oxide Inorganic materials 0.000 description 1

- WOCIAKWEIIZHES-UHFFFAOYSA-N ruthenium(iv) oxide Chemical compound O=[Ru]=O WOCIAKWEIIZHES-UHFFFAOYSA-N 0.000 description 1

- KZUNJOHGWZRPMI-UHFFFAOYSA-N samarium atom Chemical compound [Sm] KZUNJOHGWZRPMI-UHFFFAOYSA-N 0.000 description 1

- VSZWPYCFIRKVQL-UHFFFAOYSA-N selanylidenegallium;selenium Chemical compound [Se].[Se]=[Ga].[Se]=[Ga] VSZWPYCFIRKVQL-UHFFFAOYSA-N 0.000 description 1

- 238000004904 shortening Methods 0.000 description 1

- HBMJWWWQQXIZIP-UHFFFAOYSA-N silicon carbide Chemical compound [Si+]#[C-] HBMJWWWQQXIZIP-UHFFFAOYSA-N 0.000 description 1

- 229910010271 silicon carbide Inorganic materials 0.000 description 1

- 229910052709 silver Inorganic materials 0.000 description 1

- 239000004332 silver Substances 0.000 description 1

- 238000005476 soldering Methods 0.000 description 1

- CIOAGBVUUVVLOB-UHFFFAOYSA-N strontium atom Chemical compound [Sr] CIOAGBVUUVVLOB-UHFFFAOYSA-N 0.000 description 1

- IATRAKWUXMZMIY-UHFFFAOYSA-N strontium oxide Inorganic materials [O-2].[Sr+2] IATRAKWUXMZMIY-UHFFFAOYSA-N 0.000 description 1

- 239000000126 substance Substances 0.000 description 1

- 229910052715 tantalum Inorganic materials 0.000 description 1

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 1

- JBQYATWDVHIOAR-UHFFFAOYSA-N tellanylidenegermanium Chemical compound [Te]=[Ge] JBQYATWDVHIOAR-UHFFFAOYSA-N 0.000 description 1

- GZCRRIHWUXGPOV-UHFFFAOYSA-N terbium atom Chemical compound [Tb] GZCRRIHWUXGPOV-UHFFFAOYSA-N 0.000 description 1

- 238000012360 testing method Methods 0.000 description 1

- 238000002230 thermal chemical vapour deposition Methods 0.000 description 1

- FRNOGLGSGLTDKL-UHFFFAOYSA-N thulium atom Chemical compound [Tm] FRNOGLGSGLTDKL-UHFFFAOYSA-N 0.000 description 1

- 229910052723 transition metal Inorganic materials 0.000 description 1

- NAWDYIZEMPQZHO-UHFFFAOYSA-N ytterbium Chemical compound [Yb] NAWDYIZEMPQZHO-UHFFFAOYSA-N 0.000 description 1

- 229910052725 zinc Inorganic materials 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C14/00—Digital stores characterised by arrangements of cells having volatile and non-volatile storage properties for back-up when the power is down

- G11C14/0009—Digital stores characterised by arrangements of cells having volatile and non-volatile storage properties for back-up when the power is down in which the volatile element is a DRAM cell

- G11C14/0045—Digital stores characterised by arrangements of cells having volatile and non-volatile storage properties for back-up when the power is down in which the volatile element is a DRAM cell and the nonvolatile element is a resistive RAM element, i.e. programmable resistors, e.g. formed of phase change or chalcogenide material

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C13/00—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00

- G11C13/0002—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using resistive RAM [RRAM] elements

- G11C13/0021—Auxiliary circuits

- G11C13/003—Cell access

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/21—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements

- G11C11/34—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices

- G11C11/40—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors

- G11C11/401—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming cells needing refreshing or charge regeneration, i.e. dynamic cells

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C13/00—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00

- G11C13/0002—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using resistive RAM [RRAM] elements

- G11C13/0021—Auxiliary circuits

- G11C13/004—Reading or sensing circuits or methods

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C13/00—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00

- G11C13/0002—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using resistive RAM [RRAM] elements

- G11C13/0021—Auxiliary circuits

- G11C13/0061—Timing circuits or methods

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C13/00—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00

- G11C13/0002—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using resistive RAM [RRAM] elements

- G11C13/0021—Auxiliary circuits

- G11C13/0069—Writing or programming circuits or methods

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C2213/00—Indexing scheme relating to G11C13/00 for features not covered by this group

- G11C2213/70—Resistive array aspects

- G11C2213/74—Array wherein each memory cell has more than one access device

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C2213/00—Indexing scheme relating to G11C13/00 for features not covered by this group

- G11C2213/70—Resistive array aspects

- G11C2213/79—Array wherein the access device being a transistor

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Computer Hardware Design (AREA)

- Semiconductor Memories (AREA)

- Dram (AREA)

- Thin Film Transistor (AREA)

- Non-Volatile Memory (AREA)

- Power Engineering (AREA)

Abstract

Description

本実施の形態では、本発明の一態様である半導体装置が有する記憶素子の一例について説明する。

本発明の一態様の半導体装置500は、記憶素子50を有する。記憶素子50は、容量素子150を有し、容量素子150は、電極51と、電極52と、電極51と電極52に挟まれた誘電体と、を有する。また、記憶素子50は、電極51に電気的に接続するスイッチング素子61を有することが好ましい。

次に、図1(A)に示す半導体装置500が有する記憶素子50の一例として、記憶素子50が有するスイッチング素子61がトランジスタ100である例を図6(A)を用いて説明する。

次に、半導体装置500が有する記憶素子50の駆動方法の一例を図12のフローに示す。ステップS101として書き込みセットアップ(Write setup)期間を設ける。次に、ステップS102として、スイッチング素子をオン状態として書き込みを行う。次に、ステップS103として、スイッチング素子をオフして、書き込みホールド(Write hold)期間を設ける。ステップS101乃至S103を合わせてステップS100と呼ぶ。次に、ステップS302として、再びスイッチング素子をオン状態として書き込みを行う。次に、ステップS303として、スイッチング素子をオフして、書き込みホールド(Write hold)期間を設ける。ステップS302およびS303を合わせてステップS300と呼ぶ。ステップS300は1回のみでもよいが、2回以上繰り返し行ってもよい。ここで、スイッチング素子がオン状態とする信号を入力する期間の終了時から、次にスイッチング素子がオン状態とする信号を入力する期間の開始時までの時間ΔTは、ステップS103の時間となる。

図6(A)、図7(A)および図7(B)に示すトランジスタ100に用いることのできるトランジスタについて説明する。

本実施の形態では、上記実施の形態で説明したOSトランジスタについて説明する。

OSトランジスタは、酸化物半導体中の不純物濃度を低減し、酸化物半導体を真性または実質的に真性にすることでオフ電流を低くすることができる。ここで、実質的に真性とは、酸化物半導体中のキャリア密度が、1×1013/cm3未満、より好ましくは8×1011/cm3未満、さらに好ましくは1×1011/cm3未満、さらに好ましくは1×1010/cm3未満であり、1×10−9/cm3以上であることを指す。酸化物半導体において、水素、窒素、炭素、シリコン、および主成分以外の金属元素は不純物となる。例えば、水素および窒素はドナー準位の形成に寄与し、キャリア密度を増大させてしまう。

本明細書において、特に断りがない場合、オフ電流とは、トランジスタがオフ状態(非導通状態、遮断状態、ともいう)にあるときのドレイン電流をいう。オフ状態とは、特に断りがない場合、nチャネル型トランジスタでは、ゲートとソースの間の電圧Vgsがしきい値電圧Vthよりも低い状態、pチャネル型トランジスタでは、ゲートとソースの間の電圧Vgsがしきい値電圧Vthよりも高い状態をいう。例えば、nチャネル型のトランジスタのオフ電流とは、ゲートとソースの間の電圧Vgsがしきい値電圧Vthよりも低いときのドレイン電流を言う場合がある。

なおOSトランジスタの半導体層に用いる酸化物半導体としては、少なくともインジウム(In)又は亜鉛(Zn)を含むことが好ましい。特にIn及びZnを含むことが好ましい。また、それらに加えて、酸素を強く結びつけるスタビライザーを有することが好ましい。スタビライザーとしては、ガリウム(Ga)、スズ(Sn)、ジルコニウム(Zr)、ハフニウム(Hf)及びアルミニウム(Al)の少なくともいずれかを有すればよい。

半導体層を構成する酸化物半導体膜に水素が多量に含まれると、酸化物半導体と結合することによって、水素の一部がドナーとなり、キャリアである電子を生じてしまう。これにより、トランジスタの閾値電圧がマイナス方向にシフトしてしまう。そのため、酸化物半導体膜の形成後において、脱水化処理(脱水素化処理)を行い酸化物半導体膜から、水素、又は水分を除去して不純物が極力含まれないように高純度化することが好ましい。

酸化物半導体の構造について説明する。

本実施の形態では、本発明の一態様である半導体装置の構造について説明する。

図14は、図7(A)の回路図に示す記憶素子50の構造の一例を示す。図14に示す記憶素子50はトランジスタ130およびトランジスタ160の上に、絶縁膜420を有し、絶縁膜420上に絶縁膜421を有し、絶縁膜421上に導電層417等の導電層を有する。また、トランジスタ100は、トランジスタ130およびトランジスタ160の上に積層して設けられる。積層して設けることにより、記憶素子50の回路面積の縮小、すなわち半導体装置のチップ面積を縮小し、小型化を図ることができる。また絶縁膜422は、加熱により酸素の一部をトランジスタ100が有する酸化物半導体膜に供給する機能を有する絶縁膜であることが望ましい。絶縁膜422については後述する。また、容量素子150はトランジスタ100の上に積層して設けられる。また、トランジスタ100は、一対のゲート電極を有し、第1のゲート電極は端子WWLに接続し、第2のゲート電極は端子BGに接続する。

次に、図14乃至図17に示すトランジスタ130およびトランジスタ160に用いることのできるトランジスタについて説明する。ここでは一例として、図15のトランジスタ130について説明するが、図14、図16および図17のトランジスタ130およびトランジスタ160についても以下の説明を参照することができる。

次に、図14乃至図17に示すトランジスタ100に用いることのできるトランジスタについて説明する。トランジスタ100として、上述のOSトランジスタを用いることが好ましい。OSトランジスタとして用いることのできる構造を、図19に示す。

容量素子150が有する誘電体として、例えば酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、酸化アルミニウム、酸化ハフニウム、酸化ガリウムまたはGa−Zn系金属酸化物、窒化シリコンなどを用いればよく、積層または単層で設ける。また、ハフニウムシリケート(HfSiOx)、窒素が添加されたハフニウムシリケート(HfSixOyNz)、窒素が添加されたハフニウムアルミネート(HfAlxOyNz)、酸化イットリウムなどのhigh−k材料を用いてもよい。また、酸化アルミニウム、酸化マグネシウム、酸化シリコン、酸化窒化シリコン、酸化ガリウム、酸化ゲルマニウム、酸化イットリウム、酸化ジルコニウム、酸化ランタン、酸化ネオジム、酸化ハフニウムおよび酸化タンタルなどの酸化物絶縁膜、窒化シリコン、窒化酸化シリコン、窒化アルミニウム、窒化酸化アルミニウムなどの窒化物絶縁膜、または上記材料を混合した膜を用いて形成することができる。

本実施の形態では、上述の実施の形態で説明した半導体装置を電子部品に適用する例、及び該電子部品を具備する電子機器に適用する例について、図26、図27を用いて説明する。

以上の実施の形態、及び実施の形態における各構成の説明について、以下に付記する。

本明細書等において、「上に」、「下に」などの配置を示す語句は、構成同士の位置関係を、図面を参照して説明するために、便宜上用いている。構成同士の位置関係は、各構成を描写する方向に応じて適宜変化する。そのため、配置を示す語句は、明細書で説明した記載に限定されず、状況に応じて適切に言い換えることができる。

本明細書等において、トランジスタの接続関係を説明する際、ソースとドレインとの一方を、「ソース又はドレインの一方」(又は第1電極、又は第1端子)と表記し、ソースとドレインとの他方を「ソース又はドレインの他方」(又は第2電極、又は第2端子)と表記している。これは、トランジスタのソースとドレインは、トランジスタの構造又は動作条件等によって変わるためである。なおトランジスタのソースとドレインの呼称については、ソース(ドレイン)端子や、ソース(ドレイン)電極等、状況に応じて適切に言い換えることができる。

以下では、上記実施の形態中で言及しなかった語句の定義について説明する。

本明細書等において、スイッチとは、導通状態(オン状態)、または、非導通状態(オフ状態)になり、電流を流すか流さないかを制御する機能を有するものをいう。または、スイッチとは、電流を流す経路を選択して切り替える機能を有するものをいう。

本明細書等において、チャネル長とは、例えば、トランジスタの上面図において、半導体(またはトランジスタがオン状態のときに半導体の中で電流の流れる部分)とゲート電極とが重なる領域、またはチャネルが形成される領域における、ソースとドレインとの間の距離をいう。

本明細書等において、チャネル幅とは、例えば、半導体(またはトランジスタがオン状態のときに半導体の中で電流の流れる部分)とゲート電極とが重なる領域、またはチャネルが形成される領域における、ソースとドレインとが向かい合っている部分の長さをいう。

本明細書等において、AとBとが接続されている、とは、AとBとが直接接続されているものの他、電気的に接続されているものを含むものとする。ここで、AとBとが電気的に接続されているとは、AとBとの間で、何らかの電気的作用を有する対象物が存在するとき、AとBとの電気信号の授受を可能とするものをいう。

評価を行った半導体装置は、図20に示した半導体装置500を参照することができる。評価を行った半導体装置500は、図39に示す例などのように、トランジスタ130およびトランジスタ160を形成する層の上に積層して容量を設け、容量を形成する層の上に、トランジスタ100を設けた。またトランジスタ130およびトランジスタ160については、SOI基板を用いたトランジスタを用いた。

次に半導体装置500が有するトランジスタ100の構造および作製条件について説明する。トランジスタ100のチャネル長Lは0.35μm、チャネル幅は0.35μmとした。

次に半導体装置500が有する容量素子150について説明する。容量素子150の誘電体55として、スパッタリング法を用いて酸化アルミニウムを約20nmの厚さで成膜した上に、酸化窒化シリコン膜を10nmの厚さで成膜した。酸化窒化シリコン膜の成膜条件はゲート絶縁膜431に用いた条件と同じとした。また電極52および電極51としてタングステンを用いた。容量素子150の電極面積は10.77μm2、容量素子150の容量は20fF狙いとした。

次に、半導体装置500が有するトランジスタ130およびトランジスタ160について説明する。ゲート絶縁膜である絶縁膜405として、熱酸化を用いて酸化シリコンを10nm形成した。トランジスタ130のチャネル長Lは0.35μm、チャネル幅は1.1μm、トランジスタ160のチャネル長Lは0.35μm、チャネル幅は1.1μmとした。

書き込みには、図21に示すフローを用いた。また、比較例の書き込みとして、図25に示すフローを用いた。ここで、図21に示すステップS500は、図23(A)に示すステップS501乃至ステップS503を有し、ステップS700は、ステップS701乃至ステップS703を有する。

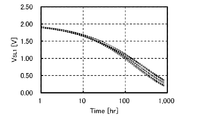

まず、半導体装置500が有する記憶素子50への書き込みを行った。試験温度は150℃とした。まず比較条件Aとして図25のフローに基づき、ステップS100に基づきデータ”1”の書き込みを行った後、ステップS500に基づき読み出しを行い(比較処理A1)、次に、ステップS800に基づき読み出しを行い(比較処理A2)、比較条件AにおけるVSL1を求めた。その後、図25のフローに基づきデータ”0”の書き込みを行った。

42 期間

50 記憶素子

51 電極

52 電極

53 端子

54 端子

55 誘電体

61 スイッチング素子

66 回路

67 回路

71 期間

72 期間

73 期間

74 期間

75 期間

76 期間

77 期間

78 期間

79 期間

80 期間

81 期間

82 期間

83 期間

84 期間

85 期間

86 期間

87 期間

88 期間

91 期間

92 期間

93 期間

94 期間

100 トランジスタ

130 トランジスタ

140 トランジスタ

150 容量素子

160 トランジスタ

400 基板

401 素子分離領域

402 不純物領域

403 不純物領域

404 チャネル形成領域

405 絶縁膜

406 ゲート電極

412 プラグ

413 プラグ

414 プラグ

416 導電層

417 導電層

418 導電層

420 絶縁膜

421 絶縁膜

422 絶縁膜

430 半導体膜

430a 酸化物半導体膜

430b 酸化物半導体膜

430c 酸化物半導体膜

431 ゲート絶縁膜

432 導電層

433 導電層

434 ゲート電極

500 半導体装置

600 回路

700 電子部品

701 リード

702 プリント基板

703 回路部

704 回路基板

901 筐体

902 筐体

903a 表示部

903b 表示部

904 選択ボタン

905 キーボード

910 電子書籍端末

911 筐体

912 筐体

913 表示部

914 表示部

915 軸部

916 電源

917 操作キー

918 スピーカー

920 テレビジョン装置

921 筐体

922 表示部

923 スタンド

924 リモコン操作機

930 本体

931 表示部

932 スピーカー

933 マイク

934 操作ボタン

941 本体

942 表示部

943 操作スイッチ

Claims (12)

- 容量素子と、スイッチング素子と、を有する半導体装置において、

前記容量素子は、第1の電極と、第2の電極と、誘電体と、を有し、

前記誘電体は、第1の電極と第2の電極に挟まれ、

前記スイッチング素子は、第1の端子と、第2の端子と、を有し、

前記第1の端子は、前記第1の電極に電気的に接続され、

前記スイッチング素子を第1の期間においてオン状態とする第1のステップを行い、

前記第1のステップの後に前記スイッチング素子を第2の期間においてオフ状態とする第2のステップを行い、

前記第2の期間は1ns以上500μs未満であり、

前記第2のステップの後に前記スイッチング素子を第3の期間においてオン状態とする第3のステップを行い、

前記第1の期間、第2の期間、および第3の期間は連続して行う半導体装置の動作方法。 - 請求項1において、

前記第1の期間および前記第3の期間は50ps以上1ms以下である半導体装置の動作方法。 - 請求項1または請求項2において、

前記半導体装置は前記スイッチング素子を有する記憶素子を有し、

前記第2の期間において、前記記憶素子の読み出し動作を行わない半導体装置の動作方法。 - 請求項1乃至請求項3のいずれか一項において、

前記誘電体は、珪素、アルミニウムおよびハフニウムから選ばれる少なくとも一の元素と、酸素と、を有し、

前記スイッチング素子は、酸化物半導体を有する半導体装置の動作方法。 - 請求項1乃至請求項4のいずれか一項において、

前記スイッチング素子は、トランジスタであり、

前記トランジスタは、酸化物半導体を有する半導体装置の動作方法。 - 容量素子と、第1のトランジスタと、を有する半導体装置において、

前記容量素子は、第1の電極と、第2の電極と、誘電体と、を有し、

前記誘電体は、第1の電極と第2の電極に挟まれ、

前記第1のトランジスタは、ゲート電極と、第3の電極と、第4の電極と、を有し、

前記第3の電極と前記第4の電極のいずれか一方はソース電極であり、いずれか他方はドレイン電極であり、

前記第3の電極は、前記第1の電極に電気的に接続され、

前記ゲート電極に第1の電位が印加され、前記第2の電極に第2の電位が印加される第1のステップを行い、

前記第1のステップの直後に、前記ゲート電極に第3の電位が印加され、前記第2の電極に第4の電位が印加される第2のステップを行い、

前記第2のステップの直後に、前記ゲート電極に第5の電位が印加され、前記第2の電極に第6の電位が印加される第3のステップを行い、

前記第1の電位と前記第2の電位の差は、前記第3の電位と前記第4の電位の差より大きく、

前記第5の電位と前記第6の電位の差は、前記第3の電位と前記第4の電位の差より大きい半導体装置の動作方法。 - 容量素子と、第1のトランジスタと、を有する半導体装置において、

前記容量素子は、第1の電極と、第2の電極と、誘電体と、を有し、

前記誘電体は、第1の電極と第2の電極に挟まれ、

前記第1のトランジスタは、ゲート電極と、第3の電極と、第4の電極と、を有し、

前記第3の電極と前記第4の電極のいずれか一方はソース電極であり、いずれか他方はドレイン電極であり、

前記第3の電極は、前記第1の電極に電気的に接続され、

前記ゲート電極に第1の電位が、前記第2の電極に第2の電位が、それぞれ印加されることにより前記第1のトランジスタをオン状態とする第1のステップを行い、

前記第1のステップの直後に、前記ゲート電極に第3の電位が、前記第2の電極に第4の電位が、それぞれ印加されることにより前記第1のトランジスタをオフ状態とする第2のステップを行い、

前記第2のステップの直後に、前記ゲート電極に第5の電位が、前記第2の電極に第6の電位が、それぞれ印加されることにより前記第1のトランジスタをオン状態とし、前記第2のステップで前記容量素子において減少した電荷を補う第3のステップを行い、

前記第1の電位と前記第2の電位の差は、前記第3の電位と前記第4の電位の差より大きく、

前記第5の電位と前記第6の電位の差は、前記第3の電位と前記第4の電位の差より大きい半導体装置の動作方法。 - 請求項6または請求項7において、

前記第2の電位と、前記第4の電位の差は0.2V以下である半導体装置の動作方法。 - 請求項6乃至請求項8のいずれか一項において、

前記第2の期間は50ps以上100ms以下であり、

前記第1の期間および前記第3の期間は50ps以上1ms以下である半導体装置の動作方法。 - 請求項6乃至請求項9のいずれか一項において、

前記半導体装置は前記第1のトランジスタを有する記憶素子を有し、

前記第2の期間において、前記記憶素子の読み出し動作を行わない半導体装置の動作方法。 - 請求項6乃至請求項10のいずれか一項において、

前記誘電体は、酸素および珪素を有し、

前記第1のトランジスタは、酸化物半導体を有する半導体装置の動作方法。 - 請求項6乃至請求項11のいずれか一項において、

前記半導体装置は第2のトランジスタを有し、

前記第1の電極は、前記第2のトランジスタのゲート電極に電気的に接続する半導体装置の動作方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2021095739A JP7179913B2 (ja) | 2015-01-23 | 2021-06-08 | 半導体装置の動作方法 |

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2015011714 | 2015-01-23 | ||

| JP2015011714 | 2015-01-23 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2021095739A Division JP7179913B2 (ja) | 2015-01-23 | 2021-06-08 | 半導体装置の動作方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2016139452A true JP2016139452A (ja) | 2016-08-04 |

| JP2016139452A5 JP2016139452A5 (ja) | 2019-02-21 |

Family

ID=56434181

Family Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2016009431A Withdrawn JP2016139452A (ja) | 2015-01-23 | 2016-01-21 | 半導体装置の動作方法 |

| JP2021095739A Active JP7179913B2 (ja) | 2015-01-23 | 2021-06-08 | 半導体装置の動作方法 |

Family Applications After (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2021095739A Active JP7179913B2 (ja) | 2015-01-23 | 2021-06-08 | 半導体装置の動作方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (2) | US9633710B2 (ja) |

| JP (2) | JP2016139452A (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2019130144A1 (ja) * | 2017-12-27 | 2019-07-04 | 株式会社半導体エネルギー研究所 | 記憶装置 |

Families Citing this family (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20180109902A (ko) | 2016-01-29 | 2018-10-08 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치, 전자 부품, 및 전자 기기 |

| SG10201701689UA (en) | 2016-03-18 | 2017-10-30 | Semiconductor Energy Lab | Semiconductor device, semiconductor wafer, and electronic device |

| US9806720B1 (en) | 2016-10-07 | 2017-10-31 | Analog Devices Global | Compound semiconductor based inverter |

Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS5954097A (ja) * | 1982-09-22 | 1984-03-28 | Hitachi Ltd | 半導体メモリ装置 |

| JP2000339977A (ja) * | 1999-05-28 | 2000-12-08 | Nec Corp | データ設定方法および装置、データ記憶装置、情報記憶媒体 |

| JP2007193862A (ja) * | 2006-01-17 | 2007-08-02 | Toshiba Corp | 不揮発性半導体記憶装置 |

| US20110116310A1 (en) * | 2009-11-13 | 2011-05-19 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and driving method thereof |

| JP2011176294A (ja) * | 2010-01-29 | 2011-09-08 | Semiconductor Energy Lab Co Ltd | 半導体記憶装置 |

| US20110286290A1 (en) * | 2010-05-20 | 2011-11-24 | Semiconductor Energy Laboratory Co., Ltd. | Driving method of semiconductor device |

| US20120099368A1 (en) * | 2010-10-20 | 2012-04-26 | Semiconductor Energy Laboratory Co., Ltd. | Method for driving semiconductor device |

Family Cites Families (106)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| DE3171836D1 (en) | 1980-12-08 | 1985-09-19 | Toshiba Kk | Semiconductor memory device |

| JPH01159895A (ja) | 1987-12-17 | 1989-06-22 | Sharp Corp | 電気的に書き込み可能な不揮発性メモリに於けるデータ書き込み方法 |

| US5555204A (en) | 1993-06-29 | 1996-09-10 | Kabushiki Kaisha Toshiba | Non-volatile semiconductor memory device |

| JP3226677B2 (ja) | 1993-09-21 | 2001-11-05 | 株式会社東芝 | 不揮発性半導体記憶装置 |

| KR0169267B1 (ko) | 1993-09-21 | 1999-02-01 | 사토 후미오 | 불휘발성 반도체 기억장치 |

| JP4103968B2 (ja) | 1996-09-18 | 2008-06-18 | 株式会社半導体エネルギー研究所 | 絶縁ゲイト型半導体装置 |

| JP4246400B2 (ja) | 1999-05-13 | 2009-04-02 | 株式会社日立製作所 | 半導体記憶装置 |

| JP2001319486A (ja) | 2000-05-12 | 2001-11-16 | Mitsubishi Electric Corp | 不揮発性半導体記憶装置 |

| JP2001351386A (ja) | 2000-06-07 | 2001-12-21 | Sony Corp | 半導体記憶装置およびその動作方法 |

| JP3875570B2 (ja) | 2001-02-20 | 2007-01-31 | 株式会社東芝 | 半導体記憶装置のデータ書き込み方法及び半導体記憶装置 |

| JP4907011B2 (ja) | 2001-04-27 | 2012-03-28 | 株式会社半導体エネルギー研究所 | 不揮発性メモリとその駆動方法、及び半導体装置 |

| TW559814B (en) | 2001-05-31 | 2003-11-01 | Semiconductor Energy Lab | Nonvolatile memory and method of driving the same |

| US6876572B2 (en) | 2003-05-21 | 2005-04-05 | Altera Corporation | Programmable logic devices with stabilized configuration cells for reduced soft error rates |

| US7336572B1 (en) | 2004-08-19 | 2008-02-26 | Marvell International Ltd. | Detecting sync patterns for optical media |

| JP4728726B2 (ja) | 2005-07-25 | 2011-07-20 | 株式会社東芝 | 半導体記憶装置 |

| EP1998374A3 (en) | 2005-09-29 | 2012-01-18 | Semiconductor Energy Laboratory Co, Ltd. | Semiconductor device having oxide semiconductor layer and manufacturing method thereof |

| JP4199781B2 (ja) * | 2006-04-12 | 2008-12-17 | シャープ株式会社 | 不揮発性半導体記憶装置 |

| JP4354498B2 (ja) | 2007-03-30 | 2009-10-28 | Okiセミコンダクタ株式会社 | 半導体メモリ装置の製造方法及び半導体メモリ装置の再生方法及び半導体メモリ装置の再出荷方法 |

| KR100888847B1 (ko) | 2007-06-28 | 2009-03-17 | 삼성전자주식회사 | 불휘발성 반도체 메모리 장치 및 그것의 프로그램 방법 |

| JP2010021170A (ja) | 2008-07-08 | 2010-01-28 | Hitachi Ltd | 半導体装置およびその製造方法 |

| TWI569454B (zh) | 2008-09-01 | 2017-02-01 | 半導體能源研究所股份有限公司 | 半導體裝置的製造方法 |

| KR101631454B1 (ko) | 2008-10-31 | 2016-06-17 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 논리회로 |

| CN101740631B (zh) | 2008-11-07 | 2014-07-16 | 株式会社半导体能源研究所 | 半导体装置及该半导体装置的制造方法 |

| JP2010135771A (ja) | 2008-11-07 | 2010-06-17 | Semiconductor Energy Lab Co Ltd | 半導体装置及び当該半導体装置の作製方法 |

| JP5781720B2 (ja) | 2008-12-15 | 2015-09-24 | ルネサスエレクトロニクス株式会社 | 半導体装置及び半導体装置の製造方法 |

| US8383470B2 (en) | 2008-12-25 | 2013-02-26 | Semiconductor Energy Laboratory Co., Ltd. | Thin film transistor (TFT) having a protective layer and manufacturing method thereof |

| US8841661B2 (en) | 2009-02-25 | 2014-09-23 | Semiconductor Energy Laboratory Co., Ltd. | Staggered oxide semiconductor TFT semiconductor device and manufacturing method thereof |

| CN102473734B (zh) | 2009-07-31 | 2015-08-12 | 株式会社半导体能源研究所 | 半导体装置及其制造方法 |

| WO2011013502A1 (en) | 2009-07-31 | 2011-02-03 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and manufacturing method thereof |

| EP2284891B1 (en) | 2009-08-07 | 2019-07-24 | Semiconductor Energy Laboratory Co, Ltd. | Semiconductor device and manufacturing method thereof |

| JP5663231B2 (ja) | 2009-08-07 | 2015-02-04 | 株式会社半導体エネルギー研究所 | 発光装置 |

| US8115883B2 (en) | 2009-08-27 | 2012-02-14 | Semiconductor Energy Laboratory Co., Ltd. | Display device and method for manufacturing the same |

| WO2011027656A1 (en) | 2009-09-04 | 2011-03-10 | Semiconductor Energy Laboratory Co., Ltd. | Transistor and display device |

| WO2011027702A1 (en) | 2009-09-04 | 2011-03-10 | Semiconductor Energy Laboratory Co., Ltd. | Light-emitting device and method for manufacturing the same |

| WO2011027676A1 (en) | 2009-09-04 | 2011-03-10 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and manufacturing method thereof |

| KR101746198B1 (ko) | 2009-09-04 | 2017-06-12 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 표시장치 및 전자기기 |

| WO2011027701A1 (en) | 2009-09-04 | 2011-03-10 | Semiconductor Energy Laboratory Co., Ltd. | Light-emitting device and method for manufacturing the same |

| WO2011027664A1 (en) | 2009-09-04 | 2011-03-10 | Semiconductor Energy Laboratory Co., Ltd. | Liquid crystal display device and method for manufacturing the same |

| CN102484140B (zh) | 2009-09-04 | 2015-04-22 | 株式会社半导体能源研究所 | 半导体器件的制造方法 |

| EP2478563B1 (en) | 2009-09-16 | 2021-04-07 | Semiconductor Energy Laboratory Co, Ltd. | Method for manufacturing a samesemiconductor device |

| JP5537366B2 (ja) | 2009-10-01 | 2014-07-02 | 株式会社半導体エネルギー研究所 | 半導体装置の駆動方法 |

| WO2011043182A1 (en) | 2009-10-05 | 2011-04-14 | Semiconductor Energy Laboratory Co., Ltd. | Method for removing electricity and method for manufacturing semiconductor device |

| KR102689629B1 (ko) | 2009-10-16 | 2024-07-31 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 |

| KR101745747B1 (ko) | 2009-10-16 | 2017-06-27 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 논리 회로 및 반도체 장치 |

| KR102290831B1 (ko) | 2009-10-16 | 2021-08-19 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 액정 표시 장치 및 이를 구비한 전자 장치 |

| KR101962603B1 (ko) | 2009-10-16 | 2019-03-28 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 액정 표시 장치 및 액정 표시 장치를 포함한 전자 기기 |

| KR101772639B1 (ko) | 2009-10-16 | 2017-08-29 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 |

| KR102162746B1 (ko) | 2009-10-21 | 2020-10-07 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 아날로그 회로 및 반도체 장치 |

| JP5730529B2 (ja) | 2009-10-21 | 2015-06-10 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| EP2491586B1 (en) | 2009-10-21 | 2019-11-20 | Semiconductor Energy Laboratory Co. Ltd. | Semiconductor device |

| WO2011052366A1 (en) | 2009-10-30 | 2011-05-05 | Semiconductor Energy Laboratory Co., Ltd. | Voltage regulator circuit |

| KR101837102B1 (ko) | 2009-10-30 | 2018-03-09 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 |

| CN104600074A (zh) | 2009-11-06 | 2015-05-06 | 株式会社半导体能源研究所 | 半导体装置 |

| KR102682982B1 (ko) | 2009-11-20 | 2024-07-10 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 |

| KR101911382B1 (ko) | 2009-11-27 | 2018-10-24 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 |

| US9057758B2 (en) | 2009-12-18 | 2015-06-16 | Semiconductor Energy Laboratory Co., Ltd. | Method for measuring current, method for inspecting semiconductor device, semiconductor device, and test element group |

| JP5740169B2 (ja) | 2010-02-19 | 2015-06-24 | 株式会社半導体エネルギー研究所 | トランジスタの作製方法 |

| KR20120121931A (ko) | 2010-02-19 | 2012-11-06 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 및 그 제조 방법 |

| KR101906151B1 (ko) | 2010-02-19 | 2018-10-11 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 트랜지스터 및 이를 이용한 표시 장치 |

| US20110227082A1 (en) | 2010-03-19 | 2011-09-22 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| JP4838399B2 (ja) * | 2010-03-30 | 2011-12-14 | パナソニック株式会社 | 不揮発性記憶装置及び不揮発性記憶装置への書き込み方法 |

| JP2011237418A (ja) | 2010-04-16 | 2011-11-24 | Semiconductor Energy Lab Co Ltd | 電流測定方法、半導体装置の検査方法、半導体装置、および特性評価用回路 |

| KR20120000499A (ko) | 2010-06-25 | 2012-01-02 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 트랜지스터 및 반도체 장치 |

| WO2012002104A1 (en) | 2010-06-30 | 2012-01-05 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and manufacturing method thereof |

| US8785241B2 (en) | 2010-07-16 | 2014-07-22 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and manufacturing method thereof |

| JP5743790B2 (ja) | 2010-08-06 | 2015-07-01 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| TWI555128B (zh) | 2010-08-06 | 2016-10-21 | 半導體能源研究所股份有限公司 | 半導體裝置及半導體裝置的驅動方法 |

| WO2012026503A1 (en) * | 2010-08-27 | 2012-03-01 | Semiconductor Energy Laboratory Co., Ltd. | Memory device and semiconductor device |

| JP2012079399A (ja) | 2010-09-10 | 2012-04-19 | Semiconductor Energy Lab Co Ltd | 半導体装置 |

| US8871565B2 (en) | 2010-09-13 | 2014-10-28 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing semiconductor device |

| KR101932576B1 (ko) | 2010-09-13 | 2018-12-26 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 및 그 제작 방법 |

| US9437743B2 (en) | 2010-10-07 | 2016-09-06 | Semiconductor Energy Laboratory Co., Ltd. | Thin film element, semiconductor device, and method for manufacturing the same |

| US9087744B2 (en) | 2010-11-05 | 2015-07-21 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and method for driving transistor |

| KR101457833B1 (ko) | 2010-12-03 | 2014-11-05 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 |

| JP6030298B2 (ja) * | 2010-12-28 | 2016-11-24 | 株式会社半導体エネルギー研究所 | 緩衝記憶装置及び信号処理回路 |

| US9799773B2 (en) | 2011-02-02 | 2017-10-24 | Semiconductor Energy Laboratory Co., Ltd. | Transistor and semiconductor device |

| US8625085B2 (en) | 2011-03-08 | 2014-01-07 | Semiconductor Energy Laboratory Co., Ltd. | Defect evaluation method for semiconductor |

| US8848464B2 (en) | 2011-04-29 | 2014-09-30 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and method of driving semiconductor device |

| US8922464B2 (en) * | 2011-05-11 | 2014-12-30 | Semiconductor Energy Laboratory Co., Ltd. | Active matrix display device and driving method thereof |

| DE112012004061B4 (de) | 2011-09-29 | 2024-06-20 | Semiconductor Energy Laboratory Co., Ltd. | Halbleitervorrichtung |

| DE112012007294B3 (de) | 2011-09-29 | 2019-05-29 | Semiconductor Energy Laboratory Co., Ltd. | Halbleitervorrichtung |

| DE112012007290B3 (de) | 2011-10-14 | 2017-06-29 | Semiconductor Energy Laboratory Co., Ltd. | Halbleitervorrichtung |

| KR20130040706A (ko) | 2011-10-14 | 2013-04-24 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 및 반도체 장치의 제작 방법 |

| KR20130046357A (ko) | 2011-10-27 | 2013-05-07 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 |

| JP6082562B2 (ja) | 2011-10-27 | 2017-02-15 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| CN103137701B (zh) | 2011-11-30 | 2018-01-19 | 株式会社半导体能源研究所 | 晶体管及半导体装置 |

| US8860023B2 (en) | 2012-05-01 | 2014-10-14 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| JP6228753B2 (ja) * | 2012-06-01 | 2017-11-08 | 株式会社半導体エネルギー研究所 | 半導体装置、表示装置、表示モジュール、及び電子機器 |

| EP2880690B1 (en) | 2012-08-03 | 2019-02-27 | Semiconductor Energy Laboratory Co. Ltd. | Semiconductor device with oxide semiconductor stacked film |

| TW202422663A (zh) | 2012-09-14 | 2024-06-01 | 日商半導體能源研究所股份有限公司 | 半導體裝置及其製造方法 |

| JP5954097B2 (ja) | 2012-10-11 | 2016-07-20 | ソニー株式会社 | 表示装置 |

| KR102220279B1 (ko) | 2012-10-19 | 2021-02-24 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 산화물 반도체막을 포함하는 다층막 및 반도체 장치의 제작 방법 |

| TWI649794B (zh) | 2012-11-08 | 2019-02-01 | 日商半導體能源研究所股份有限公司 | 金屬氧化物膜及形成金屬氧化物膜的方法 |

| KR102211596B1 (ko) | 2012-12-28 | 2021-02-03 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 |

| JP6141777B2 (ja) | 2013-02-28 | 2017-06-07 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| KR102153110B1 (ko) | 2013-03-06 | 2020-09-07 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체막 및 반도체 장치 |

| TWI618081B (zh) | 2013-05-30 | 2018-03-11 | 半導體能源研究所股份有限公司 | 半導體裝置的驅動方法 |

| US9035301B2 (en) | 2013-06-19 | 2015-05-19 | Semiconductor Energy Laboratory Co., Ltd. | Imaging device |

| US9496330B2 (en) | 2013-08-02 | 2016-11-15 | Semiconductor Energy Laboratory Co., Ltd. | Oxide semiconductor film and semiconductor device |

| US9299855B2 (en) | 2013-08-09 | 2016-03-29 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device having dual gate insulating layers |

| US9425217B2 (en) | 2013-09-23 | 2016-08-23 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| WO2015097586A1 (en) | 2013-12-25 | 2015-07-02 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| US9817040B2 (en) | 2014-02-21 | 2017-11-14 | Semiconductor Energy Laboratory Co., Ltd. | Measuring method of low off-state current of transistor |

| KR102437450B1 (ko) | 2014-06-13 | 2022-08-30 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치, 및 반도체 장치를 포함하는 전자 기기 |

| US10559667B2 (en) | 2014-08-25 | 2020-02-11 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and method for measuring current of semiconductor device |

| US9647132B2 (en) | 2015-01-30 | 2017-05-09 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and memory device |

-

2016

- 2016-01-15 US US14/996,635 patent/US9633710B2/en active Active

- 2016-01-21 JP JP2016009431A patent/JP2016139452A/ja not_active Withdrawn

-

2017

- 2017-03-06 US US15/450,147 patent/US9972389B2/en not_active Expired - Fee Related

-

2021

- 2021-06-08 JP JP2021095739A patent/JP7179913B2/ja active Active

Patent Citations (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS5954097A (ja) * | 1982-09-22 | 1984-03-28 | Hitachi Ltd | 半導体メモリ装置 |

| US4638460A (en) * | 1982-09-22 | 1987-01-20 | Hitachi, Ltd. | Semiconductor memory device |

| JP2000339977A (ja) * | 1999-05-28 | 2000-12-08 | Nec Corp | データ設定方法および装置、データ記憶装置、情報記憶媒体 |

| US6285592B1 (en) * | 1999-05-28 | 2001-09-04 | Nec Corporation | Data storage device having superior data retention characteristic and method |

| JP2007193862A (ja) * | 2006-01-17 | 2007-08-02 | Toshiba Corp | 不揮発性半導体記憶装置 |

| US20070183208A1 (en) * | 2006-01-17 | 2007-08-09 | Masayuki Tanaka | Nonvolatile semiconductor memory device and data writing method therefor |

| US20110116310A1 (en) * | 2009-11-13 | 2011-05-19 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and driving method thereof |

| JP2011123986A (ja) * | 2009-11-13 | 2011-06-23 | Semiconductor Energy Lab Co Ltd | 半導体装置および半導体装置の駆動方法 |

| JP2011176294A (ja) * | 2010-01-29 | 2011-09-08 | Semiconductor Energy Lab Co Ltd | 半導体記憶装置 |

| US20110286290A1 (en) * | 2010-05-20 | 2011-11-24 | Semiconductor Energy Laboratory Co., Ltd. | Driving method of semiconductor device |

| JP2012003832A (ja) * | 2010-05-20 | 2012-01-05 | Semiconductor Energy Lab Co Ltd | 半導体装置の駆動方法 |

| US20120099368A1 (en) * | 2010-10-20 | 2012-04-26 | Semiconductor Energy Laboratory Co., Ltd. | Method for driving semiconductor device |

| JP2013008431A (ja) * | 2010-10-20 | 2013-01-10 | Semiconductor Energy Lab Co Ltd | 記憶素子の駆動方法及び半導体装置の駆動方法 |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2019130144A1 (ja) * | 2017-12-27 | 2019-07-04 | 株式会社半導体エネルギー研究所 | 記憶装置 |

| US11158371B2 (en) | 2017-12-27 | 2021-10-26 | Semiconductor Energy Laboratory Co., Ltd. | Memory device |

Also Published As

| Publication number | Publication date |

|---|---|

| US20160217830A1 (en) | 2016-07-28 |

| US9633710B2 (en) | 2017-04-25 |

| US20170178728A1 (en) | 2017-06-22 |

| US9972389B2 (en) | 2018-05-15 |

| JP2021166113A (ja) | 2021-10-14 |

| JP7179913B2 (ja) | 2022-11-29 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6010681B2 (ja) | プログラマブルロジックデバイス | |

| US9672873B2 (en) | Semiconductor device | |

| JP6736296B2 (ja) | 半導体装置及び電子機器 | |

| JP7179913B2 (ja) | 半導体装置の動作方法 | |

| JP6397638B2 (ja) | 半導体装置の駆動方法 | |

| JP6405097B2 (ja) | 半導体装置 | |

| JP6833315B2 (ja) | 半導体装置、及び電子機器 | |

| JP6516978B2 (ja) | 半導体装置 | |

| JP6563313B2 (ja) | 半導体装置、及び電子機器 | |

| TW201545316A (zh) | 半導體裝置、電子構件以及電子裝置 | |

| US9779782B2 (en) | Semiconductor device and electronic device | |

| JP6645793B2 (ja) | 半導体装置 | |

| JP7153118B2 (ja) | 半導体装置 | |

| JP6640506B2 (ja) | 半導体装置、電子部品、および電子機器 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20190108 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20190108 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20191119 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20200107 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20200721 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20201208 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20210323 |

|

| A761 | Written withdrawal of application |

Free format text: JAPANESE INTERMEDIATE CODE: A761 Effective date: 20210608 |