JP2015195288A - 半導体装置及び半導体装置の製造方法 - Google Patents

半導体装置及び半導体装置の製造方法 Download PDFInfo

- Publication number

- JP2015195288A JP2015195288A JP2014072821A JP2014072821A JP2015195288A JP 2015195288 A JP2015195288 A JP 2015195288A JP 2014072821 A JP2014072821 A JP 2014072821A JP 2014072821 A JP2014072821 A JP 2014072821A JP 2015195288 A JP2015195288 A JP 2015195288A

- Authority

- JP

- Japan

- Prior art keywords

- insulating film

- field plate

- gate electrode

- mask

- drain electrode

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 163

- 238000004519 manufacturing process Methods 0.000 title claims abstract description 50

- 238000000034 method Methods 0.000 claims abstract description 39

- 238000005530 etching Methods 0.000 claims description 10

- 206010034972 Photosensitivity reaction Diseases 0.000 claims description 8

- 230000036211 photosensitivity Effects 0.000 claims description 8

- 238000000151 deposition Methods 0.000 claims description 7

- 239000007769 metal material Substances 0.000 claims description 6

- 230000001678 irradiating effect Effects 0.000 claims description 5

- 150000004767 nitrides Chemical class 0.000 abstract description 37

- 238000009413 insulation Methods 0.000 abstract 2

- 230000004048 modification Effects 0.000 description 47

- 238000012986 modification Methods 0.000 description 47

- 230000000694 effects Effects 0.000 description 36

- 239000000463 material Substances 0.000 description 22

- 239000000758 substrate Substances 0.000 description 19

- 229910052581 Si3N4 Inorganic materials 0.000 description 11

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 11

- 230000001154 acute effect Effects 0.000 description 10

- 229910052751 metal Inorganic materials 0.000 description 10

- 239000002184 metal Substances 0.000 description 10

- 230000000052 comparative effect Effects 0.000 description 9

- 230000008878 coupling Effects 0.000 description 9

- 238000010168 coupling process Methods 0.000 description 9

- 238000005859 coupling reaction Methods 0.000 description 9

- 239000010931 gold Substances 0.000 description 7

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 6

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 6

- TWNQGVIAIRXVLR-UHFFFAOYSA-N oxo(oxoalumanyloxy)alumane Chemical compound O=[Al]O[Al]=O TWNQGVIAIRXVLR-UHFFFAOYSA-N 0.000 description 6

- 229910052814 silicon oxide Inorganic materials 0.000 description 6

- 239000010936 titanium Substances 0.000 description 6

- 238000005229 chemical vapour deposition Methods 0.000 description 5

- 230000007423 decrease Effects 0.000 description 5

- KRHYYFGTRYWZRS-UHFFFAOYSA-N Fluorane Chemical compound F KRHYYFGTRYWZRS-UHFFFAOYSA-N 0.000 description 4

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 4

- 230000008021 deposition Effects 0.000 description 4

- 230000005684 electric field Effects 0.000 description 4

- BASFCYQUMIYNBI-UHFFFAOYSA-N platinum Chemical compound [Pt] BASFCYQUMIYNBI-UHFFFAOYSA-N 0.000 description 4

- 229910052710 silicon Inorganic materials 0.000 description 4

- 239000010703 silicon Substances 0.000 description 4

- 238000001771 vacuum deposition Methods 0.000 description 4

- 230000015572 biosynthetic process Effects 0.000 description 3

- 229910002704 AlGaN Inorganic materials 0.000 description 2

- 238000000576 coating method Methods 0.000 description 2

- 238000010586 diagram Methods 0.000 description 2

- CPLXHLVBOLITMK-UHFFFAOYSA-N magnesium oxide Inorganic materials [Mg]=O CPLXHLVBOLITMK-UHFFFAOYSA-N 0.000 description 2

- 239000000395 magnesium oxide Substances 0.000 description 2

- AXZKOIWUVFPNLO-UHFFFAOYSA-N magnesium;oxygen(2-) Chemical group [O-2].[Mg+2] AXZKOIWUVFPNLO-UHFFFAOYSA-N 0.000 description 2

- 238000000206 photolithography Methods 0.000 description 2

- LIVNPJMFVYWSIS-UHFFFAOYSA-N silicon monoxide Chemical compound [Si-]#[O+] LIVNPJMFVYWSIS-UHFFFAOYSA-N 0.000 description 2

- 238000000927 vapour-phase epitaxy Methods 0.000 description 2

- PIGFYZPCRLYGLF-UHFFFAOYSA-N Aluminum nitride Chemical compound [Al]#N PIGFYZPCRLYGLF-UHFFFAOYSA-N 0.000 description 1

- 229910052782 aluminium Inorganic materials 0.000 description 1

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 1

- 239000003990 capacitor Substances 0.000 description 1

- 230000015556 catabolic process Effects 0.000 description 1

- 238000004891 communication Methods 0.000 description 1

- 239000013078 crystal Substances 0.000 description 1

- 229910003460 diamond Inorganic materials 0.000 description 1

- 239000010432 diamond Substances 0.000 description 1

- 239000002019 doping agent Substances 0.000 description 1

- 238000001312 dry etching Methods 0.000 description 1

- 238000001704 evaporation Methods 0.000 description 1

- 229910052732 germanium Inorganic materials 0.000 description 1

- GNPVGFCGXDBREM-UHFFFAOYSA-N germanium atom Chemical compound [Ge] GNPVGFCGXDBREM-UHFFFAOYSA-N 0.000 description 1

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 1

- 229910052737 gold Inorganic materials 0.000 description 1

- CJNBYAVZURUTKZ-UHFFFAOYSA-N hafnium(iv) oxide Chemical compound O=[Hf]=O CJNBYAVZURUTKZ-UHFFFAOYSA-N 0.000 description 1

- 229910052759 nickel Inorganic materials 0.000 description 1

- 125000002524 organometallic group Chemical group 0.000 description 1

- 230000003647 oxidation Effects 0.000 description 1

- 238000007254 oxidation reaction Methods 0.000 description 1

- 238000007747 plating Methods 0.000 description 1

- 229910052697 platinum Inorganic materials 0.000 description 1

- 229910052594 sapphire Inorganic materials 0.000 description 1

- 239000010980 sapphire Substances 0.000 description 1

- 230000035945 sensitivity Effects 0.000 description 1

- 238000004544 sputter deposition Methods 0.000 description 1

- 229910052719 titanium Inorganic materials 0.000 description 1

- 150000003608 titanium Chemical class 0.000 description 1

- 230000005533 two-dimensional electron gas Effects 0.000 description 1

- 238000007738 vacuum evaporation Methods 0.000 description 1

- 238000007740 vapor deposition Methods 0.000 description 1

- 238000001039 wet etching Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/76—Making of isolation regions between components

- H01L21/765—Making of isolation regions between components by field effect

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/401—Multistep manufacturing processes

- H01L29/4011—Multistep manufacturing processes for data storage electrodes

- H01L29/40114—Multistep manufacturing processes for data storage electrodes the electrodes comprising a conductor-insulator-conductor-insulator-semiconductor structure

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/402—Field plates

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/778—Field effect transistors with two-dimensional charge carrier gas channel, e.g. HEMT ; with two-dimensional charge-carrier layer formed at a heterojunction interface

- H01L29/7786—Field effect transistors with two-dimensional charge carrier gas channel, e.g. HEMT ; with two-dimensional charge-carrier layer formed at a heterojunction interface with direct single heterostructure, i.e. with wide bandgap layer formed on top of active layer, e.g. direct single heterostructure MIS-like HEMT

- H01L29/7787—Field effect transistors with two-dimensional charge carrier gas channel, e.g. HEMT ; with two-dimensional charge-carrier layer formed at a heterojunction interface with direct single heterostructure, i.e. with wide bandgap layer formed on top of active layer, e.g. direct single heterostructure MIS-like HEMT with wide bandgap charge-carrier supplying layer, e.g. direct single heterostructure MODFET

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/08—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions with semiconductor regions connected to an electrode carrying current to be rectified, amplified or switched and such electrode being part of a semiconductor device which comprises three or more electrodes

- H01L29/0843—Source or drain regions of field-effect devices

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/12—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by the materials of which they are formed

- H01L29/20—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by the materials of which they are formed including, apart from doping materials or other impurities, only AIIIBV compounds

- H01L29/2003—Nitride compounds

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/402—Field plates

- H01L29/404—Multiple field plate structures

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/41—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions

- H01L29/423—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions not carrying the current to be rectified, amplified or switched

- H01L29/42312—Gate electrodes for field effect devices

- H01L29/42316—Gate electrodes for field effect devices for field-effect transistors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/778—Field effect transistors with two-dimensional charge carrier gas channel, e.g. HEMT ; with two-dimensional charge-carrier layer formed at a heterojunction interface

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Ceramic Engineering (AREA)

- Manufacturing & Machinery (AREA)

- Junction Field-Effect Transistors (AREA)

Abstract

Description

最初に本願発明の実施形態の内容を列記して説明する。本願発明の一実施形態は、半導体層上にゲート電極、ソース電極およびドレイン電極を形成する工程と、ゲート電極を覆い、ゲート電極の形状を反映した段差と、段差からドレイン電極までの間に位置する平坦部とを表面に有する絶縁膜を形成する工程と、絶縁膜上にレジストを形成する工程と、絶縁膜の段差の側面がその内側に位置し、ゲート電極の上面端部がその外側に位置する形状を備え、その上面から絶縁膜の段差までの距離が平坦部までの距離よりも近く、その深さ方向に向かって広がるオーバーハング形状を有する窓をレジストに形成する工程と、レジストをマスクとして利用して、絶縁膜上に金属材料を被着させ、段差の側面から平坦部に向けて延在するフィールドプレートを形成する工程と、を備える半導体装置の製造方法である。

以下、添付図面を参照して、本発明の好適な実施形態について詳細に説明する。なお、以下の説明において、同一要素又は同一機能を有する要素には、同一符号を用いることとし、重複する説明は省略する。

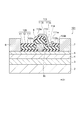

図1は、第1実施形態に係る半導体装置を示す断面図である。図1に示されるように、半導体装置であるトランジスタ1は、基板2、窒化物半導体層(半導体層)3、電子供給層4、キャップ層5、ソース電極6、ドレイン電極7、ゲート電極8、絶縁膜9、及びフィールドプレート10を備えている。トランジスタ1はHEMTである。窒化物半導体層3と電子供給層4との界面に2次元電子ガス(2DEG)が生じることにより、チャネル領域が形成される。

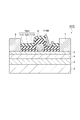

図15は、第2実施形態に係る半導体装置を示す断面図である。図15に示されるように、半導体装置であるトランジスタ101は、基板2、窒化物半導体層3、電子供給層4、キャップ層5、ソース電極6、ドレイン電極7、ゲート電極8、絶縁膜109、及びフィールドプレート110を備えている。

Claims (5)

- 半導体層上にゲート電極、ソース電極およびドレイン電極を形成する工程と、

前記ゲート電極を覆い、前記ゲート電極の形状を反映した段差と、前記段差から前記ドレイン電極までの間に位置する平坦部とを表面に有する絶縁膜を形成する工程と、

前記絶縁膜上にレジストを形成する工程と、

前記段差の側面がその内側に位置し、前記ゲート電極の上面端部がその外側に位置する形状を備え、その上面から前記絶縁膜の前記段差までの距離が前記平坦部までの距離よりも近く、その深さ方向に向かって広がるオーバーハング形状を有する窓を前記レジストに形成する工程と、

前記レジストをマスクとして利用して、前記絶縁膜上に金属材料を被着させ、前記段差の側面から前記平坦部に向けて延在するフィールドプレートを形成する工程と、

を備える半導体装置の製造方法。 - 前記フィールドプレートの前記ソース電極側における端部の膜厚は、前記フィールドプレートの前記ドレイン電極側における端部の膜厚よりも厚い、請求項1に記載の半導体装置の製造方法。

- 前記レジストを形成する工程は、

前記絶縁膜上に第1マスクを形成する工程と、

前記第1マスク上に設けられ、前記第1マスクよりも感光性が低い第2マスクを形成する工程と、

前記第1マスク及び前記第2マスクに光を照射し、前記第1マスクの一部及び前記第2マスクの一部を除去する工程と、

を有する請求項1又は2に記載の半導体装置の製造方法。 - 半導体層上にゲート電極、ソース電極およびドレイン電極を形成する工程と、

前記ゲート電極を覆い、前記ゲート電極の形状を反映した段差と、前記段差から前記ドレイン電極までの間に位置する平坦部とを表面に有する第1の絶縁膜を形成する工程と、

前記第1の絶縁膜の前記段差および前記平坦部を含む表面に前記第1の絶縁膜とエッチングレートの異なる第2の絶縁膜を形成する工程と、

前記第2の絶縁膜の前記平坦部上における領域の膜厚を減じる工程と、

前記第2の絶縁膜上に、前記膜厚が減じられた領域上の部分を含み、前記段差から前記平坦部の領域にかけて延在するフィールドプレートを形成する工程と、

を備える半導体装置の製造方法。 - 半導体層と、

前記半導体層上に設けられるソース電極と、

前記半導体層上に設けられるドレイン電極と、

前記半導体層上に設けられ、前記ソース電極と前記ドレイン電極との間に位置するゲート電極と、

前記ゲート電極を覆い、前記ゲート電極の形状を反映した段差を表面に有する絶縁膜と、

前記絶縁膜上に設けられ、前記段差の側面であって前記ゲート電極と前記ドレイン電極との間の前記側面から前記ドレイン電極に向けて延在するフィールドプレートと、

を備え、

前記フィールドプレートの前記ソース電極側における端部の膜厚は、前記フィールドプレートの前記ドレイン電極側における端部の膜厚よりも大きい半導体装置。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2014072821A JP2015195288A (ja) | 2014-03-31 | 2014-03-31 | 半導体装置及び半導体装置の製造方法 |

| US14/673,039 US9620409B2 (en) | 2014-03-31 | 2015-03-30 | Semiconductor device and method of manufacturing the same |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2014072821A JP2015195288A (ja) | 2014-03-31 | 2014-03-31 | 半導体装置及び半導体装置の製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2015195288A true JP2015195288A (ja) | 2015-11-05 |

| JP2015195288A5 JP2015195288A5 (ja) | 2017-06-01 |

Family

ID=54191422

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2014072821A Pending JP2015195288A (ja) | 2014-03-31 | 2014-03-31 | 半導体装置及び半導体装置の製造方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US9620409B2 (ja) |

| JP (1) | JP2015195288A (ja) |

Cited By (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2019047055A (ja) * | 2017-09-06 | 2019-03-22 | 住友電気工業株式会社 | トランジスタ |

| JP2019067800A (ja) * | 2017-09-28 | 2019-04-25 | 住友電工デバイス・イノベーション株式会社 | 半導体装置の製造方法および半導体装置 |

| JP2019207945A (ja) * | 2018-05-29 | 2019-12-05 | 住友電工デバイス・イノベーション株式会社 | 半導体装置の製造方法 |

| WO2022172588A1 (ja) * | 2021-02-10 | 2022-08-18 | ローム株式会社 | 窒化物半導体装置および窒化物半導体装置の製造方法 |

| WO2023276972A1 (ja) * | 2021-07-01 | 2023-01-05 | ローム株式会社 | 窒化物半導体装置 |

Families Citing this family (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN104332498B (zh) * | 2014-09-01 | 2018-01-05 | 苏州捷芯威半导体有限公司 | 一种斜场板功率器件及斜场板功率器件的制备方法 |

| JP6436531B2 (ja) * | 2015-01-30 | 2018-12-12 | 住友電工デバイス・イノベーション株式会社 | 半導体装置の製造方法 |

| JP6540461B2 (ja) * | 2015-10-30 | 2019-07-10 | 富士通株式会社 | 半導体装置及び半導体装置の製造方法 |

| DE112017000081B4 (de) * | 2016-03-14 | 2022-12-29 | Fuji Electric Co., Ltd. | Halbleitervorrichtung und Herstellungsverfahren |

| US20220376058A1 (en) * | 2020-07-07 | 2022-11-24 | Innoscience (Zhuhai) Technology Co., Ltd. | Semiconductor device and fabrication method thereof |

| US20220037518A1 (en) * | 2020-07-31 | 2022-02-03 | Taiwan Semiconductor Manufacturing Co., Ltd. | Gallium Nitride-Based Device with Step-Wise Field Plate and Method Making the Same |

| US11791389B2 (en) * | 2021-01-08 | 2023-10-17 | Wolfspeed, Inc. | Radio frequency transistor amplifiers having widened and/or asymmetric source/drain regions for improved on-resistance performance |

| US12027616B1 (en) * | 2021-02-03 | 2024-07-02 | Global Communication Semiconductors, Llc | Embedded non-overlapping source field design for improved GaN HEMT microwave performance |

| US20220376060A1 (en) * | 2021-05-20 | 2022-11-24 | Nxp Usa, Inc. | Semiconductor device with conductive element formed over dielectric layers and method of fabrication therefor |

| US20230197829A1 (en) * | 2021-12-20 | 2023-06-22 | Nxp Usa, Inc. | Transistors with source-connected field plates |

| WO2023240491A1 (en) * | 2022-06-15 | 2023-12-21 | Innoscience (suzhou) Semiconductor Co., Ltd. | Nitride-based semiconductor device and method for manufacturing the same |

Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0693426A (ja) * | 1992-09-11 | 1994-04-05 | Hitachi Ltd | 薄膜形成装置 |

| JP2007505483A (ja) * | 2003-09-09 | 2007-03-08 | ザ リージェンツ オブ ザ ユニバーシティ オブ カリフォルニア | シングルゲートまたはマルチゲートフィールドプレート製造 |

| JP2007537593A (ja) * | 2004-05-11 | 2007-12-20 | クリー インコーポレイテッド | ソース接続フィールドプレートを備えるワイドバンドギャップhemt |

| JP2008533717A (ja) * | 2005-03-11 | 2008-08-21 | クリー インコーポレイテッド | ゲート−ソースフィールドプレートを含むワイドバンドギャップトランジスタ |

| JP2008288289A (ja) * | 2007-05-16 | 2008-11-27 | Oki Electric Ind Co Ltd | 電界効果トランジスタとその製造方法 |

| JP2012175018A (ja) * | 2011-02-24 | 2012-09-10 | Fujitsu Ltd | 化合物半導体装置 |

Family Cites Families (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7662698B2 (en) * | 2006-11-07 | 2010-02-16 | Raytheon Company | Transistor having field plate |

| US7800132B2 (en) * | 2007-10-25 | 2010-09-21 | Northrop Grumman Systems Corporation | High electron mobility transistor semiconductor device having field mitigating plate and fabrication method thereof |

| JP5845638B2 (ja) | 2011-06-02 | 2016-01-20 | 住友電気工業株式会社 | 半導体装置 |

-

2014

- 2014-03-31 JP JP2014072821A patent/JP2015195288A/ja active Pending

-

2015

- 2015-03-30 US US14/673,039 patent/US9620409B2/en active Active

Patent Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0693426A (ja) * | 1992-09-11 | 1994-04-05 | Hitachi Ltd | 薄膜形成装置 |

| JP2007505483A (ja) * | 2003-09-09 | 2007-03-08 | ザ リージェンツ オブ ザ ユニバーシティ オブ カリフォルニア | シングルゲートまたはマルチゲートフィールドプレート製造 |

| JP2007537593A (ja) * | 2004-05-11 | 2007-12-20 | クリー インコーポレイテッド | ソース接続フィールドプレートを備えるワイドバンドギャップhemt |

| JP2008533717A (ja) * | 2005-03-11 | 2008-08-21 | クリー インコーポレイテッド | ゲート−ソースフィールドプレートを含むワイドバンドギャップトランジスタ |

| JP2008288289A (ja) * | 2007-05-16 | 2008-11-27 | Oki Electric Ind Co Ltd | 電界効果トランジスタとその製造方法 |

| JP2012175018A (ja) * | 2011-02-24 | 2012-09-10 | Fujitsu Ltd | 化合物半導体装置 |

Cited By (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2019047055A (ja) * | 2017-09-06 | 2019-03-22 | 住友電気工業株式会社 | トランジスタ |

| JP2019067800A (ja) * | 2017-09-28 | 2019-04-25 | 住友電工デバイス・イノベーション株式会社 | 半導体装置の製造方法および半導体装置 |

| JP2019207945A (ja) * | 2018-05-29 | 2019-12-05 | 住友電工デバイス・イノベーション株式会社 | 半導体装置の製造方法 |

| WO2022172588A1 (ja) * | 2021-02-10 | 2022-08-18 | ローム株式会社 | 窒化物半導体装置および窒化物半導体装置の製造方法 |

| WO2023276972A1 (ja) * | 2021-07-01 | 2023-01-05 | ローム株式会社 | 窒化物半導体装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| US20150279722A1 (en) | 2015-10-01 |

| US9620409B2 (en) | 2017-04-11 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP2015195288A (ja) | 半導体装置及び半導体装置の製造方法 | |

| JP5134378B2 (ja) | 電界効果トランジスタ | |

| JP2010515279A (ja) | Iii族窒化物素子のための活性領域成形およびその製造方法 | |

| TW200522170A (en) | Fabrication of single or multiple gate field plates | |

| US10600917B2 (en) | Field effect transistor and manufacturing method thereof | |

| KR102154336B1 (ko) | 고전압 구동용 전계효과 트랜지스터 및 제조 방법 | |

| JP7143660B2 (ja) | 半導体装置 | |

| TWI533452B (zh) | 化合物半導體裝置及其製造方法 | |

| JP2013026442A (ja) | 窒化物半導体装置及びその製造方法 | |

| JP2023040154A (ja) | 半導体装置 | |

| JP5740356B2 (ja) | 半導体装置 | |

| KR20150060417A (ko) | 고주파 소자 및 그 제조 방법 | |

| TWI566402B (zh) | 具有閘極間隔件之增強模式氮化鎵高電子遷移率電晶體元件及其製造方法 | |

| US20110291203A1 (en) | Semiconductor device and method for manufacturing the same | |

| JP2019207945A (ja) | 半導体装置の製造方法 | |

| US20230299128A1 (en) | Lateral field-effect transistor and preparing method | |

| JP2014078561A (ja) | 窒化物半導体ショットキバリアダイオード | |

| CN116313798A (zh) | 氮化镓基器件及其制备方法 | |

| TWI521641B (zh) | 製作氮化鎵裝置及積體電路中之自我對準隔離部的方法 | |

| JP7067336B2 (ja) | 半導体装置の製造方法 | |

| JP2019135745A (ja) | 電界効果トランジスタの製造方法 | |

| KR101598200B1 (ko) | Iii-v족 화합물 반도체 소자 패키지 및 그 제조 방법 | |

| TWI726316B (zh) | 高電子遷移率電晶體裝置及其製造方法 | |

| CN209199936U (zh) | 具有t型栅极的iii-v族半导体装置 | |

| JP5708031B2 (ja) | 縦型電界効果トランジスタとその製造方法及び電子機器 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20170331 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20170412 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20171219 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20171221 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20180619 |