JP2012053788A - 半導体集積回路装置 - Google Patents

半導体集積回路装置 Download PDFInfo

- Publication number

- JP2012053788A JP2012053788A JP2010197146A JP2010197146A JP2012053788A JP 2012053788 A JP2012053788 A JP 2012053788A JP 2010197146 A JP2010197146 A JP 2010197146A JP 2010197146 A JP2010197146 A JP 2010197146A JP 2012053788 A JP2012053788 A JP 2012053788A

- Authority

- JP

- Japan

- Prior art keywords

- circuit

- conductive pattern

- voltage

- detection circuit

- semiconductor integrated

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F21/00—Security arrangements for protecting computers, components thereof, programs or data against unauthorised activity

- G06F21/70—Protecting specific internal or peripheral components, in which the protection of a component leads to protection of the entire computer

- G06F21/86—Secure or tamper-resistant housings

- G06F21/87—Secure or tamper-resistant housings by means of encapsulation, e.g. for integrated circuits

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F21/00—Security arrangements for protecting computers, components thereof, programs or data against unauthorised activity

- G06F21/70—Protecting specific internal or peripheral components, in which the protection of a component leads to protection of the entire computer

- G06F21/86—Secure or tamper-resistant housings

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L9/00—Cryptographic mechanisms or cryptographic arrangements for secret or secure communications; Network security protocols

- H04L9/32—Cryptographic mechanisms or cryptographic arrangements for secret or secure communications; Network security protocols including means for verifying the identity or authority of a user of the system or for message authentication, e.g. authorization, entity authentication, data integrity or data verification, non-repudiation, key authentication or verification of credentials

- H04L9/3234—Cryptographic mechanisms or cryptographic arrangements for secret or secure communications; Network security protocols including means for verifying the identity or authority of a user of the system or for message authentication, e.g. authorization, entity authentication, data integrity or data verification, non-repudiation, key authentication or verification of credentials involving additional secure or trusted devices, e.g. TPM, smartcard, USB or software token

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/02—Details

- H05K1/0275—Security details, e.g. tampering prevention or detection

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/09—Shape and layout

- H05K2201/09209—Shape and layout details of conductors

- H05K2201/09218—Conductive traces

- H05K2201/09263—Meander

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/30—Assembling printed circuits with electric components, e.g. with resistor

- H05K3/32—Assembling printed circuits with electric components, e.g. with resistor electrically connecting electric components or wires to printed circuits

- H05K3/34—Assembling printed circuits with electric components, e.g. with resistor electrically connecting electric components or wires to printed circuits by soldering

- H05K3/341—Surface mounted components

- H05K3/3431—Leadless components

- H05K3/3436—Leadless components having an array of bottom contacts, e.g. pad grid array or ball grid array components

Landscapes

- Engineering & Computer Science (AREA)

- Computer Hardware Design (AREA)

- Computer Security & Cryptography (AREA)

- Theoretical Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Software Systems (AREA)

- Physics & Mathematics (AREA)

- General Engineering & Computer Science (AREA)

- Signal Processing (AREA)

- Computer Networks & Wireless Communication (AREA)

- Semiconductor Integrated Circuits (AREA)

- Storage Device Security (AREA)

- Logic Circuits (AREA)

Abstract

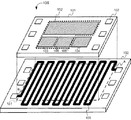

【解決手段】回路ブロックが配置された第1面と、第1面の反対側の第2面とを有する半導体基板と、半導体基板を搭載する実装基板と、実装基板のうち、回路ブロックの保護対象の部分と重なる領域に配置された導電パターンと、導電パターンに改変が加えられたことを検出する検出回路とを有する半導体集積回路装置が提供される。半導体基板の第2面と実装基板とが対向するように、半導体基板が実装基板に搭載されている。

【選択図】図1

Description

Claims (9)

- 回路ブロックが配置された第1面と、前記第1面の反対側の第2面とを有する半導体基板と、

前記半導体基板を搭載する実装基板と、

前記実装基板のうち、前記回路ブロックの保護対象の部分と重なる領域に配置された導電パターンと、

前記導電パターンに改変が加えられたことを検出する検出回路と

を有し、

前記半導体基板の前記第2面と前記実装基板とが対向するように、前記半導体基板が前記実装基板に搭載されている

ことを特徴とする半導体集積回路装置。 - 前記回路ブロックは、

データを保持するためのメモリ回路と、

前記メモリ回路に保持されるデータへのアクセスを制御する制御回路と、

を有し、

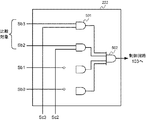

前記制御回路は、前記導電パターンに改変が加えられたことが検出された場合に、前記メモリ回路に保持されているデータをリセットするか、前記メモリ回路に保持されているデータへのアクセスを禁止するかの何れかを行うことを特徴とする請求項1に記載の半導体集積回路装置。 - 前記検出回路は、前記導電パターンの第1部分が電圧源に接続された状態と接続されていない状態とを切り替えるスイッチ回路を有し、

前記導電パターンの第2部分は基準電位ラインに接続され、

前記検出回路は、前記第1部分が前記電圧源に接続された状態から接続されていない状態に変化した場合に、前記第1部分の電圧が変化するか否かを判定し、変化しなかった場合に、前記導電パターンに改変が加えられたことを検出する

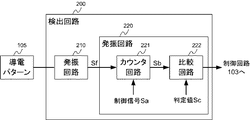

ことを特徴とする請求項1又は2に記載の半導体集積回路装置。 - 前記検出回路は、

前記導電パターンに接続され、前記導電パターンの回路定数により決定される発振周波数で発振する発振回路を有し、

前記発振回路の発振周波数が事前に設定された範囲に含まれるか否かを判定し、前記発振周波数が事前に設定された範囲に含まれない場合に、前記導電パターンに改変が加えられたことを検出する

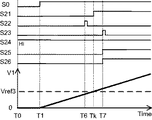

ことを特徴とする請求項1又は2に記載の半導体集積回路装置。 - 前記導電パターンの第1部分の電位を基準電位にリセットするリセット部と、

前記第1部分を電流源に接続する接続部と

を更に有し、

前記検出回路は、前記第1部分の電位を基準電位にリセットした後に前記第1部分を前記電流源に接続してから一定時間経過後の前記第1部分の電圧が事前に設定された範囲に含まれるか否かを判定し、前記一定時間経過後の電圧が前記事前に設定された範囲に含まれない場合に前記導電パターンに改変が加えられたことを検出し、

前記第1部分の電圧の変化は、前記導電パターンの回路定数に依存する

ことを特徴とする請求項1又は2に記載の半導体集積回路装置。 - 前記検出回路は、

前記導電パターンの第1部分を電流源に接続する接続手段と、

前記第1部分を基準電位にリセットするリセット手段と

を有し、

前記検出回路は、前記第1部分を基準電位にリセットした後に前記第1部分に電流を接続してから一定時間経過後の前記第1部分の電圧が事前に設定された範囲に含まれるか否かを判定し、前記一定時間経過後の電圧が前記範囲に含まれない場合に前記導電パターンに改変が加えられたことを検出し、

前記第1部分の電圧の変化は、前記導電パターンの回路定数に依存する

ことを特徴とする請求項1又は2に記載の半導体集積回路装置。 - 前記導電パターンの第2部分が基準電位ラインに接続されることを特徴とする請求項6に記載の半導体集積回路装置。

- 前記第1部分の電位が基準電位にリセットされた後に前記導電パターンがフローティングにされることを特徴とする請求項6に記載の半導体集積回路装置。

- 前記回路定数は、前記導電パターンの寄生抵抗と寄生容量とを含むことを特徴とする請求項4乃至8の何れか1項に記載の半導体集積回路装置。

Priority Applications (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2010197146A JP2012053788A (ja) | 2010-09-02 | 2010-09-02 | 半導体集積回路装置 |

| US13/196,370 US20120056635A1 (en) | 2010-09-02 | 2011-08-02 | Semiconductor integrated circuit device |

| EP11176907A EP2426616A1 (en) | 2010-09-02 | 2011-08-09 | Semiconductor integrated circuit device |

| CN2011102521654A CN102385675A (zh) | 2010-09-02 | 2011-08-30 | 半导体集成电路装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2010197146A JP2012053788A (ja) | 2010-09-02 | 2010-09-02 | 半導体集積回路装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2012053788A true JP2012053788A (ja) | 2012-03-15 |

| JP2012053788A5 JP2012053788A5 (ja) | 2013-10-17 |

Family

ID=44719239

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2010197146A Pending JP2012053788A (ja) | 2010-09-02 | 2010-09-02 | 半導体集積回路装置 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US20120056635A1 (ja) |

| EP (1) | EP2426616A1 (ja) |

| JP (1) | JP2012053788A (ja) |

| CN (1) | CN102385675A (ja) |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2012054476A (ja) * | 2010-09-02 | 2012-03-15 | Canon Inc | 半導体集積回路装置 |

| JP2017120552A (ja) * | 2015-12-28 | 2017-07-06 | 富士通株式会社 | 電子回路、及び外的作用検出用ラッチ回路 |

| JP2019110293A (ja) * | 2017-12-15 | 2019-07-04 | 電子商取引安全技術研究組合 | 半導体装置 |

Families Citing this family (17)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN102638930A (zh) * | 2012-03-13 | 2012-08-15 | 东方通信股份有限公司 | 一种电路板自毁保护罩 |

| GB2504479A (en) * | 2012-07-27 | 2014-02-05 | Johnson Electric Sa | Security wrap comprising conductor pattern to protect electronic device. |

| CN202855734U (zh) * | 2012-10-23 | 2013-04-03 | 北京同方微电子有限公司 | 用于智能卡的有源防护装置 |

| CN103035077A (zh) * | 2012-11-29 | 2013-04-10 | 深圳市新国都技术股份有限公司 | 一种pos机数据信息保护电路 |

| DE102013205729A1 (de) * | 2013-03-28 | 2014-10-02 | Fraunhofer-Gesellschaft zur Förderung der angewandten Forschung e.V. | Vorrichtung und Verfahren mit einem Träger mit Schaltungsstrukturen |

| US9659178B1 (en) | 2013-10-22 | 2017-05-23 | Square, Inc. | Device blanking |

| US9799180B1 (en) * | 2016-01-29 | 2017-10-24 | Square, Inc. | Multiplexed tamper detection system |

| US10475034B2 (en) | 2016-02-12 | 2019-11-12 | Square, Inc. | Physical and logical detections for fraud and tampering |

| CN108701193B (zh) * | 2016-02-12 | 2022-08-30 | 汉阳大学校产学协力团 | 安全半导体芯片及其工作方法 |

| US9892218B2 (en) * | 2016-04-01 | 2018-02-13 | Synopsys, Inc. | Parasitic-aware blockage |

| US10255603B1 (en) | 2017-08-31 | 2019-04-09 | Sqaure, Inc. | Processor power supply glitch mitigation |

| CN111095534B (zh) * | 2017-09-15 | 2024-07-02 | 密码研究公司 | 背面网格连接的封装技术 |

| IL258371A (en) | 2018-03-26 | 2018-05-31 | Kazuar Advanced Tech Ltd | A method and system for preventing physical damage to a computer |

| US11257072B1 (en) | 2018-03-29 | 2022-02-22 | Square, Inc. | Detecting unauthorized devices |

| US11182794B1 (en) | 2018-03-29 | 2021-11-23 | Square, Inc. | Detecting unauthorized devices using proximity sensor(s) |

| US10733291B1 (en) | 2018-06-11 | 2020-08-04 | Square, Inc. | Bi-directional communication protocol based device security |

| CN113358921B (zh) * | 2021-06-03 | 2023-12-29 | 厦门为力电子有限公司 | 开关电源的电流取样电路、及其电流检测电路 |

Citations (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH08115267A (ja) * | 1994-10-19 | 1996-05-07 | Tech Res & Dev Inst Of Japan Def Agency | 情報秘匿機構 |

| DE19705518A1 (de) * | 1997-02-13 | 1998-08-27 | Siemens Ag | Manipulationsgeschütztes elektrisches Gerät |

| JPH10320293A (ja) * | 1997-05-19 | 1998-12-04 | Rohm Co Ltd | Icカードおよびicチップモジュール |

| JPH11272829A (ja) * | 1998-03-19 | 1999-10-08 | Hitachi Ltd | 電子マネーカード |

| EP1126358A1 (fr) * | 2000-02-15 | 2001-08-22 | Ascom Monetel S.A. | Dispositif anti-intrusion |

| JP2003256793A (ja) * | 2002-02-05 | 2003-09-12 | Samsung Electronics Co Ltd | 保安機能を有する半導体集積回路 |

| EP1462907A1 (en) * | 2003-03-25 | 2004-09-29 | Bourns, Inc. | A security enclosure for a circuit |

| JP2005136391A (ja) * | 2003-10-09 | 2005-05-26 | Matsushita Electric Ind Co Ltd | 回路基板、回路基板の設計支援装置及び方法、設計支援プログラム、及び設計支援プログラム記録媒体 |

| JP2006012159A (ja) * | 2001-08-07 | 2006-01-12 | Renesas Technology Corp | 半導体装置およびicカード |

| JP2008293144A (ja) * | 2007-05-23 | 2008-12-04 | Panasonic Corp | 半導体集積回路及びicカード |

| JP2009193119A (ja) * | 2008-02-12 | 2009-08-27 | Topre Corp | データの安全ケース |

Family Cites Families (17)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4593384A (en) * | 1984-12-21 | 1986-06-03 | Ncr Corporation | Security device for the secure storage of sensitive data |

| KR940009250B1 (ko) * | 1991-12-18 | 1994-10-01 | 삼성전자 주식회사 | 복수개의 동작전압에 대응하는 리프레쉬 타이머 |

| US5233505A (en) * | 1991-12-30 | 1993-08-03 | Yeng-Ming Chang | Security device for protecting electronically-stored data |

| JPH07200414A (ja) | 1993-12-28 | 1995-08-04 | Nippon Steel Corp | 記憶内容の解読防止方法及び記憶内容の解読防止用基板 |

| AU2001253818A1 (en) * | 2000-02-14 | 2001-08-20 | Christina Alvarez | Security module system, apparatus and process |

| US20040212017A1 (en) * | 2001-08-07 | 2004-10-28 | Hirotaka Mizuno | Semiconductor device and ic card |

| JP2003288573A (ja) * | 2002-03-27 | 2003-10-10 | Seiko Epson Corp | Icカード及びその製造方法 |

| US6853093B2 (en) * | 2002-12-20 | 2005-02-08 | Lipman Electronic Engineering Ltd. | Anti-tampering enclosure for electronic circuitry |

| JP4510370B2 (ja) * | 2002-12-25 | 2010-07-21 | パナソニック株式会社 | 半導体集積回路装置 |

| US7069525B2 (en) * | 2003-07-18 | 2006-06-27 | International Business Machines Corporation | Method and apparatus for determining characteristics of MOS devices |

| JP4748929B2 (ja) * | 2003-08-28 | 2011-08-17 | パナソニック株式会社 | 保護回路および半導体装置 |

| US7180008B2 (en) * | 2004-01-23 | 2007-02-20 | Pitney Bowes Inc. | Tamper barrier for electronic device |

| US7489204B2 (en) * | 2005-06-30 | 2009-02-10 | International Business Machines Corporation | Method and structure for chip-level testing of wire delay independent of silicon delay |

| US9747472B2 (en) * | 2007-09-13 | 2017-08-29 | Avago Technologies General Ip (Singapore) Pte. Ltd. | Mesh grid protection |

| US7812428B2 (en) * | 2007-12-05 | 2010-10-12 | Atmel Rousset S.A.S. | Secure connector grid array package |

| US7952478B2 (en) * | 2008-07-29 | 2011-05-31 | International Business Machines Corporation | Capacitance-based microchip exploitation detection |

| CN101526802A (zh) * | 2009-04-21 | 2009-09-09 | 上海杉德金卡信息系统科技有限公司 | 一种用于pin输入设备的信息保护方法 |

-

2010

- 2010-09-02 JP JP2010197146A patent/JP2012053788A/ja active Pending

-

2011

- 2011-08-02 US US13/196,370 patent/US20120056635A1/en not_active Abandoned

- 2011-08-09 EP EP11176907A patent/EP2426616A1/en not_active Withdrawn

- 2011-08-30 CN CN2011102521654A patent/CN102385675A/zh active Pending

Patent Citations (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH08115267A (ja) * | 1994-10-19 | 1996-05-07 | Tech Res & Dev Inst Of Japan Def Agency | 情報秘匿機構 |

| DE19705518A1 (de) * | 1997-02-13 | 1998-08-27 | Siemens Ag | Manipulationsgeschütztes elektrisches Gerät |

| JPH10320293A (ja) * | 1997-05-19 | 1998-12-04 | Rohm Co Ltd | Icカードおよびicチップモジュール |

| JPH11272829A (ja) * | 1998-03-19 | 1999-10-08 | Hitachi Ltd | 電子マネーカード |

| EP1126358A1 (fr) * | 2000-02-15 | 2001-08-22 | Ascom Monetel S.A. | Dispositif anti-intrusion |

| JP2006012159A (ja) * | 2001-08-07 | 2006-01-12 | Renesas Technology Corp | 半導体装置およびicカード |

| JP2003256793A (ja) * | 2002-02-05 | 2003-09-12 | Samsung Electronics Co Ltd | 保安機能を有する半導体集積回路 |

| EP1462907A1 (en) * | 2003-03-25 | 2004-09-29 | Bourns, Inc. | A security enclosure for a circuit |

| JP2005136391A (ja) * | 2003-10-09 | 2005-05-26 | Matsushita Electric Ind Co Ltd | 回路基板、回路基板の設計支援装置及び方法、設計支援プログラム、及び設計支援プログラム記録媒体 |

| JP2008293144A (ja) * | 2007-05-23 | 2008-12-04 | Panasonic Corp | 半導体集積回路及びicカード |

| JP2009193119A (ja) * | 2008-02-12 | 2009-08-27 | Topre Corp | データの安全ケース |

Cited By (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2012054476A (ja) * | 2010-09-02 | 2012-03-15 | Canon Inc | 半導体集積回路装置 |

| JP2017120552A (ja) * | 2015-12-28 | 2017-07-06 | 富士通株式会社 | 電子回路、及び外的作用検出用ラッチ回路 |

| JP2019110293A (ja) * | 2017-12-15 | 2019-07-04 | 電子商取引安全技術研究組合 | 半導体装置 |

| JP7290846B2 (ja) | 2017-12-15 | 2023-06-14 | 株式会社Scu | 半導体装置 |

| JP7495551B2 (ja) | 2017-12-15 | 2024-06-04 | 株式会社Scu | 半導体装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| EP2426616A1 (en) | 2012-03-07 |

| CN102385675A (zh) | 2012-03-21 |

| US20120056635A1 (en) | 2012-03-08 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP2012053788A (ja) | 半導体集積回路装置 | |

| JP2012074674A (ja) | 半導体集積回路装置 | |

| US7859421B2 (en) | Circuit and method for detecting a voltage change | |

| KR101068432B1 (ko) | 지연 회로 | |

| JP2007024865A (ja) | 半導体装置 | |

| JP2009037456A (ja) | マイクロコントローラおよびその制御方法 | |

| JP2006197564A (ja) | 信号選択回路およびリアルタイムクロック装置 | |

| JP2010147938A (ja) | 半導体装置、及び動作モ−ド切換方法 | |

| JP4859440B2 (ja) | 半導体記憶装置 | |

| CN107645288A (zh) | 用于产生脉冲的电子电路、方法及电子装置 | |

| JP5761947B2 (ja) | 半導体集積回路装置 | |

| US10326434B2 (en) | Voltage comparator arrangement, electronic component, chip card, embedded secure element | |

| JP6585977B2 (ja) | 半導体装置および発振回路の制御方法 | |

| JP2009232304A (ja) | 水晶発振器 | |

| US6340919B1 (en) | Random number generating circuit | |

| US20220276303A1 (en) | A hardware component and a method for implementing a camouflage of current traces generated by a digital system | |

| JP2007122560A (ja) | 乱数生成回路 | |

| JP5156268B2 (ja) | トリミング電圧発生回路 | |

| TWI779862B (zh) | 偵測電路、電子電路以及偵測方法 | |

| JP5314577B2 (ja) | 半導体集積回路 | |

| JP7459704B2 (ja) | 回路装置及びリアルタイムクロック装置 | |

| CN113366324B (zh) | 检测器 | |

| JP2007271473A (ja) | ジッタ測定回路 | |

| JP6700014B2 (ja) | 半導体装置および周波数安定フラグの生成方法 | |

| JP4277645B2 (ja) | 発振開始検出回路及びそれを内蔵した半導体集積回路 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130902 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20130902 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20140326 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20140414 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140613 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20140704 |