実施の形態1

以下、図面を参照して本発明の実施の形態について説明する。以下では、アナログデジタル変換回路の一例として、入力信号(アナログ値を有するアナログ入力信号AIN)を差動信号として増幅し、その差動信号をコンパレータに与える形態のアナログデジタル変換回路について説明する。しかし、本発明はコンパレータにどのような信号の形態によりコンパレータにアナログ値を与えるかについて特に制限するものではない。また、以下の説明において入力オフセット電圧は、プリアンプ又はコンパレータが出力信号を反転させる実際の閾値と、その閾値の理想値との差の電圧値であるものとする。

本実施の形態にかかるアナログデジタル変換回路1のブロック図を図1に示す。図1に示すように、アナログデジタル変換回路1は、基準電圧生成回路10、プリアンプ群、平滑回路20、補間回路30、コンパレータ群、エンコーダ40、プリアンプキャリブレーション回路CALA0、CALA4、コンパレータキャリブレーション回路CAL30〜CAL34を有する。

基準電圧生成回路10は、複数の抵抗RAを有する。複数の抵抗RAは、高電位側基準電圧VRTと低電位側基準電圧VRBとの間に直列に接続される。そして、抵抗RAが互いに接続されるノードに発生する電圧を基準電圧VR0、VR4として出力する。

プリアンプ群は、複数のプリアンプ(例えば、第1のプリアンプと第2のプリアンプ)を有する。本実施の形態では、第1のプリアンプは、前段プリアンプPA0と後段プリアンプPB0とを有する。また、第2のプリアンプは、前段プリアンプPA4と後段プリアンプPB4とを有する。

前段プリアンプPA0は、正転入力端子にアナログ入力信号AINが入力され、反転入力端子に第1のプリアンプに対応して生成される基準電圧VR0が入力される。そして、前段プリアンプPA0は、アナログ入力信号AINの電圧値と基準電圧VR0との電圧差を増幅して差動信号として出力する。また、前段プリアンプPA0には、第1のプリアンプキャリブレーション回路(例えば、プリアンプキャリブレーション回路CALA0)が接続される。このプリアンプキャリブレーション回路CALA0は、前段プリアンプPA0の入力オフセット電圧をキャリブレーション設定値に基づき調節する。後段プリアンプPB0は、前段プリアンプPA0が出力した差動信号をさらに増幅して第1の出力信号(差動信号)として出力する。

前段プリアンプPA4は、正転入力端子にアナログ入力信号AINが入力され、反転入力端子に第2のプリアンプに対応して生成される基準電圧VR4が入力される。そして、前段プリアンプPA4は、アナログ入力信号AINの電圧値と基準電圧VR4との電圧差を増幅して差動信号として出力する。また、前段プリアンプPA4には、第2のプリアンプキャリブレーション回路(例えば、プリアンプキャリブレーション回路CALA4)が接続される。このプリアンプキャリブレーション回路CALA4は、前段プリアンプPA4の入力オフセット電圧をキャリブレーション設定値に基づき調節する。後段プリアンプPB4は、前段プリアンプPA4が出力した差動信号をさらに増幅して第2の出力信号(差動信号)として出力する。

平滑回路20は、前段プリアンプPA0の出力ノードと前段プリアンプPA4の出力ノードとの間に接続される。そして、平滑回路20は、前段プリアンプPA0の出力ノードの電圧と前段プリアンプPA4の出力ノードの電圧とを平滑化する。より具体的には、平滑回路20は、複数の抵抗を有する。そして、平滑回路20は、前段プリアンプPA0の正転出力端子に接続される出力ノードと、前段プリアンプPA4の正転出力端子に接続される出力ノードと、を抵抗により接続する。また、平滑回路20は、前段プリアンプPA0の反転出力端子に接続される出力ノードと、前段プリアンプPA4の反転出力端子に接続される出力ノードと、を抵抗により接続する。

補間回路30は、後段プリアンプPB0の出力ノードと後段プリアンプPB4の出力ノードとの間に接続される。そして、補間回路30は、後段プリアンプPB0が出力する第1の出力信号の電圧と後段プリアンプPB4が出力する第2の出力信号の電圧との間を補間する補間信号(本実施の形態では、補間信号は複数生成される)を生成する。より具体的には、補間回路30は、複数の抵抗RCを有する。そして、補間回路30は、後段プリアンプPB0の正転出力端子に接続される出力ノードと、後段プリアンプPB4の正転出力端子に接続される出力ノードと、を直列に接続された複数の抵抗RCにより接続する。そして、抵抗RCが互いに接続されるノードから補間信号を出力する。また、補間回路30は、後段プリアンプPB0の反転出力端子に接続される出力ノードと、後段プリアンプPB4の反転出力端子に接続される出力ノードと、を直列に接続された複数の抵抗RCにより接続する。そして、抵抗RCが互いに接続されるノードから補間信号を出力する。なお、以下の説明では抵抗RCはすべて同一の抵抗値を有しているものとする。

コンパレータCMP0〜CMP4は、それぞれ第1の出力信号、第2の出力信号又は補間信号のいずれか1つが入力され、それぞれの入力信号(差動信号)の電圧差に応じてデジタル値を出力する。また、コンパレータCMP0〜CMP4には、それぞれコンパレータキャリブレーション回路CAL30〜CAL34が接続される。コンパレータキャリブレーション回路CAL30〜CAL34は、キャリブレーション設定値に応じて、対応するコンパレータの入力オフセットを調節する。

エンコーダ40は、コンパレータCMP0〜CMP4が出力するデジタル値が入力される。そして、エンコーダ40は、入力されたデジタル値をエンコードしてADC出力信号を出力する。

ここで、上記において説明したプリアンプキャリブレーション回路を有する前段プリアンプPAについて詳細に説明する。なお、以下の説明において、前段プリアンプを総称する符号としてPA、前段プリアンプに対応するプリアンプキャリブレーション回路の総称としてCALA、後段プリアンプを総称する符号としてPBを場合に応じて適宜用いる。

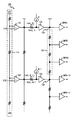

実施の形態1にかかる前段プリアンプ及びプリアンプキャリブレーション回路の回路図を図2に示す。図2に示すように、前段プリアンプPAは、NMOSトランジスタN1〜N3、負荷抵抗RLを有する。NMOSトランジスタN1は、ゲートにバイアス電圧BIASが与えられ定電流源として機能する。NMOSトランジスタN2、N3は、ソース端子が共通接続され、当該共通接続点に定電流源からの電流供給を受ける差動対を構成する。NMOSトランジスタN2のゲートは、前段プリアンプPAの正転入力端子である。また、NMOSトランジスタN3のゲートは、前段プリアンプPAの反転入力端子である。NMOSトランジスタN2のドレインと電源端子との間には負荷抵抗RLが接続される。そして、NMOSトランジスタN2のドレインと負荷抵抗RLとの間の接続点が反転出力端子となる。また、NMOSトランジスタN3のドレインと負荷抵抗RLとの間の接続点が正転出力端子となる。

また、図2に示すように、プリアンプキャリブレーション回路CALAは、NMOSトランジスタN2と並列に接続される可変電流源と、NMOSトランジスタN3と並列に接続される可変電流源とを有する。プリアンプキャリブレーション回路CALAは、可変電流源が出力する電流の値によって負荷抵抗RLに流れる電流を調節することで前段プリアンプPAのオフセットをキャンセルする。つまり、プリアンプキャリブレーション回路CALAは、キャリブレーション設定値に基づき出力する電流の値が調節されるものである。

次いで、図3にコンパレータ及びコンパレータキャリブレーション回路の回路図を示す。なお、以下の説明において、コンパレータを総称する符号としてCMP、コンパレータに対応するコンパレータキャリブレーション回路としてCALを場合に応じて適宜用いる。

図3に示すように、コンパレータCMPは、NMOSトランジスタN4〜N8、PMOSトランジスタP1〜P6を有する。NMOSトランジスタN4は、ゲートにバイアス電圧BIASが与えられ定電流源として機能する。NMOSトランジスタN5、N6は、ソース端子が共通接続され、当該共通接続点に定電流源からの電流供給を受ける差動対を構成する。NMOSトランジスタN5のゲートは、コンパレータCMPの正転入力端子である。また、NMOSトランジスタN6のゲートは、コンパレータCMPの反転入力端子である。NMOSトランジスタN7、N8及びPMOSトランジスタP1、P4は、ラッチ回路を構成する。そして、コンパレータCMPは、このラッチ回路によりNMOSトランジスタN5、N6により構成される差動対の出力をラッチして出力する。なお、ラッチ回路は2つの反転出力端子VOUTN及び正転出力端子VOUTPを有する。

PMOSトランジスタP2は、反転出力端子VOUTNと電源端子との間に接続され、ラッチ制御信号LTCHに基づき反転出力端子VOUTNの状態を決定する。PMOSトランジスタP5は、正転出力端子VOUTPと電源端子との間に接続され、ラッチ制御信号LTCHに基づき正転出力端子VOUTPの状態を決定する。PMOSトランジスタP3はNMOSトランジスタN5のドレインと電源端子との間に接続され、ラッチ制御信号LTCHに基づきNMOSトランジスタN5のドレインの電圧を決定する。PMOSトランジスタP6はNMOSトランジスタN6のドレインと電源端子との間に接続され、ラッチ制御信号LTCHに基づきNMOSトランジスタN6のドレインの電圧を決定する。ラッチ制御信号LTCHは、コンパレータCMPが比較動作を行うタイミングを制御する信号であり、図示しない制御回路から入力される。例えば、このラッチ制御信号LTCHがロウレベルのときはコンパレータCMPが動作を停止し、ハイレベルのときはコンパレータが比較動作を行う。

また、図3に示すように、コンパレータキャリブレーション回路CALは、NMOSトランジスタN5と並列に接続される可変電流源と、NMOSトランジスタN6と並列に接続される可変電流源とを有する。コンパレータキャリブレーション回路CALは、可変電流源が出力する電流の値によってラッチ回路に流れる電流を調節することでコンパレータPAのオフセットをキャンセルする。つまり、コンパレータキャリブレーション回路CALは、キャリブレーション設定値に基づき出力する電流の値が調節されるものである。

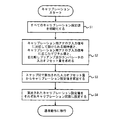

アナログデジタル変換回路1では、キャリブレーション設定値を通常動作を開始する前のキャリブレーション期間において算出する。そして、算出されたキャリブレーション設定値をプリアンプキャリブレーション回路CALA0、CALA4及びコンパレータキャリブレーション回路CAL30〜CAL34に与えることで、プリアンプ及びコンパレータで生じる入力オフセットをキャンセルする。そこで、アナログデジタル変換回路1におけるキャリブレーション設定値の設定手順を示すフローチャートを図4に示す。

図4に示すように、アナログデジタル変換回路1では、キャリブレーション動作が開始されると、まず、プリアンプキャリブレーション回路CALA0、CALA4及びコンパレータキャリブレーション回路CAL30〜CAL34のキャリブレーション設定値を初期化する(ステップS1)。続いて、キャリブレーション用アナログ入力信号AINを入力し、キャリブレーション用アナログ入力信号AINに応じたデジタル値を各コンパレータから得る。そして、コンパレータから得られたデジタル値とキャリブレーション用アナログ入力信号AINに対応して予め設けられた期待値とを比較しプリアンプ及びコンパレータの入力オフセット量を算出する(ステップS2)。

そして、ステップS2で得られた入力オフセット量から各キャリブレーション回路に与えるキャリブレーション設定値を算出する(ステップS3)。その後、算出されたキャリブレーション設定値をそれぞれプリアンプキャリブレーション回路及びコンパレータキャリブレーション回路に設定する(ステップS4)。これにより、アナログデジタル変換回路1のプリアンプ及びコンパレータの入力オフセットをキャンセルできる構成が整うため、その後、アナログデジタル変換回路1を通常動作モードにて動作させる。

ここで、ステップS3におけるキャリブレーション設定値の算出方法について説明する。まず、コンパレータCMP0〜CMP4の遷移に対応するアナログデジタル変換回路の入力換算オフセットは、(1)〜(5)式により表される。なお、(1)〜(5)式では、コンパレータCMP0の遷移に対応するアナログデジタル変換回路の入力換算オフセットをInOff30、コンパレータCMP1の遷移に対応するアナログデジタル変換回路の入力換算オフセットをInOff31、コンパレータCMP2の遷移に対応するアナログデジタル変換回路の入力換算オフセットをInOff32、コンパレータCMP3の遷移に対応するアナログデジタル変換回路の入力換算オフセットをInOff33、コンパレータCMP4の遷移に対応するアナログデジタル変換回路の入力換算オフセットをInOff34で表した。

また、(1)〜(5)式では、前段プリアンプPA0の入力換算オフセットをOffA0、後段プリアンプPB0の入力換算オフセットをOffB0、前段プリアンプPA4の入力換算オフセットをOffA4、後段プリアンプPB4の入力換算オフセットをOffB4、コンパレータCMP0の入力換算オフセットをOff30、コンパレータCMP1の入力換算オフセットをOff31、コンパレータCMP2の入力換算オフセットをOff32、コンパレータCMP3の入力換算オフセットをOff33、コンパレータCMP4の入力換算オフセットをOff34、プリアンプキャリブレーション回路CALA0のキャリブレーション設定値をCALA0、プリアンプキャリブレーション回路CALA4のキャリブレーション設定値をCALA4、コンパレータキャリブレーション回路CAL30のキャリブレーション設定値をCAL30、コンパレータキャリブレーション回路CAL31のキャリブレーション設定値をCAL31、コンパレータキャリブレーション回路CAL32のキャリブレーション設定値をCAL32、コンパレータキャリブレーション回路CAL33のキャリブレーション設定値をCAL33、コンパレータキャリブレーション回路CAL34のキャリブレーション設定値をCAL34、前段プリアンプPA0、PA4の増幅率をA1、後段プリアンプPB0、PB4の増幅率をA2として表した。

ここで、本実施の形態では、第1のプリアンプから第1の出力信号が入力されるコンパレータCMP0に対応して設けられるコンパレータキャリブレーション回路CAL30のキャリブレーション設定値CAL30を0とする。また、第2のプリアンプから第2の出力信号が入力されるコンパレータCMP4に対応して設けられるコンパレータキャリブレーション回路CAL34のキャリブレーション設定値CAL34を0とする。そして、すべてのコンパレータの遷移に対応するアナログデジタル変換回路の入力換算オフセットを0として(1)〜(5)式の解を求めると、キャリブレーション設定値CALA0、CALA4、CAL31〜CAL33は、(6)〜(10)

式により求めることができる。

つまり、キャリブレーション設定値CAL30、CAL34を0とし、さらにその他のキャリブレーション設定値を(6)〜(10)式とすることで、アナログデジタル変換回路1のデジタル値にはプリアンプ及びコンパレータの入力オフセットの影響を受けることはない。従って、このような設定により、アナログデジタル変換回路1は、アナログ入力信号AINとデジタル値との線形特性を良好に維持することができる。

上記説明より、本実施の形態にかかるアナログデジタル変換回路1では、コンパレータにアナログ入力信号を増幅して伝達するプリアンプに対してプリアンプキャリブレーション回路CALA0、CALA4を設ける。これにより、第1の出力信号(アナログ入力信号)を受けるコンパレータCMP0と第2の出力信号(アナログ入力信号)を受けるコンパレータCMP4とが出力するデジタル値に対する入力オフセットの影響がキャンセルされ、デジタル値の線形性が改善される。なお、プリアンプキャリブレーション回路CALA0、CALA4に対して設定されるキャリブレーション設定値には、前段プリアンプ、後段プリアンプ及びコンパレータの入力オフセットをキャンセルするための値が含まれる。

また、補間回路30を介して補間信号(アナログ入力信号)を受けるコンパレータCMP1〜CMP3に対してコンパレータキャリブレーション回路CAL31、CAL32、CAL33を設ける。これにより、補間信号を受けるコンパレータCMP1〜CMP3が出力するデジタル値に対する入力オフセットの影響がキャンセルされ、デジタル値の線形性が改善される。

つまり、本実施の形態にかかるアナログデジタル変換回路1では、プリアンプとコンパレータの両方に入力オフセットをキャンセルするためのキャリブレーション回路を設けることで、補間回路30を介してアナログ入力信号を受けるコンパレータを含むすべてのコンパレータから出力されるデジタル値の線形性が改善される。

ここで、本実施の形態にかかるアナログデジタル変換回路1におけるデジタル値の線形性改善の効果をさらに説明する。そこで、上記アナログデジタル変換回路1においてプリアンプキャリブレーション回路CALA0、CALA4を用いない場合の問題を以下で説明する。まず、プリアンプキャリブレーション回路CALA0、CALA4を用いない場合のコンパレータCMP0〜CMP4の遷移に対応するアナログデジタル変換回路の入力換算オフセットInOff30〜InOff34は、(11)〜(15)式により表される。

そして、入力換算オフセットInOff30〜InOff34を0として、(11)〜(15)式の解を求めると、キャリブレーション設定値CAL31〜CAL34は、(16)〜(20)式で表される。

つまり、(16)〜(20)式より、アナログデジタル変換回路1では、コンパレータキャリブレーション回路CAL30〜CAL34のみでコンパレータから出力されるデジタル値の線形性を改善することも可能であることがわかる。しかし、(16)〜(20)式を参照すると、キャリブレーション設定値CAL30〜CAL34には、前段プリアンプの増幅率A1と後段プリアンプの増幅率A2とを被乗算値として有する項が存在する。一般的に、増幅率A1、A2は大きな値であり、このような大きな値を被乗算値と有するキャリブレーション設定値CAL30〜CAL34の値は非常に大きくなる可能性が高い。また、アナログデジタル変換回路は、所定の電源電圧範囲にて動作する。そのため、キャリブレーション設定値として電源電圧範囲よりも大きな値が算出された場合、アナログデジタル変換回路1の入力オフセットを十分にキャンセルできなくなる問題がある。つまり、コンパレータの入力オフセットを調節するのみではアナログデジタル変換回路の出力結果の線形性は十分に改善されないおそれがある。

これに対して、本実施の形態にかかるアナログデジタル変換回路1では、コンパレータに対する入力オフセットの調整に加え、プリアンプに対する入力オフセットの調整を行う。これにより、上記(6)〜(10)式に示すキャリブレーション設定値が得られる。(6)〜(10)式を参照すると、各キャリブレーション設定値には、被乗算値として増幅率A1、A2を含んでいない。(6)〜(10)式では増幅率A1、A2は、除算値として含まれるのみである。つまり、本実施の形態にかかるアナログデジタル変換回路1では、キャリブレーション設定値を(16)〜(20)式で示されるキャリブレーション設定値よりも低くすることができ、入力オフセットの調整値として現実的なキャリブレーション設定値を得ることができる。

さらに、本実施の形態にかかるアナログデジタル変換回路1では、プリアンプ及びコンパレータに与えるキャリブレーション設定値が各素子に対して個別の値となる。そのため、本実施の形態にかかるアナログデジタル変換回路1では、プリアンプ及びコンパレータを含む各素子がそれぞれ別個のばらつき量の入力オフセットを有していても、それぞれの影響をキャンセルすることができる。

なお、本実施の形態にかかるアナログデジタル変換回路1においては第1、第2のプリアンプを2段のプリアンプとして構成したが、1つのプリアンプにより十分な増幅率が得られる場合は、1段の回路により第1、第2のプリアンプを構成することが可能である。そこで、アナログデジタル変換回路1の変形例となるアナログデジタル変換回路1aのブロック図を図5に示す。図5に示すように、アナログデジタル変換回路1aは、前段プリアンプPA0、PA4のみで第1、第2のプリアンプを構成する。また、この変形例では、平滑回路20を削除することができる。これにより、アナログデジタル変換回路1aは、アナログデジタル変換回路1よりも回路規模を小さくすることができる。

実施の形態2

実施の形態2にかかるアナログデジタル変換回路2のブロック図を図6に示す。図6に示すようにアナログデジタル変換回路2は、実施の形態1にかかるアナログデジタル変換回路1にスイッチ回路SWBを追加したものである。スイッチ回路SWBは、第1、第2のプリアンプの出力(例えば、後段プリアンプPBの出力)の間に設けられる。そして、スイッチ回路SWBは、後段プリアンプPBの出力の間の接続状態を他の回路から与えられるリセット信号RSTBに応じて切り替える。

このスイッチ回路SWBは、アナログデジタル変換回路2のキャリブレーション期間において短絡状態となる。これにより、キャリブレーション期間にコンパレータCMP0〜CMP4に与えられるアナログ入力信号の値がゼロとなるコンパレータ用キャリブレーション期間が生じる。実施の形態2では、このコンパレータ用キャリブレーション期間においてコンパレータCMP0〜CMP4のキャリブレーションを行う。そして、コンパレータ用キャリブレーション期間が終了した後にプリアンプのキャリブレーションを行う。

このキャリブレーション期間におけるアナログデジタル変換回路2の動作につて説明する。コンパレータCMP0〜CMP4は、キャリブレーション期間においてアナログ入力信号の値がゼロとして、この期間にコンパレータCMP0〜CMP4のキャリブレーション設定値を算出する。より具体的には、キャリブレーション設定値CAL30=コンパレータCMP0の入力オフセットOff30、キャリブレーション設定値CAL31=コンパレータCMP1の入力オフセットOff31、キャリブレーション設定値CAL32=コンパレータCMP2の入力オフセットOff32、キャリブレーション設定値CAL33=コンパレータCMP3の入力オフセットOff33、キャリブレーション設定値CAL34=コンパレータCMP4の入力オフセットOff34とする。

このようなキャリブレーション設定値とすることで、コンパレータ用キャリブレーション期間におけるコンパレータCMP0〜CMP4が出力するデジタル値は0と1との間をトグルする状態となる。

また、コンパレータ用キャリブレーション期間が完了した後に、プリアンプキャリブレーション回路CALA0、CALA4に対するキャリブレーション設定値を決定する。このとき、すでにコンパレータの入力オフセットがキャンセルされる設定が完了している。そのため、キャリブレーション設定値CALA0、CALA4を(21)、(22)式より与えることで、アナログデジタル変換回路2の全体の入力オフセットをキャンセルすることができる。

上記説明より、アナログデジタル変換回路2では、第1、第2のプリアンプの出力にスイッチ回路SWBを設けることでキャリブレーション設定値の算出を簡単にすることが可能である。

実施の形態3

実施の形態3にかかるアナログデジタル変換回路3のブロック図を図7に示す。図7に示すように、アナログデジタル変換回路3では、第1、第2のプリアンプとしてフォールディング形式の接続を有するプリアンプを用いる。フォールディング形式のプリアンプ(以下、フォールディングアンプと称す。)では、複数のプリアンプ(本実施の形態では3つ)の出力を互いに接続して1つの出力信号を生成する。なお、アナログデジタル変換回路3では、プリアンプの増加に伴い平滑回路20の抵抗の数を増加させている。また、実施の形態3にかかるアナログデジタル変換回路3では、前段プリアンプがフォールディングアンプに対応する入力信号を生成するために、本形式に対応した基準電圧VRを生成する基準電圧生成回路11を有する。

本実施の形態における第1のプリアンプは、前段プリアンプPA0a〜PA0cと後段プリアンプPB0a〜PB0cとを有する。そして、前段プリアンプPA0aと後段プリアンプPB0aとにより1つのプリアンプを構成し、前段プリアンプPA0bと後段プリアンプPB0bとにより1つのプリアンプを構成し、前段プリアンプPA0cと後段プリアンプPB0cとにより1つのプリアンプを構成する。これら3つのプリアンプは、並列に配置される。そして、図7に示す例では、奇数番目のプリアンプPB0a、PB0cの正転出力端子と偶数番目のプリアンプPB0bの反転出力端子とを接続し、奇数番目のプリアンプPB0a、PB0cの反転出力端子と偶数番目のプリアンプPB0bの正転出力端子とを接続する。また、3つのプリアンプにはそれぞれ個別の基準電圧VR0a〜VR0cと共通のアナログ入力信号AINが与えられる。

本実施の形態における第2のプリアンプは、前段プリアンプPA4a〜PA4cと後段プリアンプPB4a〜PB4cとを有する。そして、前段プリアンプPA4aと後段プリアンプPB4aとにより1つのプリアンプを構成し、前段プリアンプPA4bと後段プリアンプPB4bとにより1つのプリアンプを構成し、前段プリアンプPA4cと後段プリアンプPB4cとにより1つのプリアンプを構成する。これら3つのプリアンプは、並列に配置される。そして、図7に示す例では、奇数番目のプリアンプPB4a、PB4cの正転出力端子と偶数番目のプリアンプPB4bの反転出力端子とを接続し、奇数番目のプリアンプPB4a、PB4cの反転出力端子と偶数番目のプリアンプPB4bの正転出力端子とを接続する。また、3つのプリアンプにはそれぞれ個別の基準電圧VR4a〜VR4cと共通のアナログ入力信号AINが与えられる。

フォールディングアンプを採用した場合、本実施の形態にかかるアナログデジタル変換回路3は、後段プリアンプPB0a、PB4aを活性化させた場合には高位側信号に対する5ビットのデジタル値を生成し、後段プリアンプPB0b、PB4bを活性化させた場合には中位の信号に対する5ビットのデジタル値を生成し、後段プリアンプPB0c、PB4cを活性化させた場合には低位側の信号に対する5ビットのデジタル値を生成する。つまり、フォールディングアンプを用いることで、少ないコンパレータ数で同等の分解能の変換結果を得ることができる。

上記アナログデジタル変換回路3におけるキャリブレーション設定値について説明する。まず、コンパレータCMP0〜CMP4の遷移に対応するアナログデジタル変換回路の入力換算オフセットInOff30〜InOff34は、プリアンプの活性化状態に応じて異なる値となる。例えば、後段プリアンプPB0a、PB4aが活性化した場合におけるコンパレータCMP0〜CMP4の遷移に対応するアナログデジタル変換回路の入力換算オフセットは、(23)〜(27)式により表される。なお、OffA0aは前段プリアンプPA0aの入力オフセットであり、CALA0aはプリアンプキャリブレーション回路CALA0aのキャリブレーション設定値であり、OffA4aは前段プリアンプPA4aの入力オフセットであり、CALA4aはプリアンプキャリブレーション回路CALA4aのキャリブレーション設定値である。

また、後段プリアンプPB0b、PB4bが活性化した場合におけるコンパレータCMP0〜CMP4の遷移に対応するアナログデジタル変換回路の入力換算オフセットは、(28)〜(32)式により表される。なお、OffA0bは前段プリアンプPA0bの入力オフセットであり、CALA0bはプリアンプキャリブレーション回路CALA0bのキャリブレーション設定値であり、OffA4bは前段プリアンプPA4bの入力オフセットであり、CALA4bはプリアンプキャリブレーション回路CALA4bのキャリブレーション設定値である。

また、後段プリアンプPB0c、PB4cが活性化した場合におけるコンパレータCMP0〜CMP4の遷移に対応するアナログデジタル変換回路の入力換算オフセットは、(33)〜(37)式により表される。なお、OffA0cは前段プリアンプPA0cの入力オフセットであり、CALA0cはプリアンプキャリブレーション回路CALA0cのキャリブレーション設定値であり、OffA4cは前段プリアンプPA4cの入力オフセットであり、CALA4cはプリアンプキャリブレーション回路CALA4cのキャリブレーション設定値である。

ここで、本実施の形態では、第1のプリアンプから第1の出力信号が入力されるコンパレータCMP0に対応して設けられるコンパレータキャリブレーション回路CAL30のキャリブレーション設定値CAL30を0とする。また、第2のプリアンプから第2の出力信号が入力されるコンパレータCMP4に対応して設けられるコンパレータキャリブレーション回路CAL34のキャリブレーション設定値CAL34を0とする。そして、すべての遷移に対応するアナログデジタル変換回路の入力換算オフセットを0として(23)〜(37)式の解を求めると、キャリブレーション設定値CALA0、CALA4、CAL31〜CAL33は、(38)〜(46)式により表される。

上記説明より、フォールディング形式により構成されるプリアンプを有するアナログデジタル変換回路3においても(38)〜(46)式に示されるようなキャリブレーション設定値を得ることができる。(38)〜(46)式に示されるキャリブレーション設定値においても増幅率A1、A2を被乗算値として有する項はない。そのため、アナログデジタル変換回路3においても実施の形態1のアナログデジタル変換回路1と同様に、出力結果となるデジタル値に対する入力オフセットの影響をなくし、デジタル値の線形性を向上させることができる。

また、アナログデジタル変換回路3の変形例となるアナログデジタル変換回路3aのブロック図を図8に示す。図8に示すように、アナログデジタル変換回路3aは、アナログデジタル変換回路3に実施の形態2で説明したスイッチ回路SWBを追加したものである。このスイッチ回路SWBを追加することで、実施の形態2と同様にキャリブレーション設定値の算出を簡易化させることができる。

実施の形態4

実施の形態4では、実施の形態3にかかるアナログデジタル変換回路3におけるキャリブレーション設定値の別の算出方法について説明する。ここで、実施の形態4においてもンパレータCMP0〜CMP4の遷移に対応するアナログデジタル変換回路の入力換算オフセットは、上記(23)式〜(37)式により与えられる。しかし、実施の形態4では、プリアンプキャリブレーション回路CALA0a〜CALA4c、CALA4a〜CALA4cに与えるキャリブレーション設定値CALA0a〜CALA4c、CALA4a〜CALA4cに(47)式及び(48)式の条件を与える。

また、本実施の形態では、表記簡略化のために前段プリアンプPA0a〜PA0c及び後段プリアンプPB0a〜PB0cの入力換算オフセットの平均値OffP0を(49)式で表し、前段プリアンプPA4a〜PA4c及び後段プリアンプPB4a〜PB4cの入力換算オフセットの平均値OffP4を(50)式で表す。

そして、コンパレータCMP0〜CMP4の遷移に対応するアナログデジタル変換回路の入力換算オフセットInOff30〜InOff34は、(51)〜(55)式により表される。なお、(51)〜(55)式の値をすべてゼロとすることでアナログデジタル変換回路3のオフセットをキャンセルできることから、(51)〜(55)式では、入力換算オフセットInOff30〜InOff34をゼロとした式とした。

そして、(47)〜(55)式の解をもとめると、キャリブレーション設定値は、それぞれ(56)〜(67)式で表すことができる。

上記説明より、実施の形態4にかかるキャリブレーション設定値の算出方法では、(47)、(48)式に示す条件に従ってキャリブレーション設定値を算出することで、コンパレータキャリブレーション回路CAL30、CAL34によるオフセットの校正を行った場合であっても、各キャリブレーション設定値を一意に決定することができる。これにより、複数のキャリブレーション設定値を簡単に導出できるため、キャリブレーション設定値の算出にかかる時間を短縮することができる。

実施の形態5

実施の形態5にかかるアナログデジタル変換回路4のブロック図を図9に示す。図9に示すように、実施の形態5にかかるアナログデジタル変換回路4は、実施の形態3にかかるアナログデジタル変換回路3の変形例(アナログデジタル変換回路3a)の前段プリアンプにスイッチ回路SWA及びプリアンプキャリブレーション回路CALBを追加したものである。ここで、スイッチ回路SWAは、制御タイミングが異なるスイッチ回路SWAa〜SWAcを有する。

スイッチ回路SWAaは、フォールディングアンプの1番目のアンプに対応するプリアンプPA0a、PA4aの出力に設けられる。スイッチ回路SWAbは、フォールディングアンプの2番目のアンプに対応するプリアンプPA0b、PA4bの出力に設けられる。スイッチ回路SWAcは、フォールディングアンプの3番目のアンプに対応するプリアンプPA0c、PA4cの出力に設けられる。

また、プリアンプキャリブレーション回路CALBは、フォールディングアンプを構成するプリアンプのそれぞれに対応して設けられる。図9では、後段プリアンプPB0aに対応してプリアンプCALB0aが設けられ、後段プリアンプPB0bに対応してプリアンプCALB0bが設けられ、後段プリアンプPB0cに対応してプリアンプCALB0cが設けられ、後段プリアンプPB4aに対応してプリアンプCALB4aが設けられ、後段プリアンプPB4bに対応してプリアンプCALB4bが設けられ、後段プリアンプPB4cに対応してプリアンプCALB4cが設けられる。このプリアンプキャリブレーション回路CALBを有するフォールディングアンプの回路図を図10に示す。

図10に示すように、フォールディングアンプPBは、NMOSトランジスタN11〜N19、負荷抵抗RLを有する。フォールディングアンプPBでは、NMOSトランジスタN12、N13により1番目のプリアンプの差動対を構成し、NMOSトランジスタN11によりNMOSトランジスタN12、N13により構成される差動対に電流を供給する。また、NMOSトランジスタN12のゲートは1番目のプリアンプの正転入力端子であって、NMOSトランジスタN13のゲートは1番目のプリアンプの反転入力端子である。NMOSトランジスタN15、N16により2番目のプリアンプの差動対を構成し、NMOSトランジスタN14によりNMOSトランジスタN15、N16により構成される差動対に電流を供給する。また、NMOSトランジスタN15のゲートは2番目のプリアンプの正転入力端子であって、NMOSトランジスタN16のゲートは2番目のプリアンプの反転入力端子である。NMOSトランジスタN18、N19により3番目のプリアンプの差動対を構成し、NMOSトランジスタN17によりNMOSトランジスタN18、N19により構成される差動対に電流を供給する。また、NMOSトランジスタN18のゲートは3番目のプリアンプの正転入力端子であって、NMOSトランジスタN19のゲートは3番目のプリアンプの反転入力端子である。

そして、NMOSトランジスタN12、N16、N18のドレインは負荷抵抗RLの一端に接続される。また、NMOSトランジスタN13、N15、N19のドレインは負荷抵抗RLの一端に接続される。そして、2つの負荷抵抗RLの他端は電源端子に接続される。また、NMOSトランジスタN12、N16、N18のドレインはフォールディングアンプPBの正転出力端子となり、NMOSトランジスタN13、N15、N19のドレインはフォールディングアンプPBの反転出力端子となる。

プリアンプキャリブレーション回路CALBは、フォールディングアンプPBを構成するプリアンプのそれぞれに対応して設けられる。プリアンプキャリブレーション回路は、プリアンプの差動対を構成するトランジスタのそれぞれに並列に接続される2つの可変電流源を有する。プリアンプキャリブレーション回路CALBは、可変電流源が出力する電流の値によって負荷抵抗RLに流れる電流を調節することでプリアンプPBのオフセットをキャンセルする。つまり、プリアンプキャリブレーション回路CALBは、キャリブレーション設定値に基づき出力する電流の値が調節されるものである。

ここで、アナログデジタル変換回路4におけるキャリブレーション設定値について説明する。まず、コンパレータCMP0〜CMP4の遷移に対応するアナログデジタル変換回路の入力換算オフセットInOff30〜InOff34は、プリアンプの活性化状態に応じて異なる値となる。例えば、基準電圧VREFA0a及び基準電圧VREFA4a付近の電圧レベルを有する入力信号AINが入力されると後段プリアンプPB0a、PB4aが活性化する。この場合におけるコンパレータCMP0〜CMP4の遷移に対応するアナログデジタル変換回路の入力換算オフセットは、(67)〜(71)式により表される。なお、OffA0aは前段プリアンプPA0aの入力オフセットであり、CALA0aはプリアンプキャリブレーション回路CALA0aのキャリブレーション設定値であり、OffA4aは前段プリアンプPA4aの入力オフセットであり、CALA4aはプリアンプキャリブレーション回路CALA4aのキャリブレーション設定値である。また、OffB0aは後段プリアンプPB0aの入力オフセットであり、CALB0aはプリアンプキャリブレーション回路CALB0aのキャリブレーション設定値であり、OffB4aは後段プリアンプPB4aの入力オフセットであり、CALB4aはプリアンプキャリブレーション回路CALB4aのキャリブレーション設定値である。

また、基準電圧VREFA0b及び基準電圧VREFA4b付近の電圧レベルを有する入力信号AINが入力されると後段プリアンプPB0b、PB4bが活性化する。この場合におけるコンパレータCMP0〜CMP4の遷移に対応するアナログデジタル変換回路の入力換算オフセットは、(72)〜(76)式により表される。なお、OffA0bは前段プリアンプPA0bの入力オフセットであり、CALA0bはプリアンプキャリブレーション回路CALA0bのキャリブレーション設定値であり、OffA4bは前段プリアンプPA4bの入力オフセットであり、CALA4bはプリアンプキャリブレーション回路CALA4bのキャリブレーション設定値である。また、OffB0bは後段プリアンプPB0bの入力オフセットであり、CALB0bはプリアンプキャリブレーション回路CALB0bのキャリブレーション設定値であり、OffB4bは後段プリアンプPB4bの入力オフセットであり、CALB4bはプリアンプキャリブレーション回路CALB4bのキャリブレーション設定値である。

また、基準電圧VREFA0c及び基準電圧VREFA4c付近の電圧レベルを有する入力信号AINが入力されると後段プリアンプPB0c、PB4cが活性化する。この場合におけるコンパレータCMP0〜CMP4の遷移に対応するアナログデジタル変換回路の入力換算オフセットは、(77)〜(81)式により表される。なお、OffA0cは前段プリアンプPA0cの入力オフセットであり、CALA0cはプリアンプキャリブレーション回路CALA0cのキャリブレーション設定値であり、OffA4cは前段プリアンプPA4cの入力オフセットであり、CALA4cはプリアンプキャリブレーション回路CALA4cのキャリブレーション設定値である。また、OffB0cは後段プリアンプPB0cの入力オフセットであり、CALB0cはプリアンプキャリブレーション回路CALB0cのキャリブレーション設定値であり、OffB4cは後段プリアンプPB4cの入力オフセットであり、CALB4cはプリアンプキャリブレーション回路CALB4cのキャリブレーション設定値である。

実施の形態5にかかるアナログデジタル変換回路4では、実施の形態2にかかるアナログデジタル変換器4と同様に、キャリブレーション設定値を設定する対象となるコンパレータ又はプリアンプの前段に設けられるスイッチ回路をオンする。このとき、実施の形態5にかかるアナログデジタル変換回路4では、スイッチ回路が複数のステージに設けられているため、図11に示すフローチャートに沿ってキャリブレーションを行う。

図11に示すように、アナログデジタル変換回路4では、キャリブレーション開始時点において、まず、全てのキャリブレーション設定値を初期化する。また、スイッチ回路SWB、SWAa〜SWAcをオフにする(ステップS11)。続いて、スイッチ回路SWBをオンする(ステップS12)。これにより、コンパレータCMP0〜CMP4の正転入力端子と反転入力端子は同電位になる。この状態で、コンパレータCMP0〜CMP4に対応するコンパレータキャリブレーション回路CAL30〜CAL34のキャリブレーション設定値を操作する。そして、コンパレータCMP0〜CMP4の出力がハイレベルとロウレベルとの間をトグルするようにキャリブレーション設定値を設定する(ステップS13)。

続いて、スイッチ回路SWBをオフし、スイッチ回路SWAaをオンする(ステップS14)。これにより、フォールディングアンプの1番目のプリアンプ(図9のプリアンプPB0aとプリアンプPB4a)の正転入力端子と反転入力端子が同電位になる。そして、プリアンプPB0a、PB4aに対応するプリアンプキャリブレーション回路CALB0a、CALB4aのキャリブレーション設定値を操作する。そして、コンパレータCMP0〜CMP4の出力がハイレベルとロウレベルとの間をトグルするようにプリアンプキャリブレーション回路CALB0a、CALB4aのキャリブレーション設定値を設定する(ステップS15)。

続いて、スイッチ回路SWAaをオフし、スイッチ回路SWAbをオンする(ステップS16)。これにより、フォールディングアンプの2番目のプリアンプ(図9のプリアンプPB0bとプリアンプPB4b)の正転入力端子と反転入力端子が同電位になる。そして、プリアンプPB0b、PB4bに対応するプリアンプキャリブレーション回路CALB0b、CALB4bのキャリブレーション設定値を操作する。そして、コンパレータCMP0〜CMP4の出力がハイレベルとロウレベルとの間をトグルするようにプリアンプキャリブレーション回路CALB0b、CALB4bのキャリブレーション設定値を設定する(ステップS17)。

続いて、スイッチ回路SWAbをオフし、スイッチ回路SWAcをオンする(ステップS18)。これにより、フォールディングアンプの3番目のプリアンプ(図9のプリアンプPB0cとプリアンプPB4c)の正転入力端子と反転入力端子が同電位になる。そして、プリアンプPB0c、PB4cに対応するプリアンプキャリブレーション回路CALB0c、CALB4cのキャリブレーション設定値を操作する。そして、コンパレータCMP0〜CMP4の出力がハイレベルとロウレベルとの間をトグルするようにプリアンプキャリブレーション回路CALB0c、CALB4cのキャリブレーション設定値を設定する(ステップS19)。

続いて、スイッチ回路SWAcをオフする(ステップS20)。続いて、キャリブレーション用アナログ入力信号AINを入力し、キャリブレーション用アナログ入力信号AINに応じたデジタル値を各コンパレータから得る。そして、コンパレータから得られたデジタル値とキャリブレーション用アナログ入力信号AINに対応して予め設けられた期待値とを比較しプリアンプPA0a〜PA0c、PA4a〜PA4cの入力オフセット量を算出する。この入力オフセット量に基づき、プリアンプPA0a〜PA0c、PA4a〜PA4cに対応するプリアンプキャリブレーション回路CALA0a〜CALA0c、CALA4a〜CALA4cのキャリブレーション設定値を設定する(ステップS21)。これにより、全てのキャリブレーション設定値の設定が完了するため、その後通常動作に移行する。

上記説明より、実施の形態5にかかるアナログデジタル変換回路4では、後段プリアンプPBに対してもプリアンプキャリブレーション回路CALBを設けた。これにより、後段プリアンプPBに対しても独立したキャリブレーション設定値を設定することが可能になり、実施の形態1〜4に記載のアナログデジタル変換回路よりも高精度にキャリブレーションを行うことが可能になる。

実施の形態6

実施の形態6にかかるアナログデジタル変換回路5のブロック図を図12に示す。図21に示すブロック図では、フォールディングアンプを1つの回路ブロックとして示した。また、前段プリアンプPA及びプリアンプ用補間回路(例えば、プリアンプ用補間回路31)についても回路ブロックとして詳細な素子の表示を省略した。さらに、図12では、フォールディングアンプの後段に接続される補間回路30及びコンパレータCMPについても省略した。補間回路30及びコンパレータCMPについては上記実施の形態1〜5に準ずるものである。

実施の形態6にかかるアナログデジタル変換回路5は、実施の形態5にかかるアナログデジタル変換回路4の後段プリアンプとなるフォールディングアンプの数を増加させたものである。実施の形態5にかかるアナログデジタル変換回路4では、フォールディングアンプは2つであったが、実施の形態6にかかるアナログデジタル変換回路6は、フォールディングアンプの数は3つである。

また、実施の形態6にかかるアナログデジタル変換回路5では、追加したフォールディングアンプ(例えば、後段プリアンプに相当するプリアンプPB2a〜PB2c)に入力する信号を補間回路31により生成する。つまり、実施の形態6にかかる補間回路31は、2つプリアンプPAの出力の間(例えば、プリアンプPA0aとプリアンプPA4aとの間)に直列に接続された2つの抵抗を有する。そして、2つの抵抗の間から追加したフォールディングアンプに入力されるプリアンプ用補間信号を生成する。図9に示す例では、追加したフォールディングアンプは、プリアンプPB0a〜PB0cにより構成されるフォールディングアンプに対応する入力電圧レベルと、プリアンプPB4a〜PB4cにより構成されるフォールディングアンプに対応する入力電圧レベルと、の中間電圧レベルに対応するものである。

また、図9に示すアナログデジタル変換回路5では、追加したフォールディングアンプの出力にスイッチ回路SWBが設けられている。

実施の形態6にかかるアナログデジタル変換回路5では、後段プリアンプの数を増加させた場合における補正回路31の変形例を示した。つまり、本発明にかかるアナログデジタル変換回路では、補正回路31により、中間的な電圧レベルの信号を出力することで、前段プリアンプの数を増加させることなく後段プリアンプの数を増加させることができる。

実施の形態7

実施の形態7にかかるアナログデジタル変換回路6のブロック図を図13に示す。図13に示すブロック図は、図12に示したブロック図を拡張したものである。図13に示すように、アナログデジタル変換回路6は、図12に示したアナログデジタル変換回路5の後段プリアンプに相当するフォールディングアンプを2段有する。また、図13に示すアナログデジタル変換回路6は、コンパレータCMPを9個(例えば、コンパレータCMP0〜CMP8)有する。つまり、アナログデジタル変換回路6は、実施の形態1〜6にかかるアナログデジタル変換回路よりも高分解能である。

図13に示すように、アナログデジタル変換回路6は、前段プリアンプPA、第1の後段プリアンプPB、第2の後段プリアンプPC、補正回路31、32、スイッチ回路SWAa〜SWAc、スイッチ回路SWBa〜SWBc、スイッチ回路SWCを有する。そして、アナログデジタル変換回路6は、第2の後段プリアンプPCの出力信号を実施の形態1〜4において示した補間回路30及びコンパレータCMP0〜CMP8に出力する。

より具体的には、アナログデジタル変換回路6は、補間回路30及びコンパレータCMP0〜CMP8に信号を出力する第2の後段プリアンプPCが複数設けられている。この第2の後段プリアンプPCは、実施の形態3において説明したフォールディングアンプである。図13に示す例では、コンパレータCMP0に信号を出力するフォールディングアンプは、プリアンプPC0a〜PC0cにより構成され、コンパレータCMP2に信号を出力するフォールディングアンプは、プリアンプPC2a〜PC2cにより構成され、コンパレータCMP4に信号を出力するフォールディングアンプは、プリアンプPC4a〜PC4cにより構成され、コンパレータCMP6に信号を出力するフォールディングアンプは、プリアンプPC6a〜PC6cにより構成され、コンパレータCMP8に信号を出力するフォールディングアンプは、プリアンプPC8a〜PC8cにより構成される。また、上記5つのフォールディングアンプPCの出力にはスイッチ回路SWCが設けられている。スイッチ回路SWCは、対応するフォールディングアンプの出力端子間をリセット信号に応じて短絡する。

そして、第2の後段プリアンプと第1の後段プリアンプとの間にはプリアンプ用補間回路(例えば、補間回路32)が設けられる。補間回路32は、第1の後段プリアンプPBの出力信号に基づき第2の後段プリアンプPCへの入力信号を生成する。より具体的には、補間回路32は、第1の後段プリアンプ(不図示)から第2の後段プリアンプPCの1番目の後段プリアンプPC0a、PC4a、PC8aに入力されるべき信号を受信し、これら受信した信号と、受信した信号から生成される第2の後段プリアンプPCの1番目の後段プリアンプPC2a、PC6aに入力されるプリアンプ用補間信号と、を出力する。また、補間回路32は、第1の後段プリアンプPBから第2の後段プリアンプPCの2番目の後段プリアンプPC0b、PC4b、PC8bに入力されるべき信号を受信し、これら受信した信号と、受信した信号から生成される第2の後段プリアンプPCの2番目の後段プリアンプPC2b、PC6bに入力されるプリアンプ用補間信号と、を出力する。また、補間回路32は、第1の後段プリアンプ(不図示)から第2の後段プリアンプPCの3番目の後段プリアンプPC0c、PC4c、PC8cに入力されるべき信号を受信し、これら受信した信号と、受信した信号から生成される第2の後段プリアンプPCの3番目の後段プリアンプPC2c、PC6cに入力されるプリアンプ用補間信号と、を出力する。

図13では、第2の後段プリアンプPCとして設けられるフォールディングアンプの2番目の後段プリアンプPC0b、PC4b、PC8bに対応する信号を生成する第1の前段プリアンプのみを示した。しかし、アナログデジタル変換回路6では、第2の後段プリアンプPCとして設けられるフォールディングアンプの1番目の後段プリアンプPC0a、PC4a、PC8aに対応する信号を生成する第1の後段プリアンプ、及び、第2の後段プリアンプPCとして設けられるフォールディングアンプの3番目の後段プリアンプPC0c、PC4c、PC8cに対応する信号を生成する第1の後段プリアンプ、も有する。また、アナログデジタル変換回路6は、1番目の後段プリアンプPC0a、PC4a、PC8aに対応する信号を生成する第1の後段プリアンプPBに対応する前段プリアンプPA、及び、3番目の後段プリアンプPC0c、PC4c、PC8cに対応する信号を生成する第1の後段プリアンプPBに対応する前段プリアンプPAも有する。これら、不図示の構成要素については、図13に図示する前段プリアンプPA及び第1の後段プリアンプPBの接続形態に準じた接続形態となる。

ここでは、図13において図示した構成要素についてのみ説明する。第1の後段プリアンプPBは、3つのフォールディングアンプを構成する。第1の後段プリアンプPB0a〜PB0cは、第2の後段プリアンプPC0bに入力される信号を出力する。第1の後段プリアンプPB4a〜PB4cは、第2の後段プリアンプPC4bに入力される信号を出力する。第1の後段プリアンプPB8a〜PB8cは、第2の後段プリアンプPC8bに入力される信号を出力する。

また、図13に図示する第1の後段プリアンプPBの出力にはスイッチ回路SWBbが設けられており、各フォールディングアンプの出力端子間をリセット信号に応じて短絡する。なお、スイッチ回路SWBaは、後段プリアンプPC0a、PC4a、PC8aに対応する信号を生成する第1の後段プリアンプの出力端子に設けられ、第1の後段プリアンプの出力端子間をリセット信号に応じて短絡する。また、スイッチ回路SWBcは、後段プリアンプPC0c、PC4c、PC8cに対応する信号を生成する第1の後段プリアンプの出力端子に設けられ、第1の後段プリアンプの出力端子間をリセット信号に応じて短絡する。

補間回路31は、前段プリアンプと第1の後段プリアンプとの間に設けられる。補間回路31は、前段プリアンプPAの出力信号に基づき第1の後段プリアンプPBへの入力信号を生成する。より具体的には、補間回路31は、前段プリアンプPA0a、PA8aから第1の後段プリアンプPBの1番目の後段プリアンプPB0a、PB8aに入力されるべき信号を受信し、これら受信した信号と、受信した信号から生成される第1の後段プリアンプPBの1番目の後段プリアンプPB4aに入力される信号と、を出力する。また、補間回路31は、前段プリアンプPBから第1の後段プリアンプPBの2番目の後段プリアンプPB0b、PB8bに入力されるべき信号を受信し、これら受信した信号と、受信した信号から生成される第1の後段プリアンプPBの2番目の後段プリアンプPB4bに入力される信号と、を出力する。また、補間回路31は、前段プリアンプPA0c、PA8cから第1の後段プリアンプPBの3番目の後段プリアンプPB0c、PB8cに入力されるべき信号を受信し、これら受信した信号と、受信した信号から生成される第1の後段プリアンプPBの3番目の後段プリアンプPB4cに入力される信号と、を出力する。

また、図13に図示する前段プリアンプPA0a、PA8aの出力にはスイッチ回路SWAaが設けられており、前段プリアンプPAの出力端子間をリセット信号に応じて短絡する。スイッチ回路SWAbは、前段プリアンプPA0b、PA8b出力端子に設けられ、前段プリアンプの出力端子間をリセット信号に応じて短絡する。また、スイッチ回路SWAcは、前段プリアンプPA0c、PA8c出力端子に設けられ、前段プリアンプの出力端子間をリセット信号に応じて短絡する。

続いて、実施の形態7にかかるアナログデジタル変換回路6のキャリブレーション動作について説明する。実施の形態7にかかるアナログデジタル変換回路6では、実施の形態2にかかるアナログデジタル変換器4と同様に、キャリブレーション設定値を設定する対象となるコンパレータ又はプリアンプの前段に設けられるスイッチ回路をオンする。このとき、実施の形態7にかかるアナログデジタル変換回路6では、スイッチ回路が複数のステージに設けられているため、図14に示すフローチャートに沿ってキャリブレーションを行う。

なお、上記説明では、プリアンプキャリブレーション回路及びコンパレータキャリブレーション回路については、説明を省略したが、実施の形態7にかかるアナログデジタル変換回路においてもこれらキャリブレーション回路は実装されているものとする。

図14に示すように、アナログデジタル変換回路6では、キャリブレーション開始時点において、まず、全てのキャリブレーション設定値を初期化する。また、全てのスイッチ回路をオフにする(ステップS30)。続いて、スイッチ回路SWCをオンする(ステップS31)。これにより、コンパレータCMP0〜CMP8の正転入力端子と反転入力端子は同電位になる。この状態で、コンパレータCMP0〜CMP8に対応するコンパレータキャリブレーション回路CAL30〜CAL38のキャリブレーション設定値を操作する。そして、コンパレータCMP0〜CMP8の出力がハイレベルとロウレベルとの間をトグルするようにキャリブレーション設定値を設定する(ステップS32)。

続いて、スイッチ回路SWCをオフし、スイッチ回路SWBaをオンする(ステップS33)。これにより、第2の後段プリアンプのフォールディングアンプの1番目のプリアンプ(図13のプリアンプPC0a、PC2a、PC4a、PC6a、PC8a)の正転入力端子と反転入力端子が同電位になる。そして、プリアンプPC0a、PC2a、PC4a、PC6a、PC8aに対応するプリアンプキャリブレーション回路CALC0a、CALC2a、CALC4a、CALC6a、CALC8aのキャリブレーション設定値を操作する。そして、コンパレータCMP0〜CMP8の出力がハイレベルとロウレベルとの間をトグルするようにプリアンプキャリブレーション回路CALC0a、CALC2a、CALC4a、CALC6a、CALC8aのキャリブレーション設定値を設定する(ステップS34)。

続いて、スイッチ回路SWBaをオフし、スイッチ回路SWBbをオンする(ステップS35)。これにより、第2の後段プリアンプのフォールディングアンプの2番目のプリアンプ(図13のプリアンプPC0b、PC2b、PC4b、PC6b、PC8b)の正転入力端子と反転入力端子が同電位になる。そして、プリアンプPC0b、PC2b、PC4b、PC6b、PC8bに対応するプリアンプキャリブレーション回路CALC0b、CALC2b、CALC4b、CALC6b、CALC8bのキャリブレーション設定値を操作する。そして、コンパレータCMP0〜CMP8の出力がハイレベルとロウレベルとの間をトグルするようにプリアンプキャリブレーション回路CALC0b、CALC2b、CALC4b、CALC6b、CALC8bのキャリブレーション設定値を設定する(ステップS36)。

続いて、スイッチ回路SWBbをオフし、スイッチ回路SWBcをオンする(ステップS37)。これにより、第2の後段アンプのフォールディングアンプの3番目のプリアンプ(図13のプリアンプPC0c、PC2c、PC4c、PC6c、PC8c)の正転入力端子と反転入力端子が同電位になる。そして、プリアンプPC0c、PC2c、PC4c、PC6c、PC8cに対応するプリアンプキャリブレーション回路CALC0c、CALC2c、CALC4c、CALC6c、CALC8cのキャリブレーション設定値を操作する。そして、コンパレータCMP0〜CMP8の出力がハイレベルとロウレベルとの間をトグルするようにプリアンプキャリブレーション回路CALC0c、CALC2c、CALC4c、CALC6c、CALC8cのキャリブレーション設定値を設定する(ステップS38)。

続いて、スイッチ回路SWBcをオフし、スイッチ回路SWAaをオンする(ステップS39)。これにより、第1の後段プリアンプのフォールディングアンプの1番目のプリアンプ(図13のプリアンプPB0a、PB4a、PB8a)の正転入力端子と反転入力端子が同電位になる。そして、プリアンプPB0a、PB4a、PB8aに対応するプリアンプキャリブレーション回路CALB0a、CALB4a、CALB8aのキャリブレーション設定値を操作する。そして、コンパレータCMP0〜CMP8の出力がハイレベルとロウレベルとの間をトグルするようにプリアンプキャリブレーション回路CALB0a、CALB4a、CALB8aのキャリブレーション設定値を設定する(ステップS40)。

続いて、スイッチ回路SWAaをオフし、スイッチ回路SWAbをオンする(ステップS41)。これにより、第1の後段プリアンプのフォールディングアンプの2番目のプリアンプ(図13のプリアンプPB0b、PB4b、PB8b)の正転入力端子と反転入力端子が同電位になる。そして、プリアンプPB0b、PB4b、PB8bに対応するプリアンプキャリブレーション回路CALB0b、CALB4b、CALB8bのキャリブレーション設定値を操作する。そして、コンパレータCMP0〜CMP8の出力がハイレベルとロウレベルとの間をトグルするようにプリアンプキャリブレーション回路CALB0b、CALB4b、CALB8bのキャリブレーション設定値を設定する(ステップS42)。

続いて、スイッチ回路SWAbをオフし、スイッチ回路SWAcをオンする(ステップS43)。これにより、第1の前段プリアンプのフォールディングアンプの3番目のプリアンプ(図13のプリアンプPB0c、PB4c、PB8c)の正転入力端子と反転入力端子が同電位になる。そして、プリアンプPB0c、PB4c、PB8cに対応するプリアンプキャリブレーション回路CALB0c、CALB4c、CAL8cのキャリブレーション設定値を操作する。そして、コンパレータCMP0〜CMP8の出力がハイレベルとロウレベルとの間をトグルするようにプリアンプキャリブレーション回路CALB0c、CALB4c、CAL8cのキャリブレーション設定値を設定する(ステップS44)。

続いて、スイッチ回路SWAcをオフする(ステップS45)。続いて、キャリブレーション用アナログ入力信号AINを入力し、キャリブレーション用アナログ入力信号AINに応じたデジタル値を各コンパレータから得る。そして、コンパレータから得られたデジタル値とキャリブレーション用アナログ入力信号AINに対応して予め設けられた期待値とを比較しプリアンプPA0a〜PA0c、PA8a〜PA8cの入力オフセット量を算出する。この入力オフセット量に基づき、プリアンプPA0a〜PA0c、PA8a〜PA8cに対応するプリアンプキャリブレーション回路CALA0a〜CALA0c、CALA8a〜CALA8cのキャリブレーション設定値を設定する(ステップS46)。これにより、全てのキャリブレーション設定値の設定が完了するため、その後通常動作に移行する。

上記説明より、実施の形態7にかかるアナログデジタル変換回路6では、後段プリアンプが2段のフォールディングアンプにより構成される。そして、2段のフォールディングアンプを構成する第1の後段プリアンプPB及び第2の後段プリアンプPCに対してもプリアンプキャリブレーション回路CALB、CALCを設けた。これにより、後段プリアンプPB、PCに対しても独立したキャリブレーション設定値を設定することが可能になり、実施の形態1〜6に記載のアナログデジタル変換回路よりも高精度にキャリブレーションを行うことが可能になる。

実施の形態8

上記実施の形態において示したフォールディングアンプでは、1つのプリアンプに対するキャリブレーション動作中においても他のプリアンプを動作させる。一方、実施の形態8にかかるアナログデジタル変換回路では、フォールディングアンプを構成するプリアンプのうち1つのプリアンプに対してキャリブレーション動作を行っている期間は、他のプリアンプの動作を停止する。

そこで、実施の形態8にかかるフォールディングアンプの回路図を図15に示す。図15に示すフォールディングアンプPBは、図10で示したフォールディングアンプPBにスイッチ回路SW1〜SW3を追加したものである。スイッチ回路SW1〜SW3は、電流源となるトランジスタN1〜N3と各電流源に対応する差動対との間に設けられる。スイッチ回路SW1〜SW3は、制御信号に応じてオン/オフが制御される。

図15で示したフォールディングアンプPBを有するアナログデジタル変換回路のキャリブレーション動作について説明する。実施の形態8では、実施の形態5に対応するアナログデジタル変換回路に図15で示したフォールディングアンプPBを採用した場合の動作について説明する。そこで、実施の形態8にかかるアナログデジタル変換回路のキャリブレーション動作のフローチャートを図16に示す。

図16に示すように、実施の形態8にかかるアナログデジタル変換回路では、キャリブレーション開始時点において、まず、全てのキャリブレーション設定値を初期化する。また、スイッチ回路SWB、SWAa〜SWAcをオフ、スイッチ回路SW1〜SW3をオンにする(ステップS51)。続いて、スイッチ回路SWBをオンする(ステップS52)。これにより、コンパレータCMP0〜CMP4の正転入力端子と反転入力端子は同電位になる。この状態で、コンパレータCMP0〜CMP4に対応するコンパレータキャリブレーション回路CAL30〜CAL34のキャリブレーション設定値を操作する。そして、コンパレータCMP0〜CMP4の出力がハイレベルとロウレベルとの間をトグルするようにキャリブレーション設定値を設定する(ステップS53)。

続いて、スイッチ回路SWB、SW2、SW3をオフし、スイッチ回路SWAa、SW1をオンする(ステップS54)。これにより、フォールディングアンプの1番目のプリアンプ(図9のプリアンプPB0aとプリアンプPB4a)の正転入力端子と反転入力端子が同電位になる。また、フォールディングアンプの2番目のプリアンプ(図9のプリアンプPB0bとプリアンプPB4b)、及び、フォールディングアンプの3番目のプリアンプ(図9のプリアンプPB0cとプリアンプPB4c)が停止する。そして、プリアンプPB0a、PB4aに対応するプリアンプキャリブレーション回路CALB0a、CALB4aのキャリブレーション設定値を操作する。そして、コンパレータCMP0〜CMP4の出力がハイレベルとロウレベルとの間をトグルするようにプリアンプキャリブレーション回路CALB0a、CALB4aのキャリブレーション設定値を設定する(ステップS55)。

続いて、スイッチ回路SWAa、SW1、SW3をオフし、スイッチ回路SWAb、SW2をオンする(ステップS56)。これにより、フォールディングアンプの2番目のプリアンプ(図9のプリアンプPB0bとプリアンプPB4b)の正転入力端子と反転入力端子が同電位になる。また、フォールディングアンプの1番目のプリアンプ(図9のプリアンプPB0aとプリアンプPB4a)、及び、フォールディングアンプの3番目のプリアンプ(図9のプリアンプPB0cとプリアンプPB4c)が停止する。そして、プリアンプPB0b、PB4bに対応するプリアンプキャリブレーション回路CALB0b、CALB4bのキャリブレーション設定値を操作する。そして、コンパレータCMP0〜CMP4の出力がハイレベルとロウレベルとの間をトグルするようにプリアンプキャリブレーション回路CALB0b、CALB4bのキャリブレーション設定値を設定する(ステップS57)。

続いて、スイッチ回路SWAb、SW1、SW2をオフし、スイッチ回路SWAc、SW3をオンする(ステップS58)。これにより、フォールディングアンプの3番目のプリアンプ(図9のプリアンプPB0cとプリアンプPB4c)の正転入力端子と反転入力端子が同電位になる。また、フォールディングアンプの1番目のプリアンプ(図9のプリアンプPB0aとプリアンプPB4a)、及び、フォールディングアンプの2番目のプリアンプ(図9のプリアンプPB0bとプリアンプPB4b)が停止する。そして、プリアンプPB0c、PB4cに対応するプリアンプキャリブレーション回路CALB0c、CALB4cのキャリブレーション設定値を操作する。そして、コンパレータCMP0〜CMP4の出力がハイレベルとロウレベルとの間をトグルするようにプリアンプキャリブレーション回路CALB0c、CALB4cのキャリブレーション設定値を設定する(ステップS59)。

続いて、スイッチ回路SWAcをオフし、スイッチ回路SW1〜SW3をオンする(ステップS60)。続いて、キャリブレーション用アナログ入力信号AINを入力し、キャリブレーション用アナログ入力信号AINに応じたデジタル値を各コンパレータから得る。そして、コンパレータから得られたデジタル値とキャリブレーション用アナログ入力信号AINに対応して予め設けられた期待値とを比較しプリアンプPA0a〜PA0c、PA4a〜PA4cの入力オフセット量を算出する。この入力オフセット量に基づき、プリアンプPA0a〜PA0c、PA4a〜PA4cに対応するプリアンプキャリブレーション回路CALA0a〜CALA0c、CALA4a〜CALA4cのキャリブレーション設定値を設定する(ステップS61)。これにより、全てのキャリブレーション設定値の設定が完了するため、その後通常動作に移行する。

上記説明より、実施の形態8にかかるアナログデジタル変換回路では、フォールディングアンプを構成する後段プリアンプPBのキャリブレーション設定値を設定する際に、キャリブレーション対象となっていない後段プリアンプPBを停止する。これにより、キャリブレーション対象となっている後段プリアンプのみを正確にキャリブレーションすることができる。そのため、実施の形態8にかかるアナログデジタル変換回路は、キャリブレーションによるオフセットの補正を他の実施の形態よりも高精度に行うことができる。

なお、本発明は上記実施の形態に限られたものではなく、趣旨を逸脱しない範囲で適宜変更することが可能である。例えば、アナログデジタル変換回路を構成するプリアンプの個数及びコンパレータの個数は、アナログデジタル変換回路の仕様に応じて変更することが可能である。